5 - Синтез цифровых устройств.pptx

- Количество слайдов: 14

Роль и место булевой алгебры 1. 2. 3. 4. Последовательность действий синтеза вычислительных устройств: Словесное описание функции Таблица истинности Алгебраическое выражение Логическая схема Булева алгебра рассматривается как абстрактная модель аппарата, описывающая его работу. 1

Последовательность действий в аппаратной среде 1. 2. 3. 4. 5. 6. Физико-технический процесс Транзистор Вентиль Узел Блок Устройство 2

Минимизация алгебраического выражения проводится по двум критериям: 1. Минимум аппаратных затрат (вентилей) 2. Минимум времени задержки (в узле, блоке или устройстве) В современной микроэлектронике доминирует второй критерий, т. е. время задержки в системе стараются снизить в ущерб количеству вентилей 3

Законы Булевой алгебры Законы эквивалентности X+1=1 X+0=X X*1=X X*0=0 X = X X*X=X X+X=X 4

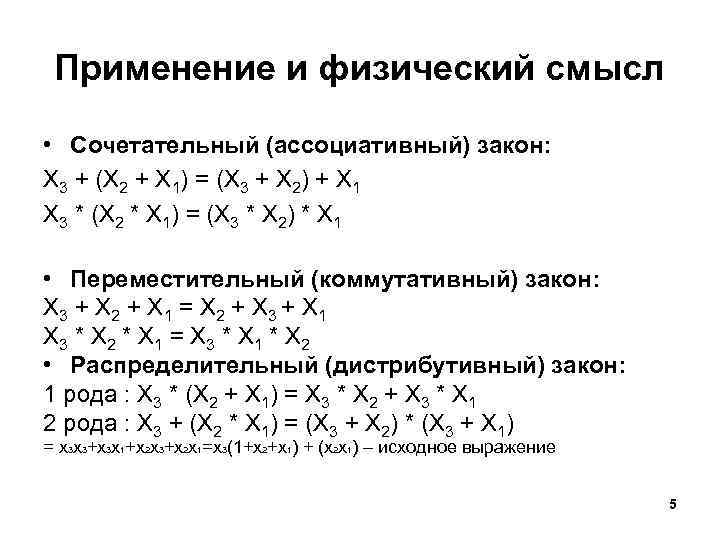

Применение и физический смысл • Сочетательный (ассоциативный) закон: X 3 + (X 2 + X 1) = (X 3 + X 2) + X 1 X 3 * (X 2 * X 1) = (X 3 * X 2) * X 1 • Переместительный (коммутативный) закон: X 3 + X 2 + X 1 = X 2 + X 3 + X 1 X 3 * X 2 * X 1 = X 3 * X 1 * X 2 • Распределительный (дистрибутивный) закон: 1 рода : X 3 * (X 2 + X 1) = X 3 * X 2 + X 3 * X 1 2 рода : X 3 + (X 2 * X 1) = (X 3 + X 2) * (X 3 + X 1) = x 3 x 3+x 3 x 1+x 2 x 3+x 2 x 1=x 3(1+x 2+x 1) + (x 2 x 1) – исходное выражение 5

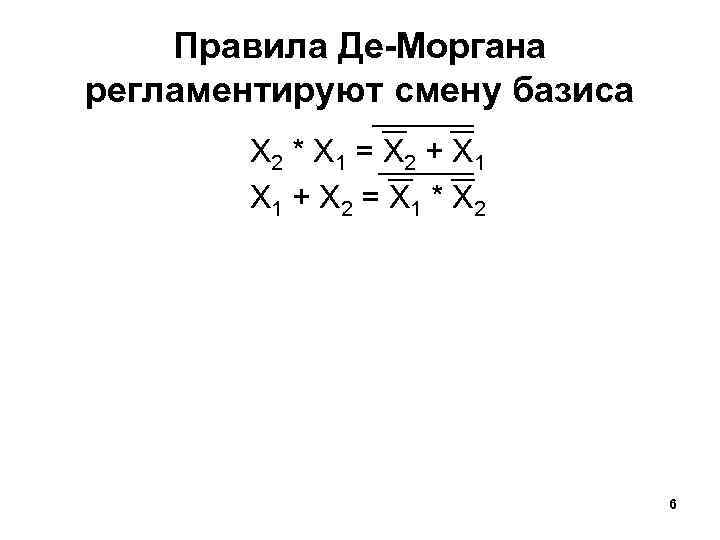

Правила Де-Моргана регламентируют смену базиса X 2 * X 1 = X 2 + X 1 + X 2 = X 1 * X 2 6

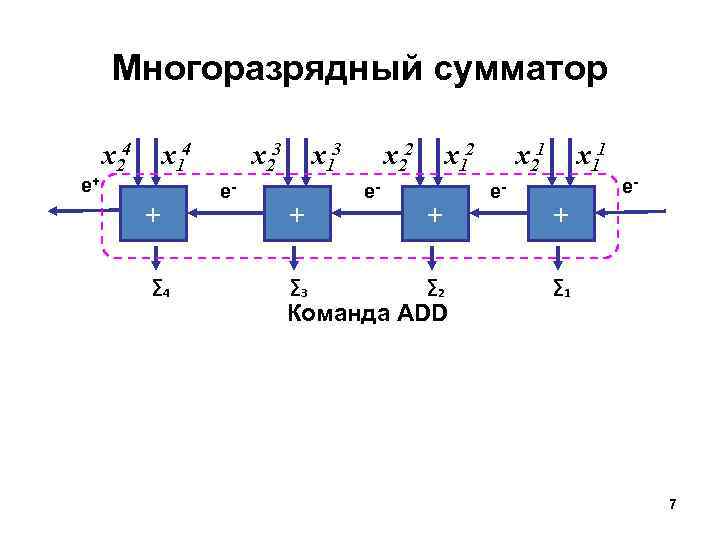

Многоразрядный сумматор e+ x 24 x 14 + ∑ 4 x 23 e- x 13 + ∑ 3 x 22 e- x 12 + ∑ 2 Команда ADD x 21 e- x 11 + e- ∑ 1 7

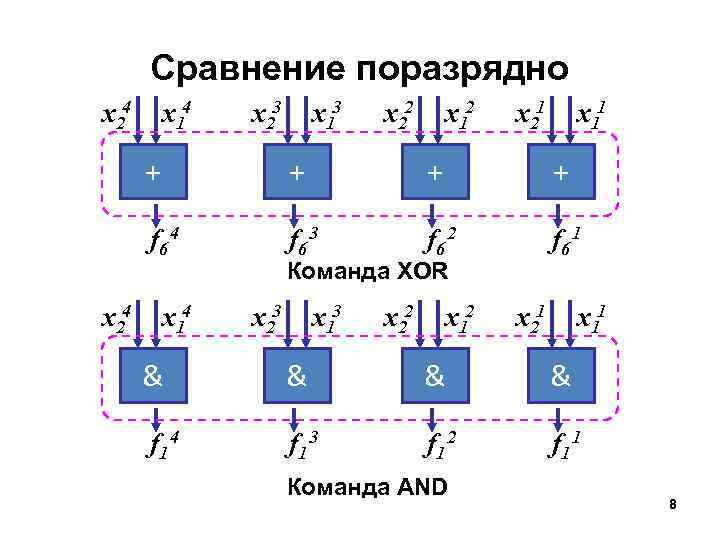

Сравнение поразрядно x 24 x 14 x 23 x 13 x 22 x 12 x 21 x 11 + + + f 6 4 x 24 + f 6 3 f 6 2 f 6 1 x 14 Команда XOR x 23 x 13 x 22 x 12 x 21 x 11 & & f 1 4 f 1 3 f 1 2 f 1 1 Команда AND 8

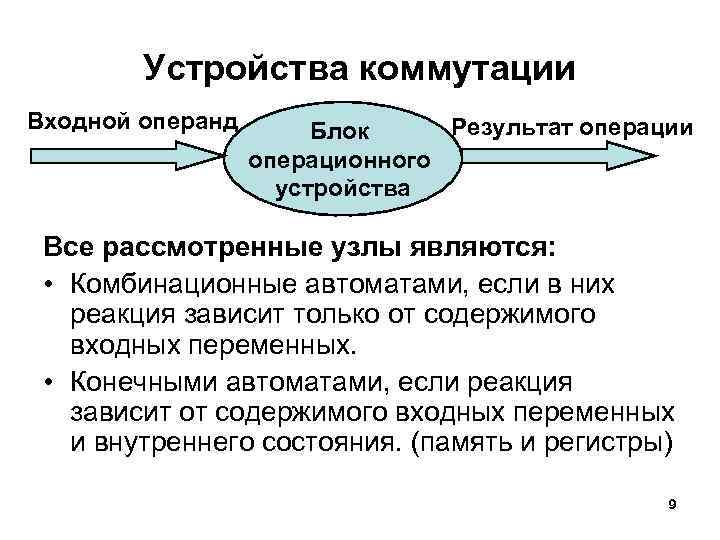

Устройства коммутации Входной операнд Результат операции Блок операционного устройства Все рассмотренные узлы являются: • Комбинационные автоматами, если в них реакция зависит только от содержимого входных переменных. • Конечными автоматами, если реакция зависит от содержимого входных переменных и внутреннего состояния. (память и регистры) 9

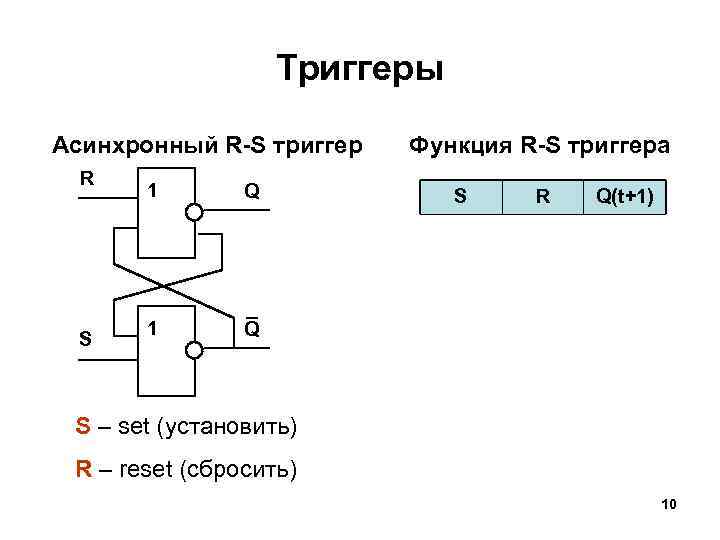

Триггеры Асинхронный R-S триггер R S 1 Q 1 Функция R-S триггера Q S R Q(t+1) S – set (установить) R – reset (сбросить) 10

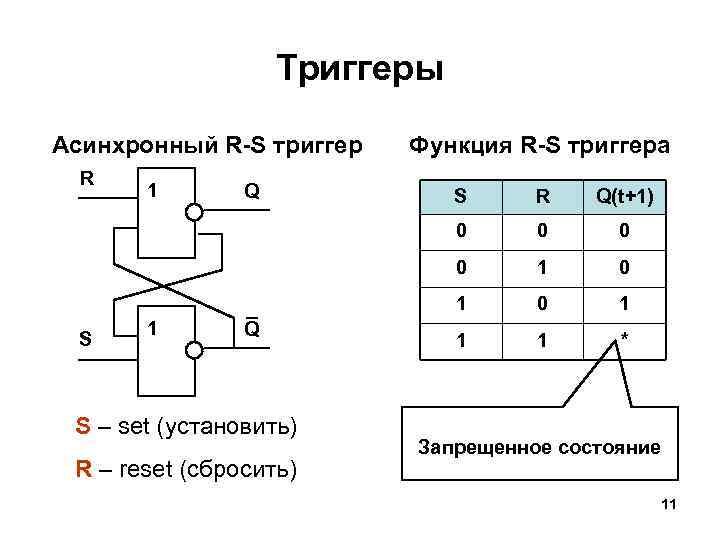

Триггеры Асинхронный R-S триггер R 1 Q Функция R-S триггера S – set (установить) R – reset (сбросить) 0 0 1 Q Q(t+1) 0 1 R 0 S S 0 1 1 1 * Запрещенное состояние 11

Синхронный R-S триггер R & 1 Q C S & S 12

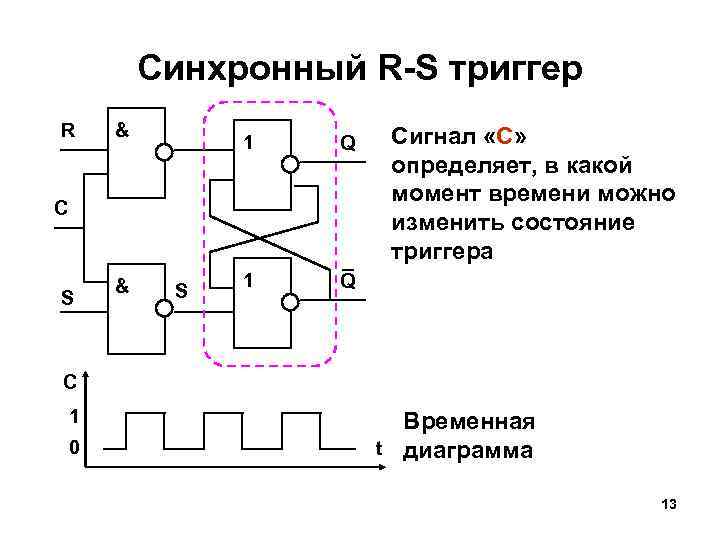

Синхронный R-S триггер R & 1 Q C S & S Сигнал «С» определяет, в какой момент времени можно изменить состояние триггера C 1 0 Временная t диаграмма 13

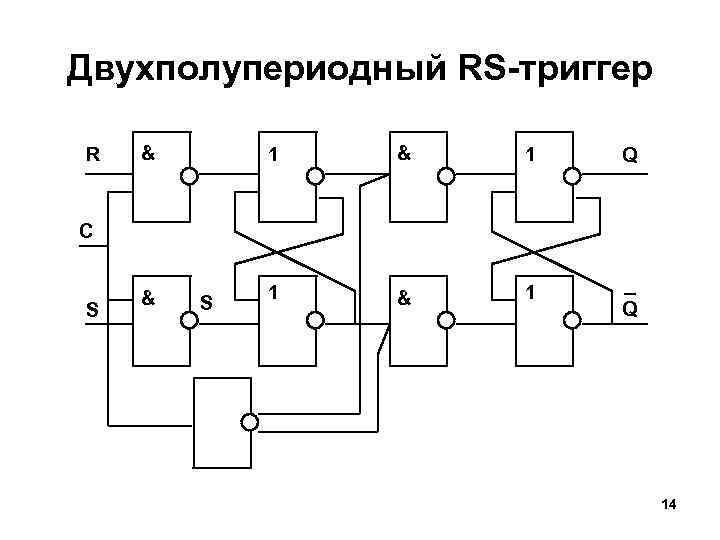

Двухполупериодный RS-триггер R & 1 1 & 1 Q C S & S Q 14

5 - Синтез цифровых устройств.pptx