33f42a362c3819b1c4147bb1224a289c.ppt

- Количество слайдов: 22

RMO 1 C-3 An ultra low power LNA with 15 d. B gain and 4. 4 db NF in 90 nm CMOS process for 60 GHz phase array radio Emanuel Cohen(12), Shmuel Ravid(1), and Dan Ritter(2) (1) (2) Mobile Wireless Group, Intel Haifa, Israel Department of Electrical Engineering, Technion, Haifa, Israel

RMO 1 C-3 An ultra low power LNA with 15 d. B gain and 4. 4 db NF in 90 nm CMOS process for 60 GHz phase array radio Emanuel Cohen(12), Shmuel Ravid(1), and Dan Ritter(2) (1) (2) Mobile Wireless Group, Intel Haifa, Israel Department of Electrical Engineering, Technion, Haifa, Israel

Outline • Design methodology flow and passives • Circuit implementation options • LNA measurements • Conclusions

Outline • Design methodology flow and passives • Circuit implementation options • LNA measurements • Conclusions

Motivation • How low can we get power consumption in a mm-wave LNA without compromising gain NF and size? • Typical LNA designed for 60 GHz showed a power of 20 m. W (@15 d. B gain). For a phase array with 30 -60 elements we end up with ~1 Watt ! • Power and size must go down for a full phase array system in commercial application

Motivation • How low can we get power consumption in a mm-wave LNA without compromising gain NF and size? • Typical LNA designed for 60 GHz showed a power of 20 m. W (@15 d. B gain). For a phase array with 30 -60 elements we end up with ~1 Watt ! • Power and size must go down for a full phase array system in commercial application

LNA Design Methodology 1. Choose the passive circuits and models 2. Choose the transistor width for optimized target 3. Choose best topology with optimized transistor width

LNA Design Methodology 1. Choose the passive circuits and models 2. Choose the transistor width for optimized target 3. Choose best topology with optimized transistor width

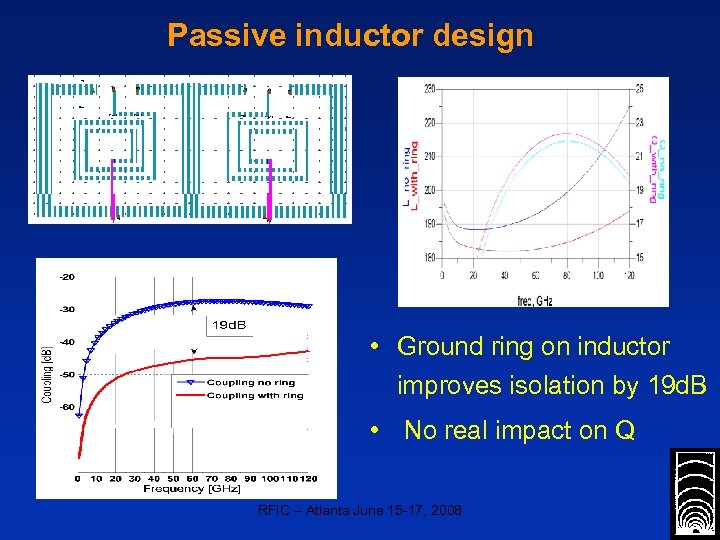

Passive inductor design • Ground ring on inductor improves isolation by 19 d. B • No real impact on Q RFIC – Atlanta June 15 -17, 2008

Passive inductor design • Ground ring on inductor improves isolation by 19 d. B • No real impact on Q RFIC – Atlanta June 15 -17, 2008

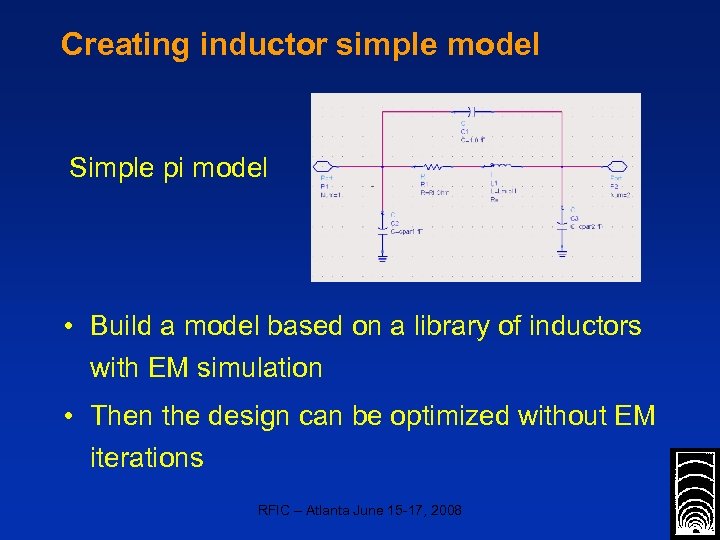

Creating inductor simple model Simple pi model • Build a model based on a library of inductors with EM simulation • Then the design can be optimized without EM iterations RFIC – Atlanta June 15 -17, 2008

Creating inductor simple model Simple pi model • Build a model based on a library of inductors with EM simulation • Then the design can be optimized without EM iterations RFIC – Atlanta June 15 -17, 2008

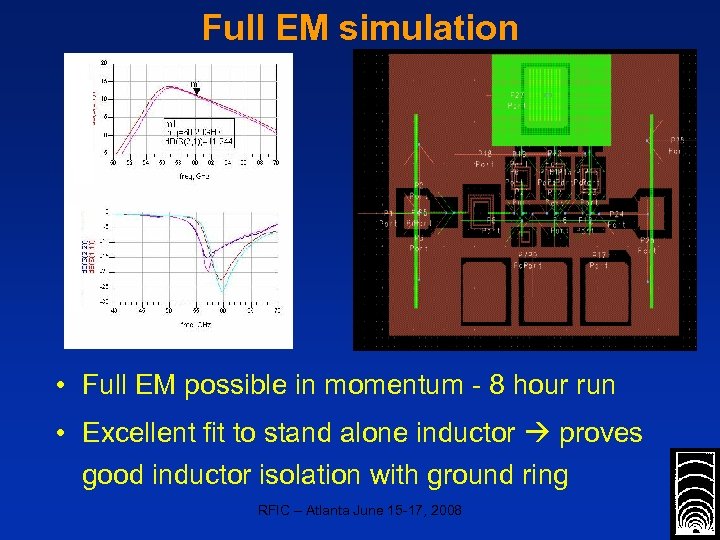

Full EM simulation • Full EM possible in momentum - 8 hour run • Excellent fit to stand alone inductor proves good inductor isolation with ground ring RFIC – Atlanta June 15 -17, 2008

Full EM simulation • Full EM possible in momentum - 8 hour run • Excellent fit to stand alone inductor proves good inductor isolation with ground ring RFIC – Atlanta June 15 -17, 2008

![Capacitors MIM cap Parasitic capacitance 200 pf Finger Cap [pf] Q Parasitic capacitance [pf] Capacitors MIM cap Parasitic capacitance 200 pf Finger Cap [pf] Q Parasitic capacitance [pf]](https://present5.com/presentation/33f42a362c3819b1c4147bb1224a289c/image-8.jpg) Capacitors MIM cap Parasitic capacitance 200 pf Finger Cap [pf] Q Parasitic capacitance [pf] Q • MIM cap Q~9 and finger cap Q >>10 • Finger cap has ~8% parasitic (after optimizing and using 2 -4 layers only) • Finger cap was chosen for the design RFIC – Atlanta June 15 -17, 2008

Capacitors MIM cap Parasitic capacitance 200 pf Finger Cap [pf] Q Parasitic capacitance [pf] Q • MIM cap Q~9 and finger cap Q >>10 • Finger cap has ~8% parasitic (after optimizing and using 2 -4 layers only) • Finger cap was chosen for the design RFIC – Atlanta June 15 -17, 2008

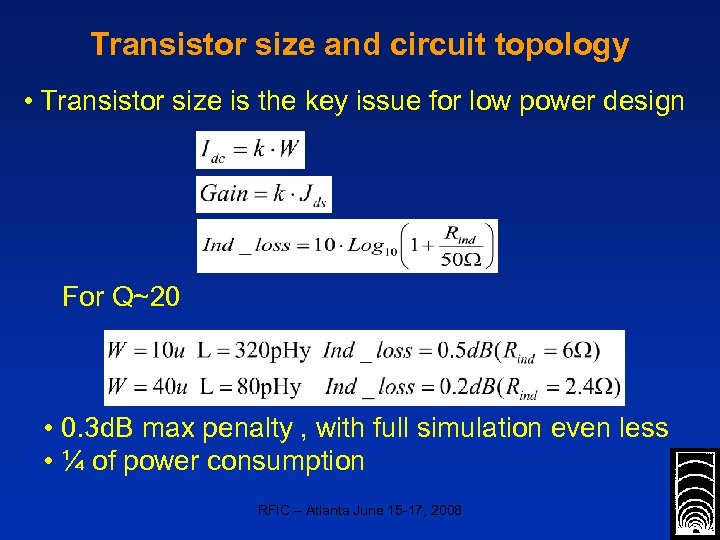

Transistor size and circuit topology • Transistor size is the key issue for low power design For Q~20 • 0. 3 d. B max penalty , with full simulation even less • ¼ of power consumption RFIC – Atlanta June 15 -17, 2008

Transistor size and circuit topology • Transistor size is the key issue for low power design For Q~20 • 0. 3 d. B max penalty , with full simulation even less • ¼ of power consumption RFIC – Atlanta June 15 -17, 2008

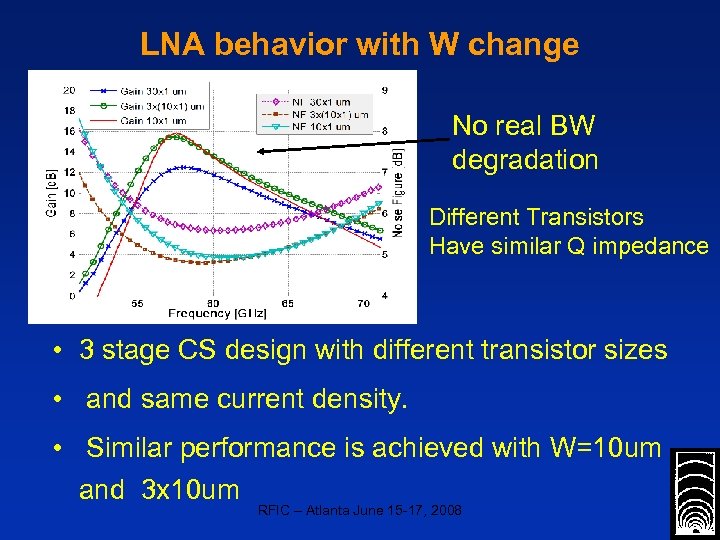

LNA behavior with W change No real BW degradation Different Transistors Have similar Q impedance • 3 stage CS design with different transistor sizes • and same current density. • Similar performance is achieved with W=10 um and 3 x 10 um RFIC – Atlanta June 15 -17, 2008

LNA behavior with W change No real BW degradation Different Transistors Have similar Q impedance • 3 stage CS design with different transistor sizes • and same current density. • Similar performance is achieved with W=10 um and 3 x 10 um RFIC – Atlanta June 15 -17, 2008

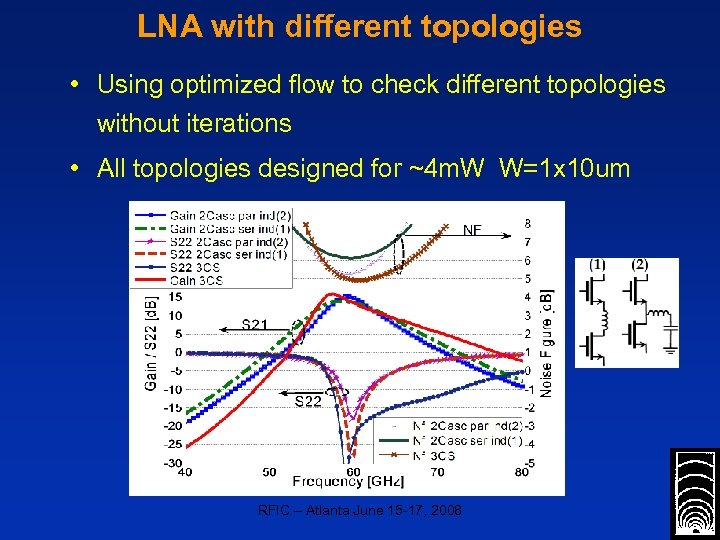

LNA with different topologies • Using optimized flow to check different topologies without iterations • All topologies designed for ~4 m. W W=1 x 10 um RFIC – Atlanta June 15 -17, 2008

LNA with different topologies • Using optimized flow to check different topologies without iterations • All topologies designed for ~4 m. W W=1 x 10 um RFIC – Atlanta June 15 -17, 2008

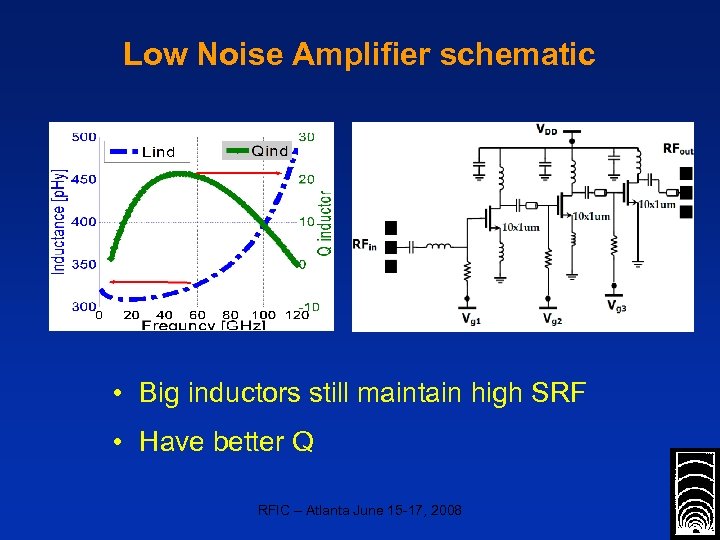

Low Noise Amplifier schematic • Big inductors still maintain high SRF • Have better Q RFIC – Atlanta June 15 -17, 2008

Low Noise Amplifier schematic • Big inductors still maintain high SRF • Have better Q RFIC – Atlanta June 15 -17, 2008

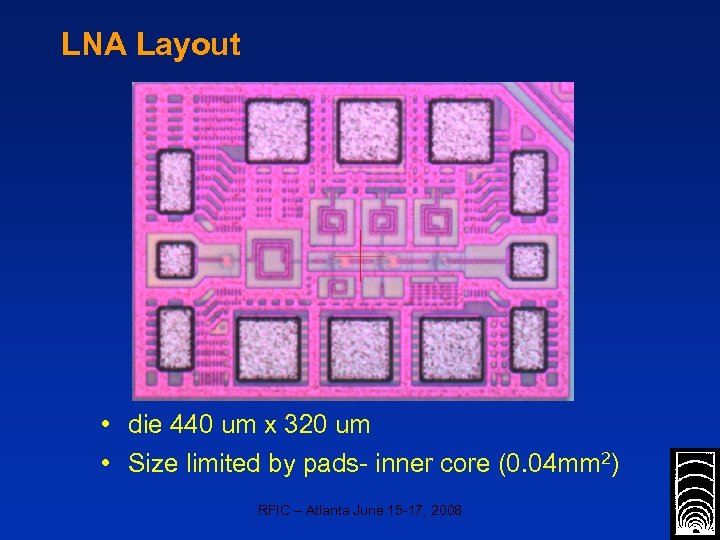

LNA Layout • die 440 um x 320 um • Size limited by pads- inner core (0. 04 mm 2) RFIC – Atlanta June 15 -17, 2008

LNA Layout • die 440 um x 320 um • Size limited by pads- inner core (0. 04 mm 2) RFIC – Atlanta June 15 -17, 2008

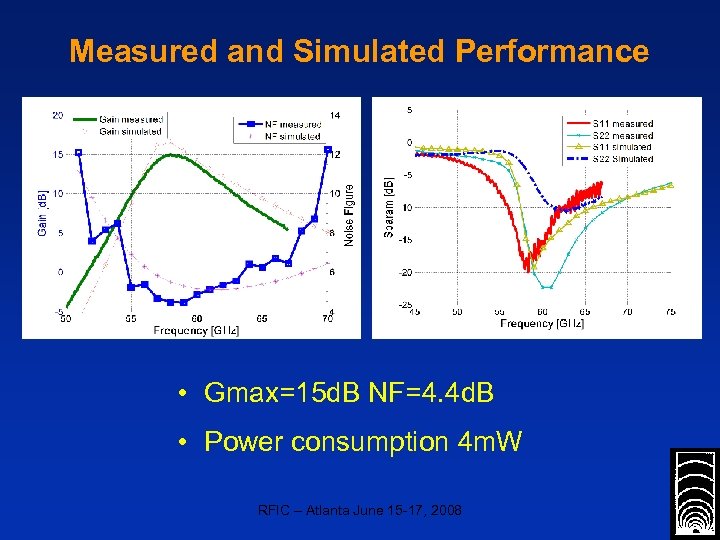

Measured and Simulated Performance • Gmax=15 d. B NF=4. 4 d. B • Power consumption 4 m. W RFIC – Atlanta June 15 -17, 2008

Measured and Simulated Performance • Gmax=15 d. B NF=4. 4 d. B • Power consumption 4 m. W RFIC – Atlanta June 15 -17, 2008

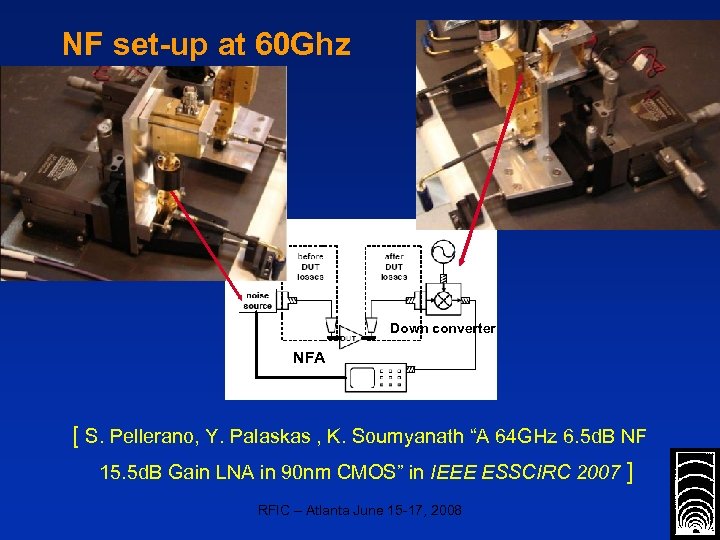

NF set-up at 60 Ghz Down converter NFA [ S. Pellerano, Y. Palaskas , K. Soumyanath “A 64 GHz 6. 5 d. B NF 15. 5 d. B Gain LNA in 90 nm CMOS” in IEEE ESSCIRC 2007 ] RFIC – Atlanta June 15 -17, 2008

NF set-up at 60 Ghz Down converter NFA [ S. Pellerano, Y. Palaskas , K. Soumyanath “A 64 GHz 6. 5 d. B NF 15. 5 d. B Gain LNA in 90 nm CMOS” in IEEE ESSCIRC 2007 ] RFIC – Atlanta June 15 -17, 2008

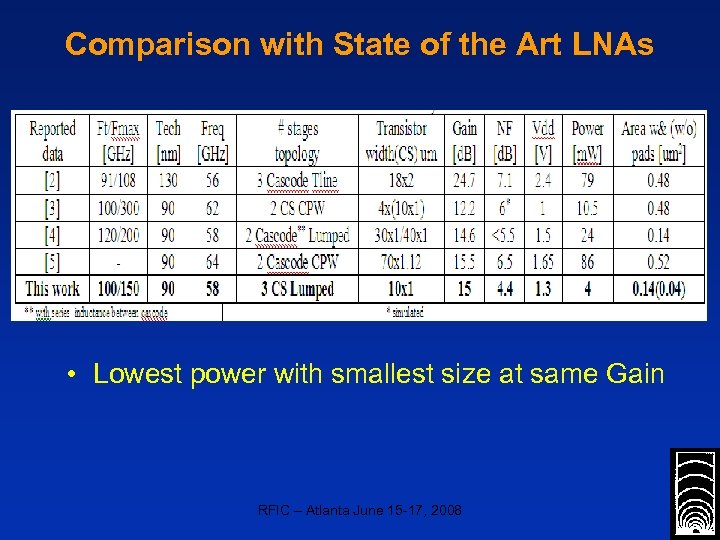

Comparison with State of the Art LNAs • Lowest power with smallest size at same Gain RFIC – Atlanta June 15 -17, 2008

Comparison with State of the Art LNAs • Lowest power with smallest size at same Gain RFIC – Atlanta June 15 -17, 2008

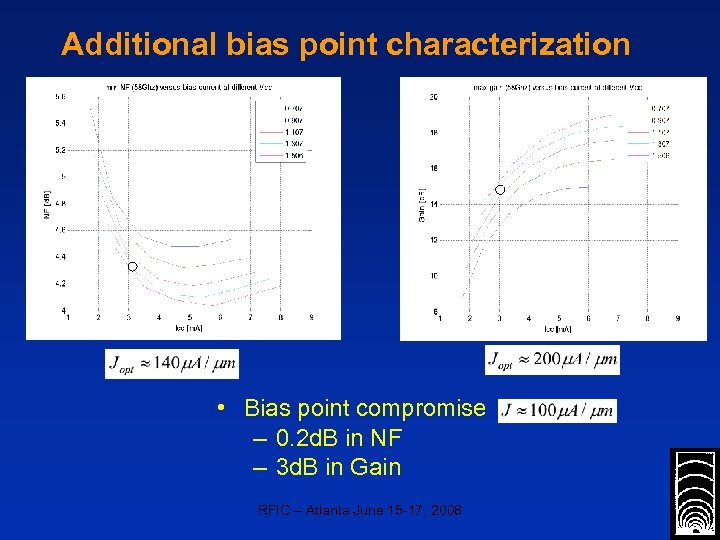

Additional bias point characterization • Bias point compromise – 0. 2 d. B in NF – 3 d. B in Gain RFIC – Atlanta June 15 -17, 2008

Additional bias point characterization • Bias point compromise – 0. 2 d. B in NF – 3 d. B in Gain RFIC – Atlanta June 15 -17, 2008

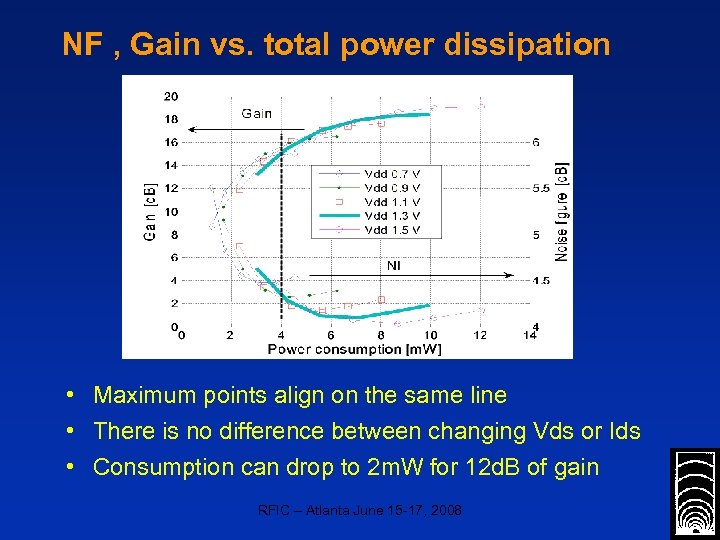

NF , Gain vs. total power dissipation • Maximum points align on the same line • There is no difference between changing Vds or Ids • Consumption can drop to 2 m. W for 12 d. B of gain RFIC – Atlanta June 15 -17, 2008

NF , Gain vs. total power dissipation • Maximum points align on the same line • There is no difference between changing Vds or Ids • Consumption can drop to 2 m. W for 12 d. B of gain RFIC – Atlanta June 15 -17, 2008

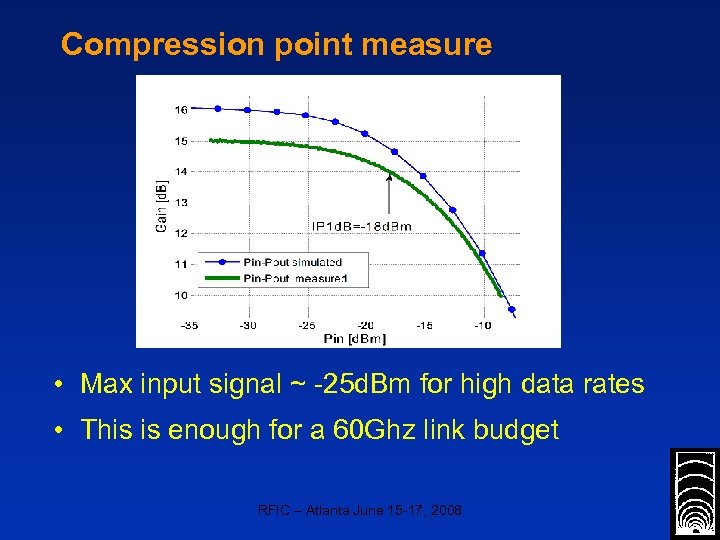

Compression point measure • Max input signal ~ -25 d. Bm for high data rates • This is enough for a 60 Ghz link budget RFIC – Atlanta June 15 -17, 2008

Compression point measure • Max input signal ~ -25 d. Bm for high data rates • This is enough for a 60 Ghz link budget RFIC – Atlanta June 15 -17, 2008

Conclusions • Fast design flow with lumped inductor and ground ring was created • The flow enabled a check of full circuits topology for a fair comparison on optimized results • The CS and small transistor size 1 x 10 um is the best tradeoff between power consumption Gain and NF. • A record power consumption of 4 m. W achieved with best NF of 4. 4 d. B 15 d. B gain and similar to smallest footprint published • Lumped inductor enabled smallest size and no additional design complexity RFIC – Atlanta June 15 -17, 2008

Conclusions • Fast design flow with lumped inductor and ground ring was created • The flow enabled a check of full circuits topology for a fair comparison on optimized results • The CS and small transistor size 1 x 10 um is the best tradeoff between power consumption Gain and NF. • A record power consumption of 4 m. W achieved with best NF of 4. 4 d. B 15 d. B gain and similar to smallest footprint published • Lumped inductor enabled smallest size and no additional design complexity RFIC – Atlanta June 15 -17, 2008

Thank You RFIC – Atlanta June 15 -17, 2008

Thank You RFIC – Atlanta June 15 -17, 2008

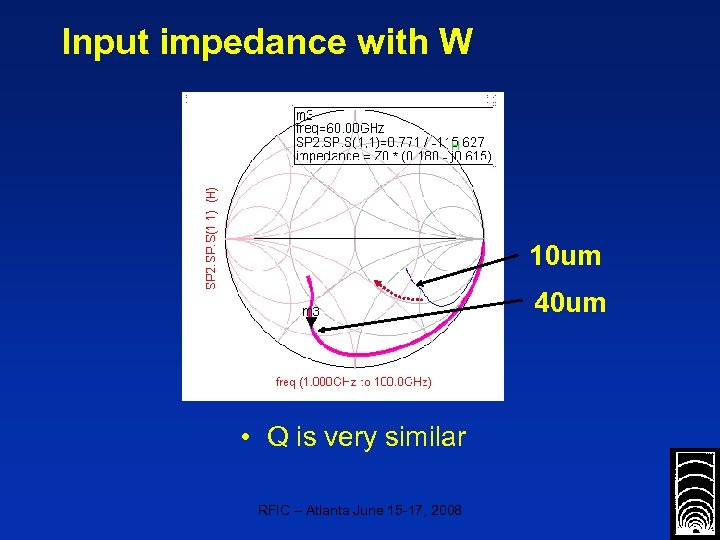

Input impedance with W 10 um 40 um • Q is very similar RFIC – Atlanta June 15 -17, 2008

Input impedance with W 10 um 40 um • Q is very similar RFIC – Atlanta June 15 -17, 2008