41d9bd8e7da010993a4620086968c706.ppt

- Количество слайдов: 21

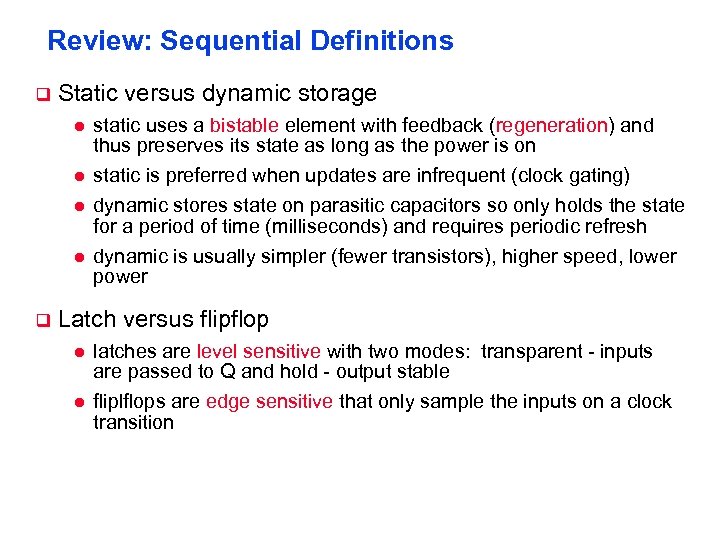

Review: Sequential Definitions q Static versus dynamic storage l l static uses a bistable element with feedback (regeneration) and thus preserves its state as long as the power is on static is preferred when updates are infrequent (clock gating) l l q dynamic stores state on parasitic capacitors so only holds the state for a period of time (milliseconds) and requires periodic refresh dynamic is usually simpler (fewer transistors), higher speed, lower power Latch versus flipflop l l latches are level sensitive with two modes: transparent - inputs are passed to Q and hold - output stable fliplflops are edge sensitive that only sample the inputs on a clock transition

Review: Sequential Definitions q Static versus dynamic storage l l static uses a bistable element with feedback (regeneration) and thus preserves its state as long as the power is on static is preferred when updates are infrequent (clock gating) l l q dynamic stores state on parasitic capacitors so only holds the state for a period of time (milliseconds) and requires periodic refresh dynamic is usually simpler (fewer transistors), higher speed, lower power Latch versus flipflop l l latches are level sensitive with two modes: transparent - inputs are passed to Q and hold - output stable fliplflops are edge sensitive that only sample the inputs on a clock transition

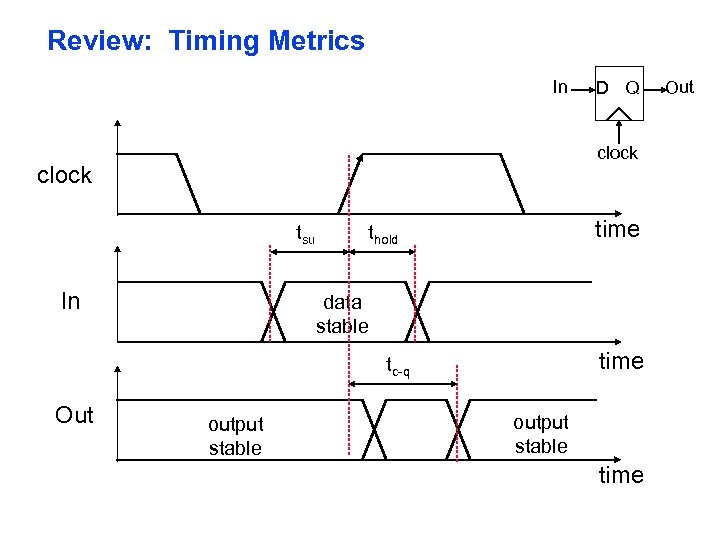

Review: Timing Metrics In clock tsu In time thold data stable time tc-q Out D Q output stable time Out

Review: Timing Metrics In clock tsu In time thold data stable time tc-q Out D Q output stable time Out

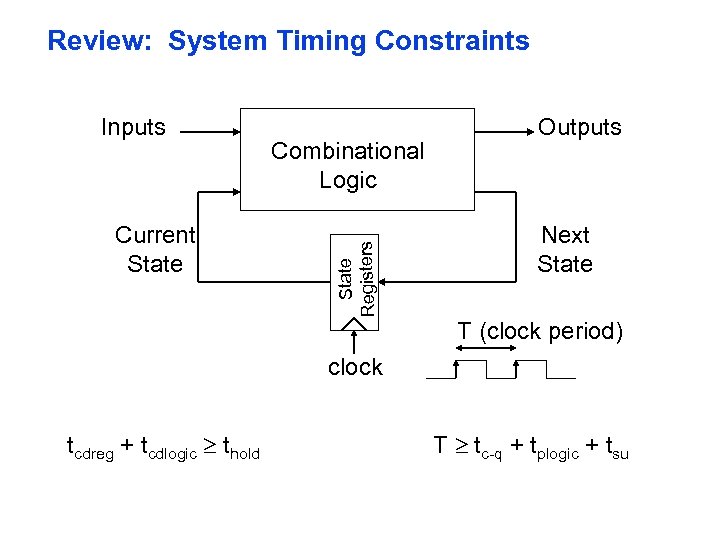

Review: System Timing Constraints Current State Combinational Logic State Registers Inputs Outputs Next State T (clock period) clock tcdreg + tcdlogic thold T tc-q + tplogic + tsu

Review: System Timing Constraints Current State Combinational Logic State Registers Inputs Outputs Next State T (clock period) clock tcdreg + tcdlogic thold T tc-q + tplogic + tsu

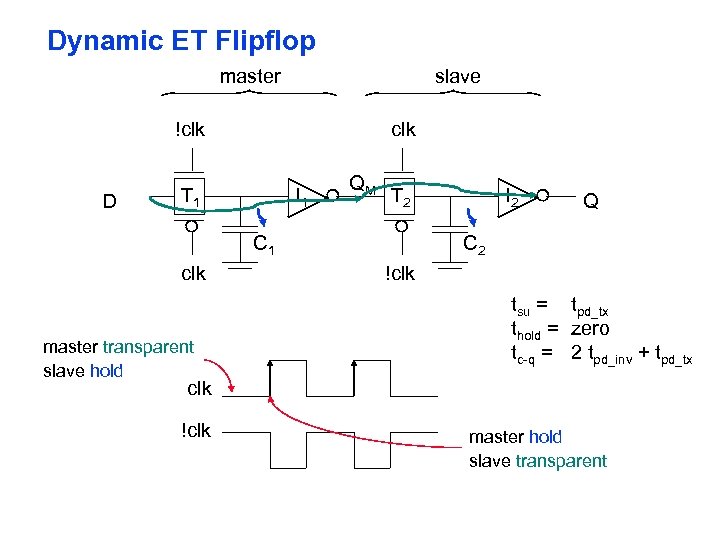

Dynamic ET Flipflop master slave !clk D clk T 1 I 1 QM T 2 C 1 clk master transparent slave hold I 2 Q C 2 !clk tsu = tpd_tx thold = zero tc-q = 2 tpd_inv + tpd_tx clk !clk master hold slave transparent

Dynamic ET Flipflop master slave !clk D clk T 1 I 1 QM T 2 C 1 clk master transparent slave hold I 2 Q C 2 !clk tsu = tpd_tx thold = zero tc-q = 2 tpd_inv + tpd_tx clk !clk master hold slave transparent

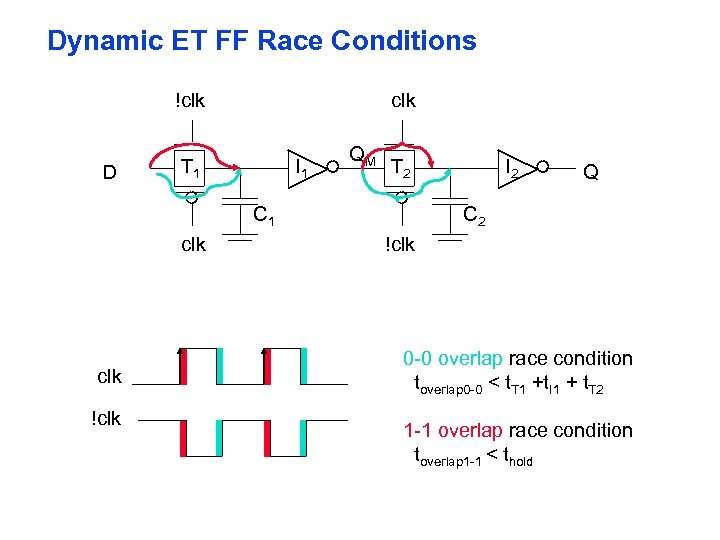

Dynamic ET FF Race Conditions !clk D clk T 1 I 1 QM T 2 C 1 clk !clk I 2 Q C 2 !clk 0 -0 overlap race condition toverlap 0 -0 < t. T 1 +t. I 1 + t. T 2 1 -1 overlap race condition toverlap 1 -1 < thold

Dynamic ET FF Race Conditions !clk D clk T 1 I 1 QM T 2 C 1 clk !clk I 2 Q C 2 !clk 0 -0 overlap race condition toverlap 0 -0 < t. T 1 +t. I 1 + t. T 2 1 -1 overlap race condition toverlap 1 -1 < thold

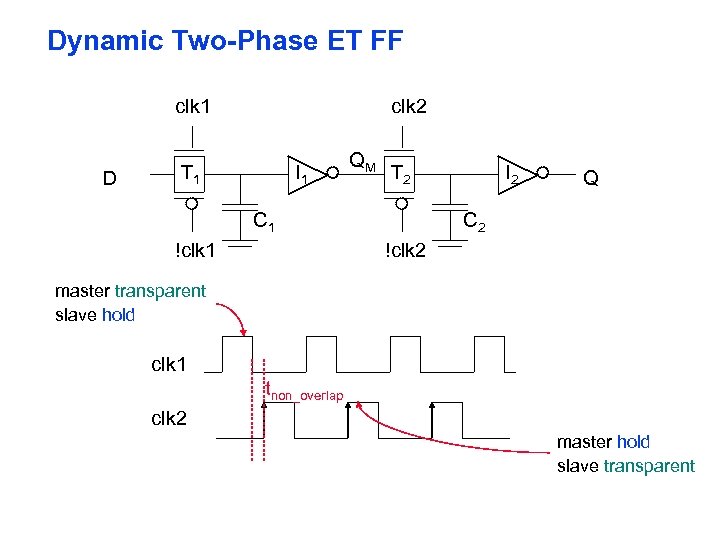

Dynamic Two-Phase ET FF clk 1 D clk 2 T 1 I 1 QM T 2 C 1 !clk 1 I 2 Q C 2 !clk 2 master transparent slave hold clk 1 tnon_overlap clk 2 master hold slave transparent

Dynamic Two-Phase ET FF clk 1 D clk 2 T 1 I 1 QM T 2 C 1 !clk 1 I 2 Q C 2 !clk 2 master transparent slave hold clk 1 tnon_overlap clk 2 master hold slave transparent

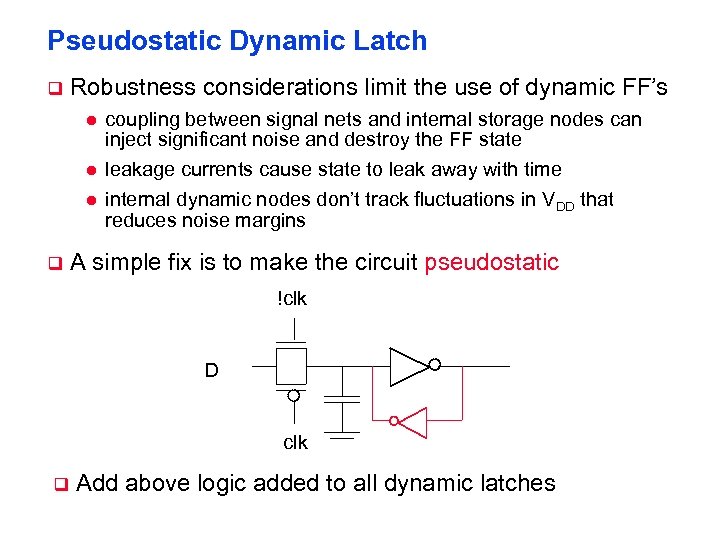

Pseudostatic Dynamic Latch q Robustness considerations limit the use of dynamic FF’s l l l q coupling between signal nets and internal storage nodes can inject significant noise and destroy the FF state leakage currents cause state to leak away with time internal dynamic nodes don’t track fluctuations in VDD that reduces noise margins A simple fix is to make the circuit pseudostatic !clk D clk q Add above logic added to all dynamic latches

Pseudostatic Dynamic Latch q Robustness considerations limit the use of dynamic FF’s l l l q coupling between signal nets and internal storage nodes can inject significant noise and destroy the FF state leakage currents cause state to leak away with time internal dynamic nodes don’t track fluctuations in VDD that reduces noise margins A simple fix is to make the circuit pseudostatic !clk D clk q Add above logic added to all dynamic latches

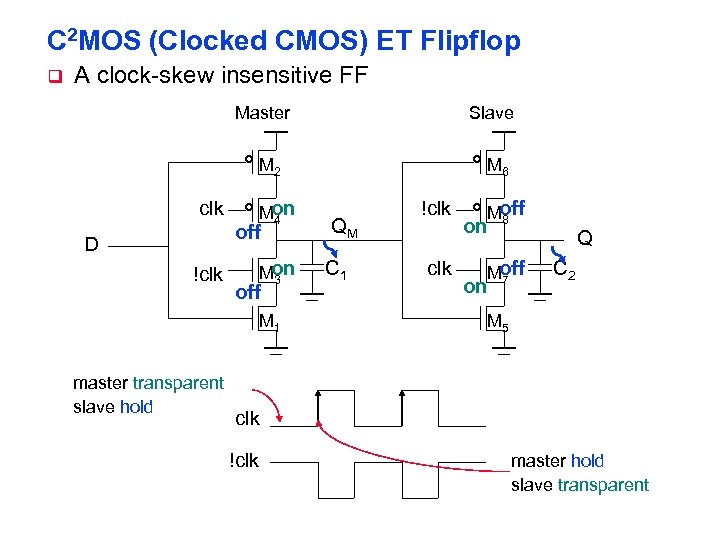

C 2 MOS (Clocked CMOS) ET Flipflop q A clock-skew insensitive FF Master Slave M 2 clk Mon 4 off D !clk Mon 3 off M 1 master transparent slave hold M 6 QM C 1 !clk Moff 8 on Q Moff 7 on C 2 M 5 clk !clk master hold slave transparent

C 2 MOS (Clocked CMOS) ET Flipflop q A clock-skew insensitive FF Master Slave M 2 clk Mon 4 off D !clk Mon 3 off M 1 master transparent slave hold M 6 QM C 1 !clk Moff 8 on Q Moff 7 on C 2 M 5 clk !clk master hold slave transparent

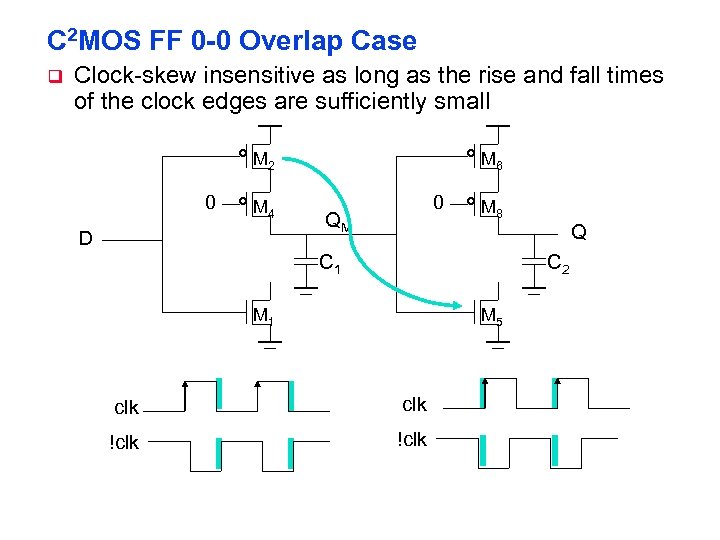

C 2 MOS FF 0 -0 Overlap Case q Clock-skew insensitive as long as the rise and fall times of the clock edges are sufficiently small M 2 0 M 4 D M 6 0 QM M 8 Q C 1 C 2 M 1 M 5 clk !clk

C 2 MOS FF 0 -0 Overlap Case q Clock-skew insensitive as long as the rise and fall times of the clock edges are sufficiently small M 2 0 M 4 D M 6 0 QM M 8 Q C 1 C 2 M 1 M 5 clk !clk

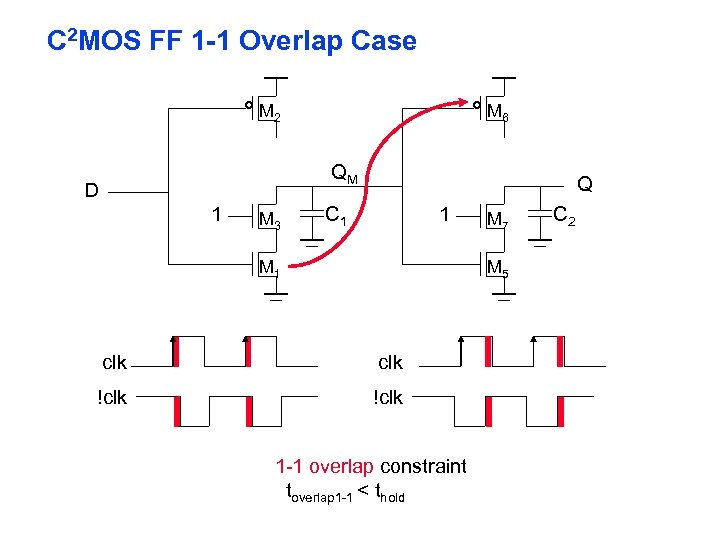

C 2 MOS FF 1 -1 Overlap Case M 2 M 6 QM D 1 M 3 Q C 1 1 M 7 M 5 clk !clk 1 -1 overlap constraint toverlap 1 -1 < thold C 2

C 2 MOS FF 1 -1 Overlap Case M 2 M 6 QM D 1 M 3 Q C 1 1 M 7 M 5 clk !clk 1 -1 overlap constraint toverlap 1 -1 < thold C 2

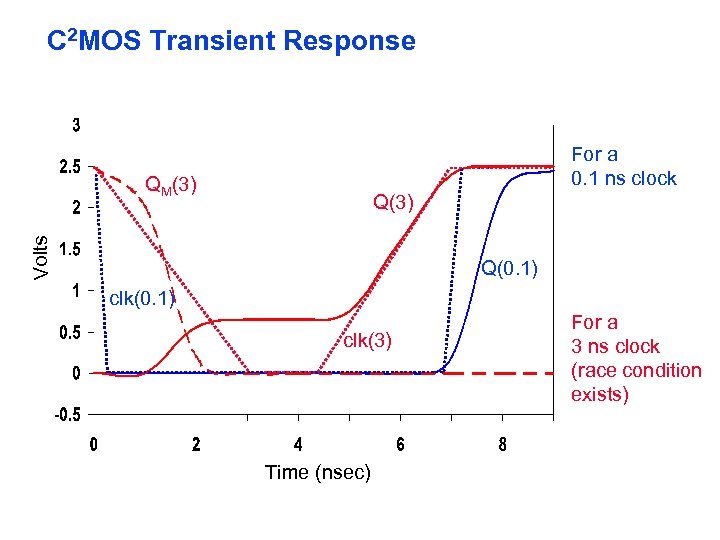

C 2 MOS Transient Response For a 0. 1 ns clock QM(3) Volts Q(3) Q(0. 1) clk(3) Time (nsec) For a 3 ns clock (race condition exists)

C 2 MOS Transient Response For a 0. 1 ns clock QM(3) Volts Q(3) Q(0. 1) clk(3) Time (nsec) For a 3 ns clock (race condition exists)

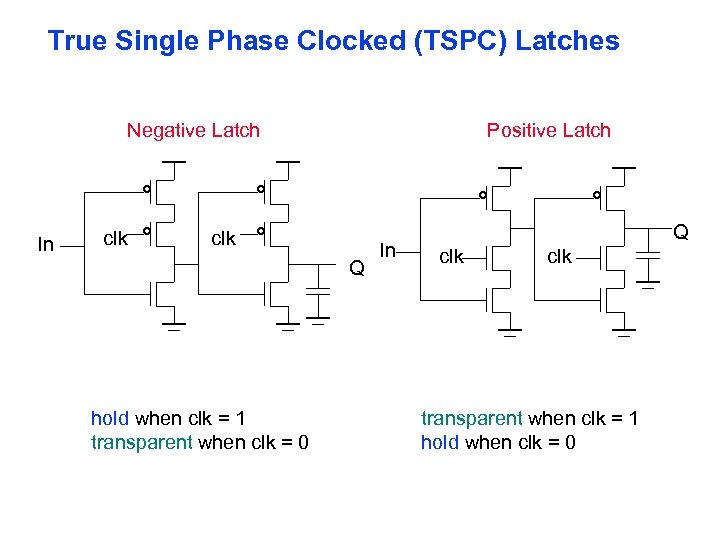

True Single Phase Clocked (TSPC) Latches Negative Latch In clk Positive Latch clk Q hold when clk = 1 transparent when clk = 0 In Q clk transparent when clk = 1 hold when clk = 0

True Single Phase Clocked (TSPC) Latches Negative Latch In clk Positive Latch clk Q hold when clk = 1 transparent when clk = 0 In Q clk transparent when clk = 1 hold when clk = 0

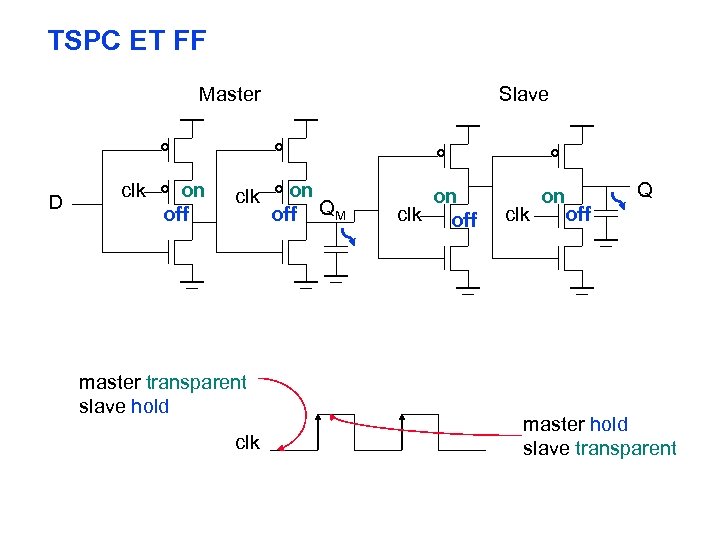

TSPC ET FF Master D clk on off clk master transparent slave hold clk Slave on off QM on clk off Q master hold slave transparent

TSPC ET FF Master D clk on off clk master transparent slave hold clk Slave on off QM on clk off Q master hold slave transparent

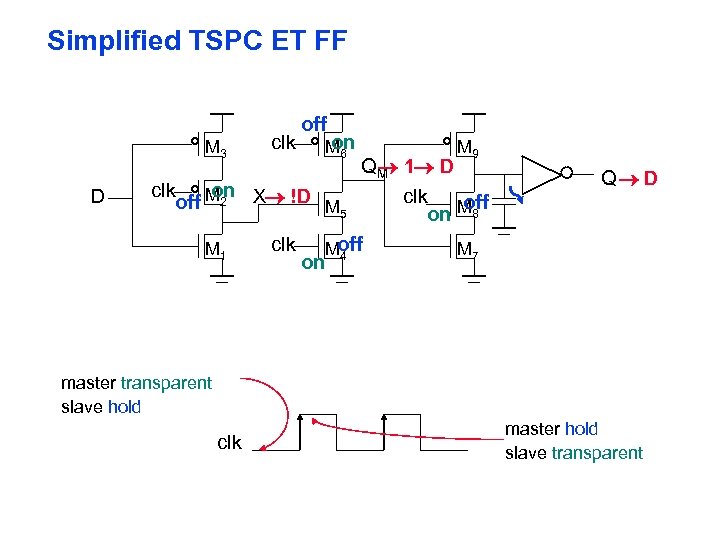

Simplified TSPC ET FF M 3 D clk off on M 6 M 9 QM 1 D clk M 2 X !D on clk off M 5 on M 8 clk Moff M 1 M 7 4 on Q D master transparent slave hold clk master hold slave transparent

Simplified TSPC ET FF M 3 D clk off on M 6 M 9 QM 1 D clk M 2 X !D on clk off M 5 on M 8 clk Moff M 1 M 7 4 on Q D master transparent slave hold clk master hold slave transparent

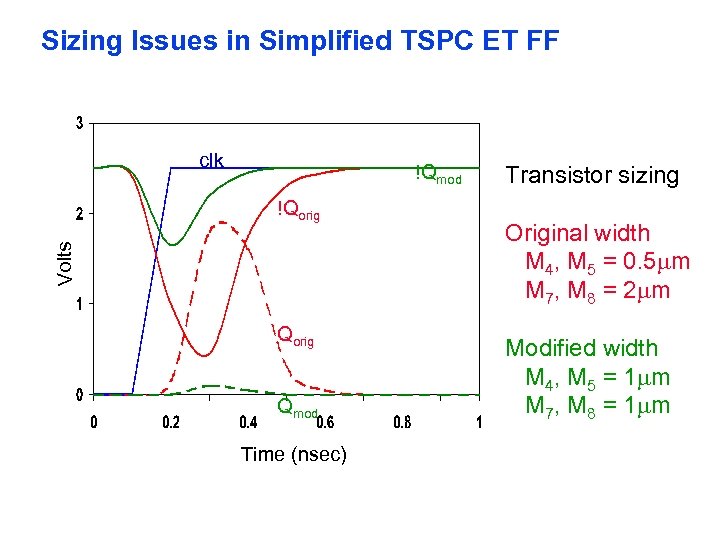

Sizing Issues in Simplified TSPC ET FF clk !Qmod Volts !Qorig Qmod Time (nsec) Transistor sizing Original width M 4, M 5 = 0. 5 m M 7, M 8 = 2 m Modified width M 4, M 5 = 1 m M 7, M 8 = 1 m

Sizing Issues in Simplified TSPC ET FF clk !Qmod Volts !Qorig Qmod Time (nsec) Transistor sizing Original width M 4, M 5 = 0. 5 m M 7, M 8 = 2 m Modified width M 4, M 5 = 1 m M 7, M 8 = 1 m

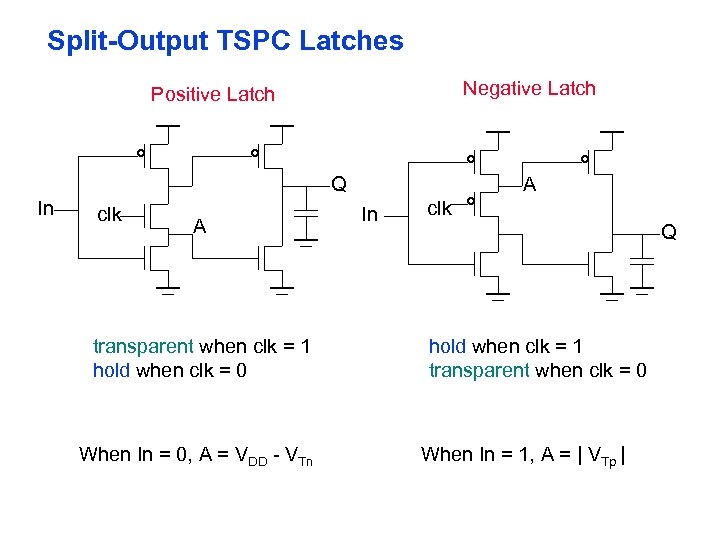

Split-Output TSPC Latches Negative Latch Positive Latch Q In clk A transparent when clk = 1 hold when clk = 0 When In = 0, A = VDD - VTn A In clk Q hold when clk = 1 transparent when clk = 0 When In = 1, A = | VTp |

Split-Output TSPC Latches Negative Latch Positive Latch Q In clk A transparent when clk = 1 hold when clk = 0 When In = 0, A = VDD - VTn A In clk Q hold when clk = 1 transparent when clk = 0 When In = 1, A = | VTp |

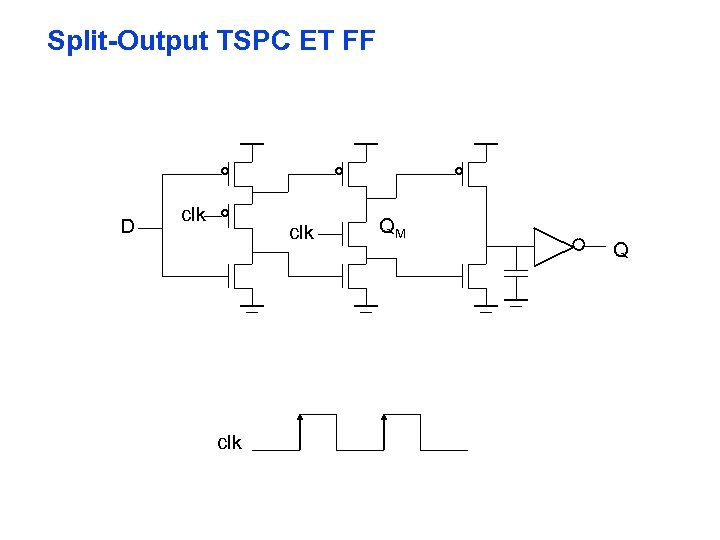

Split-Output TSPC ET FF D clk clk QM Q

Split-Output TSPC ET FF D clk clk QM Q

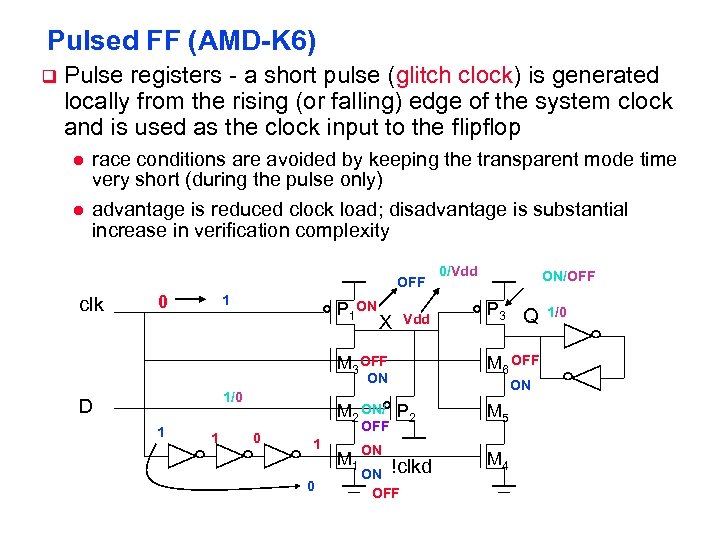

Pulsed FF (AMD-K 6) q Pulse registers - a short pulse (glitch clock) is generated locally from the rising (or falling) edge of the system clock and is used as the clock input to the flipflop l race conditions are avoided by keeping the transparent mode time very short (during the pulse only) l advantage is reduced clock load; disadvantage is substantial increase in verification complexity OFF clk 0 1 P 1 ON X Vdd M 3 OFF ON 1/0 D 1 1 M 2 ON/ P 2 0 OFF 1 0 M 1 ON ON !clkd OFF 0/Vdd ON/OFF P 3 Q M 6 OFF ON M 5 M 4 1/0

Pulsed FF (AMD-K 6) q Pulse registers - a short pulse (glitch clock) is generated locally from the rising (or falling) edge of the system clock and is used as the clock input to the flipflop l race conditions are avoided by keeping the transparent mode time very short (during the pulse only) l advantage is reduced clock load; disadvantage is substantial increase in verification complexity OFF clk 0 1 P 1 ON X Vdd M 3 OFF ON 1/0 D 1 1 M 2 ON/ P 2 0 OFF 1 0 M 1 ON ON !clkd OFF 0/Vdd ON/OFF P 3 Q M 6 OFF ON M 5 M 4 1/0

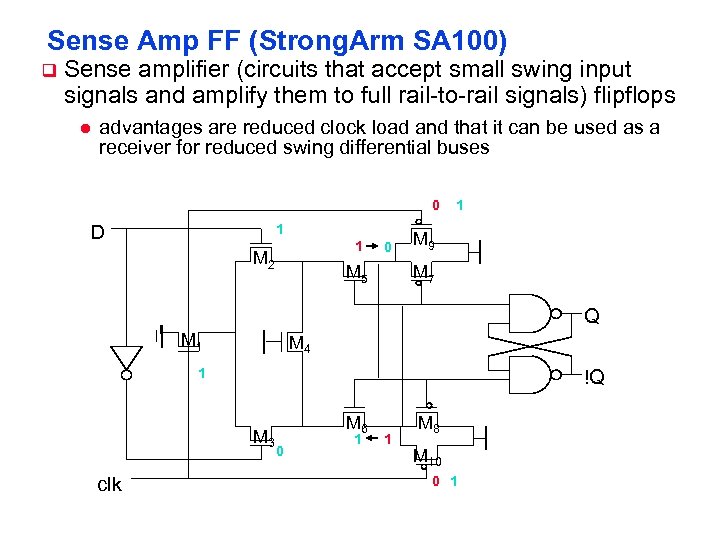

Sense Amp FF (Strong. Arm SA 100) q Sense amplifier (circuits that accept small swing input signals and amplify them to full rail-to-rail signals) flipflops l advantages are reduced clock load and that it can be used as a receiver for reduced swing differential buses 0 D 1 1 M 2 0 M 5 1 M 9 M 7 Q M 1 M 4 1 !Q M 3 clk M 6 0 1 1 M 8 M 10 0 1

Sense Amp FF (Strong. Arm SA 100) q Sense amplifier (circuits that accept small swing input signals and amplify them to full rail-to-rail signals) flipflops l advantages are reduced clock load and that it can be used as a receiver for reduced swing differential buses 0 D 1 1 M 2 0 M 5 1 M 9 M 7 Q M 1 M 4 1 !Q M 3 clk M 6 0 1 1 M 8 M 10 0 1

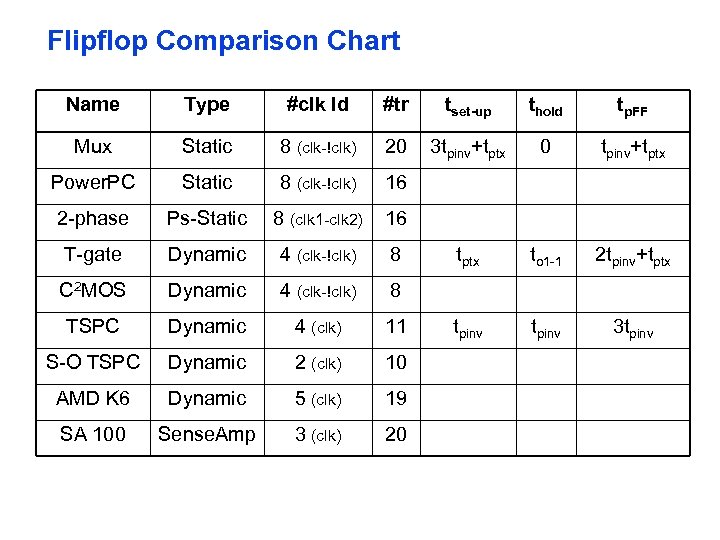

Flipflop Comparison Chart Name Type #clk ld #tr tset-up thold tp. FF Mux Static 8 (clk-!clk) 20 3 tpinv+tptx 0 tpinv+tptx Power. PC Static 8 (clk-!clk) 16 2 -phase Ps-Static 8 (clk 1 -clk 2) 16 T-gate Dynamic 4 (clk-!clk) 8 tptx to 1 -1 2 tpinv+tptx C 2 MOS Dynamic 4 (clk-!clk) 8 TSPC Dynamic 4 (clk) 11 tpinv 3 tpinv S-O TSPC Dynamic 2 (clk) 10 AMD K 6 Dynamic 5 (clk) 19 SA 100 Sense. Amp 3 (clk) 20

Flipflop Comparison Chart Name Type #clk ld #tr tset-up thold tp. FF Mux Static 8 (clk-!clk) 20 3 tpinv+tptx 0 tpinv+tptx Power. PC Static 8 (clk-!clk) 16 2 -phase Ps-Static 8 (clk 1 -clk 2) 16 T-gate Dynamic 4 (clk-!clk) 8 tptx to 1 -1 2 tpinv+tptx C 2 MOS Dynamic 4 (clk-!clk) 8 TSPC Dynamic 4 (clk) 11 tpinv 3 tpinv S-O TSPC Dynamic 2 (clk) 10 AMD K 6 Dynamic 5 (clk) 19 SA 100 Sense. Amp 3 (clk) 20

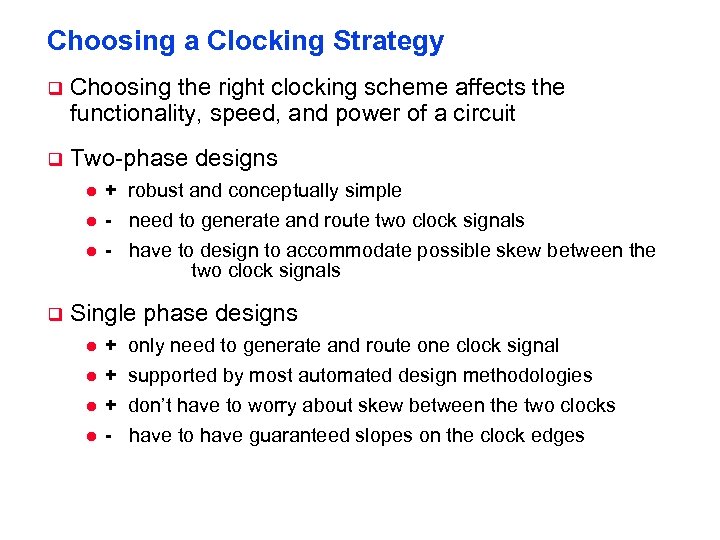

Choosing a Clocking Strategy q Choosing the right clocking scheme affects the functionality, speed, and power of a circuit q Two-phase designs l l - need to generate and route two clock signals l q + robust and conceptually simple - have to design to accommodate possible skew between the two clock signals Single phase designs l l + + + - only need to generate and route one clock signal supported by most automated design methodologies don’t have to worry about skew between the two clocks have to have guaranteed slopes on the clock edges

Choosing a Clocking Strategy q Choosing the right clocking scheme affects the functionality, speed, and power of a circuit q Two-phase designs l l - need to generate and route two clock signals l q + robust and conceptually simple - have to design to accommodate possible skew between the two clock signals Single phase designs l l + + + - only need to generate and route one clock signal supported by most automated design methodologies don’t have to worry about skew between the two clocks have to have guaranteed slopes on the clock edges