053df6dd7745842b8c282855c42df00e.ppt

- Количество слайдов: 55

Review: Hardware Support for Memory Disambiguation: The Simple Version

Quick Recap: Explicit Register Renaming

Review: Advantages of Explicit Renaming

Independent “Fetch” unit

Branches must be resolved quickly

Relationship between precise interrupts and speculation:

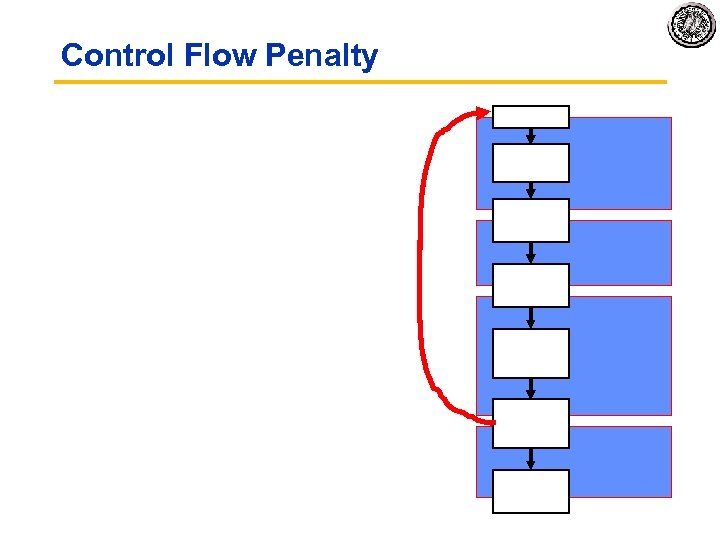

Control Flow Penalty

MIPS Branches and Jumps

Branch Penalties in Modern Pipelines

Reducing Control Flow Penalty

Administrative

Branch Prediction

Case for Branch Prediction when Issue N instructions per clock cycle

Static Branch Prediction

Predicated Execution

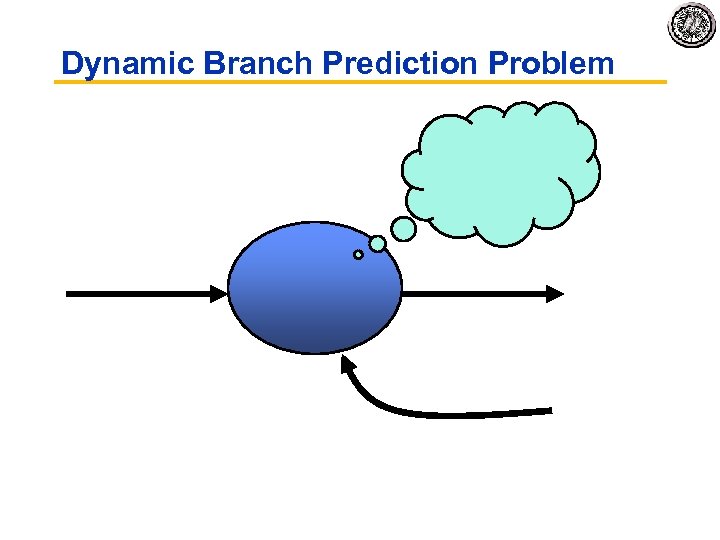

Dynamic Branch Prediction Problem

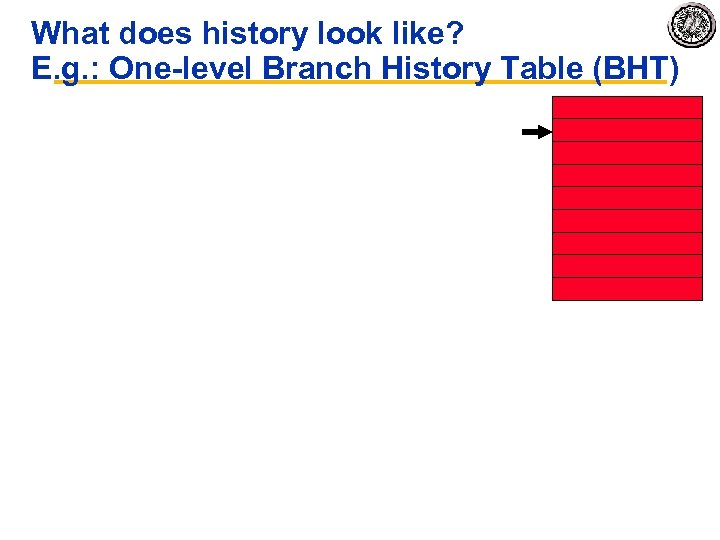

What does history look like? E. g. : One-level Branch History Table (BHT)

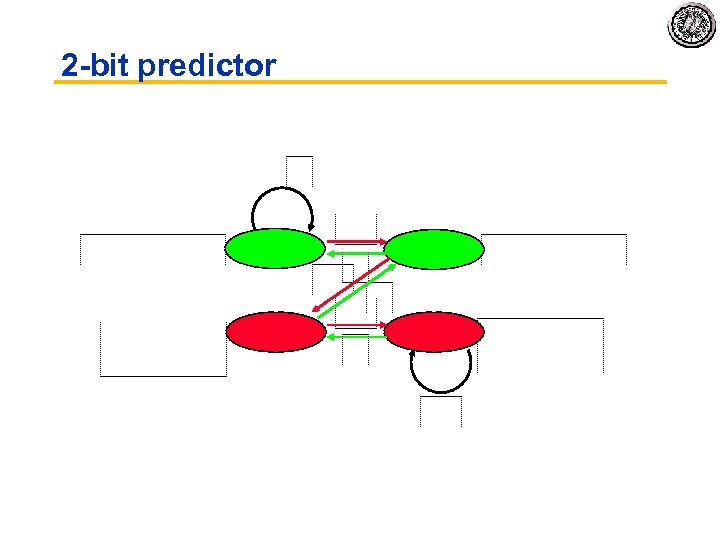

2 -bit predictor

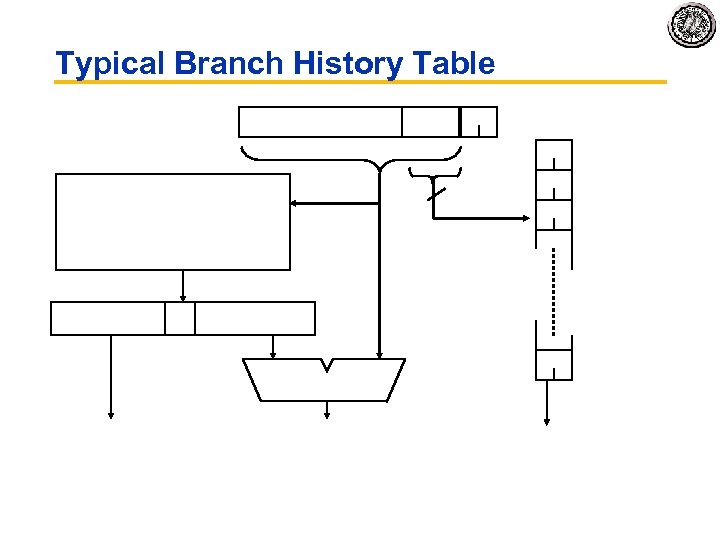

Typical Branch History Table

Pipeline considerations for BHT

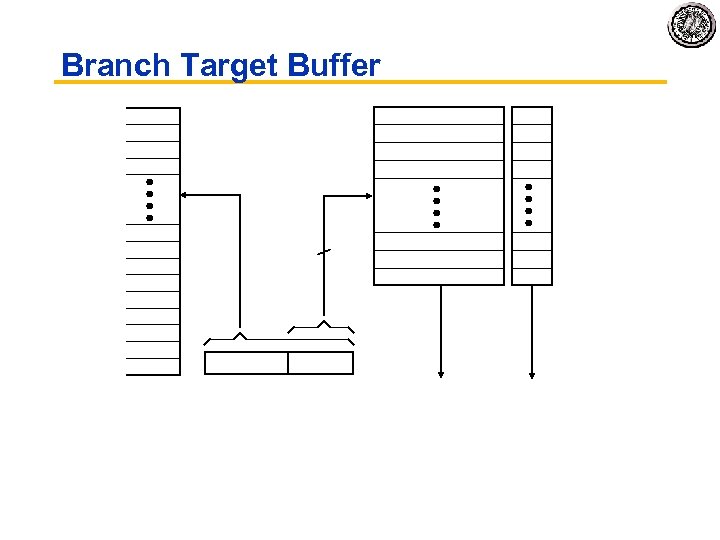

Branch Target Buffer

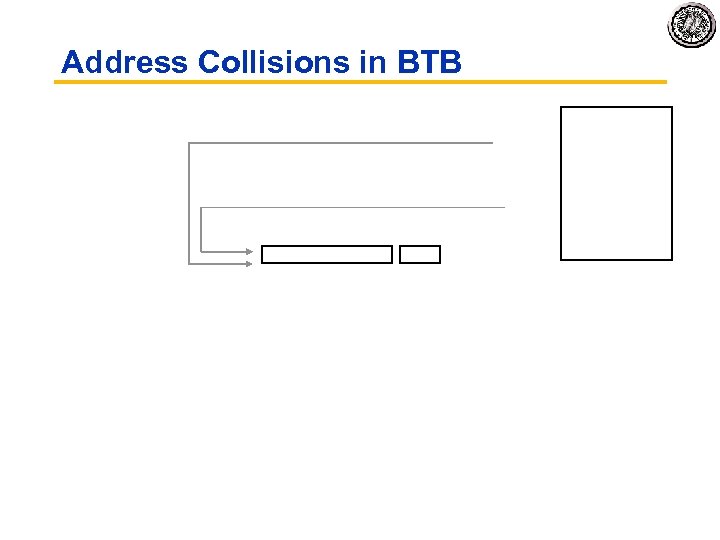

Address Collisions in BTB

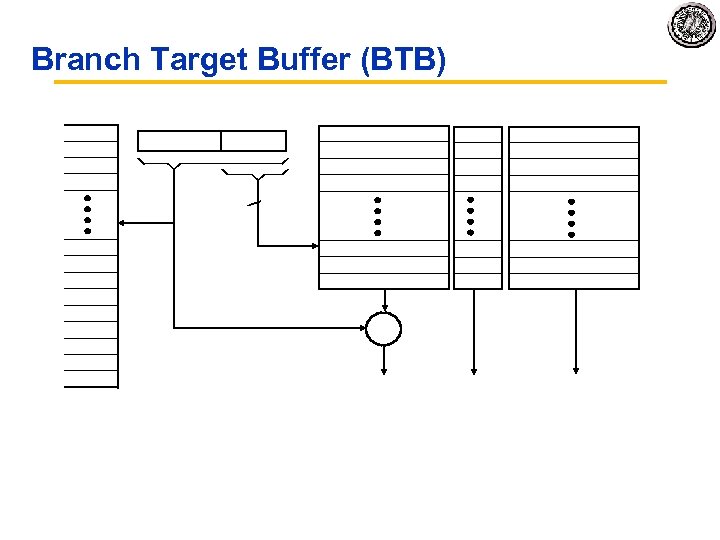

Branch Target Buffer (BTB)

Consulting BTB Before Decoding

Combining BTB and BHT

Uses of Jump Register (JR)

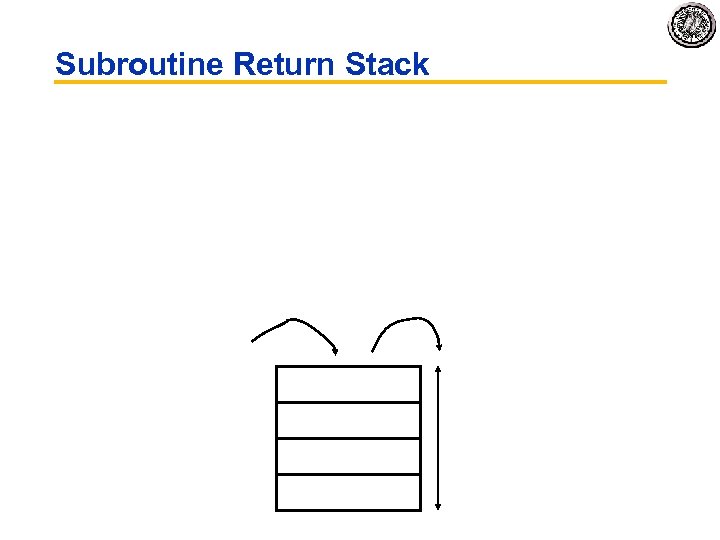

Subroutine Return Stack

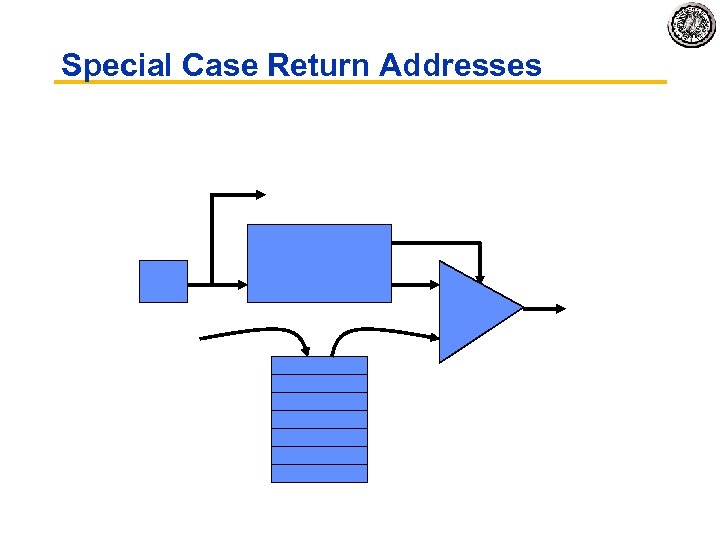

Special Case Return Addresses

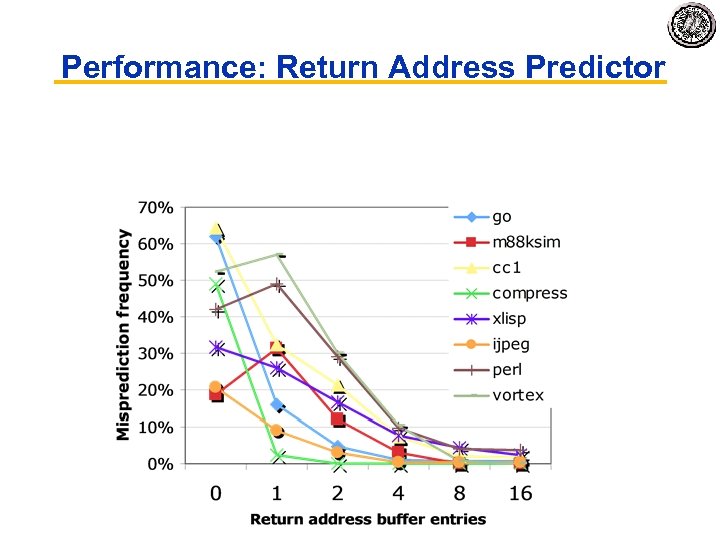

Performance: Return Address Predictor

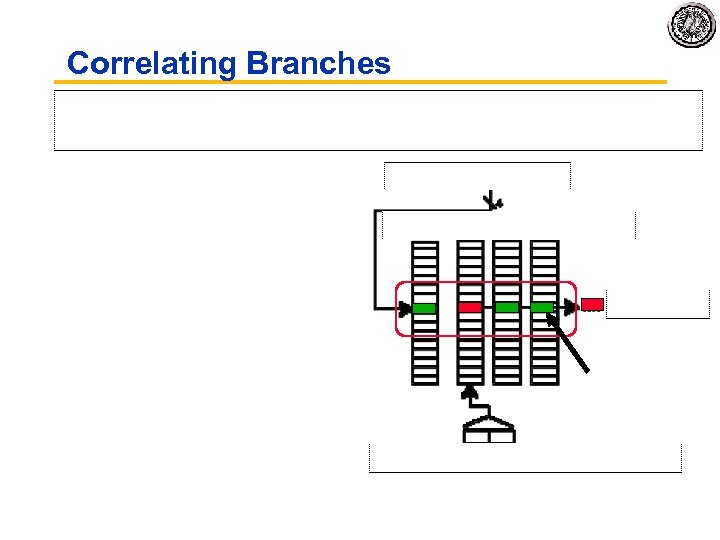

Correlating Branches

Correlating Branches

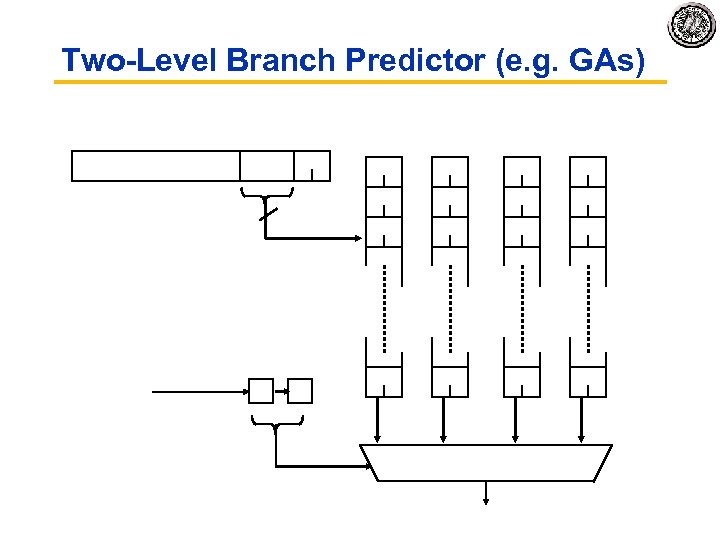

Two-Level Branch Predictor (e. g. GAs)

What are Important Metrics?

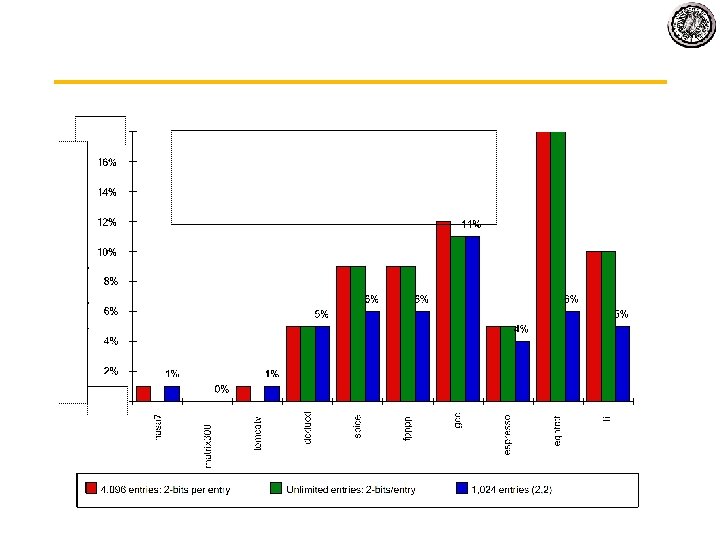

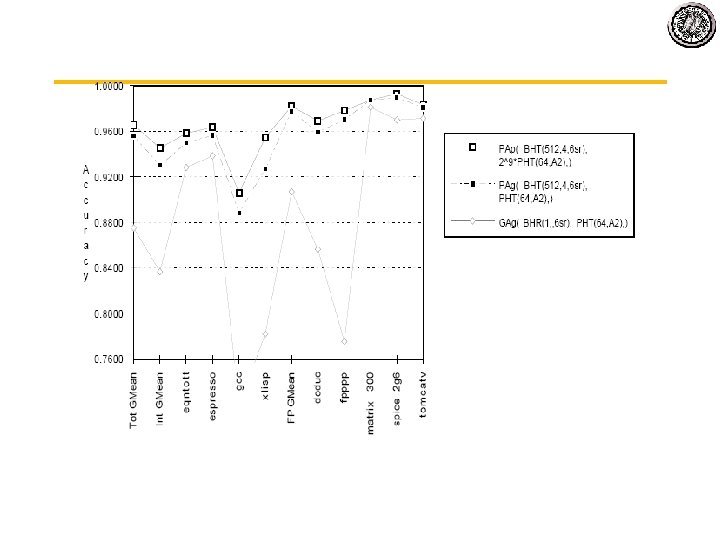

BHT Accuracy

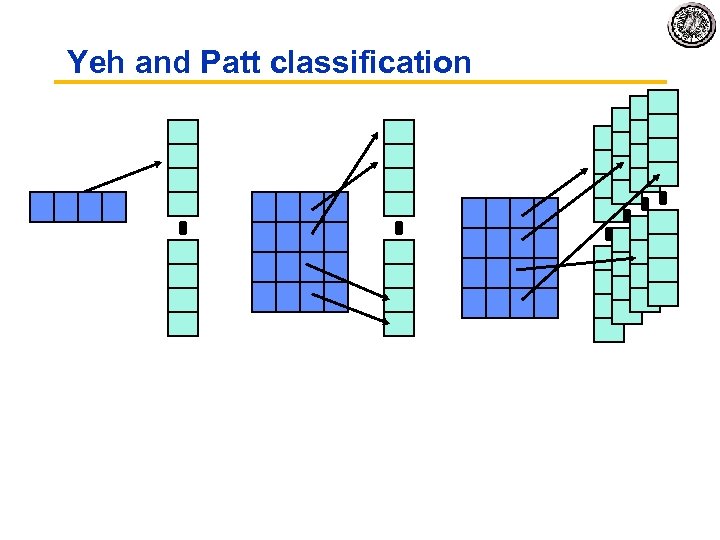

Yeh and Patt classification

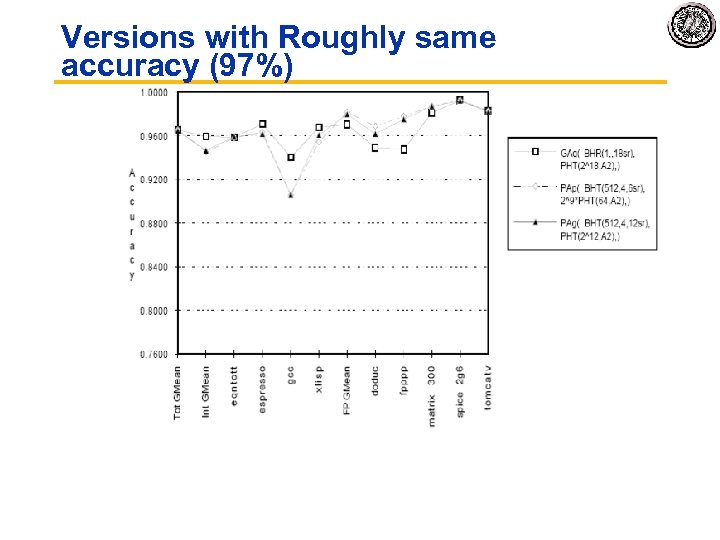

Versions with Roughly same accuracy (97%)

Why doesn’t GAg do better?

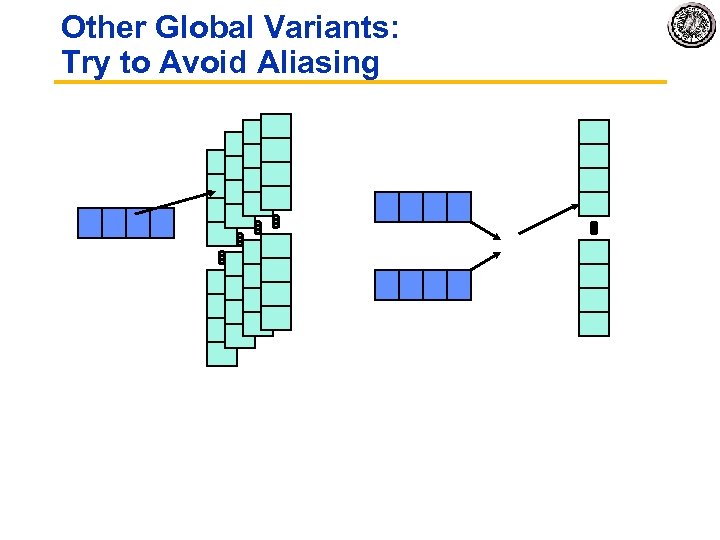

Other Global Variants: Try to Avoid Aliasing

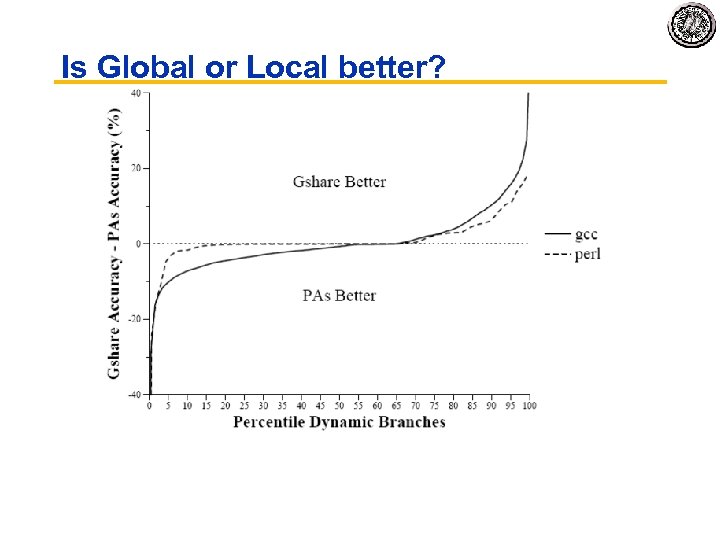

Is Global or Local better?

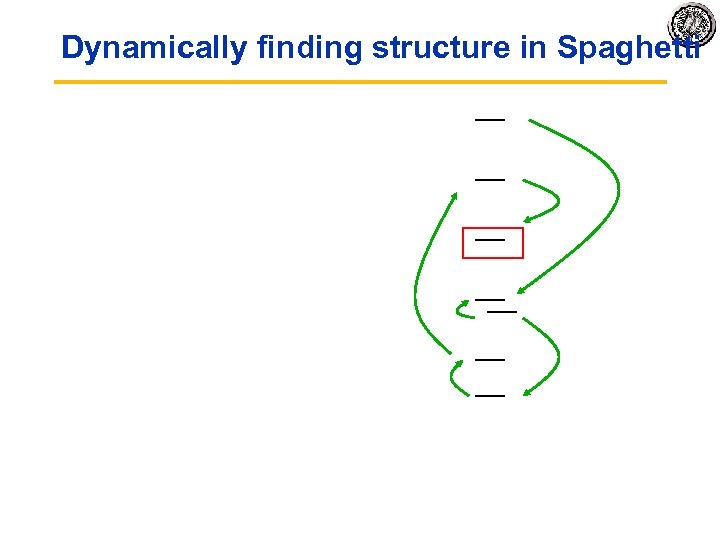

Dynamically finding structure in Spaghetti

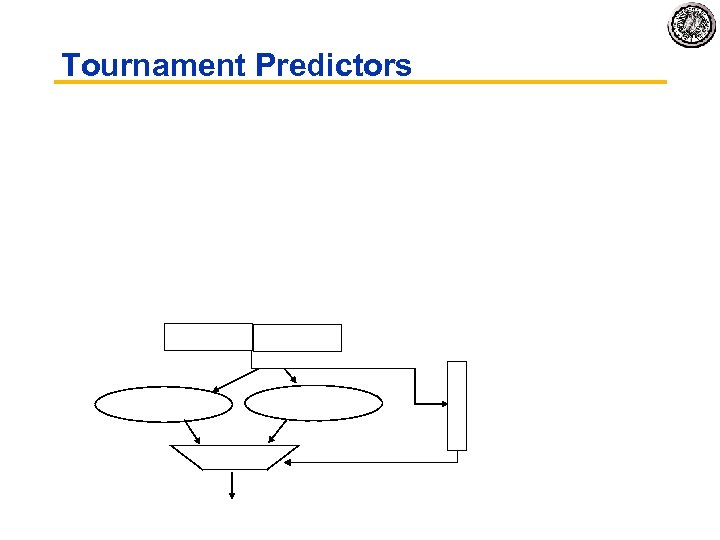

Tournament Predictors

Tournament Predictor in Alpha 21264

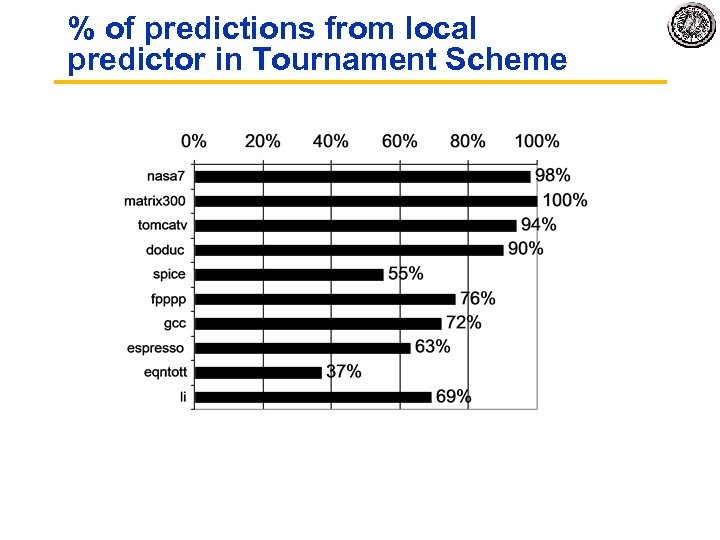

% of predictions from local predictor in Tournament Scheme

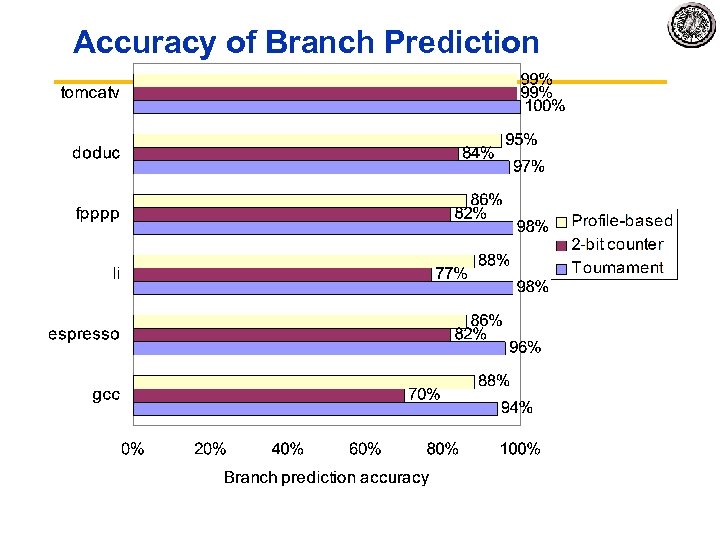

Accuracy of Branch Prediction

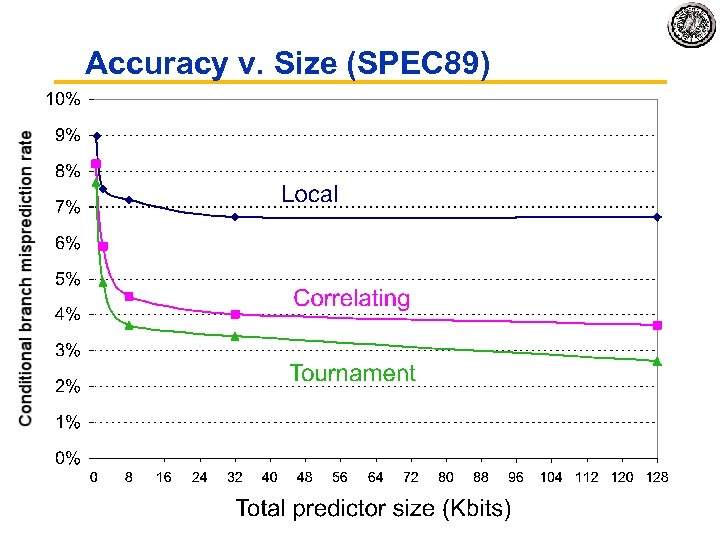

Accuracy v. Size (SPEC 89)

Pitfall: Sometimes bigger and dumber is better

Speculating Both Directions

Conclusion

053df6dd7745842b8c282855c42df00e.ppt