75be2a940dda10e91dfcb99eaaf57932.ppt

- Количество слайдов: 16

Real-Time System-On-A-Chip Emulation

Real-Time System-On-A-Chip Emulation

1. 2. 3. 4. 5. 6. Introduction Describing SOC Designs System-Level Design Flow SOC Implemantation Paths-Emulation and ASICs Case Study : A 1 Mbps Narrow-Band Transmission System Conclusions

1. 2. 3. 4. 5. 6. Introduction Describing SOC Designs System-Level Design Flow SOC Implemantation Paths-Emulation and ASICs Case Study : A 1 Mbps Narrow-Band Transmission System Conclusions

4. SOC Implemantation Paths. Emulation and ASICs o Berkeley Emulation Engine n n o Direct Mapped Designs and the BEE Architecture BEE Emulation Prototyping Concepts for BEE Hardware Emulation Designing for ASICs

4. SOC Implemantation Paths. Emulation and ASICs o Berkeley Emulation Engine n n o Direct Mapped Designs and the BEE Architecture BEE Emulation Prototyping Concepts for BEE Hardware Emulation Designing for ASICs

Berkeley Emulation Engine o o Provide a large, unified, real-time emulation flatform for data-flow-centric designs Rapid prototyping n o Using an existing H/W framework to speed up design process Systhesis-based design method n n n The emulation runs at the same speed as the final product Design discription can be utilized in emulation environmant and final ASIC implementation Maintaining cycle-accurate

Berkeley Emulation Engine o o Provide a large, unified, real-time emulation flatform for data-flow-centric designs Rapid prototyping n o Using an existing H/W framework to speed up design process Systhesis-based design method n n n The emulation runs at the same speed as the final product Design discription can be utilized in emulation environmant and final ASIC implementation Maintaining cycle-accurate

Direct Mapped Designs and the BEE Architecture 1 o o o Direct Mapping – top level element already explicitly specity the H/W architecture with cycle-accurate behavior H/W architecture FPGA and ASIC implementations are functionally same Suited for high level of parallelism and low-power with stringent perfomance specifications

Direct Mapped Designs and the BEE Architecture 1 o o o Direct Mapping – top level element already explicitly specity the H/W architecture with cycle-accurate behavior H/W architecture FPGA and ASIC implementations are functionally same Suited for high level of parallelism and low-power with stringent perfomance specifications

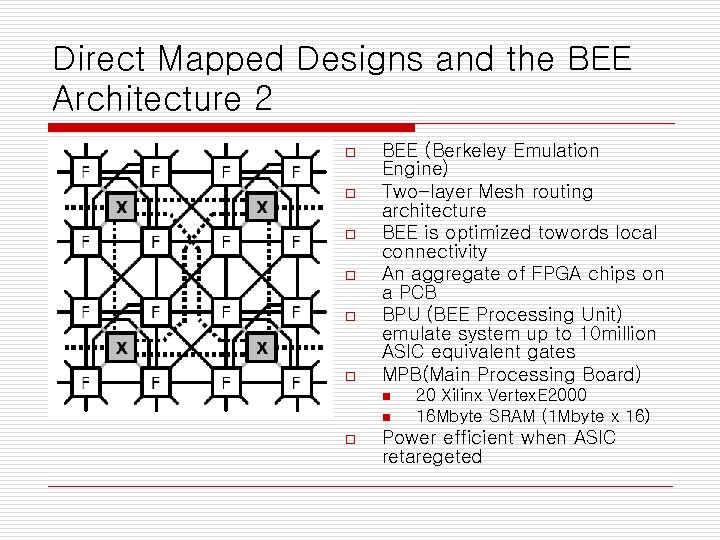

Direct Mapped Designs and the BEE Architecture 2 o o o BEE (Berkeley Emulation Engine) Two-layer Mesh routing architecture BEE is optimized towords local connectivity An aggregate of FPGA chips on a PCB BPU (BEE Processing Unit) emulate system up to 10 million ASIC equivalent gates MPB(Main Processing Board) n n o 20 Xilinx Vertex. E 2000 16 Mbyte SRAM (1 Mbyte x 16) Power efficient when ASIC retaregeted

Direct Mapped Designs and the BEE Architecture 2 o o o BEE (Berkeley Emulation Engine) Two-layer Mesh routing architecture BEE is optimized towords local connectivity An aggregate of FPGA chips on a PCB BPU (BEE Processing Unit) emulate system up to 10 million ASIC equivalent gates MPB(Main Processing Board) n n o 20 Xilinx Vertex. E 2000 16 Mbyte SRAM (1 Mbyte x 16) Power efficient when ASIC retaregeted

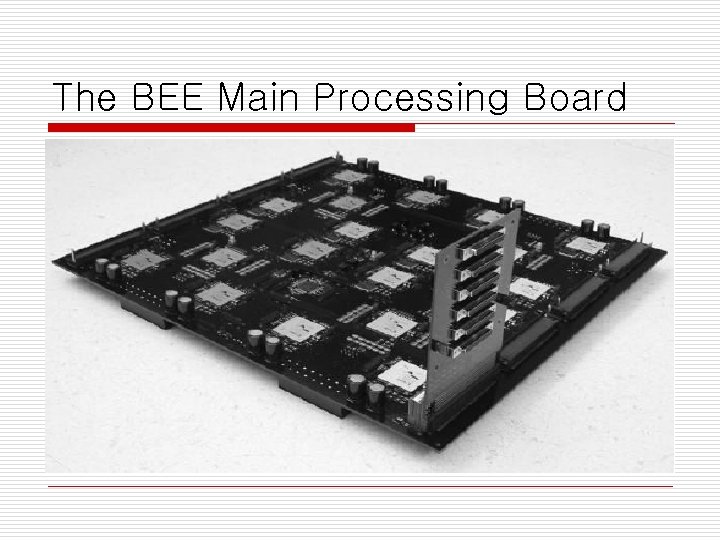

The BEE Main Processing Board

The BEE Main Processing Board

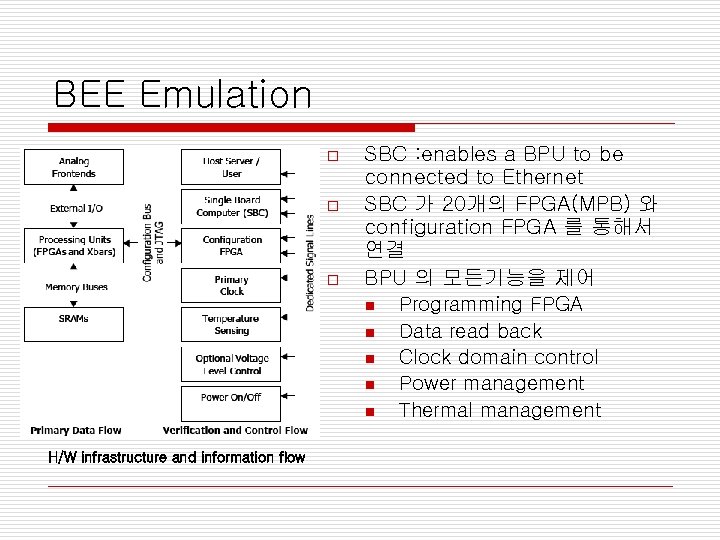

BEE Emulation o o o H/W infrastructure and information flow SBC : enables a BPU to be connected to Ethernet SBC 가 20개의 FPGA(MPB) 와 configuration FPGA 를 통해서 연결 BPU 의 모든기능을 제어 n Programming FPGA n Data read back n Clock domain control n Power management n Thermal management

BEE Emulation o o o H/W infrastructure and information flow SBC : enables a BPU to be connected to Ethernet SBC 가 20개의 FPGA(MPB) 와 configuration FPGA 를 통해서 연결 BPU 의 모든기능을 제어 n Programming FPGA n Data read back n Clock domain control n Power management n Thermal management

Prototyping Concepts for BEE Hardware Emulation o o o Functional and cycle-level emulaton 과 filnal ASIC implementation 은 동등한 과정 Concept-oriented prototyping BEE excels in real-time in-circuit verification

Prototyping Concepts for BEE Hardware Emulation o o o Functional and cycle-level emulaton 과 filnal ASIC implementation 은 동등한 과정 Concept-oriented prototyping BEE excels in real-time in-circuit verification

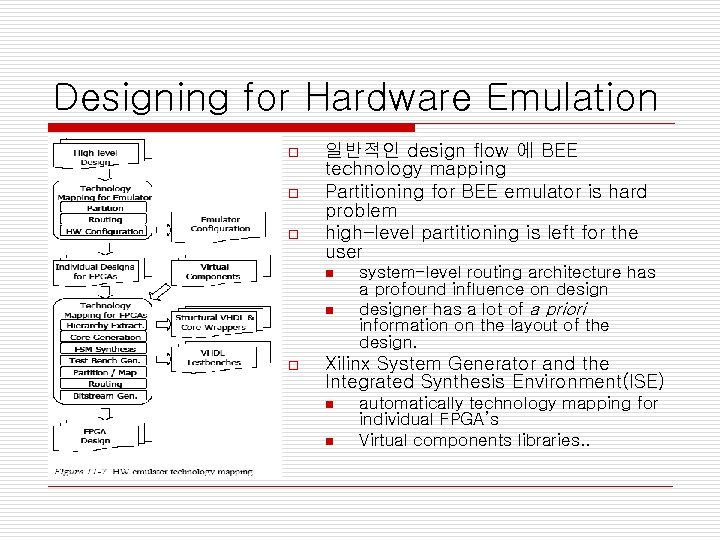

Designing for Hardware Emulation o o o 일반적인 design flow 에 BEE technology mapping Partitioning for BEE emulator is hard problem high-level partitioning is left for the user n n o system-level routing architecture has a profound influence on designer has a lot of a priori information on the layout of the design. Xilinx System Generator and the Integrated Synthesis Environment(ISE) n n automatically technology mapping for individual FPGA’s Virtual components libraries. .

Designing for Hardware Emulation o o o 일반적인 design flow 에 BEE technology mapping Partitioning for BEE emulator is hard problem high-level partitioning is left for the user n n o system-level routing architecture has a profound influence on designer has a lot of a priori information on the layout of the design. Xilinx System Generator and the Integrated Synthesis Environment(ISE) n n automatically technology mapping for individual FPGA’s Virtual components libraries. .

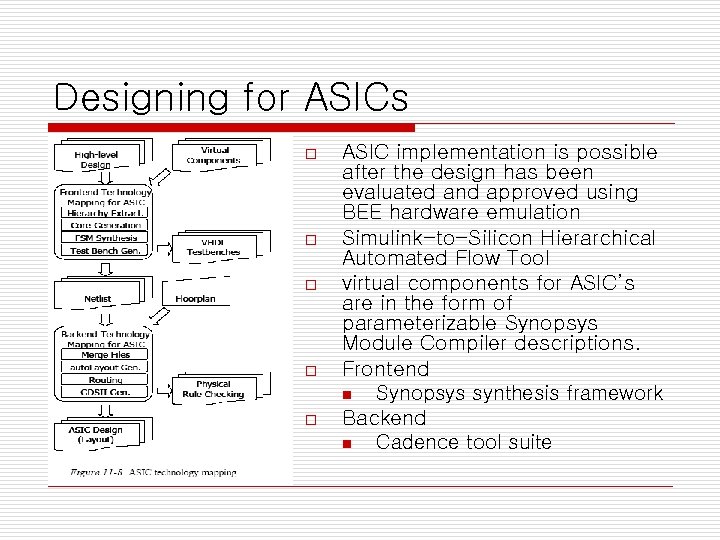

Designing for ASICs o o o ASIC implementation is possible after the design has been evaluated and approved using BEE hardware emulation Simulink-to-Silicon Hierarchical Automated Flow Tool virtual components for ASIC’s are in the form of parameterizable Synopsys Module Compiler descriptions. Frontend n Synopsys synthesis framework Backend n Cadence tool suite

Designing for ASICs o o o ASIC implementation is possible after the design has been evaluated and approved using BEE hardware emulation Simulink-to-Silicon Hierarchical Automated Flow Tool virtual components for ASIC’s are in the form of parameterizable Synopsys Module Compiler descriptions. Frontend n Synopsys synthesis framework Backend n Cadence tool suite

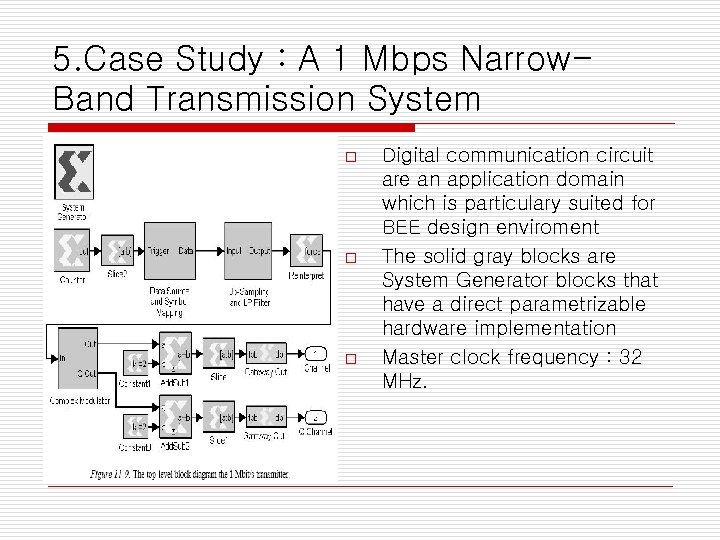

5. Case Study : A 1 Mbps Narrow. Band Transmission System o o o Digital communication circuit are an application domain which is particulary suited for BEE design enviroment The solid gray blocks are System Generator blocks that have a direct parametrizable hardware implementation Master clock frequency : 32 MHz.

5. Case Study : A 1 Mbps Narrow. Band Transmission System o o o Digital communication circuit are an application domain which is particulary suited for BEE design enviroment The solid gray blocks are System Generator blocks that have a direct parametrizable hardware implementation Master clock frequency : 32 MHz.

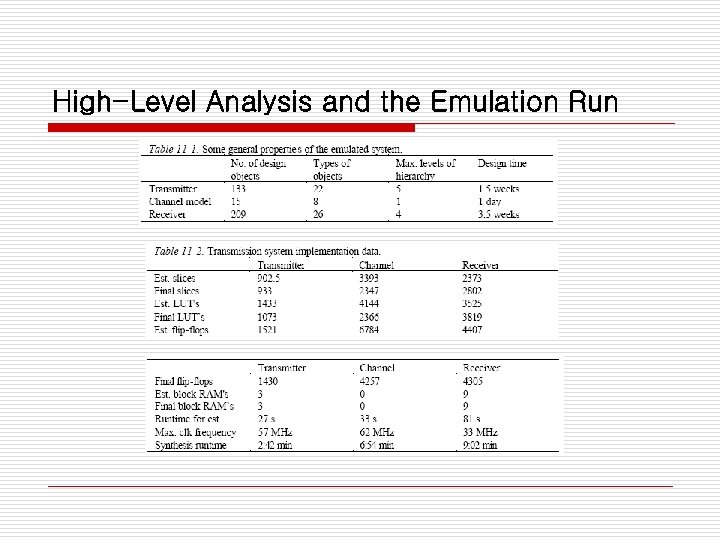

High-Level Analysis and the Emulation Run

High-Level Analysis and the Emulation Run

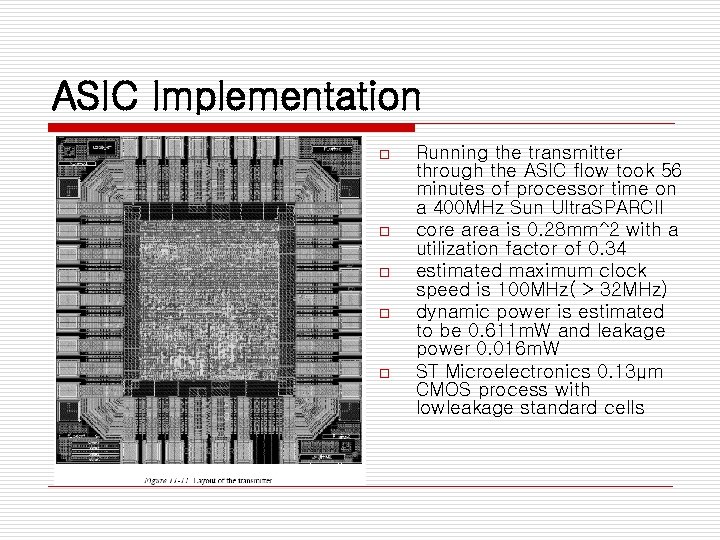

ASIC Implementation o o o Running the transmitter through the ASIC flow took 56 minutes of processor time on a 400 MHz Sun Ultra. SPARCII core area is 0. 28 mm^2 with a utilization factor of 0. 34 estimated maximum clock speed is 100 MHz( > 32 MHz) dynamic power is estimated to be 0. 611 m. W and leakage power 0. 016 m. W ST Microelectronics 0. 13µm CMOS process with lowleakage standard cells

ASIC Implementation o o o Running the transmitter through the ASIC flow took 56 minutes of processor time on a 400 MHz Sun Ultra. SPARCII core area is 0. 28 mm^2 with a utilization factor of 0. 34 estimated maximum clock speed is 100 MHz( > 32 MHz) dynamic power is estimated to be 0. 611 m. W and leakage power 0. 016 m. W ST Microelectronics 0. 13µm CMOS process with lowleakage standard cells

6. Conclusions o o o high degree of designer productivity and predictable performance. Hardware emulation n High verification speed n Confidence on the archieved results Test can be performed with real-world I/O Performance and functionality verification can be implemented on the emulator Objective advantages from the designer’s point of view include improved understanding of the overall system and its real-time behavior with the analog portions of the system. Effecively eliminating the simulation speed bottlenecks, automatic testbench generation, and interoperability with other analysis software

6. Conclusions o o o high degree of designer productivity and predictable performance. Hardware emulation n High verification speed n Confidence on the archieved results Test can be performed with real-world I/O Performance and functionality verification can be implemented on the emulator Objective advantages from the designer’s point of view include improved understanding of the overall system and its real-time behavior with the analog portions of the system. Effecively eliminating the simulation speed bottlenecks, automatic testbench generation, and interoperability with other analysis software