ОТМП_11у-2011.ppt

- Количество слайдов: 52

Развитие семейства МП х86 фирмы Intel Лекция 4 Лектор: Люличева И. А. 1

Развитие семейства МП х86 фирмы Intel Лекция 4 Лектор: Люличева И. А. 1

Рассматриваются вопросы n n n Процессоры i 386, i 486 Поддержка многозадачности Архитектура Pentium и др. Методы повышения производительности микропроцессоров. Иерархия памяти МПС, организация кешпамяти Ассемблеры, дизассемблеры и отладчики 2

Рассматриваются вопросы n n n Процессоры i 386, i 486 Поддержка многозадачности Архитектура Pentium и др. Методы повышения производительности микропроцессоров. Иерархия памяти МПС, организация кешпамяти Ассемблеры, дизассемблеры и отладчики 2

Тенденции развития микропроцессоров n n Современный уровень развития микропроцессорной техники достиг такого уровня что, в течение 5 лет происходит смена двух-трех поколений микропроцессоров. Для понимания того, как работают современные МП мы начнем с первых 32 разрядных МП фирмы Intel.

Тенденции развития микропроцессоров n n Современный уровень развития микропроцессорной техники достиг такого уровня что, в течение 5 лет происходит смена двух-трех поколений микропроцессоров. Для понимания того, как работают современные МП мы начнем с первых 32 разрядных МП фирмы Intel.

4. 1 МП 80386 и 486 Процессор i 386 был полностью совместим со своими предшественниками — процессорами 8086 -80286. Он выполняет программы, предназначенные для них без необходимости модификации кода (или с минимальными модификациями). n Вместе с тем i 386 является серьезной переработкой процессора 80286. Ни до, ни после i 386, архитектура процессоров x 86 ни разу не переделывались столь кардинально. n Процессор адресует до 4 Гбайт физической памяти и до 64 Тбайт виртуальной памяти.

4. 1 МП 80386 и 486 Процессор i 386 был полностью совместим со своими предшественниками — процессорами 8086 -80286. Он выполняет программы, предназначенные для них без необходимости модификации кода (или с минимальными модификациями). n Вместе с тем i 386 является серьезной переработкой процессора 80286. Ни до, ни после i 386, архитектура процессоров x 86 ни разу не переделывались столь кардинально. n Процессор адресует до 4 Гбайт физической памяти и до 64 Тбайт виртуальной памяти.

МП 80386 В своей основе МП 80386 состоит из шести блоков, работающих параллельно: 1. блок интерфейса с магистралью (BIU), 2. блок предварительной выборки команд, 3. блок декодирования команд, 4. исполнительный блок (EU), 5. блок управления сегментами 6. блок разбиения на страницы Это как бы зачаток конвейера.

МП 80386 В своей основе МП 80386 состоит из шести блоков, работающих параллельно: 1. блок интерфейса с магистралью (BIU), 2. блок предварительной выборки команд, 3. блок декодирования команд, 4. исполнительный блок (EU), 5. блок управления сегментами 6. блок разбиения на страницы Это как бы зачаток конвейера.

Структурная схема МП 80386

Структурная схема МП 80386

Блок интерфейса с магистралью Блок BIU обеспечивает интерфейс между МП 80386 и его окружением. Он принимает внутренние запросы для выборки команд. Одновременно он генерирует или обрабатывает сигналы для исполнения текущего цикла магистрали. К ним относятся сигналы адреса, данных и управления для обращения к внешней памяти и устройствам ввода-вывода. Блок BIU управляет также интерфейсом с внешними арбитрами магистрали и сопроцессорами.

Блок интерфейса с магистралью Блок BIU обеспечивает интерфейс между МП 80386 и его окружением. Он принимает внутренние запросы для выборки команд. Одновременно он генерирует или обрабатывает сигналы для исполнения текущего цикла магистрали. К ним относятся сигналы адреса, данных и управления для обращения к внешней памяти и устройствам ввода-вывода. Блок BIU управляет также интерфейсом с внешними арбитрами магистрали и сопроцессорами.

Блок предвыборки команд n Когда блок BIU не занимает цикла магистрали для исполнения команды, блок предвыборки команд использует его для последовательной выборки из памяти байтов команд. Эти команды хранятся в 16 -байтовой очереди команд в ожидании обработки блоком декодирования команд.

Блок предвыборки команд n Когда блок BIU не занимает цикла магистрали для исполнения команды, блок предвыборки команд использует его для последовательной выборки из памяти байтов команд. Эти команды хранятся в 16 -байтовой очереди команд в ожидании обработки блоком декодирования команд.

Интерфейс локальной магистрали 80386 С интерфейсом локальной магистрали МП 80386 совместимы следующие компоненты: n 8041, 8042 Универсальный периферийный интерфейс n 8237 Контроллер ПДП n 8253, 8254 Программируемый интервальный таймер n 8255 Программируемый периферийный интерфейс n 82 59 А Программируемый контроллер прерываний n 8272 Контроллер гибкого диска n 8274 Мультипротокольный последовательный контроллер n 82062, 82064 Контроллер жесткого диска n 82258 Улучшенный контроллер ПДП (удаленный узел)

Интерфейс локальной магистрали 80386 С интерфейсом локальной магистрали МП 80386 совместимы следующие компоненты: n 8041, 8042 Универсальный периферийный интерфейс n 8237 Контроллер ПДП n 8253, 8254 Программируемый интервальный таймер n 8255 Программируемый периферийный интерфейс n 82 59 А Программируемый контроллер прерываний n 8272 Контроллер гибкого диска n 8274 Мультипротокольный последовательный контроллер n 82062, 82064 Контроллер жесткого диска n 82258 Улучшенный контроллер ПДП (удаленный узел)

Исполнительный блок n n n Блок EU выполняет команды из очереди команд и взаимодействует со всеми другими блоками, требуемыми для завершения выполнения команды. Для ускорения выполнения команд с обращением к памяти блок EU приступает к их выполнению до завершения выполнения предыдущей команды. В состав EU входят АЛУ и регистры.

Исполнительный блок n n n Блок EU выполняет команды из очереди команд и взаимодействует со всеми другими блоками, требуемыми для завершения выполнения команды. Для ускорения выполнения команд с обращением к памяти блок EU приступает к их выполнению до завершения выполнения предыдущей команды. В состав EU входят АЛУ и регистры.

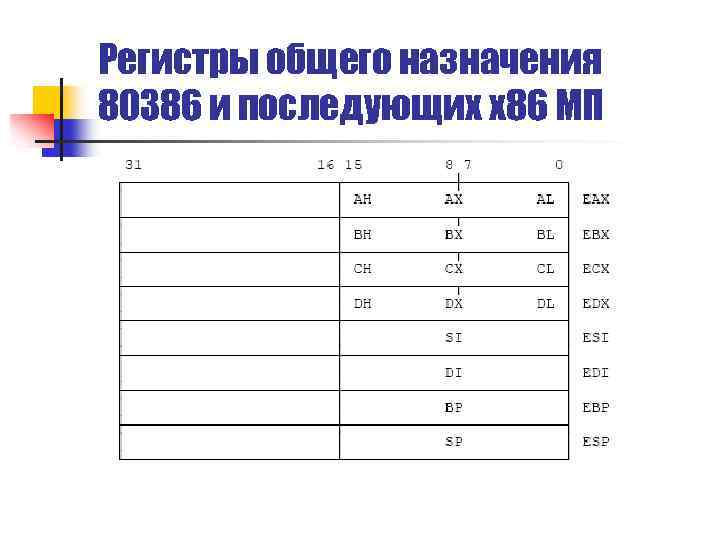

Регистры 80386 В составе микропроцессора имеются 8 32 -битных регистров общего назначения (РОНов) EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP. Младшая, 16 -битная, половина каждого из этих регистров соответствует регистрам AX, BX, CX, DX, SI, DI, BP, SP в предыдущих процессорах семейства x 86. Как и раньше возможна адресация младших и старших 8 -битных половин, младшей 16 -битной половины 32 разрядных регистров данных (AL и AH, BL и BH, CL и CH, DL и DH).

Регистры 80386 В составе микропроцессора имеются 8 32 -битных регистров общего назначения (РОНов) EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP. Младшая, 16 -битная, половина каждого из этих регистров соответствует регистрам AX, BX, CX, DX, SI, DI, BP, SP в предыдущих процессорах семейства x 86. Как и раньше возможна адресация младших и старших 8 -битных половин, младшей 16 -битной половины 32 разрядных регистров данных (AL и AH, BL и BH, CL и CH, DL и DH).

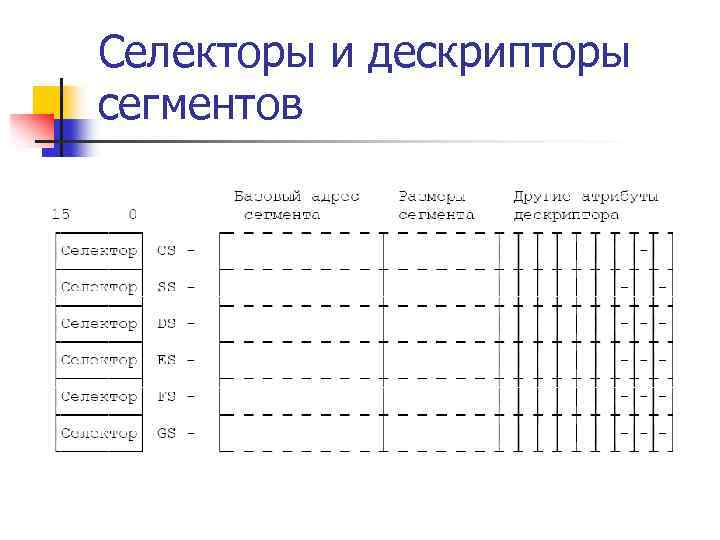

Регистры 80386 Регистр указатель команды и регистр флагов также стали 32 -битными (EIP и EFLAGS соответственно), причем в регистре флагов добавлены новая группа флажков. К 4 -м 16 -битным сегментным регистрам (ES, CS, SS, DS) прибавились ещё 2 16 -битных регистра (FS и GS) и 16 -разрядные дескрипторы сегментов. Добавлены 3 новых группы спец. регистров (каждый регистр размером 32 бит): 3 регистра управления (CR 0 (MSW), CR 2, CR 3), 8 регистров отладки (DR 0, DR 1, DR 2, DR 3, DR 6, DR 7), 2 тестовых регистра (TR 6, TR 7).

Регистры 80386 Регистр указатель команды и регистр флагов также стали 32 -битными (EIP и EFLAGS соответственно), причем в регистре флагов добавлены новая группа флажков. К 4 -м 16 -битным сегментным регистрам (ES, CS, SS, DS) прибавились ещё 2 16 -битных регистра (FS и GS) и 16 -разрядные дескрипторы сегментов. Добавлены 3 новых группы спец. регистров (каждый регистр размером 32 бит): 3 регистра управления (CR 0 (MSW), CR 2, CR 3), 8 регистров отладки (DR 0, DR 1, DR 2, DR 3, DR 6, DR 7), 2 тестовых регистра (TR 6, TR 7).

Регистры общего назначения 80386 и последующих х86 МП

Регистры общего назначения 80386 и последующих х86 МП

Блок управления сегментами (СР) n n Блок управления сегментами преобразует логические адреса в линейные по запросу блока EU. Для ускорения этого преобразования текущие дескрипторы сегментов помещаются во встроенную кэш-память. Во время трансляции адресов блок управления сегментами проверяет, нет ли нарушения сегментации. Полученный линейный адрес направляется в блок разбиения на страницы. Если страничная трансляция отключена, то сформированный линейный адрес считается физическим и выставляется на шину процессора для выполнения цикла чтения или записи памяти.

Блок управления сегментами (СР) n n Блок управления сегментами преобразует логические адреса в линейные по запросу блока EU. Для ускорения этого преобразования текущие дескрипторы сегментов помещаются во встроенную кэш-память. Во время трансляции адресов блок управления сегментами проверяет, нет ли нарушения сегментации. Полученный линейный адрес направляется в блок разбиения на страницы. Если страничная трансляция отключена, то сформированный линейный адрес считается физическим и выставляется на шину процессора для выполнения цикла чтения или записи памяти.

Селекторы и дескрипторы сегментов

Селекторы и дескрипторы сегментов

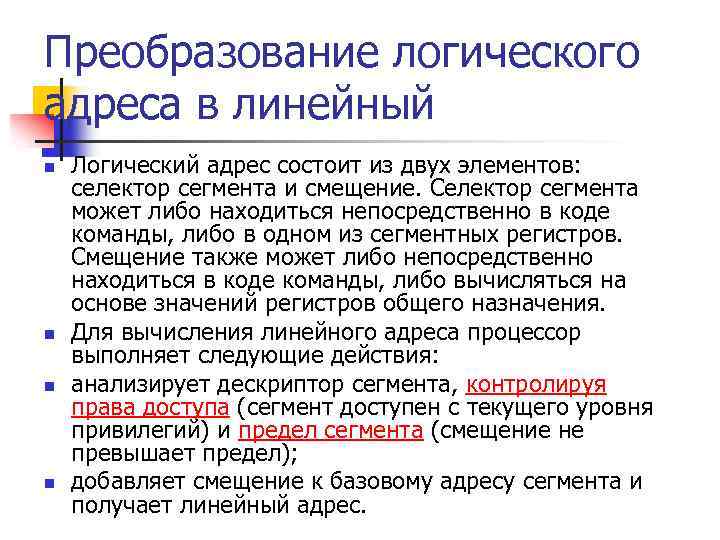

Преобразование логического адреса в линейный n n Логический адрес состоит из двух элементов: селектор сегмента и смещение. Селектор сегмента может либо находиться непосредственно в коде команды, либо в одном из сегментных регистров. Смещение также может либо непосредственно находиться в коде команды, либо вычисляться на основе значений регистров общего назначения. Для вычисления линейного адреса процессор выполняет следующие действия: анализирует дескриптор сегмента, контролируя права доступа (сегмент доступен с текущего уровня привилегий) и предел сегмента (смещение не превышает предел); добавляет смещение к базовому адресу сегмента и получает линейный адрес.

Преобразование логического адреса в линейный n n Логический адрес состоит из двух элементов: селектор сегмента и смещение. Селектор сегмента может либо находиться непосредственно в коде команды, либо в одном из сегментных регистров. Смещение также может либо непосредственно находиться в коде команды, либо вычисляться на основе значений регистров общего назначения. Для вычисления линейного адреса процессор выполняет следующие действия: анализирует дескриптор сегмента, контролируя права доступа (сегмент доступен с текущего уровня привилегий) и предел сегмента (смещение не превышает предел); добавляет смещение к базовому адресу сегмента и получает линейный адрес.

Механизм формирования адреса

Механизм формирования адреса

МП 80386 Поддержка многозадачности в процессорах x 86 (начиная с 80286) обозначает аппаратную поддержку «прозрачного» переключения с одной обычной программы (задачи) на другую. При переключении процессор сохраняет свое состояние (включая адрес следующей команды, и селекторы сегментов) в сегменте состояния (TSS; сегмент памяти, с селектором из регистра TR) одной задачи, после чего восстанавливает состояние другой задачи из ее сегмента состояния (селектор сегмента состояния новой задачи загружается из дескриптора ее сегмента кода).

МП 80386 Поддержка многозадачности в процессорах x 86 (начиная с 80286) обозначает аппаратную поддержку «прозрачного» переключения с одной обычной программы (задачи) на другую. При переключении процессор сохраняет свое состояние (включая адрес следующей команды, и селекторы сегментов) в сегменте состояния (TSS; сегмент памяти, с селектором из регистра TR) одной задачи, после чего восстанавливает состояние другой задачи из ее сегмента состояния (селектор сегмента состояния новой задачи загружается из дескриптора ее сегмента кода).

МП 80386 Переключение между задачами обычно осуществляется: n прерыванием таймера; время, на которое настроен таймер, называется квантом времени для задачи n системным вызовом (вызовом функции операционной системы) n исключением — например, при попытке выполнить недопустимую команду или обращении к отсутствующей памяти n отладкой

МП 80386 Переключение между задачами обычно осуществляется: n прерыванием таймера; время, на которое настроен таймер, называется квантом времени для задачи n системным вызовом (вызовом функции операционной системы) n исключением — например, при попытке выполнить недопустимую команду или обращении к отсутствующей памяти n отладкой

Набор инструкций 80386 n n Набор инструкций i 386 был расширен, в основном, за счет добавления 32 -битных вариантов существующих инструкций (образованных 32 -битными префиксами), включая те у которых 32 -битные варианты имеют другие мнемоники (pushad/popad, pushfd/popfd, cwd*/cdq, movsd/cmpsd/scasd/lodsd/insd/outsd, iretd), а также команды mov для новых регистров. Другие новые инструкции: установка байта по условию (set*) команды переходов (jmp, j*) с относительным 16 битным смещением команды загрузки полного адреса для новых сегментных регистров (lfs, lgs)

Набор инструкций 80386 n n Набор инструкций i 386 был расширен, в основном, за счет добавления 32 -битных вариантов существующих инструкций (образованных 32 -битными префиксами), включая те у которых 32 -битные варианты имеют другие мнемоники (pushad/popad, pushfd/popfd, cwd*/cdq, movsd/cmpsd/scasd/lodsd/insd/outsd, iretd), а также команды mov для новых регистров. Другие новые инструкции: установка байта по условию (set*) команды переходов (jmp, j*) с относительным 16 битным смещением команды загрузки полного адреса для новых сегментных регистров (lfs, lgs)

![Примеры команд. 386 add eax, ebx ; eax += ebx; add eax, [ebx] ; Примеры команд. 386 add eax, ebx ; eax += ebx; add eax, [ebx] ;](https://present5.com/presentation/11653834_32331699/image-21.jpg) Примеры команд. 386 add eax, ebx ; eax += ebx; add eax, [ebx] ; eax += ebx[0]; inc eax ; eax++; mov eax, DWORD PTR [ebx] ; Load int from memory: eax= ebx[0]; mov eax, DWORD PTR [ebx+4] ; Load next int: eax= ebx[1];

Примеры команд. 386 add eax, ebx ; eax += ebx; add eax, [ebx] ; eax += ebx[0]; inc eax ; eax++; mov eax, DWORD PTR [ebx] ; Load int from memory: eax= ebx[0]; mov eax, DWORD PTR [ebx+4] ; Load next int: eax= ebx[1];

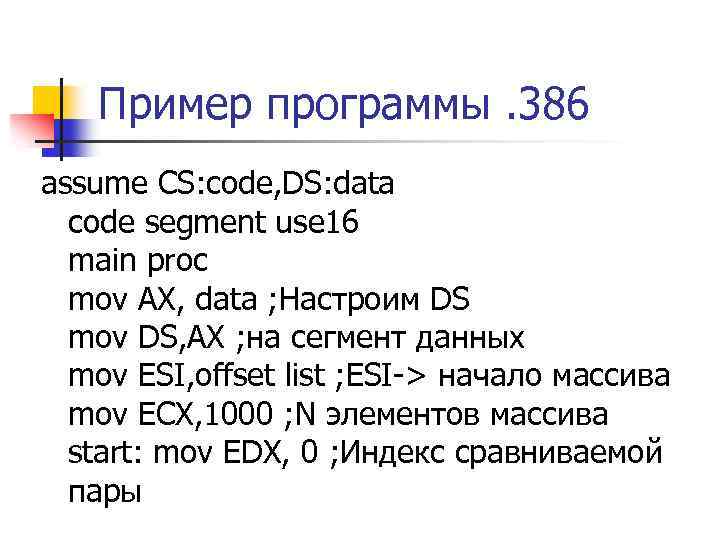

Пример программы. 386 assume CS: code, DS: data code segment use 16 main proc mov AX, data ; Настроим DS mov DS, AX ; на сегмент данных mov ESI, offset list ; ESI-> начало массива mov ECX, 1000 ; N элементов массивa start: mov EDX, 0 ; Индекс сравниваемой пары

Пример программы. 386 assume CS: code, DS: data code segment use 16 main proc mov AX, data ; Настроим DS mov DS, AX ; на сегмент данных mov ESI, offset list ; ESI-> начало массива mov ECX, 1000 ; N элементов массивa start: mov EDX, 0 ; Индекс сравниваемой пары

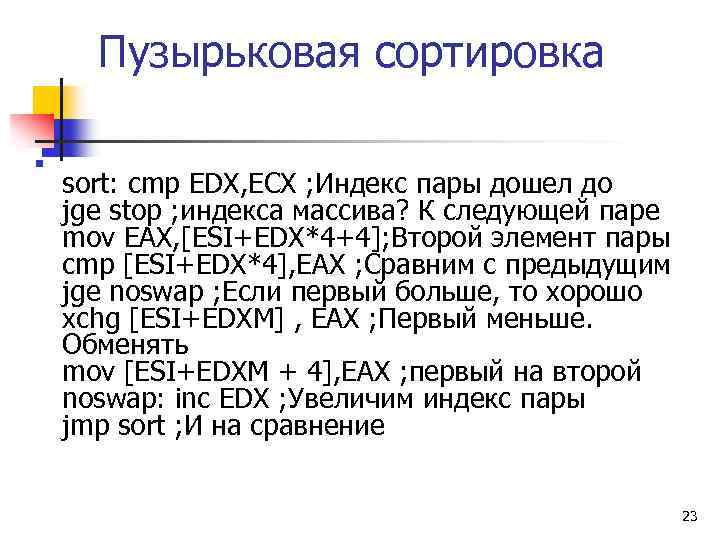

Пузырьковая сортировка n sort: cmp EDX, ECX ; Индекс пары дошел до jge stop ; индекса массива? К следующей паре mov EAX, [ESI+EDX*4+4]; Второй элемент пары cmp [ESI+EDX*4], EAX ; Сравним с предыдущим jge noswap ; Если первый больше, то хорошо xchg [ESI+EDXM] , EAX ; Первый меньше. Обменять mov [ESI+EDXM + 4], EAX ; первый на второй noswap: inc EDX ; Увеличим индекс пары jmp sort ; И на сравнение 23

Пузырьковая сортировка n sort: cmp EDX, ECX ; Индекс пары дошел до jge stop ; индекса массива? К следующей паре mov EAX, [ESI+EDX*4+4]; Второй элемент пары cmp [ESI+EDX*4], EAX ; Сравним с предыдущим jge noswap ; Если первый больше, то хорошо xchg [ESI+EDXM] , EAX ; Первый меньше. Обменять mov [ESI+EDXM + 4], EAX ; первый на второй noswap: inc EDX ; Увеличим индекс пары jmp sort ; И на сравнение 23

МП 80486 Разработан фирмой Intel. Выпускался разными фирмами в модификациях SX, DX 2, DX 4. Достоинства МП 80486 n Внутренний кэш первого уровня n Встроенный математический сопроцессор (версии DX) n Конвейерная обработка инструкций (команд) n Усовершенствованный модуль интерфейса шины n Укороченные циклы памяти n Использование буферов записи. Процессор обладал 32 -битными шинами адреса и данных. Это требовало наличия памяти в виде четырёх 30 -контактных модулей SIMM или одного 72 -контактного модуля SIMM.

МП 80486 Разработан фирмой Intel. Выпускался разными фирмами в модификациях SX, DX 2, DX 4. Достоинства МП 80486 n Внутренний кэш первого уровня n Встроенный математический сопроцессор (версии DX) n Конвейерная обработка инструкций (команд) n Усовершенствованный модуль интерфейса шины n Укороченные циклы памяти n Использование буферов записи. Процессор обладал 32 -битными шинами адреса и данных. Это требовало наличия памяти в виде четырёх 30 -контактных модулей SIMM или одного 72 -контактного модуля SIMM.

Особенности 80486 Полная программная совместимость с ЦПУ 386 DX, 386 SX, встроенным 376(TM) и процессорами 80286, 8086 и 8088; n 32 -разрядный CPU для выполнения арифметических и логических операций; n Встроенный модуль FPU для обработки арифметических операций с плавающей точкой для поддержки 32, 64, и 80 разрядных форматов. n Дополнительные сигналы управления шиной для поддержки непротиворечивости кэша; n Сегментация - одна из форм управления памятью для создания защищенных адресных пространств;

Особенности 80486 Полная программная совместимость с ЦПУ 386 DX, 386 SX, встроенным 376(TM) и процессорами 80286, 8086 и 8088; n 32 -разрядный CPU для выполнения арифметических и логических операций; n Встроенный модуль FPU для обработки арифметических операций с плавающей точкой для поддержки 32, 64, и 80 разрядных форматов. n Дополнительные сигналы управления шиной для поддержки непротиворечивости кэша; n Сегментация - одна из форм управления памятью для создания защищенных адресных пространств;

Особенности 80486 n n n Постраничное разбиение, одна из форм управления памятью, которая обеспечивает доступ к структурам данных, большим, чем доступное пространство памяти, путем хранения данных частично в памяти, частично на диске; конвеерное выполнение команд, перекрывающееся по времени с интерпретацией других команд; Регистры отладки для аппаратной поддержки контрольных точек в командах и данных;

Особенности 80486 n n n Постраничное разбиение, одна из форм управления памятью, которая обеспечивает доступ к структурам данных, большим, чем доступное пространство памяти, путем хранения данных частично в памяти, частично на диске; конвеерное выполнение команд, перекрывающееся по времени с интерпретацией других команд; Регистры отладки для аппаратной поддержки контрольных точек в командах и данных;

Кэш МП 80486 n n Intel 486 имел, расположенную на кристалле, кэш память объёмом 8 КБ, а позднее и 16 КБ, работающую на частоте ядра. Наличие кэша позволило существенно увеличить скорость выполнения операций микропроцессором. Изначально кэш Intel 486 работал по принципу сквозной записи (англ. write-through или WT), но позже, в рамках семейства Intel 486, были выпущены модели с внутренним кэшем работающим по принципу обратной записи (англ. write-back или WB). Процессор мог использовать и внешний кэш, скорость чтениязаписи которого, однако, была заметно ниже чем у внутреннего кэша. При этом внутренний кэш стали называть кэшем первого уровня (Level 1 Cache), а внешний кэш, расположенный на материнской плате, кэшем второго уровня (Level 2 Cache).

Кэш МП 80486 n n Intel 486 имел, расположенную на кристалле, кэш память объёмом 8 КБ, а позднее и 16 КБ, работающую на частоте ядра. Наличие кэша позволило существенно увеличить скорость выполнения операций микропроцессором. Изначально кэш Intel 486 работал по принципу сквозной записи (англ. write-through или WT), но позже, в рамках семейства Intel 486, были выпущены модели с внутренним кэшем работающим по принципу обратной записи (англ. write-back или WB). Процессор мог использовать и внешний кэш, скорость чтениязаписи которого, однако, была заметно ниже чем у внутреннего кэша. При этом внутренний кэш стали называть кэшем первого уровня (Level 1 Cache), а внешний кэш, расположенный на материнской плате, кэшем второго уровня (Level 2 Cache).

Математический сопроцессор В Intel 486 был использован встроенный математический сопроцессор (FPU), это был первый микропроцессор со встроенным FPU. Встроенный FPU был программно совместим с микросхемой Intel 80387 – математическим сопроцессором, применявшимся в системах с процессором Intel 386. Благодаря использованию встроенного сопроцессора удешевлялась и ускорялась система.

Математический сопроцессор В Intel 486 был использован встроенный математический сопроцессор (FPU), это был первый микропроцессор со встроенным FPU. Встроенный FPU был программно совместим с микросхемой Intel 80387 – математическим сопроцессором, применявшимся в системах с процессором Intel 386. Благодаря использованию встроенного сопроцессора удешевлялась и ускорялась система.

Математический сопроцессор n n Изначально все выпускавшиеся микропроцессоры Intel 486 оснащались работающим сопроцессором, эти процессоры получили имя Intel 486 DX. Позже, в 1991 году, Intel решает выпустить процессоры с отключённым сопроцессором, и эти процессоры получили наименование Intel 486 SX.

Математический сопроцессор n n Изначально все выпускавшиеся микропроцессоры Intel 486 оснащались работающим сопроцессором, эти процессоры получили имя Intel 486 DX. Позже, в 1991 году, Intel решает выпустить процессоры с отключённым сопроцессором, и эти процессоры получили наименование Intel 486 SX.

Структурная схема МП 80486 DX

Структурная схема МП 80486 DX

Hello world для MS-DOS для архитектуры x 86 на диалекте TASM: . MODEL TINY CODE SEGMENT ASSUME CS: CODE, DS: CODE ORG 100 h START: mov ah, 9 mov dx, OFFSET Msg int 21 h int 20 h Msg DB 'Hello World', 13, 10, '$' CODE ENDS END START

Hello world для MS-DOS для архитектуры x 86 на диалекте TASM: . MODEL TINY CODE SEGMENT ASSUME CS: CODE, DS: CODE ORG 100 h START: mov ah, 9 mov dx, OFFSET Msg int 21 h int 20 h Msg DB 'Hello World', 13, 10, '$' CODE ENDS END START

Pentium был первым CISC процессором использующим суперскалярную архитектуру. Pentium имеет два конвейера, которые могут выполнять две инструкции одновременно. Каждый конвейер имеет свое арифметическо логическое устройство (ALU), совокупность устройств генерации адреса и интерфейс кэ ширования данных.

Pentium был первым CISC процессором использующим суперскалярную архитектуру. Pentium имеет два конвейера, которые могут выполнять две инструкции одновременно. Каждый конвейер имеет свое арифметическо логическое устройство (ALU), совокупность устройств генерации адреса и интерфейс кэ ширования данных.

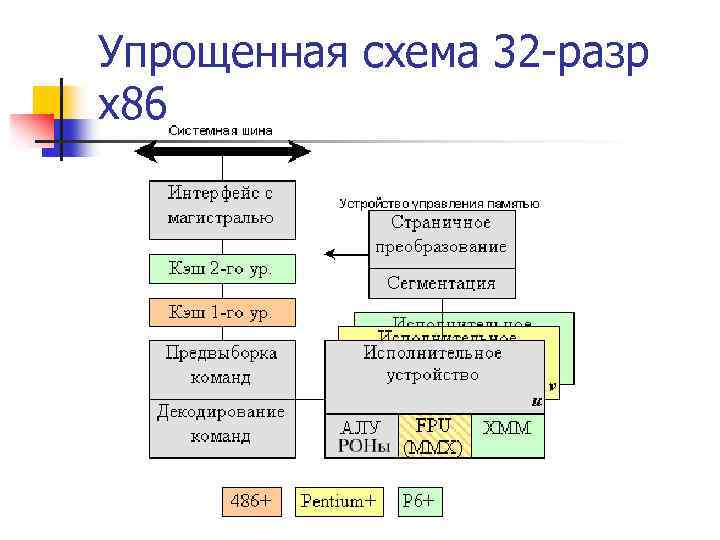

Упрощенная схема 32 -разр х86

Упрощенная схема 32 -разр х86

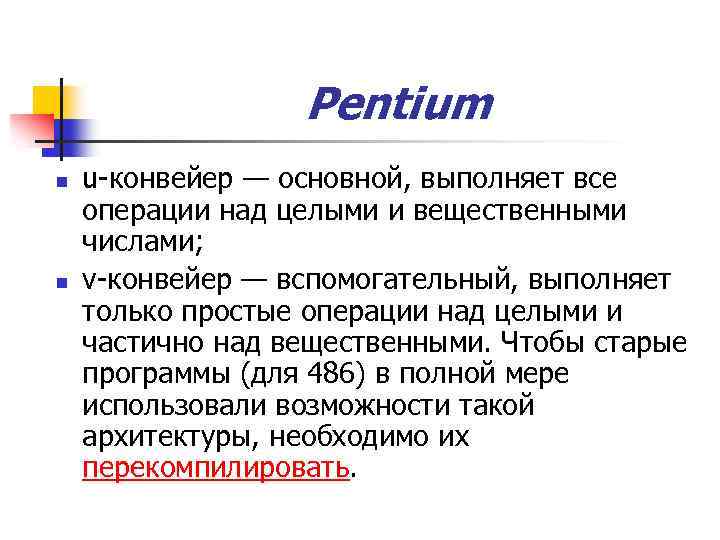

Pentium n n u-конвейер — основной, выполняет все операции над целыми и вещественными числами; v-конвейер — вспомогательный, выполняет только простые операции над целыми и частично над вещественными. Чтобы старые программы (для 486) в полной мере использовали возможности такой архитектуры, необходимо их перекомпилировать.

Pentium n n u-конвейер — основной, выполняет все операции над целыми и вещественными числами; v-конвейер — вспомогательный, выполняет только простые операции над целыми и частично над вещественными. Чтобы старые программы (для 486) в полной мере использовали возможности такой архитектуры, необходимо их перекомпилировать.

4. 2 Методы повышения производительности МПС Делятся на несколько групп n Технологические n Архитектурные n Уровня системы команд n Усовершенствование системных шин, n многоуровневая организация памяти и. т. д.

4. 2 Методы повышения производительности МПС Делятся на несколько групп n Технологические n Архитектурные n Уровня системы команд n Усовершенствование системных шин, n многоуровневая организация памяти и. т. д.

4. 1 Технологические методы повышения производительности МП n n n повышение тактовой частоты, увеличение числа транзисторов в кристалле, увеличение числа слоев металлизации Каждый из этих методов сопряжен со своими трудностями

4. 1 Технологические методы повышения производительности МП n n n повышение тактовой частоты, увеличение числа транзисторов в кристалле, увеличение числа слоев металлизации Каждый из этих методов сопряжен со своими трудностями

Повышение тактовой частоты n n n Несмотря на рост быстродействия ключей, прекратился рост тактовых частот процессоров, хотя раньше это был синоним производительности. Остается только увеличивать число ядер - 2, 4, 8, 80, кто больше? Несколько лет назад Intel штурмовала вершины тактовых частот, и в обиходе были цифры 10 ГГц и выше. В начале 2008 года снизили планку до 4 -: -5 ГГц. Но прошел год, пропали упоминания и о 5 ГГц. С некоторого времени существует тенденция, когда максимальная тактовая частота процессоров с переходом на более тонкие технологические процессы, по крайней мере, не растет. (См. таблицу).

Повышение тактовой частоты n n n Несмотря на рост быстродействия ключей, прекратился рост тактовых частот процессоров, хотя раньше это был синоним производительности. Остается только увеличивать число ядер - 2, 4, 8, 80, кто больше? Несколько лет назад Intel штурмовала вершины тактовых частот, и в обиходе были цифры 10 ГГц и выше. В начале 2008 года снизили планку до 4 -: -5 ГГц. Но прошел год, пропали упоминания и о 5 ГГц. С некоторого времени существует тенденция, когда максимальная тактовая частота процессоров с переходом на более тонкие технологические процессы, по крайней мере, не растет. (См. таблицу).

Повышение тактовой частоты Год 1993 1 Технология мкм 2 Макс. тактовая частота процессора МГц /Модель 1997 2003 2005 2007 2009 0. 5 0. 35 0. 25 0, 09 0, 065 0, 045 0. 03 45 35 30 15 3800/ Pentium 4 673 3160 */ Quad -Core Прогноз 3000 Длина канала нм 3 199 5 200/ Pent 200 450/ Penti um Pro 1000/ Pentium III Xeon

Повышение тактовой частоты Год 1993 1 Технология мкм 2 Макс. тактовая частота процессора МГц /Модель 1997 2003 2005 2007 2009 0. 5 0. 35 0. 25 0, 09 0, 065 0, 045 0. 03 45 35 30 15 3800/ Pentium 4 673 3160 */ Quad -Core Прогноз 3000 Длина канала нм 3 199 5 200/ Pent 200 450/ Penti um Pro 1000/ Pentium III Xeon

Повышение тактовой частоты При переходе с 130 нм на 90 нм тех. процесс прироста тактовой частоты непропорционален, а при переходе с 90 нм тех. процесса к 65 нм прироста вообще не было. n Еще одно явное подтверждение сказанного, Intel была вынуждена сообщить о снятии из своих планов производства процессора Pentium 4 с тактовой частотой 4 ГГц. Это сделано не только по причине тепловыделения, но и из-за их нестабильной работы. n Вместо повышения тактовой частоты фирма применила многоядерность.

Повышение тактовой частоты При переходе с 130 нм на 90 нм тех. процесс прироста тактовой частоты непропорционален, а при переходе с 90 нм тех. процесса к 65 нм прироста вообще не было. n Еще одно явное подтверждение сказанного, Intel была вынуждена сообщить о снятии из своих планов производства процессора Pentium 4 с тактовой частотой 4 ГГц. Это сделано не только по причине тепловыделения, но и из-за их нестабильной работы. n Вместо повышения тактовой частоты фирма применила многоядерность.

Помехи при повышении частоты n n n Помехи в цепях питания микросхем известны, это явление всегда рассматривалось с точки зрения помехоустойчивости узлов выполненных на быстродействующих интегральных микросхемах. Появление чипов с сотнями миллионов ключей, каждый из которых имеет быстродействие на много порядков большее приобрело качественно новое значение. Изменился не только уровень помехи, но она приобрела еще и энергетическую составляющую, расширился спектральный диапазон. Старыми методами проблема стала нерешаема.

Помехи при повышении частоты n n n Помехи в цепях питания микросхем известны, это явление всегда рассматривалось с точки зрения помехоустойчивости узлов выполненных на быстродействующих интегральных микросхемах. Появление чипов с сотнями миллионов ключей, каждый из которых имеет быстродействие на много порядков большее приобрело качественно новое значение. Изменился не только уровень помехи, но она приобрела еще и энергетическую составляющую, расширился спектральный диапазон. Старыми методами проблема стала нерешаема.

Потребление мощности n n n Для увеличения скорости вычислений производители применили известный способ повышения производительности, используемый в серверах. Это параллельное вычисление на нескольких процессорах или многоядерных процессорах, что иногда является полным аналогом многопроцессорных серверов. Пока ядер 2 и 4. И как предел стремления повысить производительность, это 80 ядерный чип представленный Intel. Он представляет собой 32 битный процессор, содержащий 100 млн. транзисторов, с рабочим напряжением питания 0, 95 В, работающий на частоте 3, 16 ГГц и потребляющий 98 Вт. После поднятия тактовой частоты до 4 ГГц производительность возросла, но мощность превысила 120 Вт.

Потребление мощности n n n Для увеличения скорости вычислений производители применили известный способ повышения производительности, используемый в серверах. Это параллельное вычисление на нескольких процессорах или многоядерных процессорах, что иногда является полным аналогом многопроцессорных серверов. Пока ядер 2 и 4. И как предел стремления повысить производительность, это 80 ядерный чип представленный Intel. Он представляет собой 32 битный процессор, содержащий 100 млн. транзисторов, с рабочим напряжением питания 0, 95 В, работающий на частоте 3, 16 ГГц и потребляющий 98 Вт. После поднятия тактовой частоты до 4 ГГц производительность возросла, но мощность превысила 120 Вт.

Увеличение числа транзисторов n n Для увеличение числа транзисторов используются более совершенные технологические процессы с меньшими проектными нормами а также более плотная компоновка функциональных блоков кристалла. Но при минимальном размере деталей внутренней структуры интегральных схем 0, 1 -0, 2 мкм достигается оптимум, ниже которого все характеристики транзистора быстро ухудшаются. При этом начинают проявляться эффекты квантовой связи и пр.

Увеличение числа транзисторов n n Для увеличение числа транзисторов используются более совершенные технологические процессы с меньшими проектными нормами а также более плотная компоновка функциональных блоков кристалла. Но при минимальном размере деталей внутренней структуры интегральных схем 0, 1 -0, 2 мкм достигается оптимум, ниже которого все характеристики транзистора быстро ухудшаются. При этом начинают проявляться эффекты квантовой связи и пр.

Увеличение числа транзисторов n n n Проектная норма 0, 05 -0, 1 мкм (50 -100 нм) - это нижний предел твердотельной микроэлектроники, основанной на классических принципах синтеза схем. Сейчас работы в области нанотехнологий ведутся в четырех основных направлениях: - молекулярная электроника; - биохимические и органические решения; - квазимеханические решения на основе нанотрубок; - квантовые компьютеры. Три последних пребывают пока еще в значительной степени на уровне теоретических работ. Наибольшие практические результаты достигнуты в области молекулярной электроники.

Увеличение числа транзисторов n n n Проектная норма 0, 05 -0, 1 мкм (50 -100 нм) - это нижний предел твердотельной микроэлектроники, основанной на классических принципах синтеза схем. Сейчас работы в области нанотехнологий ведутся в четырех основных направлениях: - молекулярная электроника; - биохимические и органические решения; - квазимеханические решения на основе нанотрубок; - квантовые компьютеры. Три последних пребывают пока еще в значительной степени на уровне теоретических работ. Наибольшие практические результаты достигнуты в области молекулярной электроники.

Число слоев металлизации n Увеличение числа слоев металлизации (от 4 -5 до 10 -12)– тоже не панацея. Кстати, различные фирмы по-разному подходят к этой технологии.

Число слоев металлизации n Увеличение числа слоев металлизации (от 4 -5 до 10 -12)– тоже не панацея. Кстати, различные фирмы по-разному подходят к этой технологии.

Иерархия памяти в МПС Регистровый файл Кеш 1 уровня Кеш 2 уровня Кеш 3 уровня Основная память Внешние носители Флеш-память HDD CD/DVD Стриммеры и др.

Иерархия памяти в МПС Регистровый файл Кеш 1 уровня Кеш 2 уровня Кеш 3 уровня Основная память Внешние носители Флеш-память HDD CD/DVD Стриммеры и др.

Отладчик и дизассемблер Дизассе мблер — транслятор, преобразующий машинный код, объектный файл или библиотечные модули в текст программы на языке ассемблера. По режиму работы с пользователем делятся на n Автоматические n Интерактивные Дизассемблеры бывают однопроходные и многопроходные.

Отладчик и дизассемблер Дизассе мблер — транслятор, преобразующий машинный код, объектный файл или библиотечные модули в текст программы на языке ассемблера. По режиму работы с пользователем делятся на n Автоматические n Интерактивные Дизассемблеры бывают однопроходные и многопроходные.

Отладчик и дизассемблер Основная трудность при работе дизассемблера — отличить данные от машинного кода, поэтому на первых проходах автоматически или интерактивно собирается информация о границах процедур и функций, а на последнем проходе формируется итоговый листинг. Обычно однопроходный дизассемблер и построчный ассемблер являются составной частью отладчика.

Отладчик и дизассемблер Основная трудность при работе дизассемблера — отличить данные от машинного кода, поэтому на первых проходах автоматически или интерактивно собирается информация о границах процедур и функций, а на последнем проходе формируется итоговый листинг. Обычно однопроходный дизассемблер и построчный ассемблер являются составной частью отладчика.

Порядок работы в отладчике Необходимый минимум для отладки программ: n Важные элементы основного меню n Горячие клавиши n Переход между окнами n Контектстное меню n Смена состояний регистров n Исправление кода программы n Дамп памяти 48

Порядок работы в отладчике Необходимый минимум для отладки программ: n Важные элементы основного меню n Горячие клавиши n Переход между окнами n Контектстное меню n Смена состояний регистров n Исправление кода программы n Дамп памяти 48

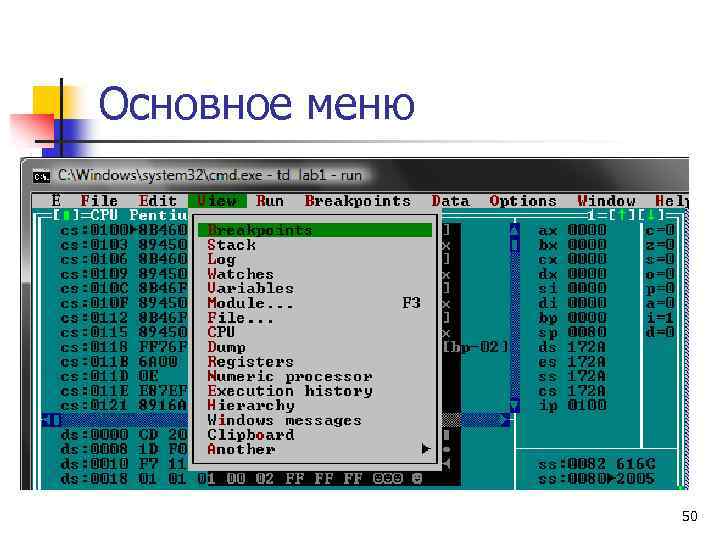

Важные элементы основного меню n n n Окна(Windows) – основное, стек, точки прерывания, пользователя Запуск(Run) лучше использовать горячие клавиши, оттуда можно перезапустить программу Просмотр(View) – огромный выбор вариантов!! 49

Важные элементы основного меню n n n Окна(Windows) – основное, стек, точки прерывания, пользователя Запуск(Run) лучше использовать горячие клавиши, оттуда можно перезапустить программу Просмотр(View) – огромный выбор вариантов!! 49

Основное меню 50

Основное меню 50

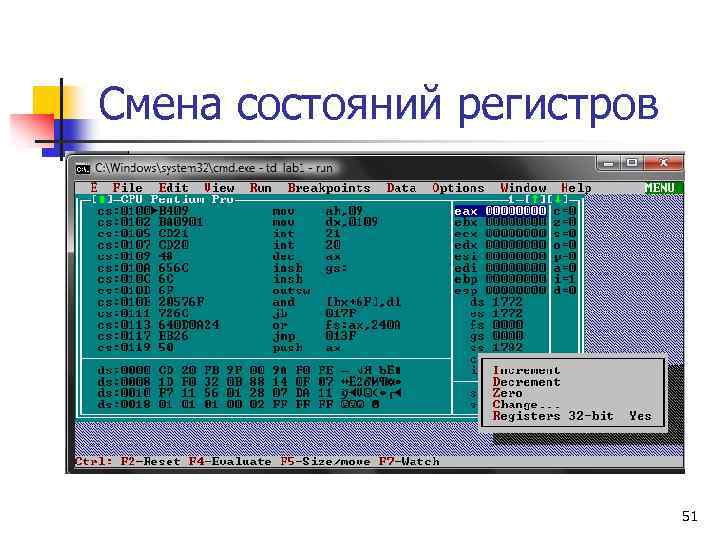

Смена состояний регистров 51

Смена состояний регистров 51

Пакет TASM n n n Пакет TASM состоит из нескольких стандартных директорий BIN LIB INCLUDE DOC Примеры находятся в директории EXAMPLES и хорошо задокументированы (на англ. языке) 52

Пакет TASM n n n Пакет TASM состоит из нескольких стандартных директорий BIN LIB INCLUDE DOC Примеры находятся в директории EXAMPLES и хорошо задокументированы (на англ. языке) 52