c0041dfcbce140194b40e0aff7d82e92.ppt

- Количество слайдов: 123

Rapid Prototyping Design Process

Rapid Prototyping Design Process

Module Goals

Module Goals

Module Outline

Module Outline

Module Outline

Module Outline

Module Outline

Module Outline

Hardware Synthesis

Hardware Synthesis

Definitions

Definitions

Definitions (Cont. )

Definitions (Cont. )

Definitions (Cont. )

Definitions (Cont. )

Synthesis Goals

Synthesis Goals

Synthesis Constraints

Synthesis Constraints

Synthesis Processes

Synthesis Processes

Synthesis Categories

Synthesis Categories

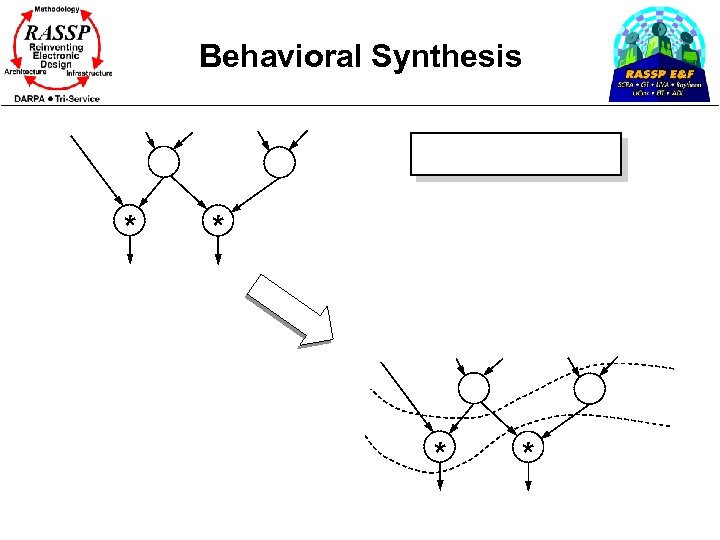

Behavioral Synthesis * *

Behavioral Synthesis * *

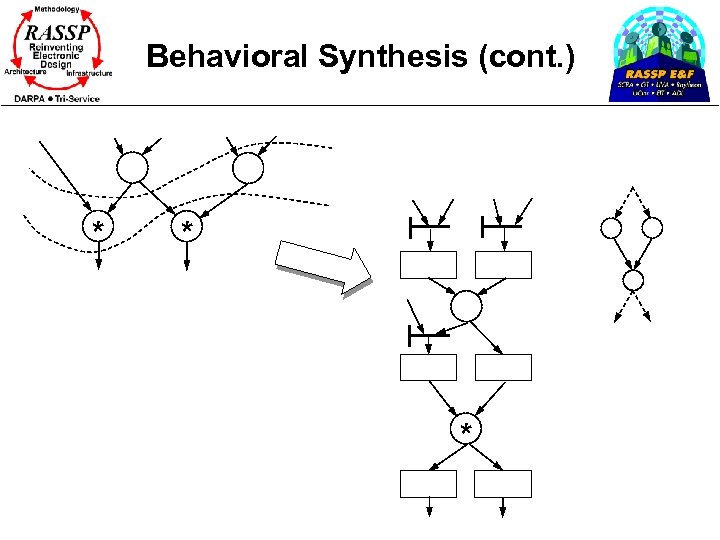

Behavioral Synthesis (cont. ) * * *

Behavioral Synthesis (cont. ) * * *

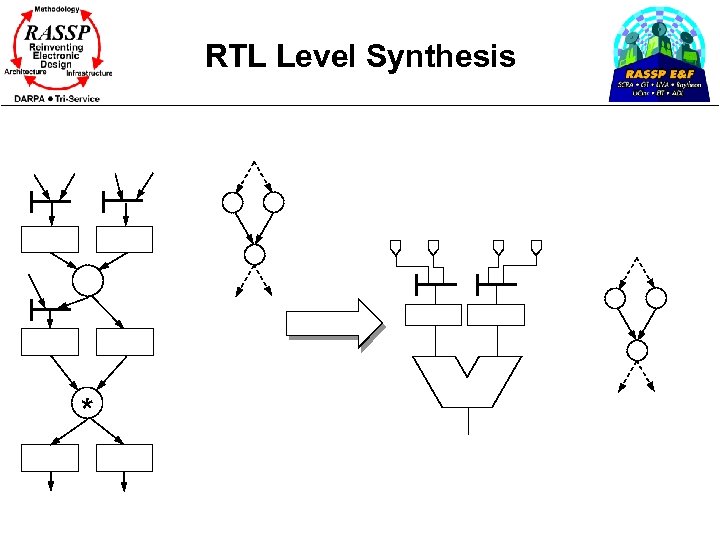

RTL Level Synthesis *

RTL Level Synthesis *

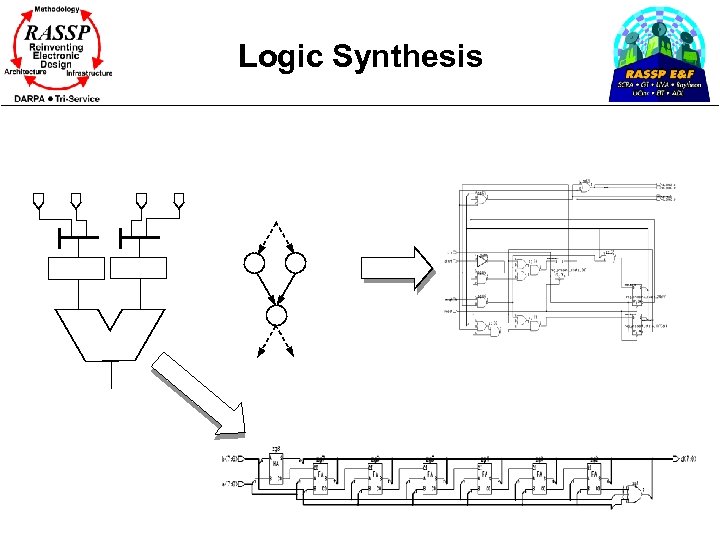

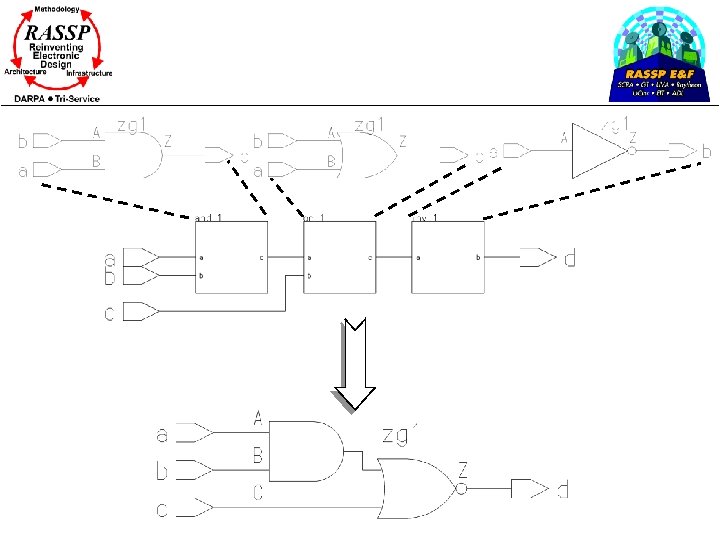

Logic Synthesis

Logic Synthesis

Module Outline

Module Outline

Module Outline

Module Outline

Types

Types

Types (cont. )

Types (cont. )

Attributes

Attributes

Concurrent Signal Assignment Statements

Concurrent Signal Assignment Statements

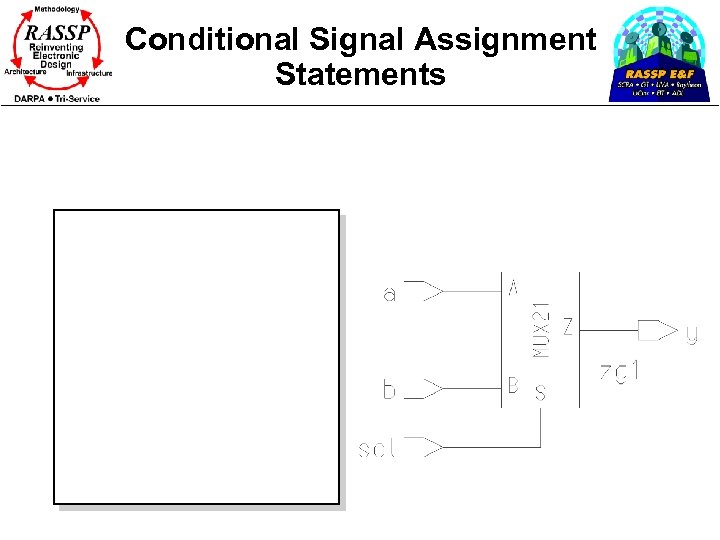

Conditional Signal Assignment Statements

Conditional Signal Assignment Statements

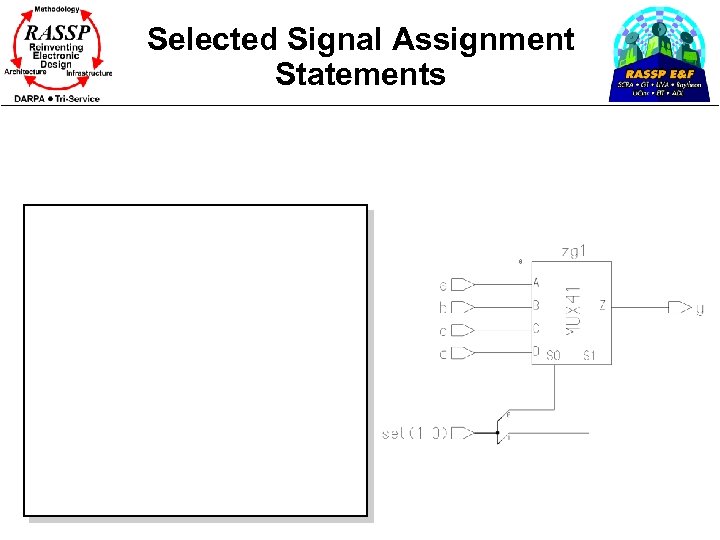

Selected Signal Assignment Statements

Selected Signal Assignment Statements

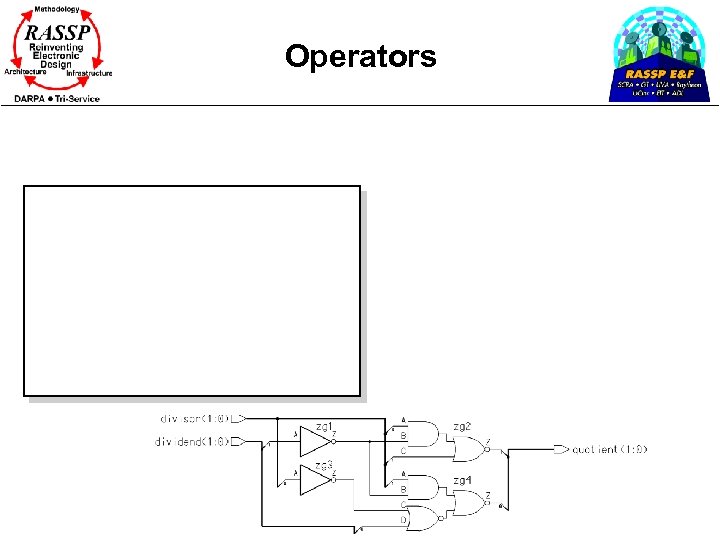

Operators

Operators

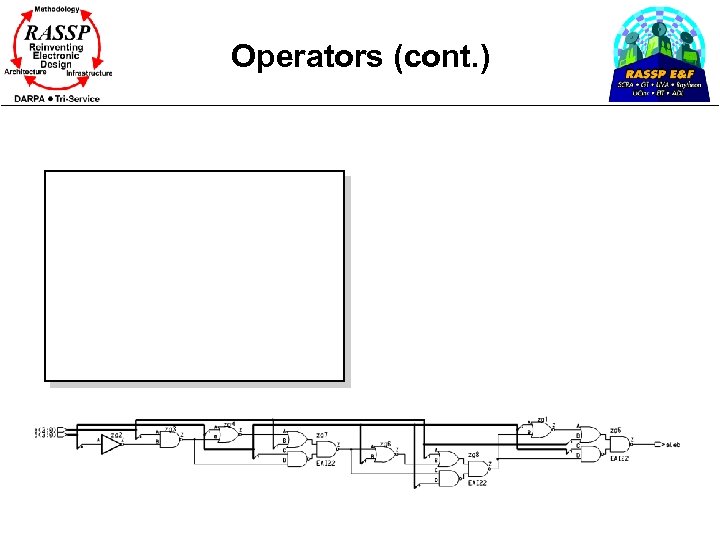

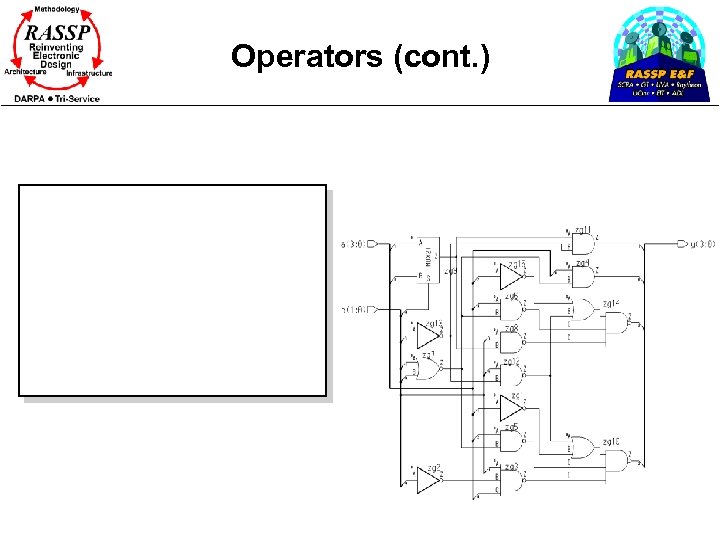

Operators (cont. )

Operators (cont. )

Operators (cont. )

Operators (cont. )

Process Statements

Process Statements

Sequential Signal Assignment Statements

Sequential Signal Assignment Statements

Sequential IF Statements

Sequential IF Statements

Sequential Case Statements

Sequential Case Statements

Sequential Loop Statements

Sequential Loop Statements

Procedures and Functions

Procedures and Functions

Procedures and Functions (cont. )

Procedures and Functions (cont. )

Procedures and Functions (cont. )

Procedures and Functions (cont. )

Using Procedures and Functions

Using Procedures and Functions

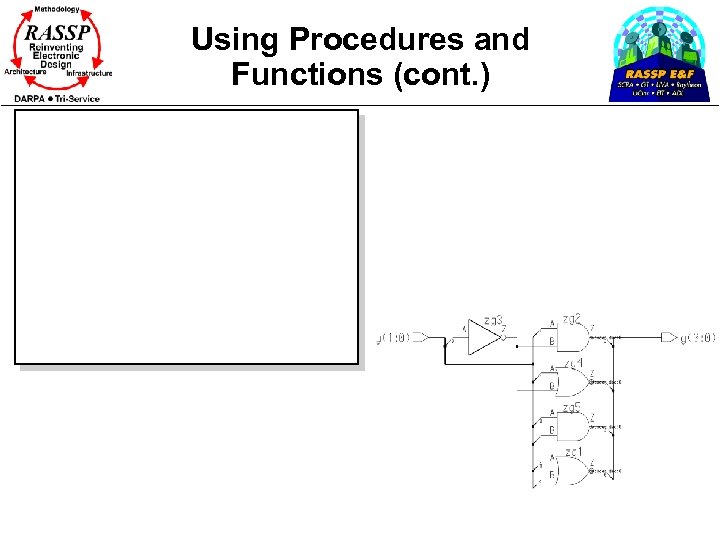

Using Procedures and Functions (cont. )

Using Procedures and Functions (cont. )

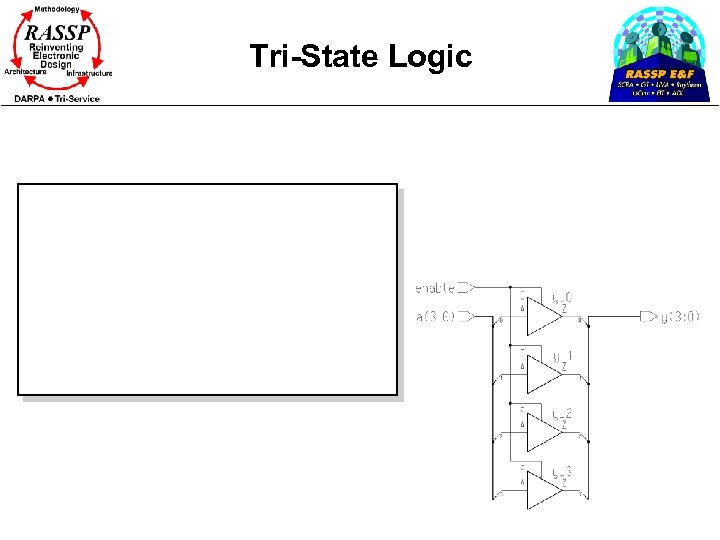

Tri-State Logic

Tri-State Logic

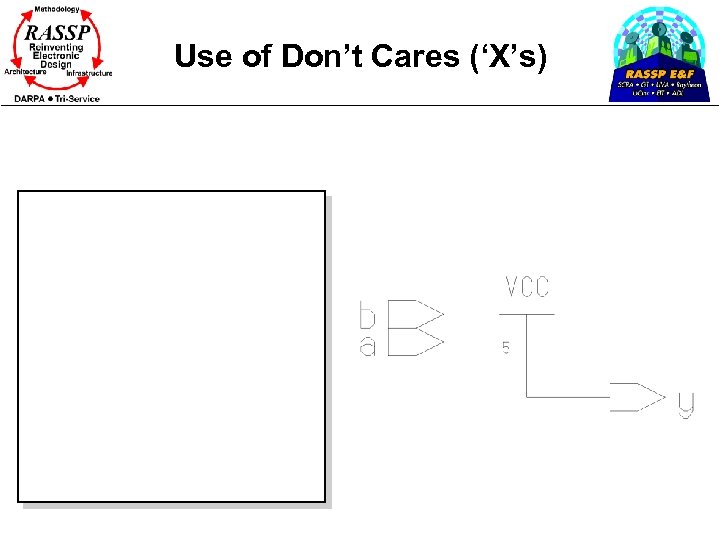

Use of Don’t Cares (‘X’s)

Use of Don’t Cares (‘X’s)

After Clauses

After Clauses

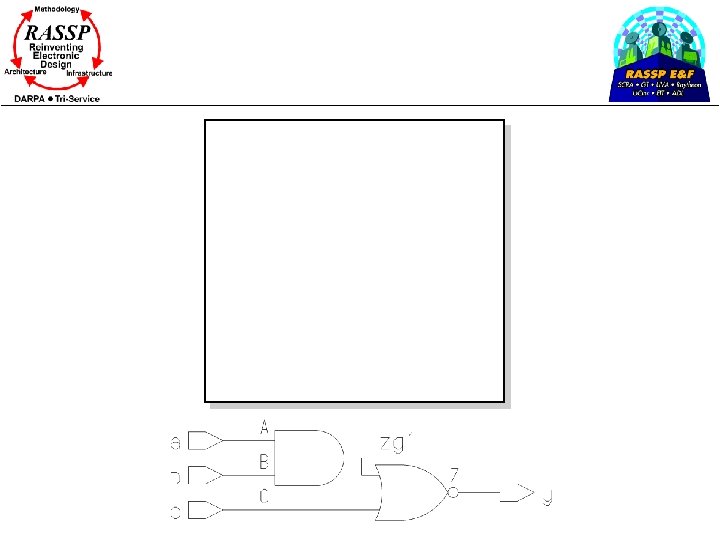

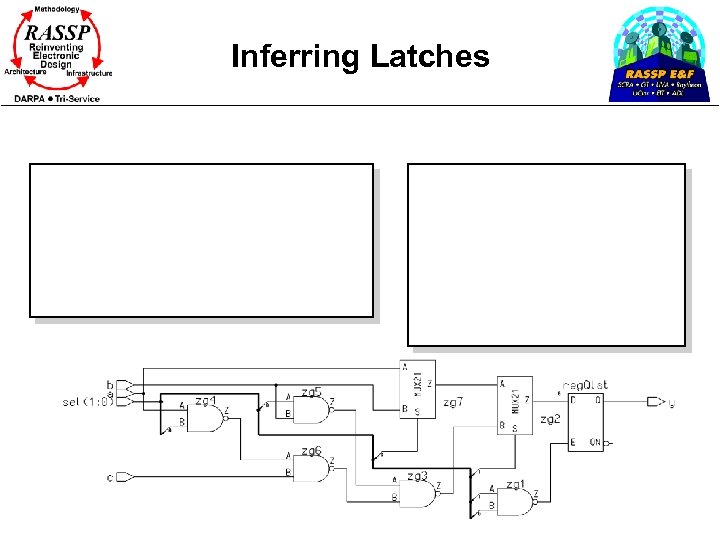

Inferring Latches

Inferring Latches

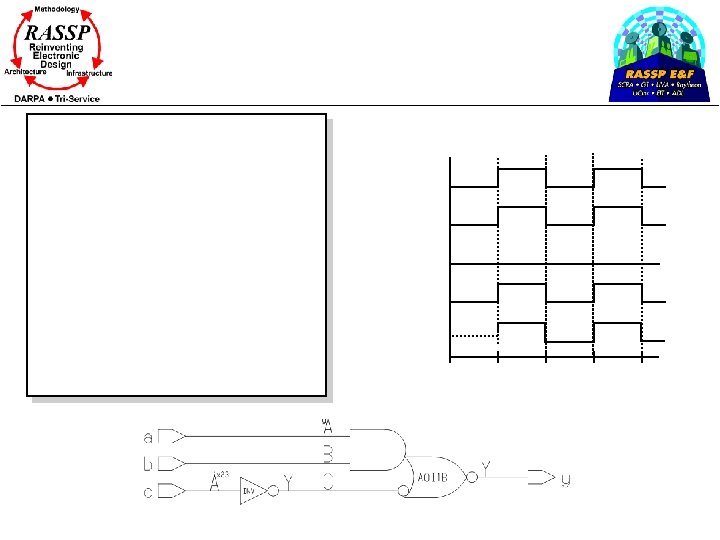

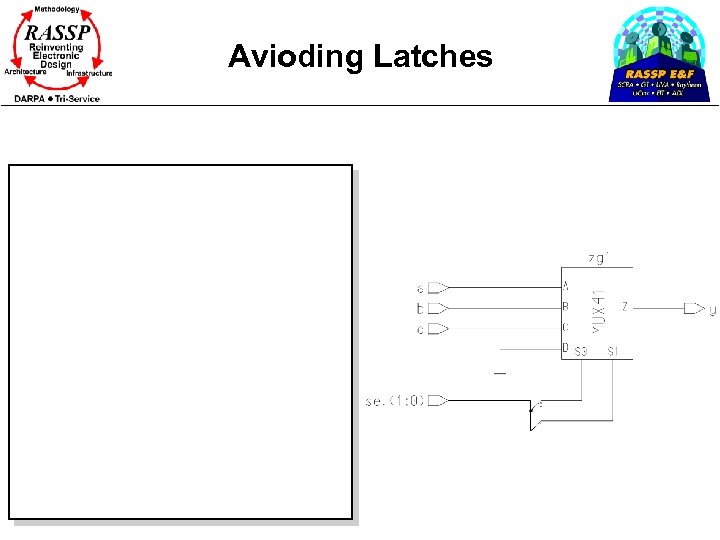

Avioding Latches

Avioding Latches

Module Outline

Module Outline

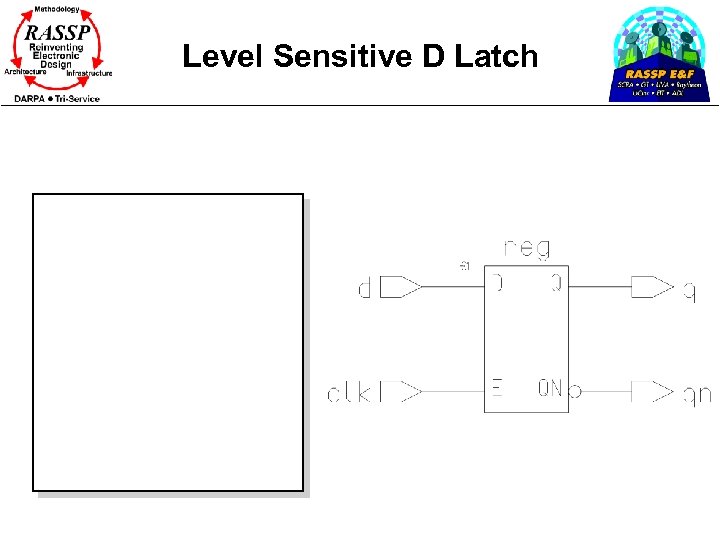

Level Sensitive D Latch

Level Sensitive D Latch

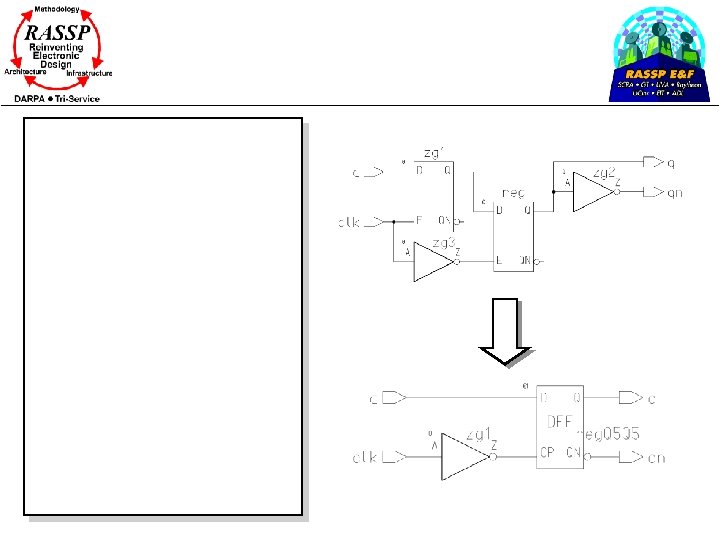

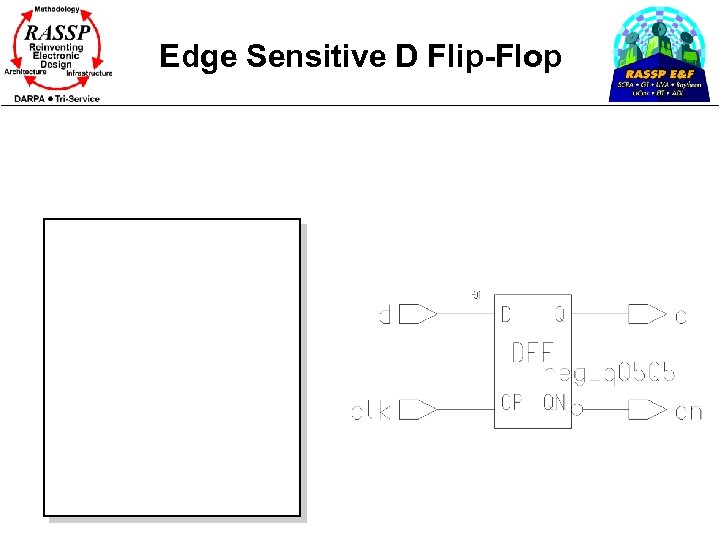

Edge Sensitive D Flip-Flop

Edge Sensitive D Flip-Flop

Edge Sensitive D Flip-Flop (cont. )

Edge Sensitive D Flip-Flop (cont. )

Edge Sensitive Flip-Flops

Edge Sensitive Flip-Flops

Edge Sensitive Flip-Flops

Edge Sensitive Flip-Flops

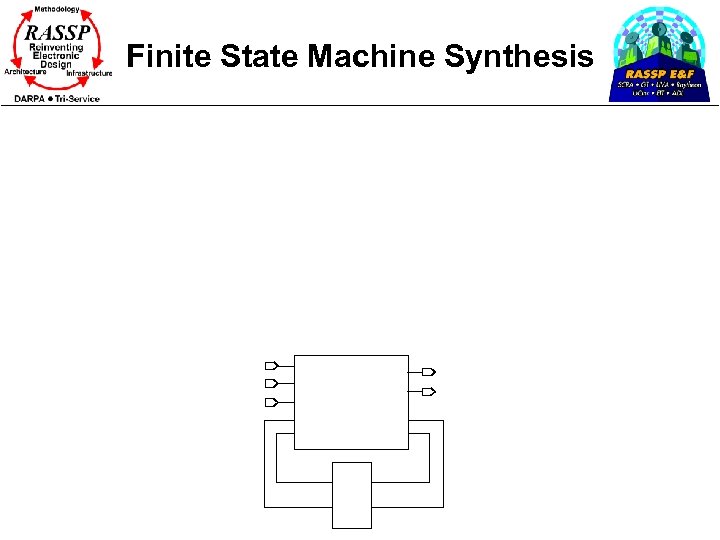

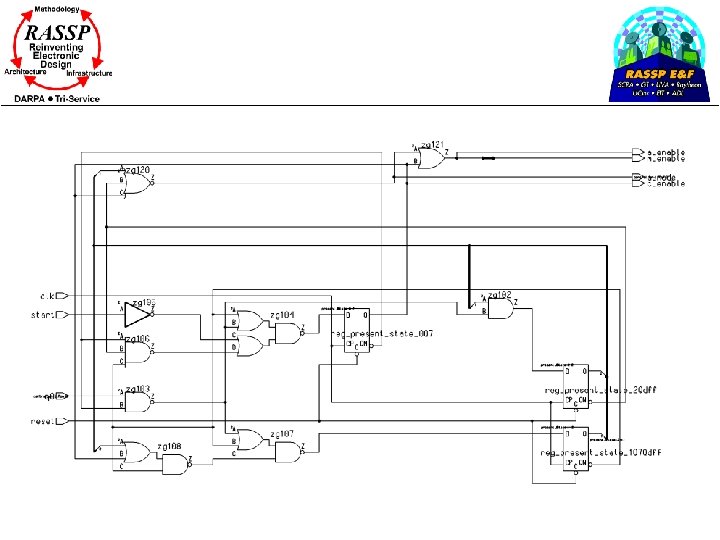

Finite State Machine Synthesis

Finite State Machine Synthesis

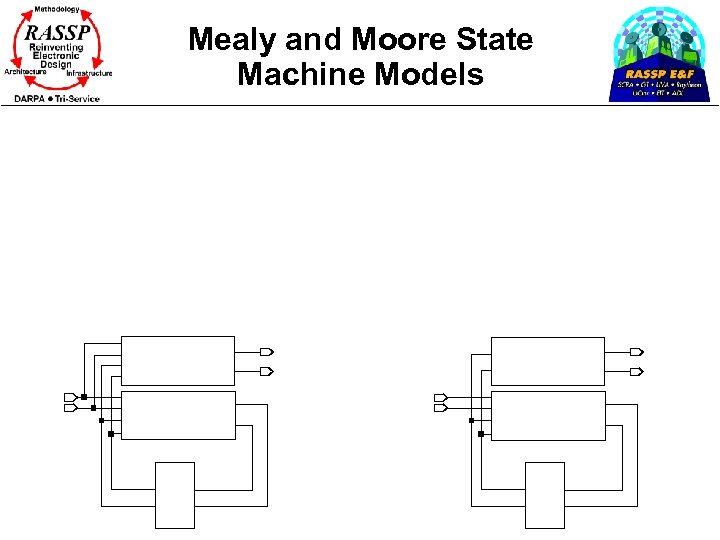

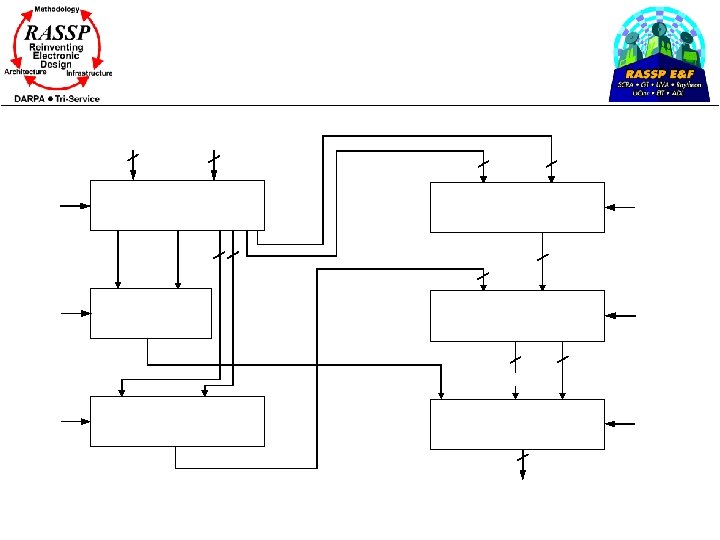

Mealy and Moore State Machine Models

Mealy and Moore State Machine Models

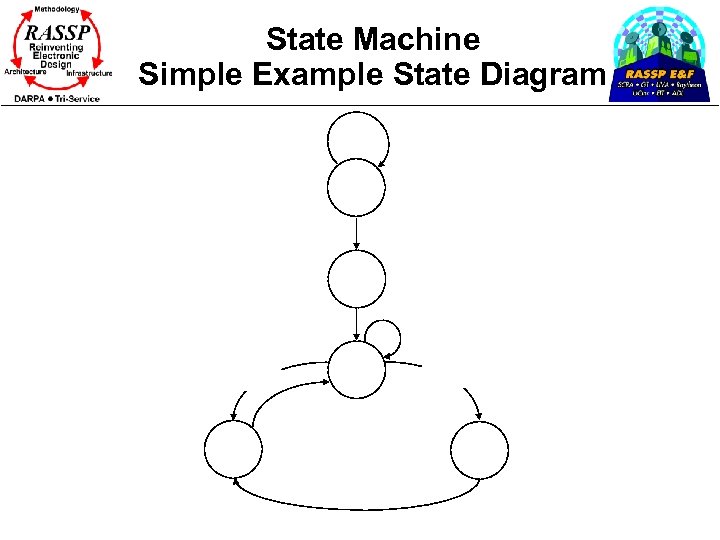

State Machine Simple Example State Diagram

State Machine Simple Example State Diagram

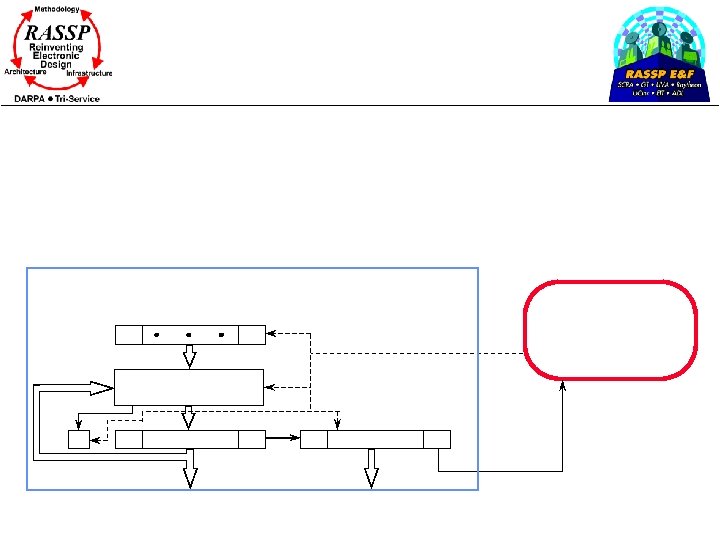

Sequential Datapaths

Sequential Datapaths

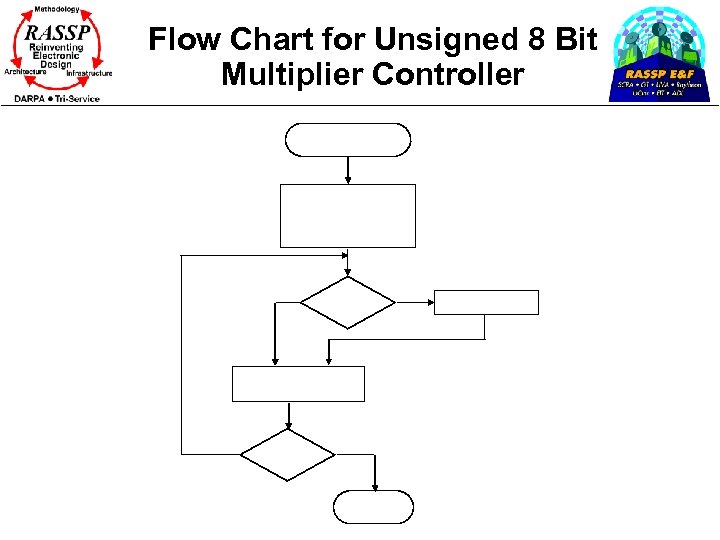

Flow Chart for Unsigned 8 Bit Multiplier Controller

Flow Chart for Unsigned 8 Bit Multiplier Controller

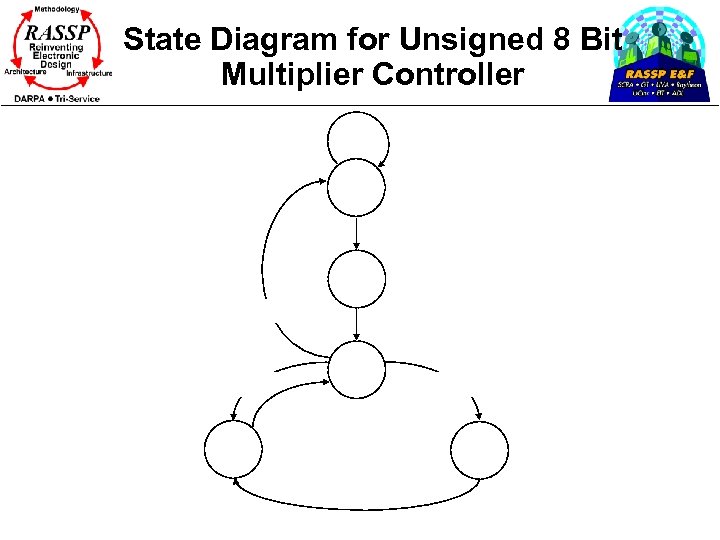

State Diagram for Unsigned 8 Bit Multiplier Controller

State Diagram for Unsigned 8 Bit Multiplier Controller

Module Outline

Module Outline

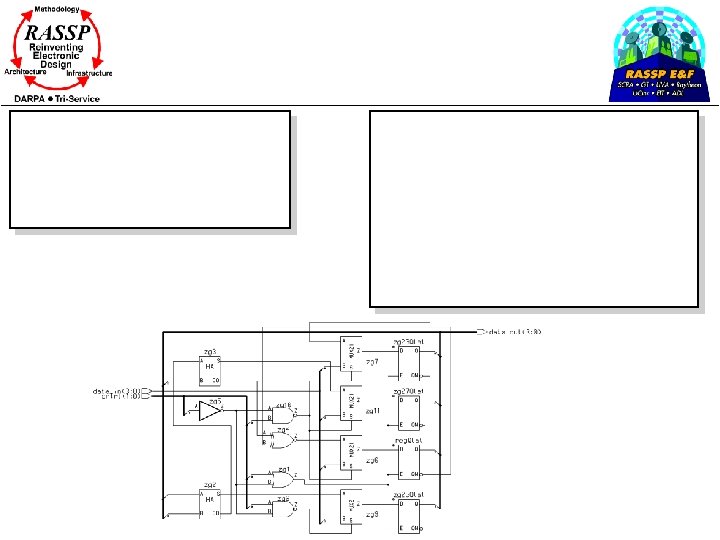

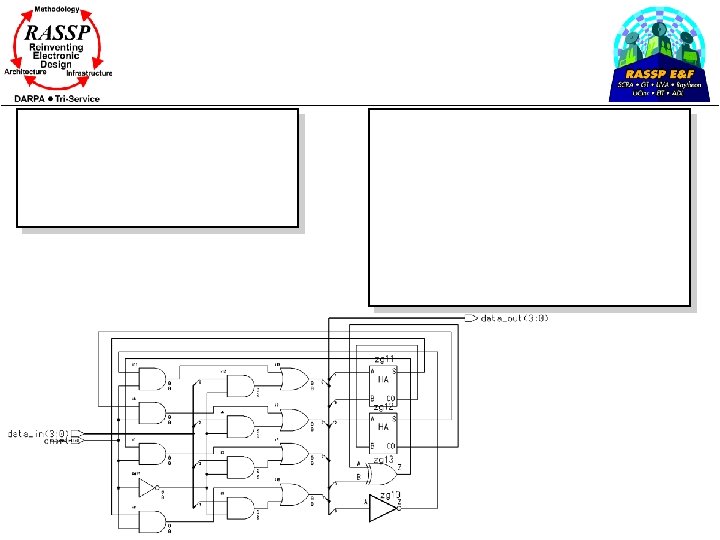

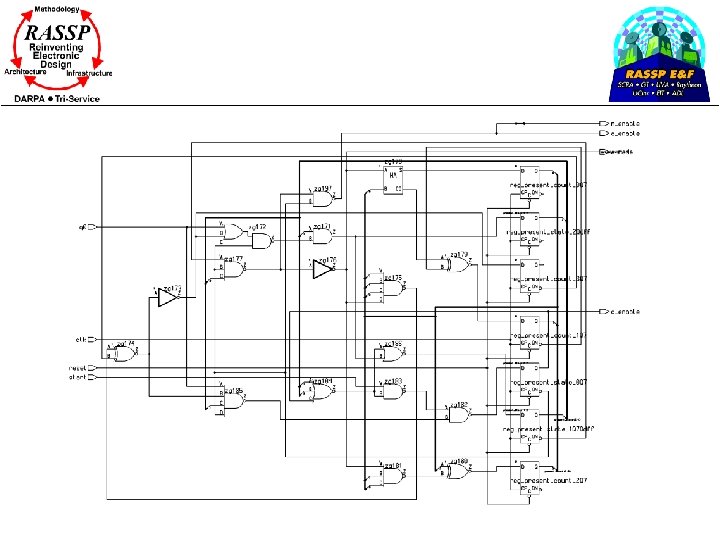

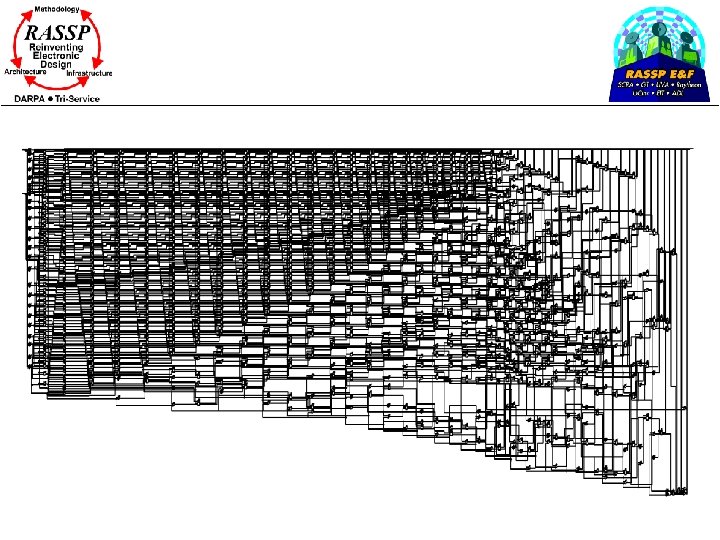

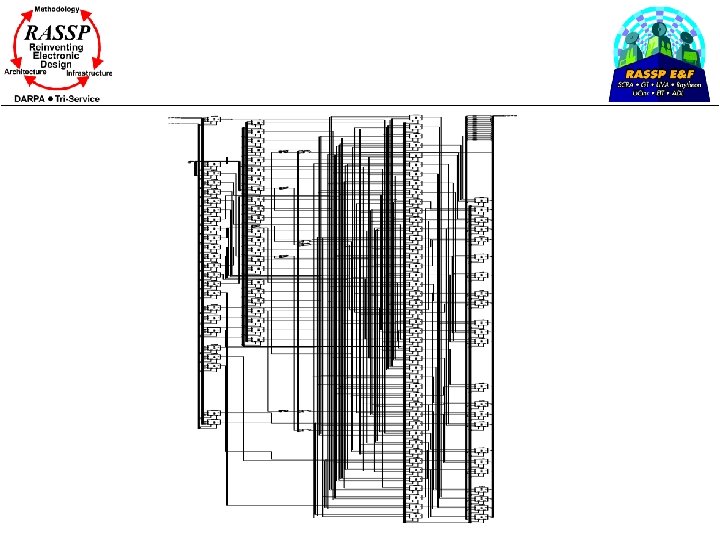

RTL Level Synthesis

RTL Level Synthesis

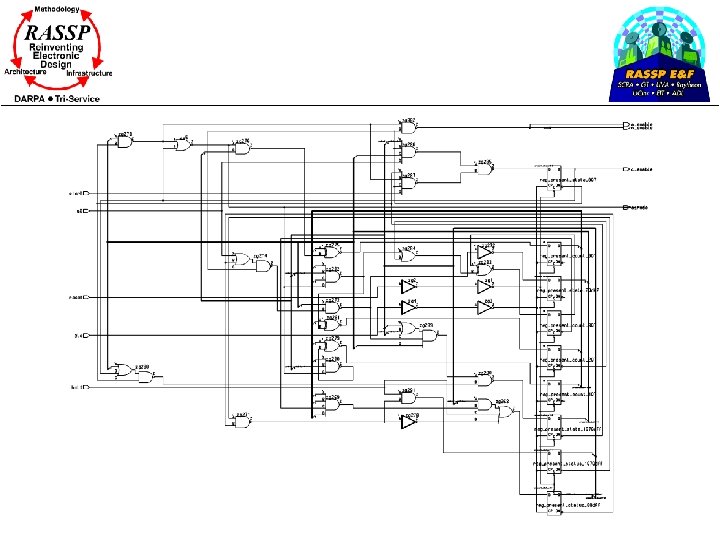

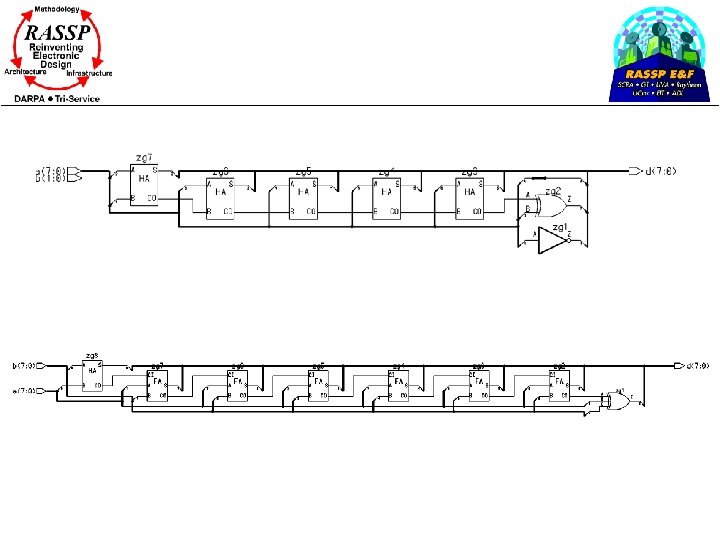

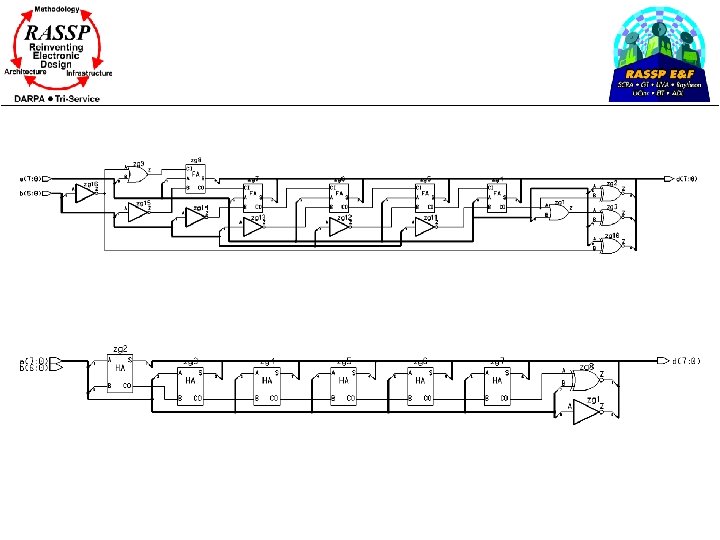

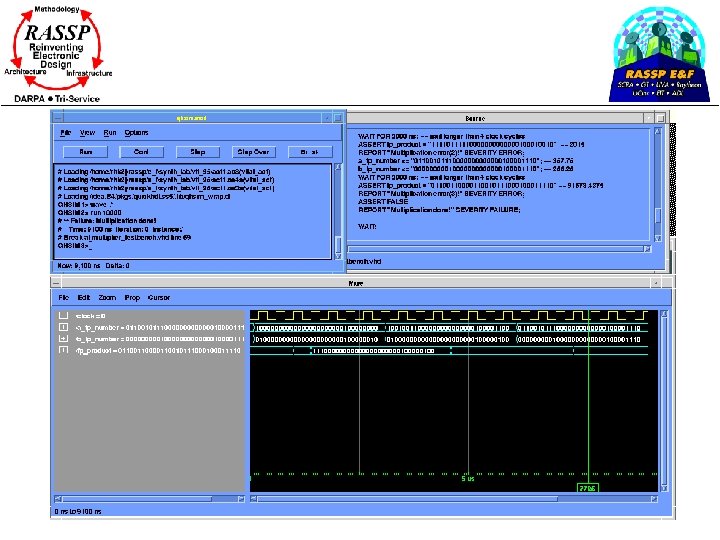

Floating Point Multiplier Code

Floating Point Multiplier Code

Floating Point Multiplier Code

Floating Point Multiplier Code

Floating Point Multiplier Code

Floating Point Multiplier Code

Floating Point Multiplier Code

Floating Point Multiplier Code

Floating Point Multiplier Code

Floating Point Multiplier Code

Module Outline

Module Outline

Structural VHDL

Structural VHDL

Module Outline

Module Outline

Implementation Technology Considerations

Implementation Technology Considerations

Module Outline

Module Outline

Summary

Summary

Summary (cont. )

Summary (cont. )

References

References