Лекция 03 Защищенный режим.ppt

- Количество слайдов: 28

Работа процессора в защищенном режиме Protected Mode

Режимы работы процессора

Цели разработки защищенного режима • Обеспечение многозадачности • Защита кодов и данных одновременно выполняемых программ друг от друга • Расширение адресного пространства • Возможность работы с непрерывными массивами данных длины более 64 Кбайт

Взаимодействие программ и операционной системы • В реальном режиме операционная система загружает программу в память и передает ей управление, а далее компьютер работает полностью под управлением программы пользователя (за исключением прерываний, когда операционная система временно берет управление на себя) • В защищенном режиме программы пользователя все время работают совместно с операционной системой и ждут разрешения операционной системы на выполнение

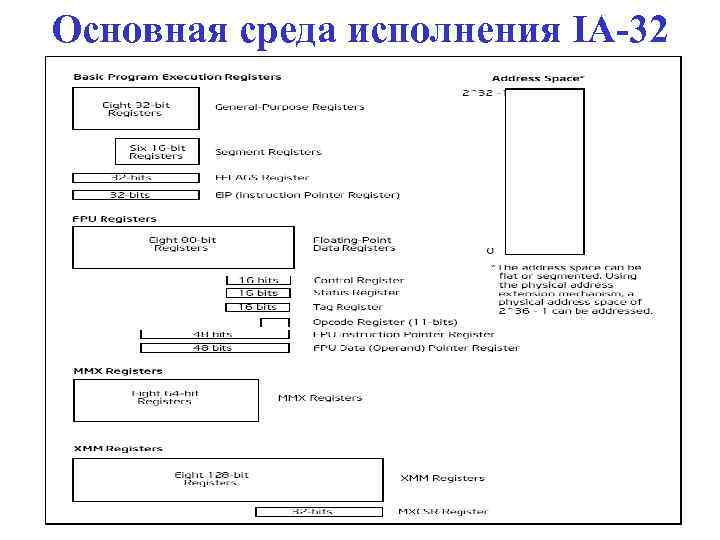

Основная среда исполнения IA-32

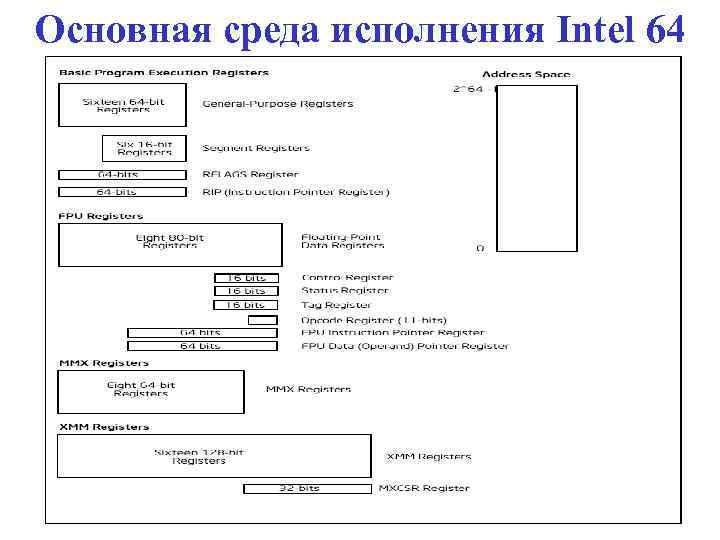

Основная среда исполнения Intel 64

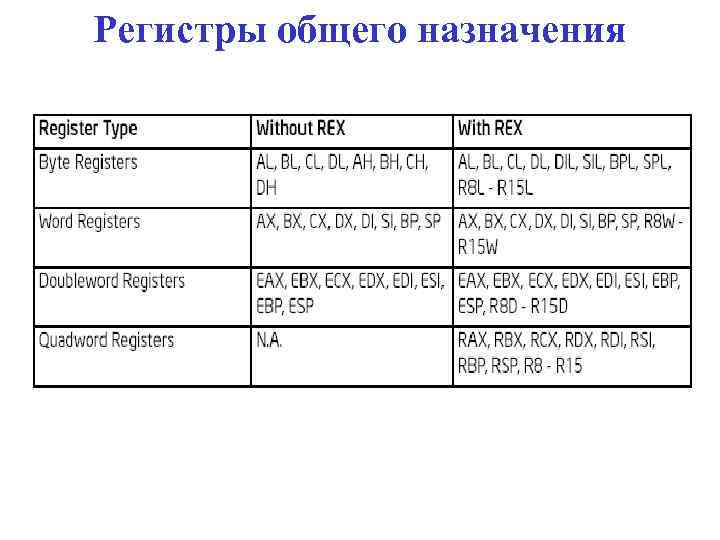

Регистры общего назначения

Регистр флагов EFLAGS

Регистры и структуры данных системного уровня в IA-32

Регистры и структуры данных системного уровня в IA-32 e

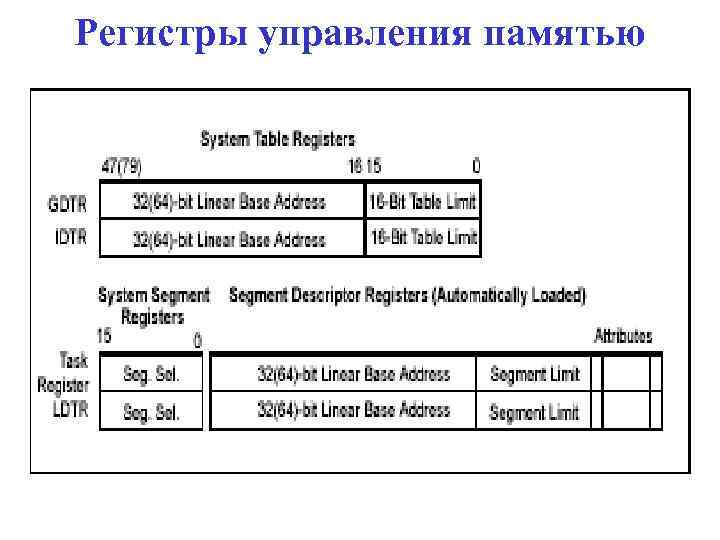

Регистры управления памятью

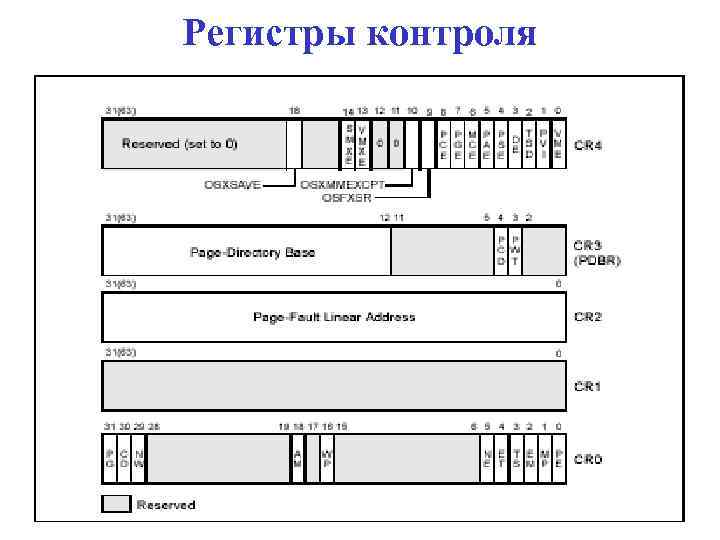

Регистры контроля

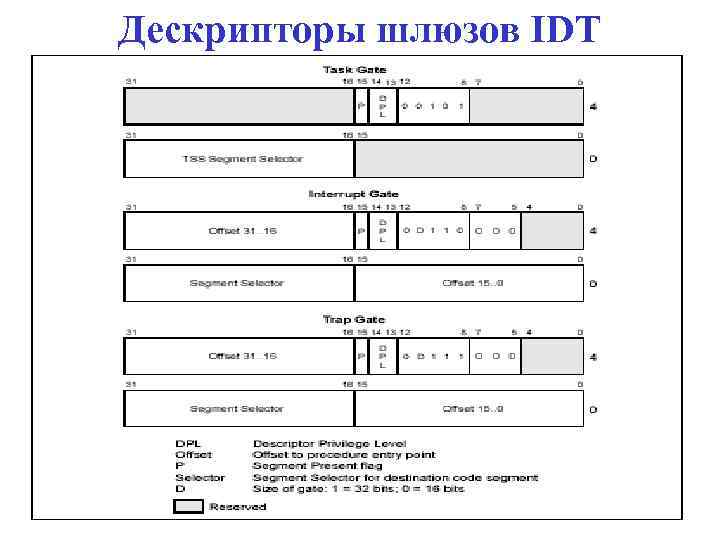

Дескрипторы шлюзов IDT

Исключения и прерывания защищенного режима

Вызов процедуры обработки прерывания

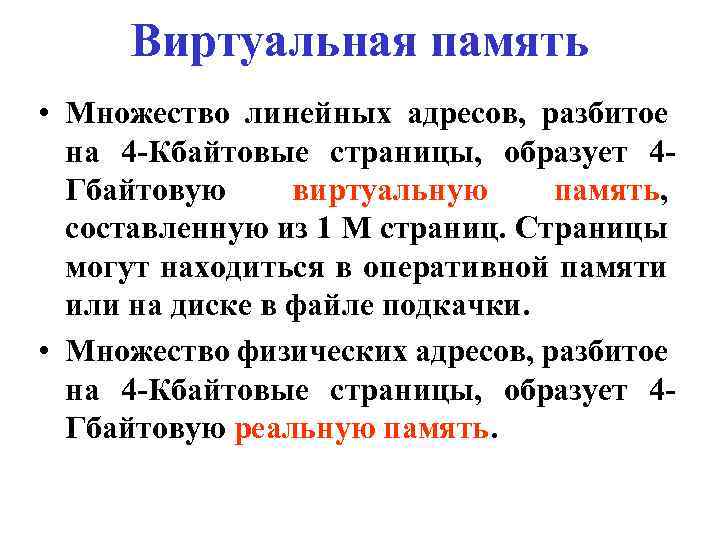

Виртуальная память • Множество линейных адресов, разбитое на 4 -Кбайтовые страницы, образует 4 Гбайтовую виртуальную память, составленную из 1 М страниц. Страницы могут находиться в оперативной памяти или на диске в файле подкачки. • Множество физических адресов, разбитое на 4 -Кбайтовые страницы, образует 4 Гбайтовую реальную память.

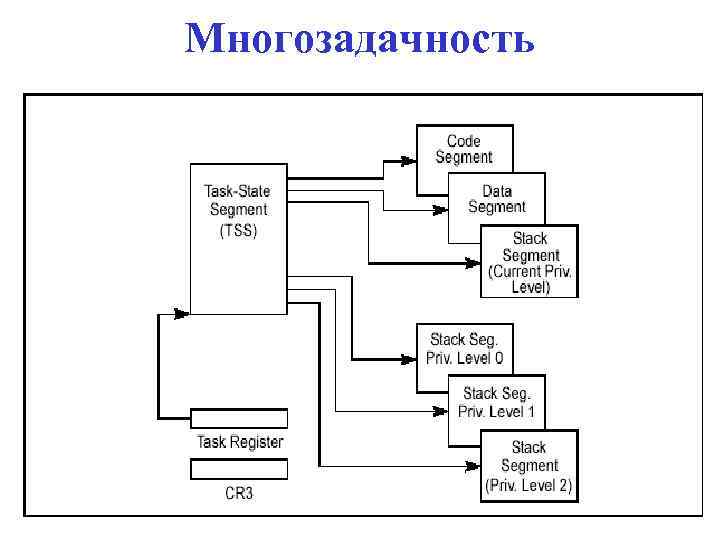

Многозадачность • Многозадачность – способность процессора выполнять несколько задач одновременно. • Задача – программа, которая выполняется или ожидает выполнения, пока выполняется другая задача, причем в определение задачи обычно включают ресурсы, требуемые для ее решения (объем памяти, процессорное время, дисковое пространство и др. ) • Контекст – информация о задаче, сохраняемая для последующего восстановления прерванного процесса.

Многозадачность Контексты сохраняются не в стеке, а в фиксированной (для каждой задачи) области памяти в специальной структуре данных, называемой сегментом состояния задачи (TSS), причем каждой задаче соответствует один TSS. Сегмент TSS определяется дескриптором, который может находиться только в GDT. Сегмент TSS не является ни сегментом кода, ни сегментом данных. Доступ к нему имеет только процессор, но не задача, даже на нулевом уровне! Если предполагается программно использовать сегмент TSS, то следует применить альтернативное именование.

Многозадачность

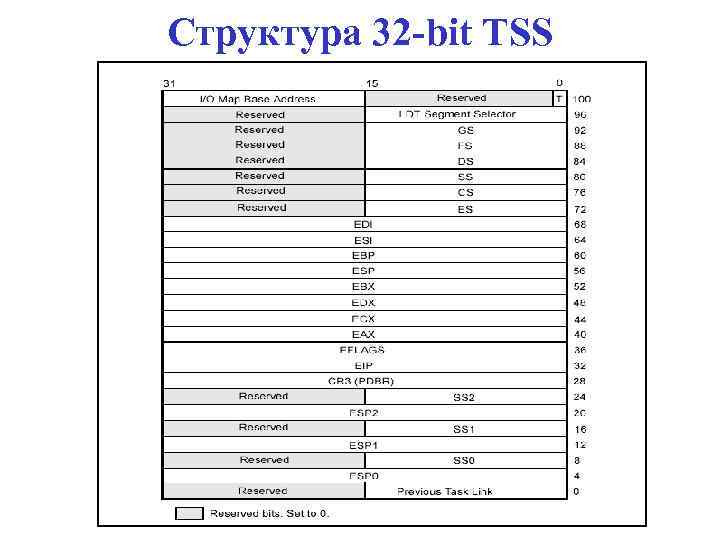

Структура 32 -bit TSS

Структура 32 -bit TSS 00 h – Обратная связь 04 h – Вершина стека (ESP). Кольцо 0 08 h – Начало стека. Кольцо 0 0 Ch – Вершина стека (ESP). Кольцо 1 10 h – Начало стека. Кольцо 1 14 h – Вершина стека (ESP). Кольцо 2 18 h – Начало стека. Кольцо 2 1 Ch – CR 3 20 h – EIP 24 h – EFLAGS 28 h – EAX 2 Ch – ECX 30 h – EDX 34 h – EBX 38 h – ESP 3 Ch – EBP 40 h – ESI 44 h – EDI 48 h – ES 4 Ch – CS 50 h – SS 54 h – DS 58 h – FS 5 Ch – GS 60 h – LDTR …

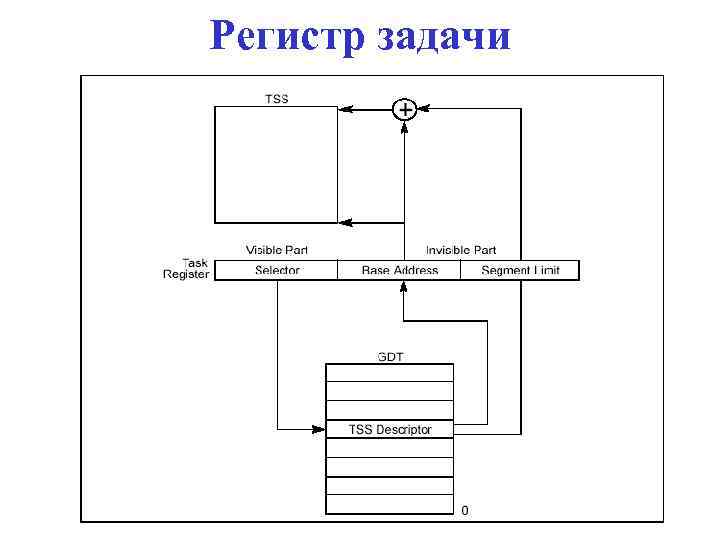

Переключение задач • • • Task Status Segment – сегмент состояния задачи TSS Descriptor – дескриптор TSS Task Register – регистр задачи Task Gate Descriptor – дескриптор шлюза задачи CR 3 – управляющий регистр. Содержит базовый физический адрес каталога страниц, используемых задачей

Переключение задач • • Переключение задачи могут вызывать следующие четыре события: Старая задача выполняет команду FAR CALL или FAR JMP, и селектор выбирает шлюз задачи; Старая задача выполняет команду FAR CALL или FAR JMP, и селектор выбирает дескриптор TSS; Старая задача выполняет команду IRET для возврата в предыдущую задачу; эта команда приводит в переключению задачи, если в регистре FLAGS бит вложенности задачи NT=1; Возникло аппаратное или программное прерывание и соответствующий элемент IDT содержит шлюз задачи.

Переключение задач • • • Процесс переключения задачи можно представить следующим образом: Процессор сохраняет контекст старой задачи в сегменте TSS старой задачи; Процессор загружает в TR селектор сегмента новой задачи; Процессор загружает в сегмент TSS новой задачи селектор TSS старой задачи (в поле обратной связи); Получив доступ к сегменту TSS новой задачи, процессор загружает контекст новой задачи в регистры (в том числе CS: EIP – точка старта) Процессор устанавливает флаги NT (в регистре EFLAGS) и TS (в CR 0 для анализа командами FPU), устанавливает бит занятости задачи в дескрипторе TSS новой задачи.

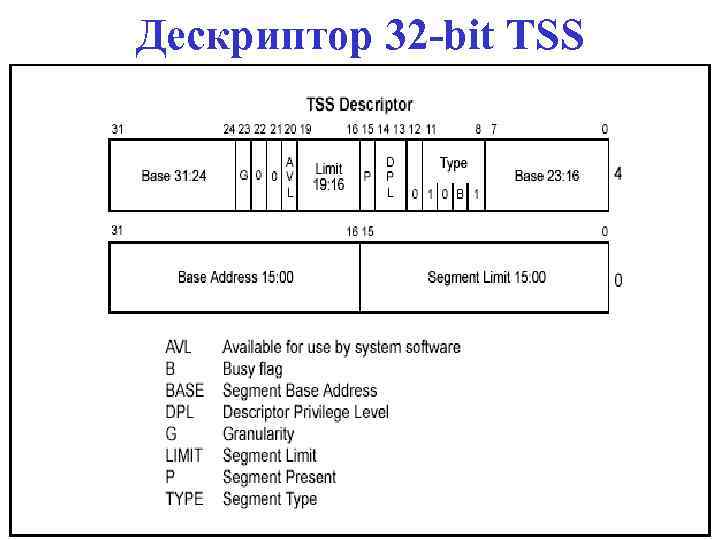

Дескриптор 32 -bit TSS

Регистр задачи

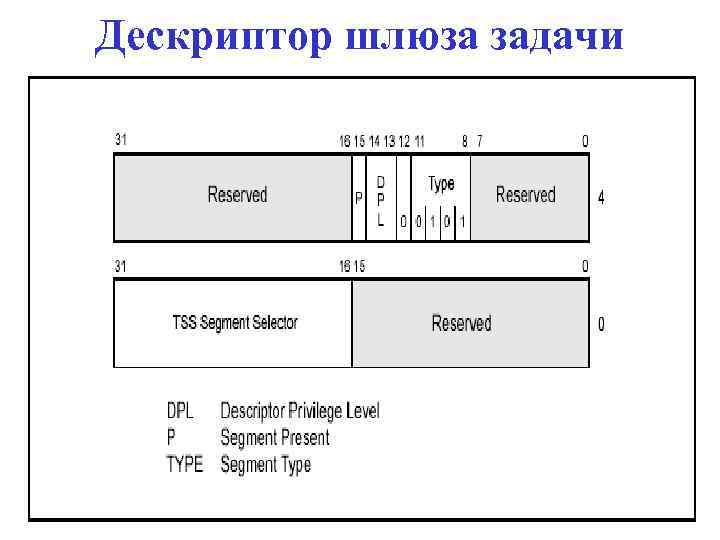

Дескриптор шлюза задачи

Прерывание переключения задачи

Лекция 03 Защищенный режим.ppt