ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВА Блок-схема ПЛУ

ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВА

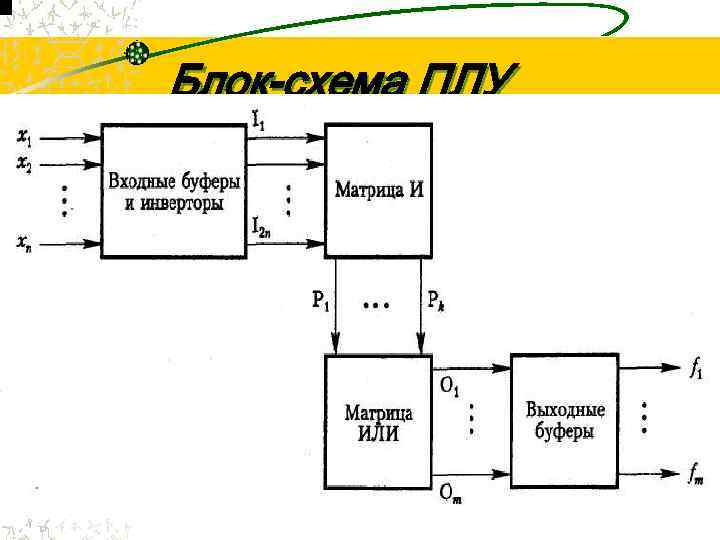

Блок-схема ПЛУ 2

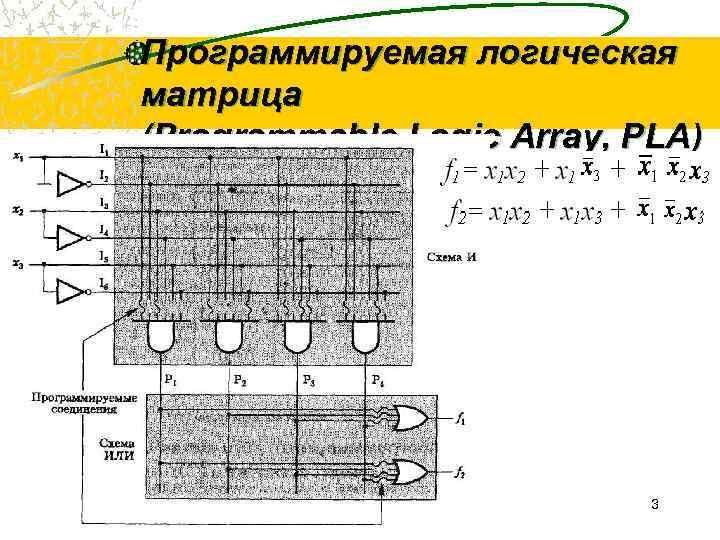

Программируемая логическая матрица (Programmable Logic Array, PLA) 3

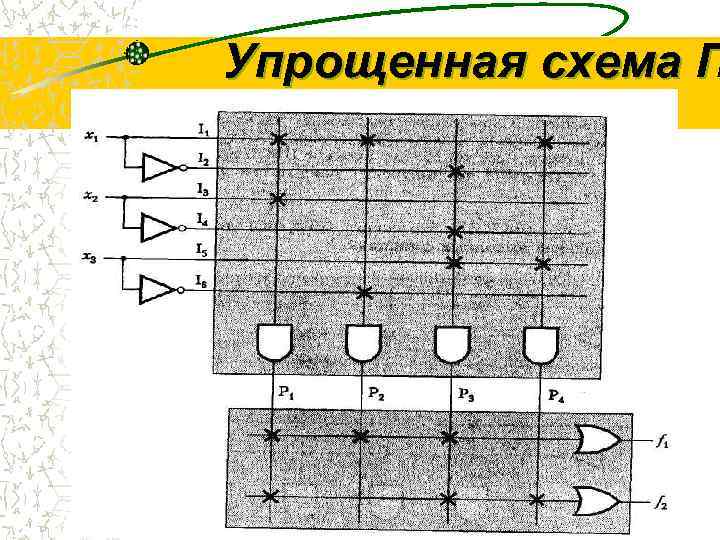

Упрощенная схема П 4

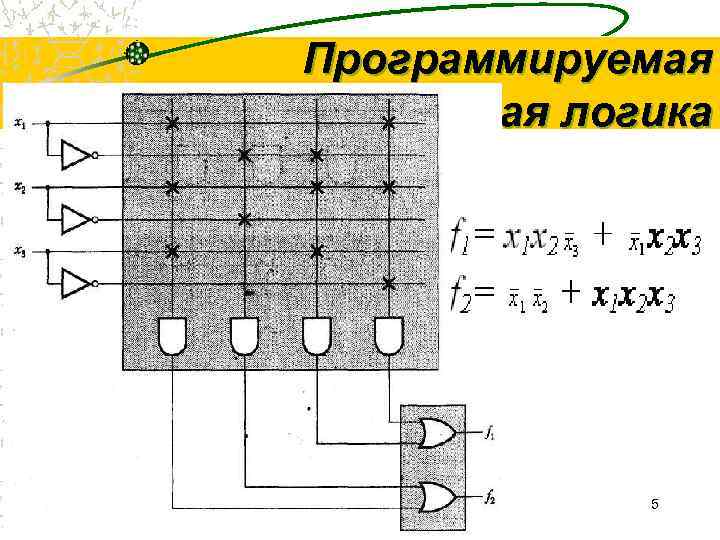

Программируемая матричная логика 5

Пример обработки выходного сигнала ПМЛ- элемента 6

Сложные программируемые логические устройства 7

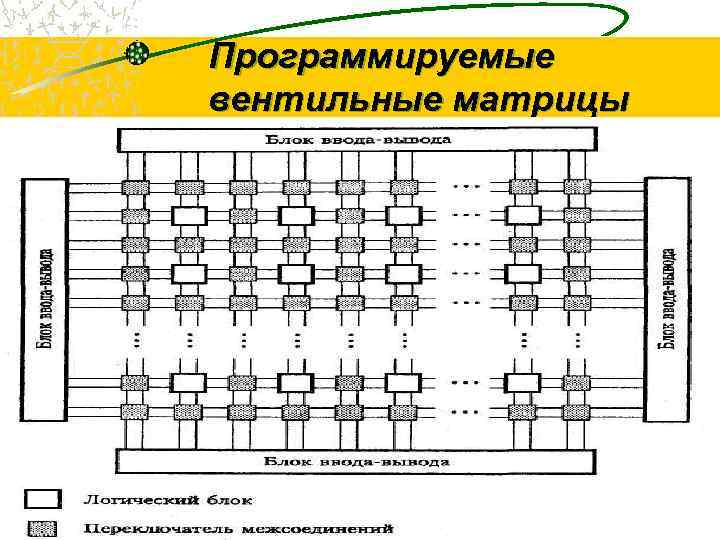

Программируемые вентильные матрицы 8

Пример счетчика с прямым / обратным счетом 9

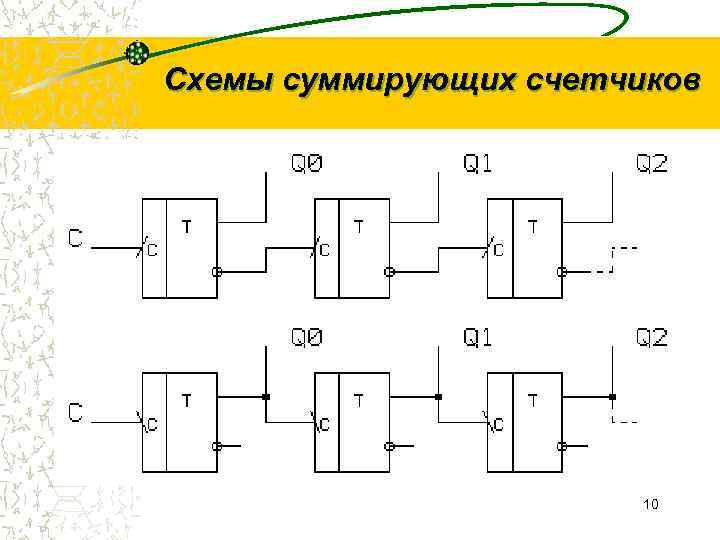

Схемы суммирующих счетчиков 10

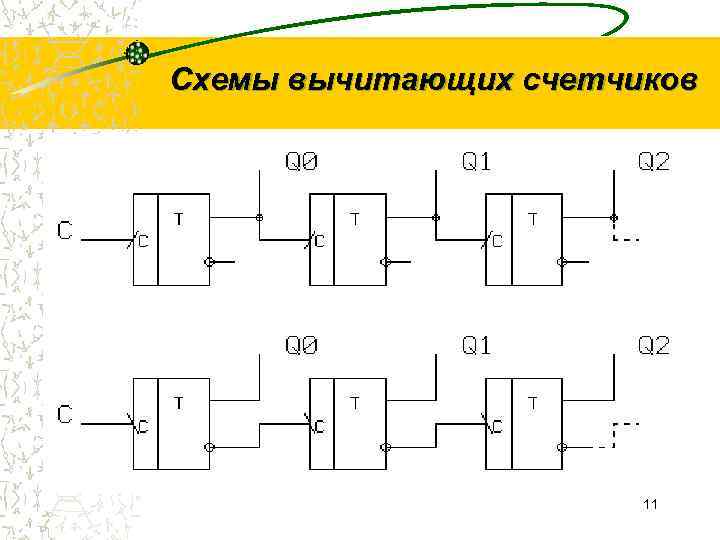

Схемы вычитающих счетчиков 11

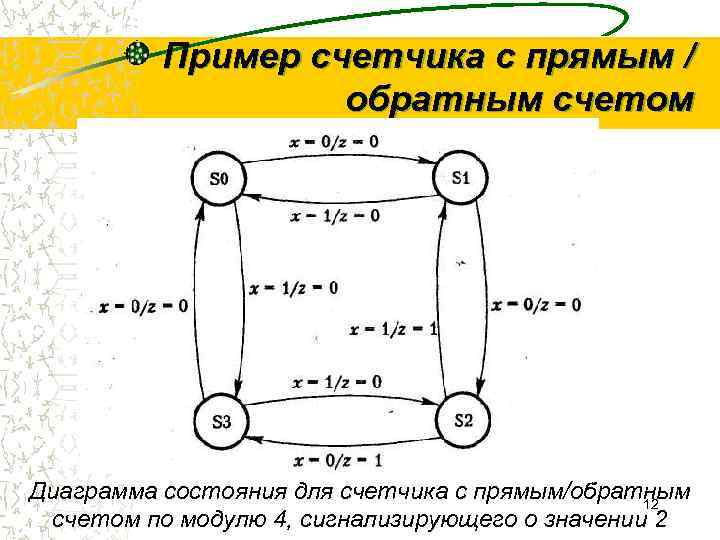

Пример счетчика с прямым / обратным счетом Диаграмма состояния для счетчика с прямым/обратным 12 счетом по модулю 4, сигнализирующего о значении 2

Состояния для счетчика с прямым / обратным счетом 13

Реализация счетчика с прямым / обратным счетом 14

Фрагмент схемы реверсивного счетчика 15

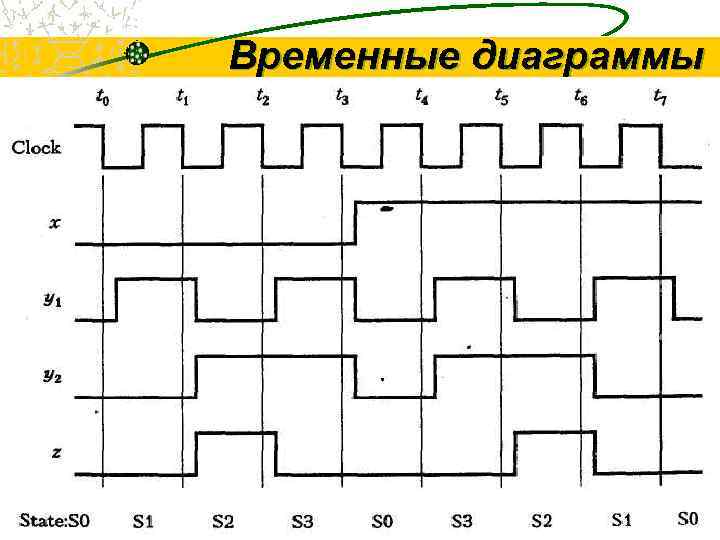

Временные диаграммы 16

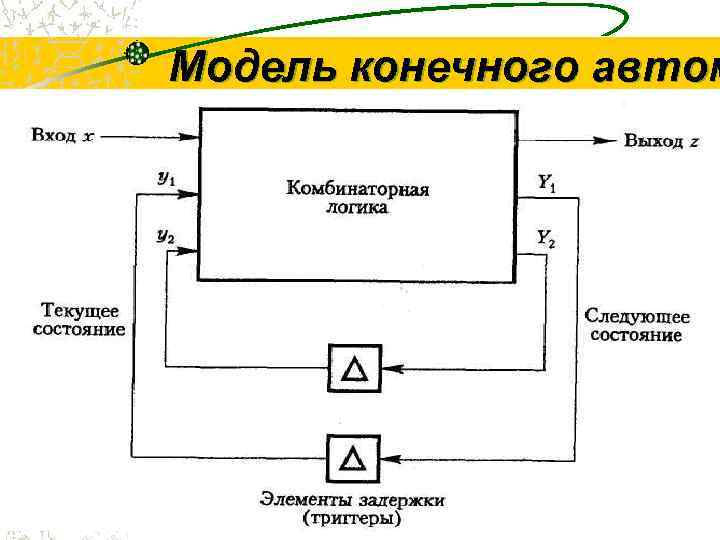

Модель конечного автом 17

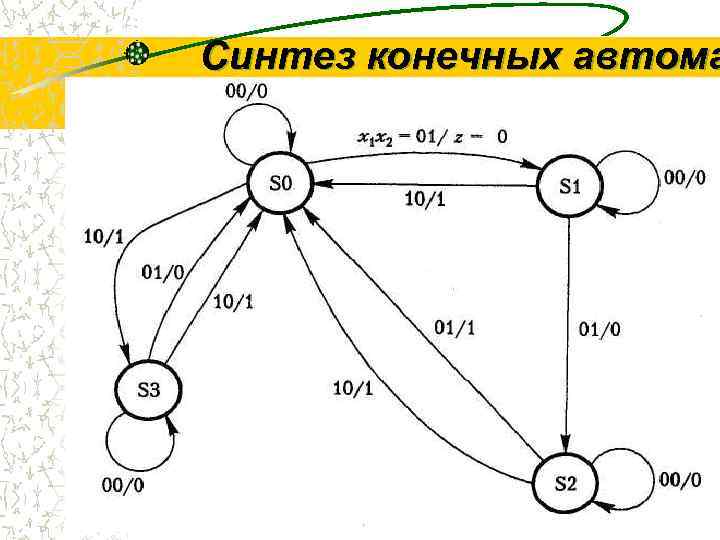

Синтез конечных автома 18

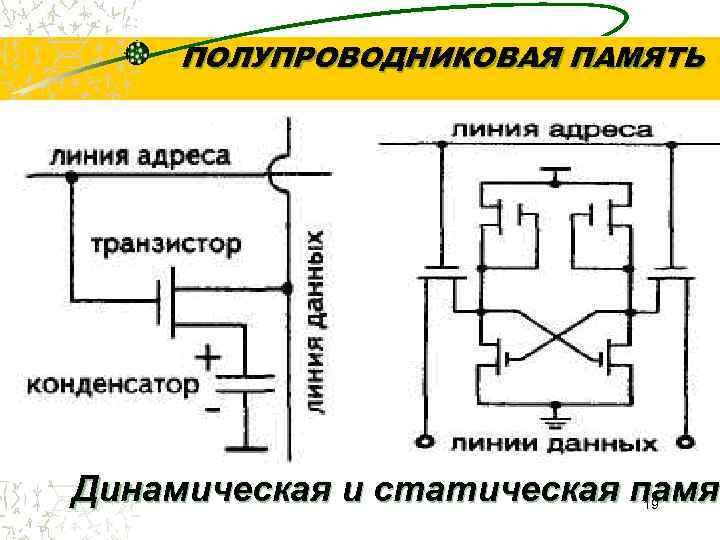

ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ Динамическая и статическая памят памя 19

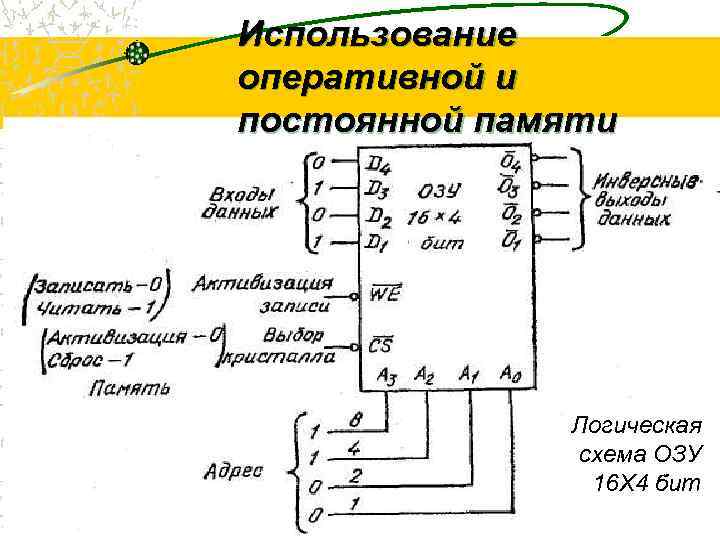

Использование оперативной и постоянной памяти 20

Использование оперативной и постоянной памяти Логическая схема ОЗУ 16 X 4 бит 21

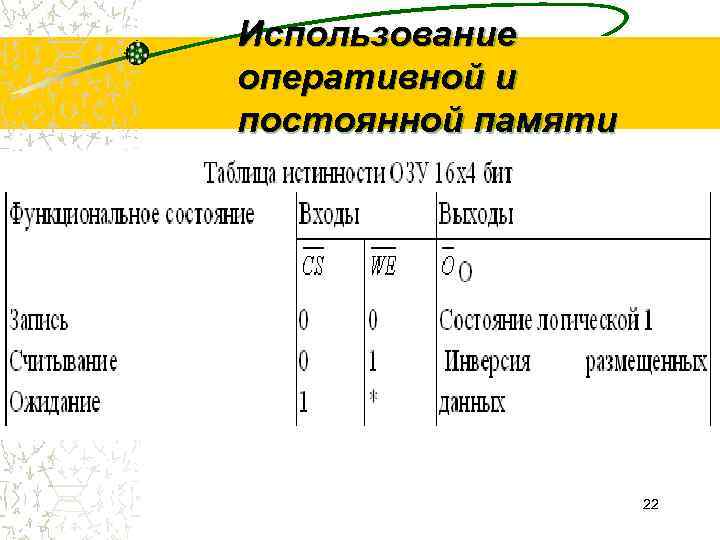

Использование оперативной и постоянной памяти 22

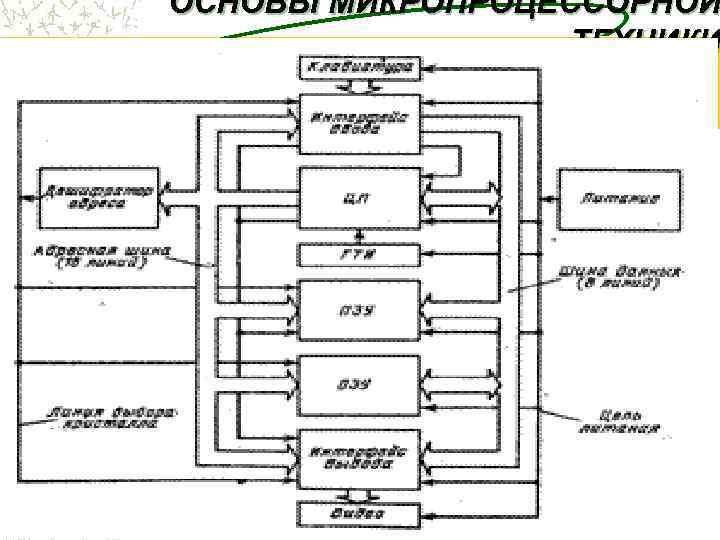

ОСНОВЫ МИКРОПРОЦЕССОРНОЙ ТЕХНИКИ 23

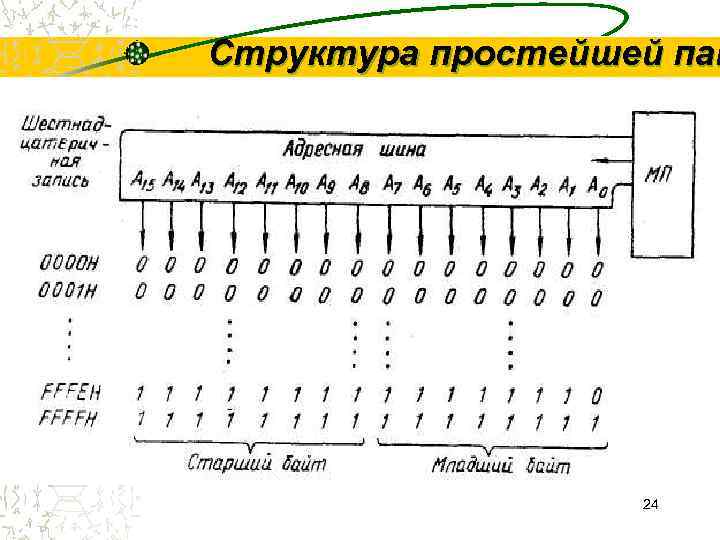

Структура простейшей пам 24

Способы формирования памяти микро-ЭВМ 25 а одном кристалле; б—на двух кристаллах: в—на восьми крист

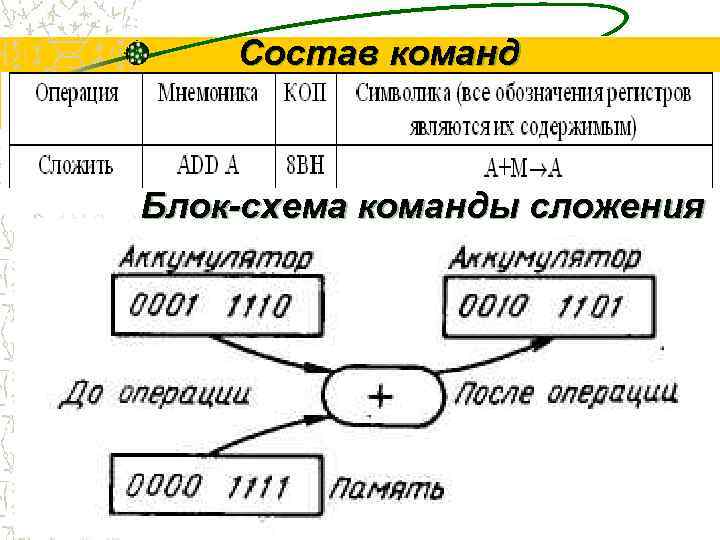

Состав команд Блок-схема команды сложения 26

Структура элементарного микропроцессора 27

Структура элементарного микропроцессора 28 Выполнение операции ADD (а) и структура АЛУ (б)

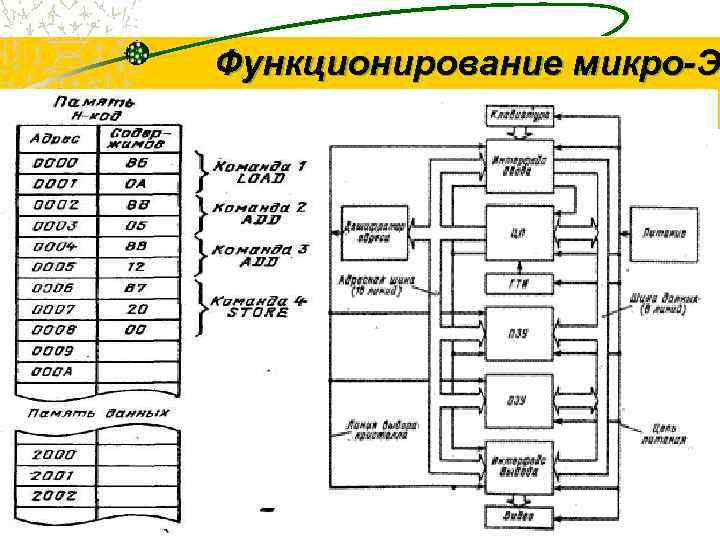

Функционирование микро-Э 29

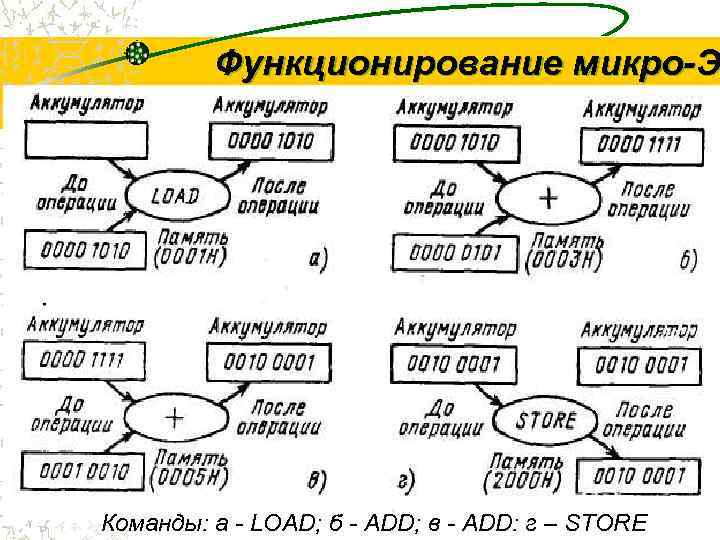

Функционирование микро-Э 30 Команды: a - LOAD; б - ADD; в - ADD: г – STORE

Подробный анализ команды LOAD непосредственных 31

Код коррекции ошибок (Error Correcting Code — позволяют не только обнаружить. ЕСС) ошибку, но и исправить ее в одном Реализация кода коррекции ошибок разряде. при 4 -байтовой организации, очевидно, дороже реализации проверки нечетности или четности, но при 8 -байтовой организации стоимость реализации кода коррекции ошибок 32 не превышает стоимости

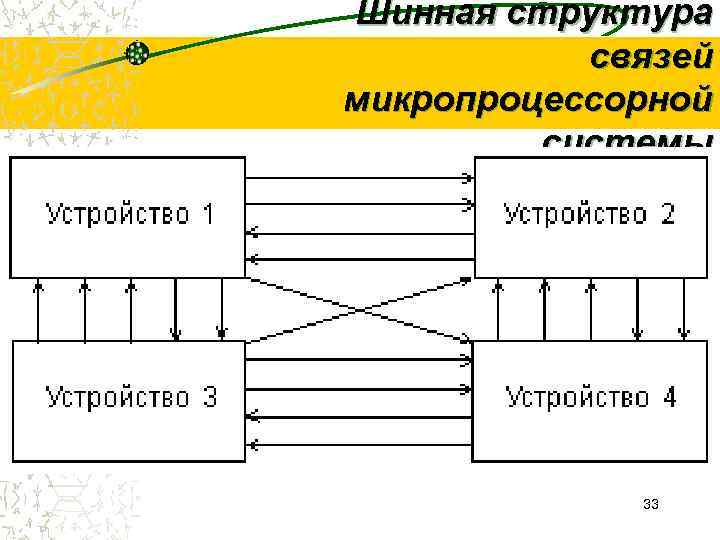

Шинная структура связей микропроцессорной системы 33

Шинная структура связей микропроцессорной системы 34

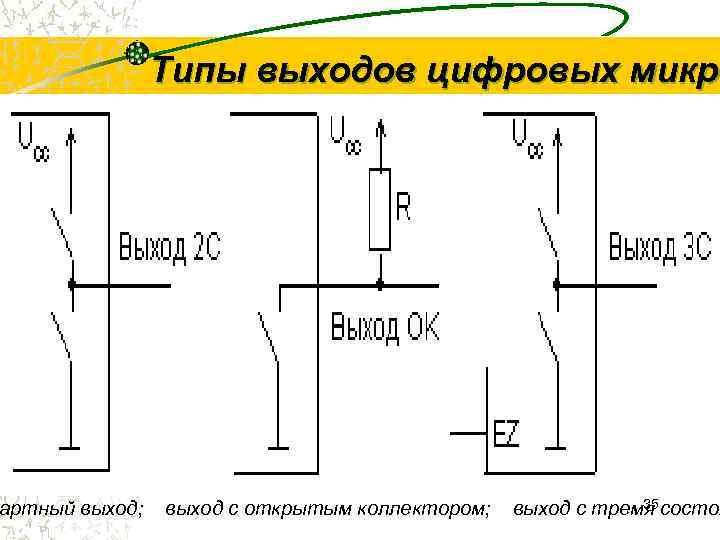

Типы выходов цифровых микро артный выход; выход с открытым коллектором; 35 выход с тремя состоя

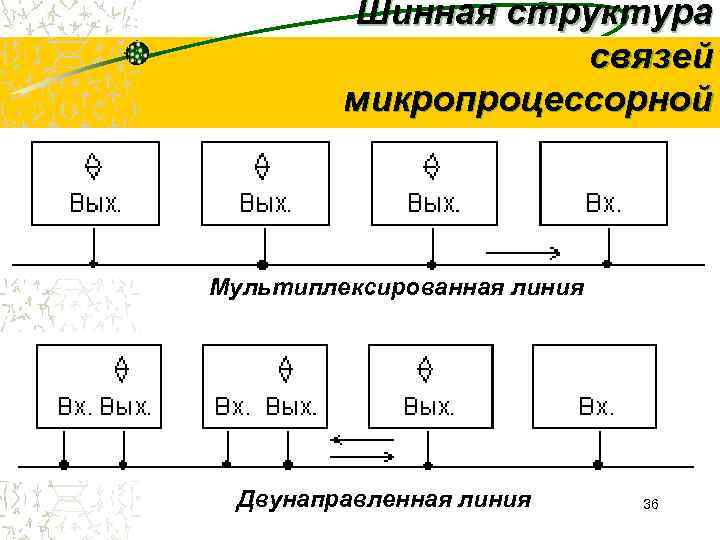

Шинная структура связей микропроцессорной системы Мультиплексированная линия Двунаправленная линия 36

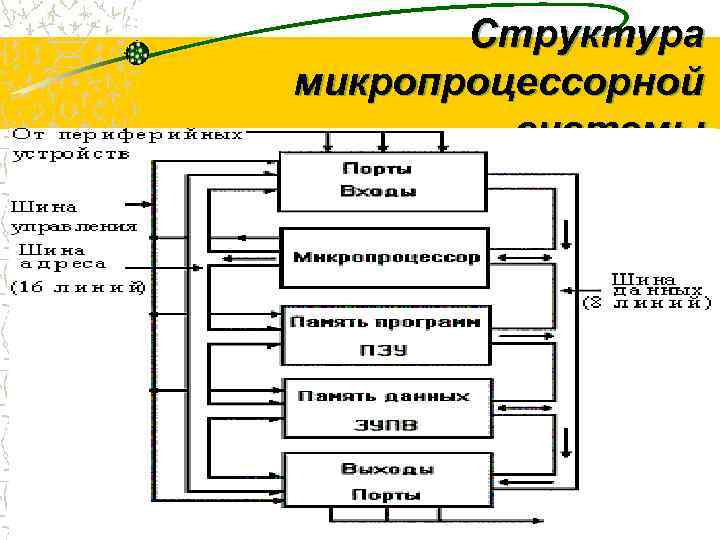

Структура микропроцессорной системы 37

Логическая структура микропроцессора 38

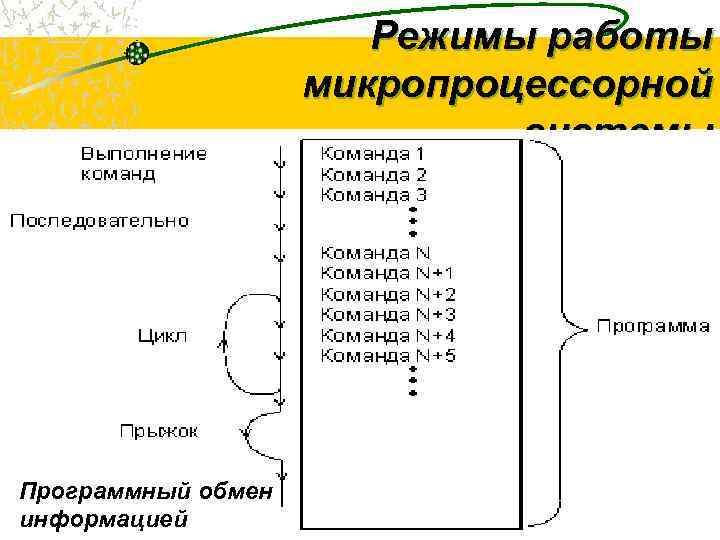

Режимы работы микропроцессорной системы Программный обмен 39 информацией

Режимы работы микропроцессорной системы Обслуживание прерывания 40

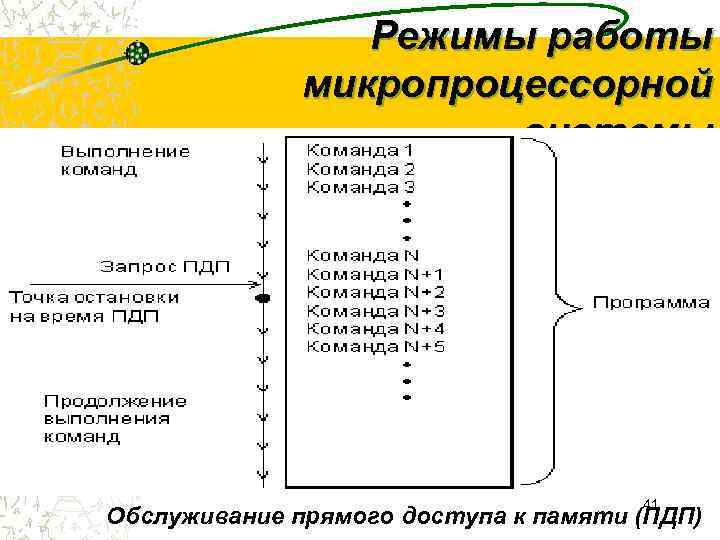

Режимы работы микропроцессорной системы 41 Обслуживание прямого доступа к памяти (ПДП)

Режимы работы микропроцессорной системы Информационные потоки в режиме прямого доступа к па 42

Типы микропроцессорных си Основные типы следующие: • микроконтроллеры — наиболее простой тип микропроцессорных систем, в которых все или большинство узлов системы выполнены в виде одной микросхемы; • контроллеры — управляющие микропроцессорные системы, выполненные в виде отдельных модулей; • микрокомпьютеры — более мощные микропроцессорные системы с развитыми средствами сопряжения с внешними устройствами. • компьютеры (в том числе персональные) — самые мощные и наиболее универсальные 43 микропроцессорные системы.

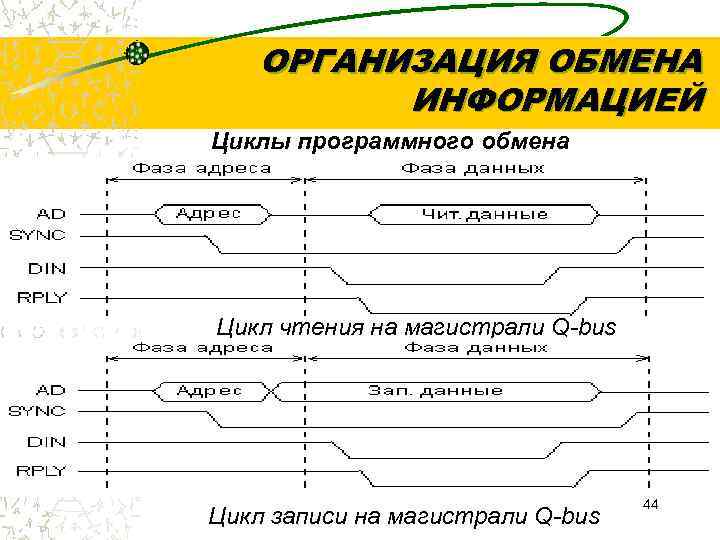

ОРГАНИЗАЦИЯ ОБМЕНА ИНФОРМАЦИЕЙ Циклы программного обмена Цикл чтения на магистрали Q-bus 44 Цикл записи на магистрали Q-bus

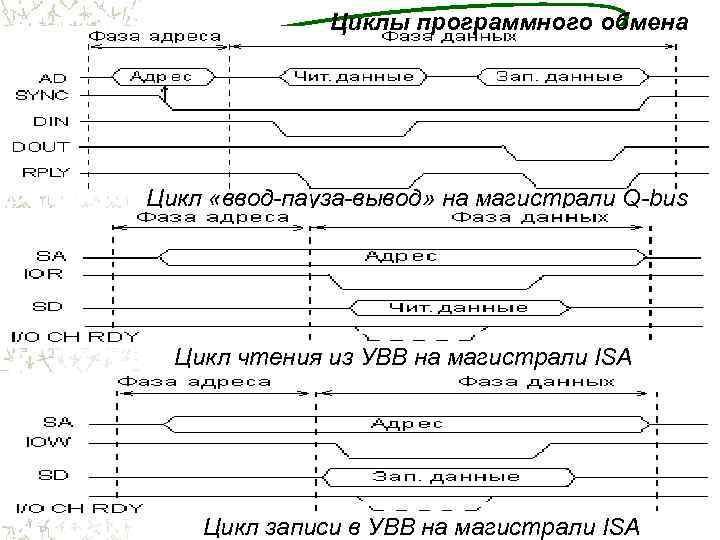

Циклы программного обмена Цикл «ввод-пауза-вывод» на магистрали Q-bus Цикл чтения из УВВ на магистрали ISA 45 Цикл записи в УВВ на магистрали ISA

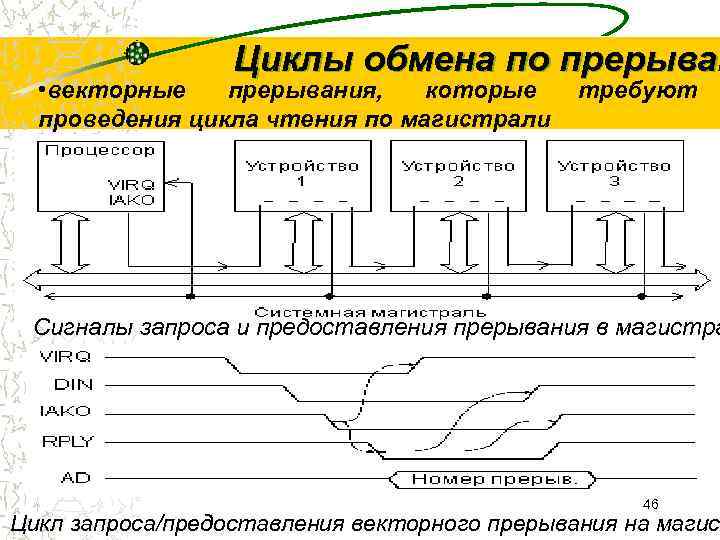

Циклы обмена по прерыван • векторные прерывания, которые требуют проведения цикла чтения по магистрали Сигналы запроса и предоставления прерывания в магистра 46 Цикл запроса/предоставления векторного прерывания на магис

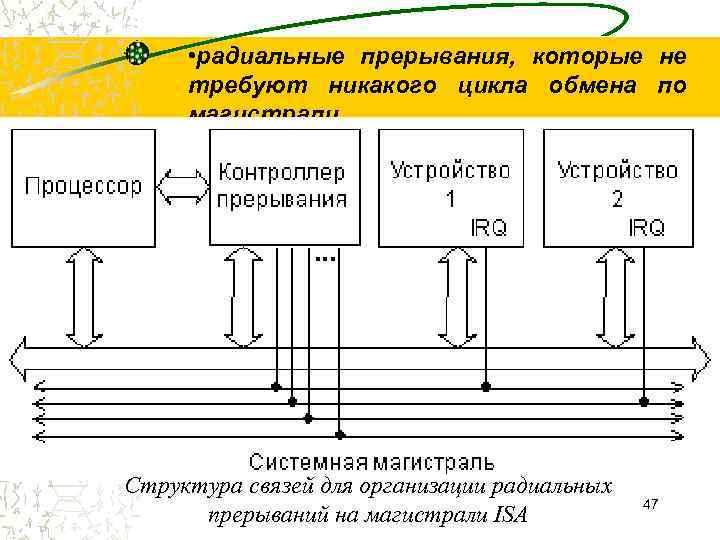

• радиальные прерывания, которые не требуют никакого цикла обмена по магистрали. Структура связей для организации радиальных 47 прерываний на магистрали ISA

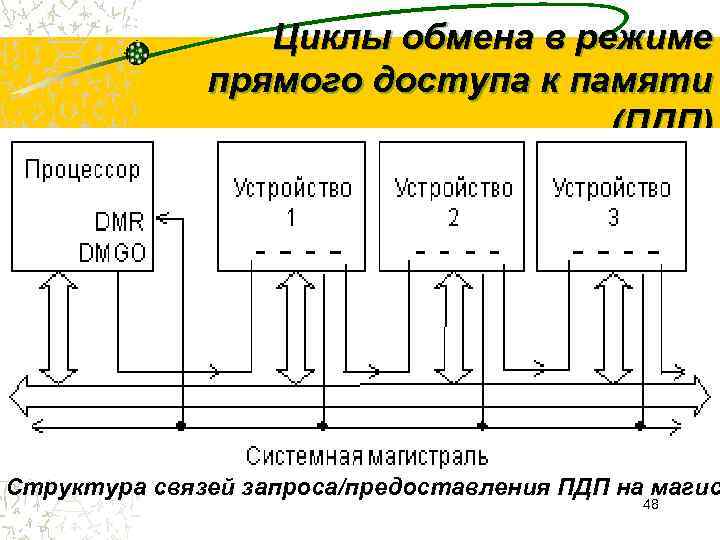

Циклы обмена в режиме прямого доступа к памяти (ПДП) Структура связей запроса/предоставления ПДП на магис 48

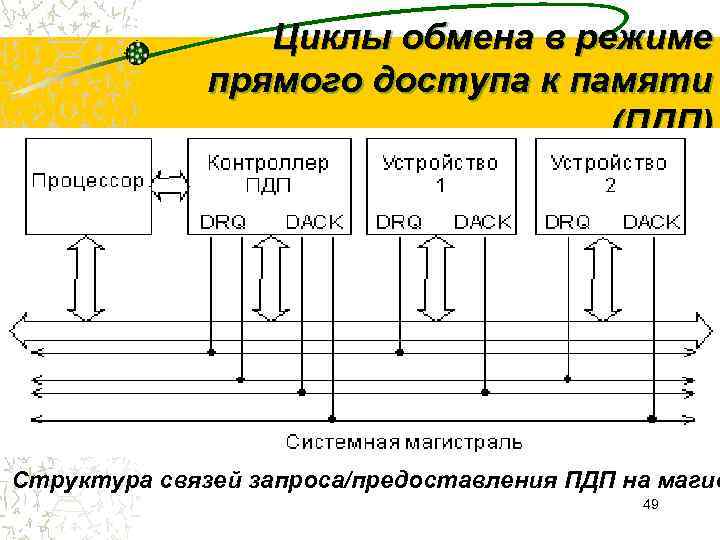

Циклы обмена в режиме прямого доступа к памяти (ПДП) Структура связей запроса/предоставления ПДП на магис 49

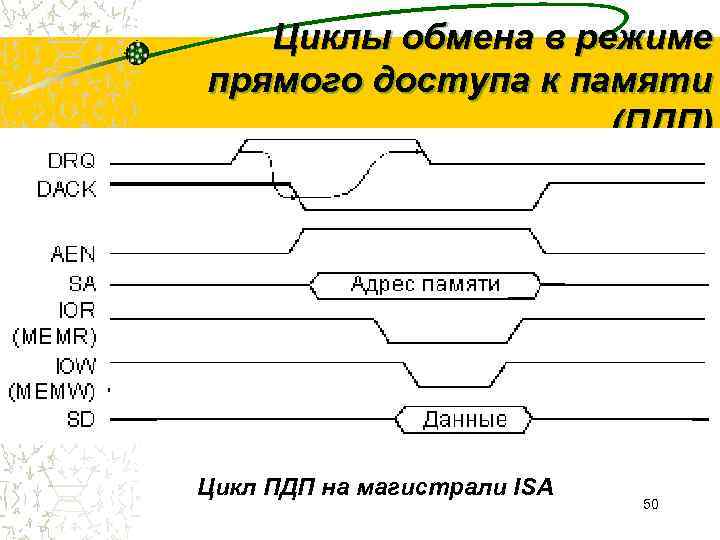

Циклы обмена в режиме прямого доступа к памяти (ПДП) Цикл ПДП на магистрали ISA 50

Прохождение сигналов по магис 51

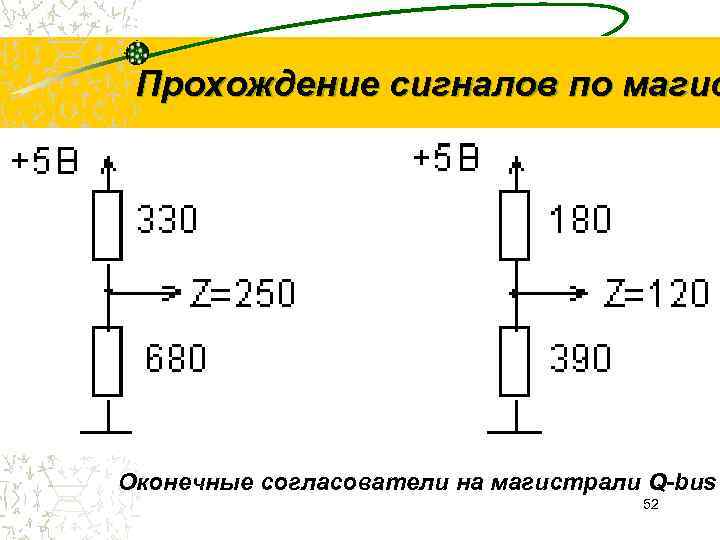

Прохождение сигналов по магис Оконечные согласователи на магистрали Q-bus 52

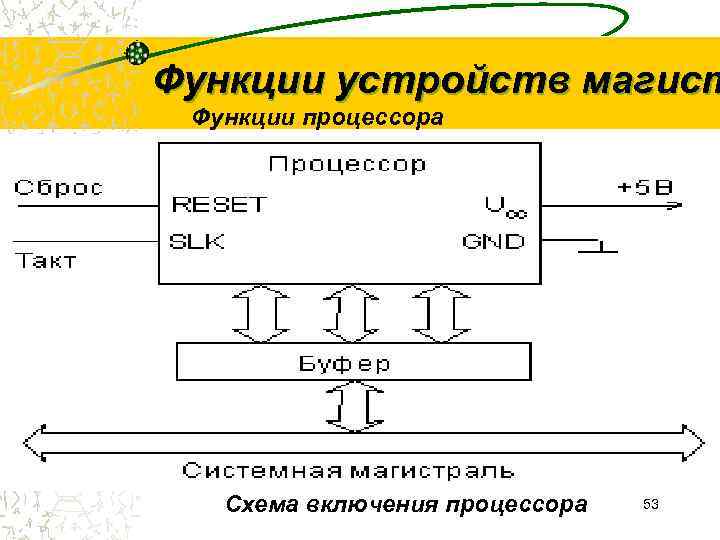

Функции устройств магист Функции процессора Схема включения процессора 53

Внутренняя структура микропроцессора 54

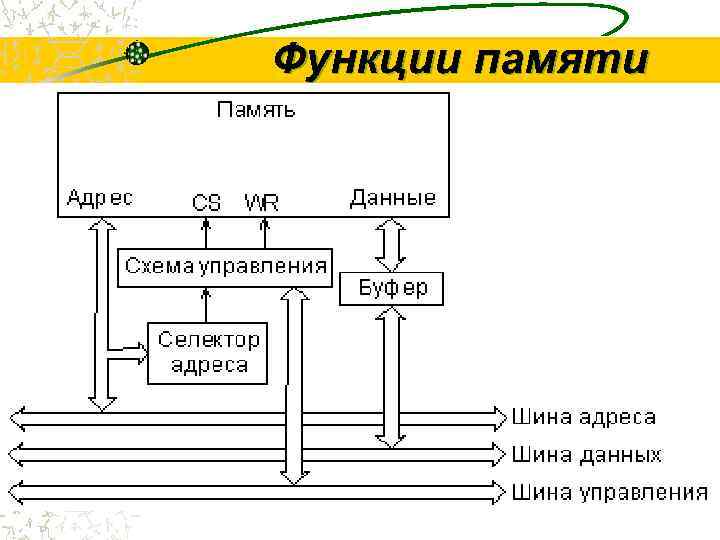

Функции памяти 55

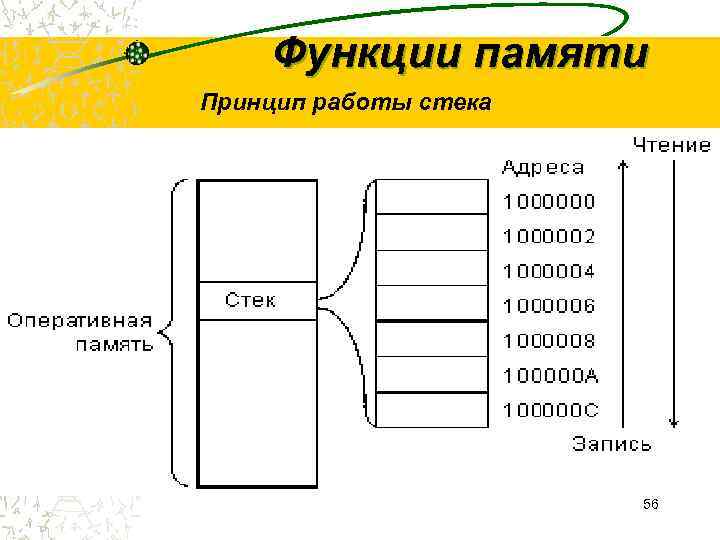

Функции памяти Принцип работы стека 56

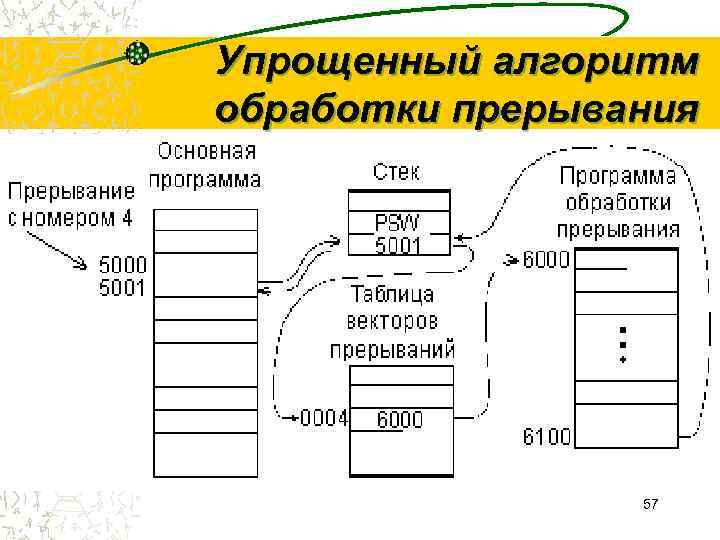

Упрощенный алгоритм обработки прерывания 57

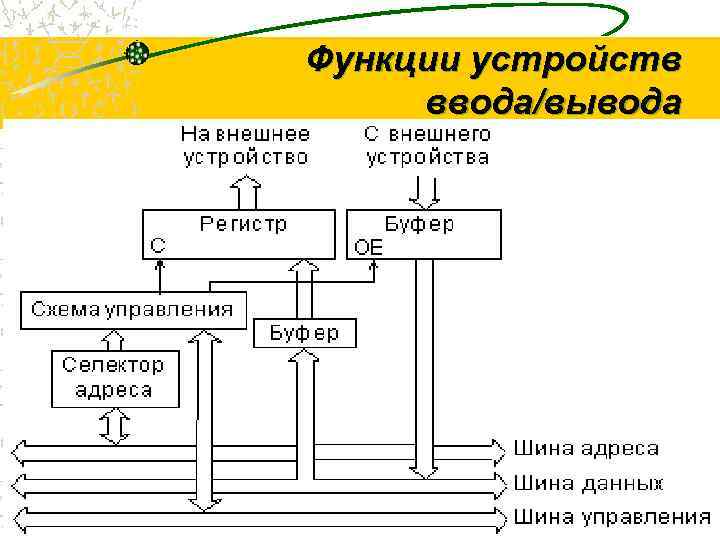

Функции устройств ввода/вывода 58

ФУНКЦИОНИРОВАНИЕ ПРОЦЕС Адресация операндов. Методы адр • Непосредственная адресация • Регистровая адресация адресация • Прямая • Косвенно-регистровая адрес 59

Сегментирование памя 60

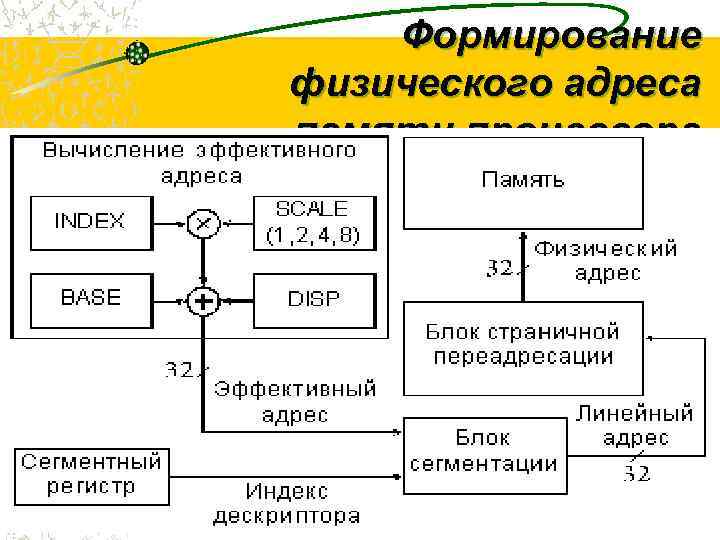

Формирование физического адреса памяти процессора 61

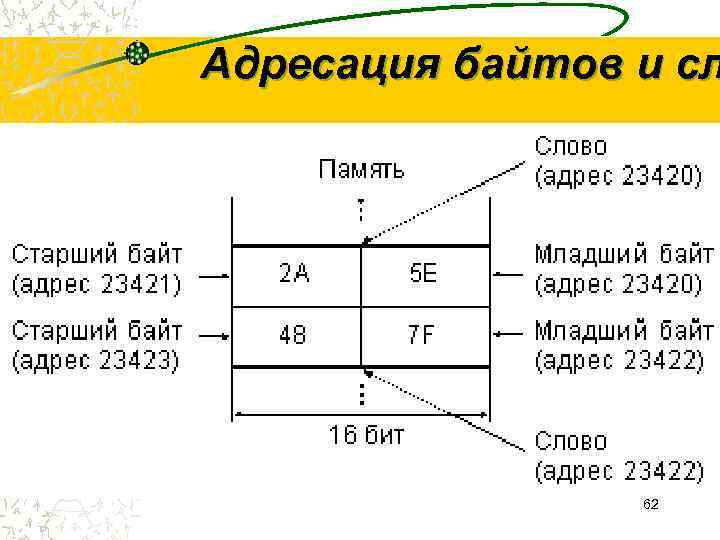

Адресация байтов и сл 62

ОРГАНИЗАЦИЯ МИКРОКОНТРОЛЛЕ РОВ 63

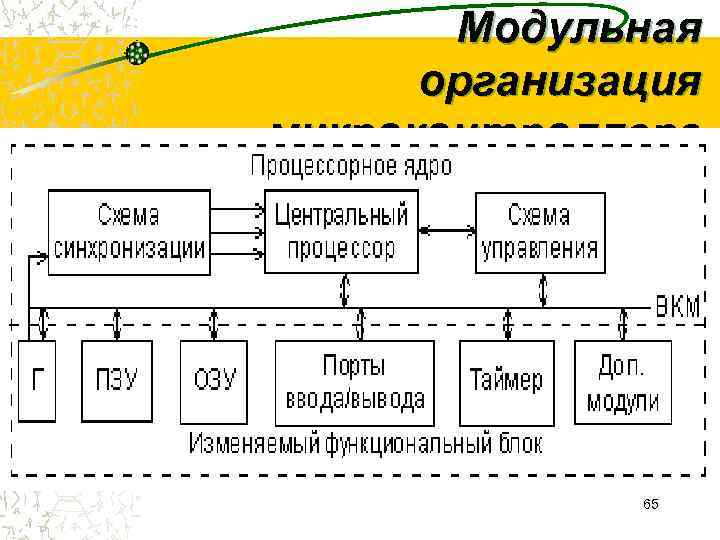

микроконтроллеров: • модульная организация, при которой на базе одного процессорного ядра (центрального процессора) проектируется ряд (линейка) МК, различающихся объемом и типом памяти программ, объемом памяти данных, набором периферийных модулей, частотой синхронизации; • использование закрытой архитектуры МК, которая характеризуется отсутствием линий магистралей адреса и данных на выводах корпуса МК. Таким образом, МК представляет собой законченную систему обработки данных, наращивание возможностей которой с использованием параллельных магистралей адреса и данных не предполагается; • использование типовых функциональных периферийных модулей (таймеры, процессоры событий, контроллеры последовательных интерфейсов, аналого-цифровые преобразователи и др. ), имеющих незначительные отличия в алгоритмах работы в МК различных производителей; 64 • расширение числа режимов работы периферийных

Модульная организация микроконтроллера 65

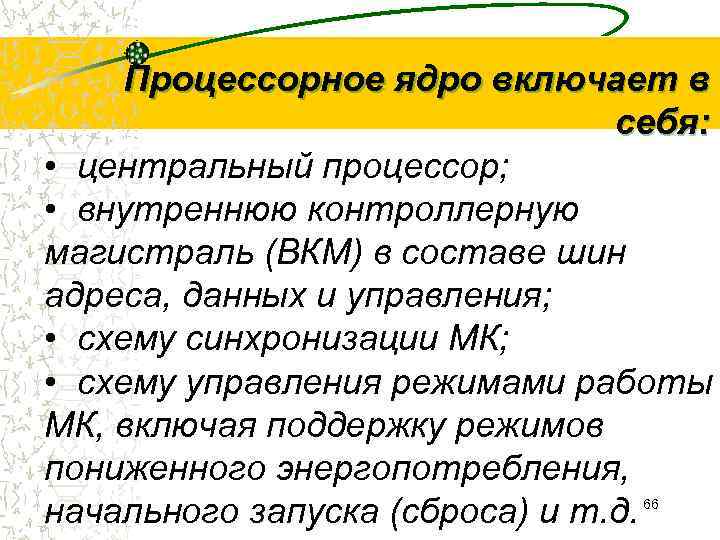

Процессорное ядро включает в себя: • центральный процессор; • внутреннюю контроллерную магистраль (ВКМ) в составе шин адреса, данных и управления; • схему синхронизации МК; • схему управления режимами работы МК, включая поддержку режимов пониженного энергопотребления, начального запуска (сброса) и т. д. 66

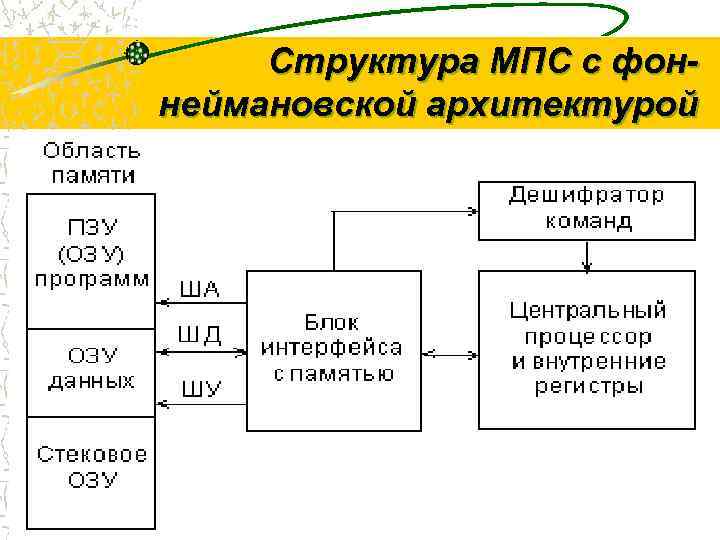

Структура МПС с фон- неймановской архитектурой 67

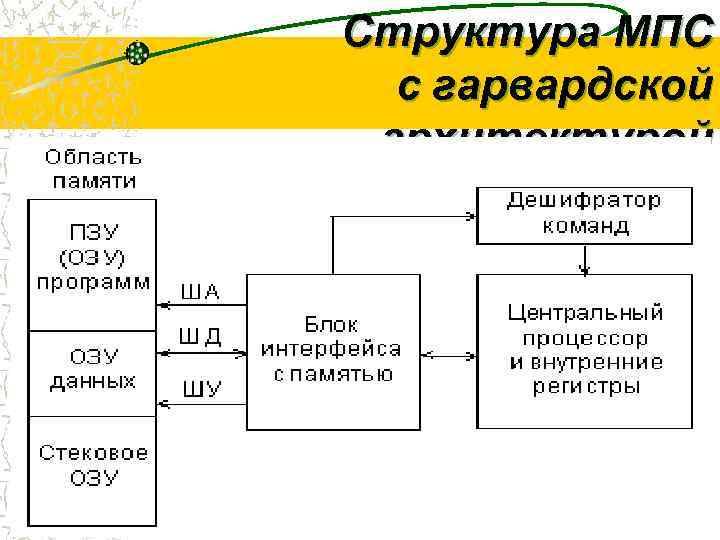

Структура МПС с гарвардской архитектурой

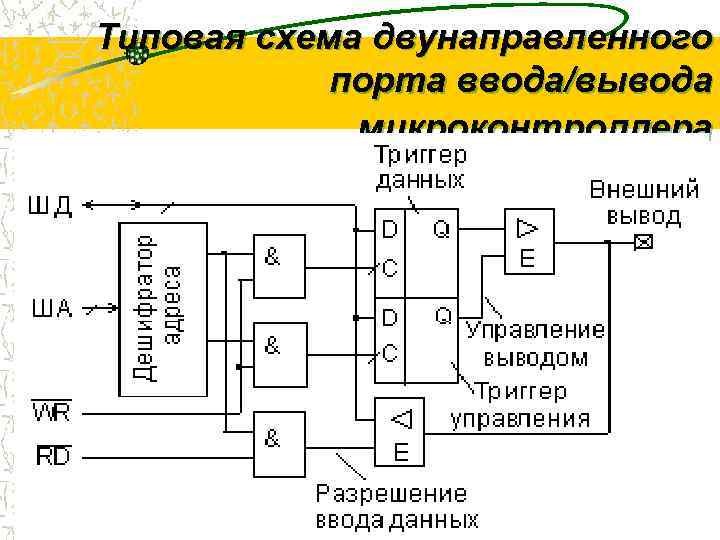

Типовая схема двунаправленного порта ввода/вывода микроконтроллера 69

ИИТ и Э. Тема 3 - лекции от 06.09.11.ppt

- Количество слайдов: 69