5. Временные характеристики синхронных схем.pptx

- Количество слайдов: 30

Проектирование цифровых устройств на языке VHDL Временные характеристики синхронных схем 1

Проектирование цифровых устройств на языке VHDL Временные характеристики синхронных схем 1

Основные временные характеристики регистров 2

Основные временные характеристики регистров 2

Временные характеристики триггеров • Время установки сигнала (setup time) tsu – минимальное время, которое сигнал на входе регистра должен быть стабилен до прихода фронта синхронизации • Время удержания сигнала (hold time) th – минимальное время, которое сигнал на входе регистра должен быть стабилен после прихода фронта синхронизации • Задержка распространения tco – время, необходимое для формирования значения на выходе регистра после прихода фронта синхронизации 3

Временные характеристики триггеров • Время установки сигнала (setup time) tsu – минимальное время, которое сигнал на входе регистра должен быть стабилен до прихода фронта синхронизации • Время удержания сигнала (hold time) th – минимальное время, которое сигнал на входе регистра должен быть стабилен после прихода фронта синхронизации • Задержка распространения tco – время, необходимое для формирования значения на выходе регистра после прихода фронта синхронизации 3

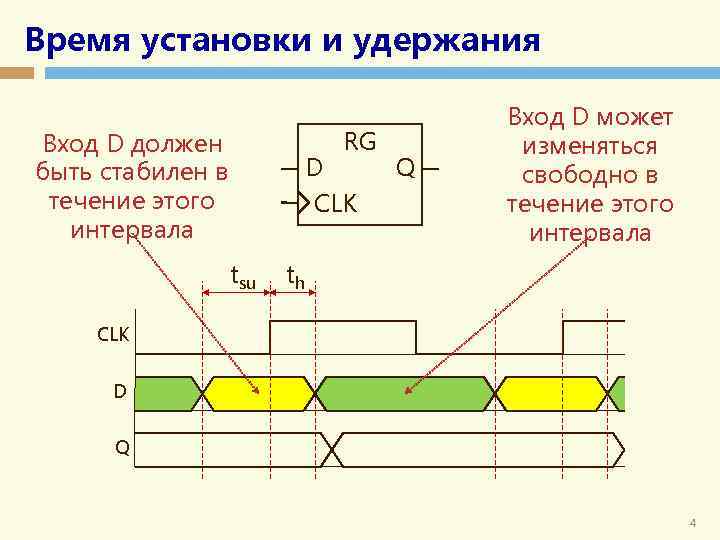

Время установки и удержания Вход D должен быть стабилен в течение этого интервала D RG CLK tsu Q Вход D может изменяться свободно в течение этого интервала th CLK D Q 4

Время установки и удержания Вход D должен быть стабилен в течение этого интервала D RG CLK tsu Q Вход D может изменяться свободно в течение этого интервала th CLK D Q 4

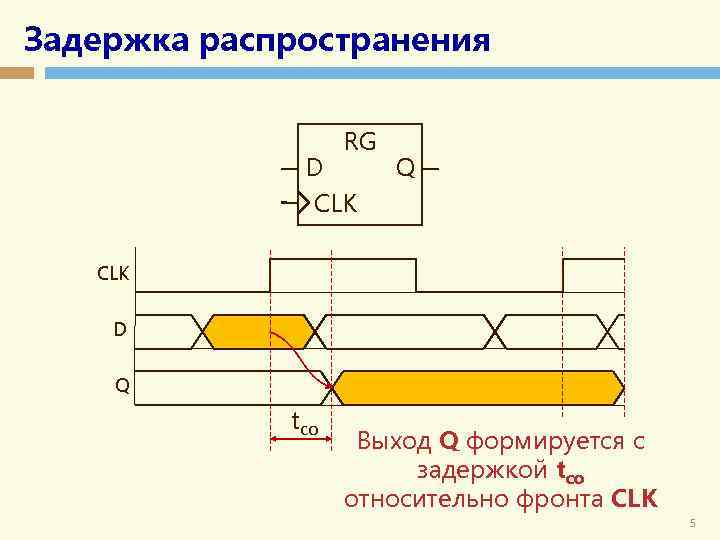

Задержка распространения D RG Q CLK D Q tco Выход Q формируется с задержкой tco относительно фронта CLK 5

Задержка распространения D RG Q CLK D Q tco Выход Q формируется с задержкой tco относительно фронта CLK 5

Время установки tsu 6

Время установки tsu 6

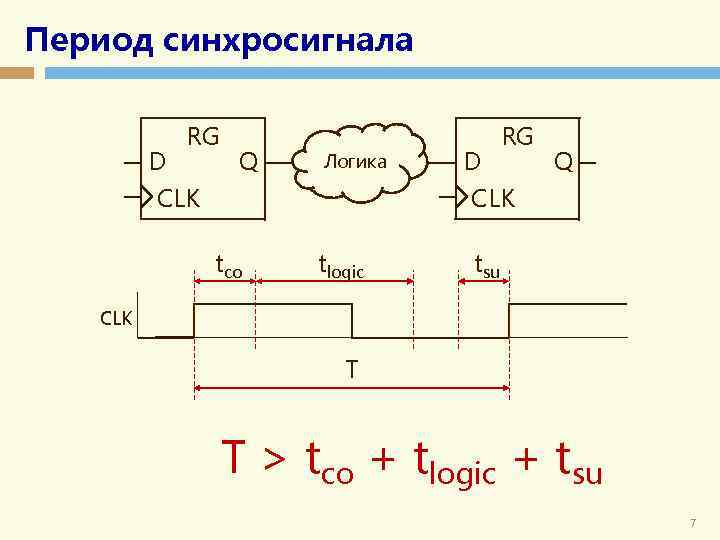

Период синхросигнала D RG Q Логика CLK D RG Q CLK tco tlogic tsu CLK T T > tco + tlogic + tsu 7

Период синхросигнала D RG Q Логика CLK D RG Q CLK tco tlogic tsu CLK T T > tco + tlogic + tsu 7

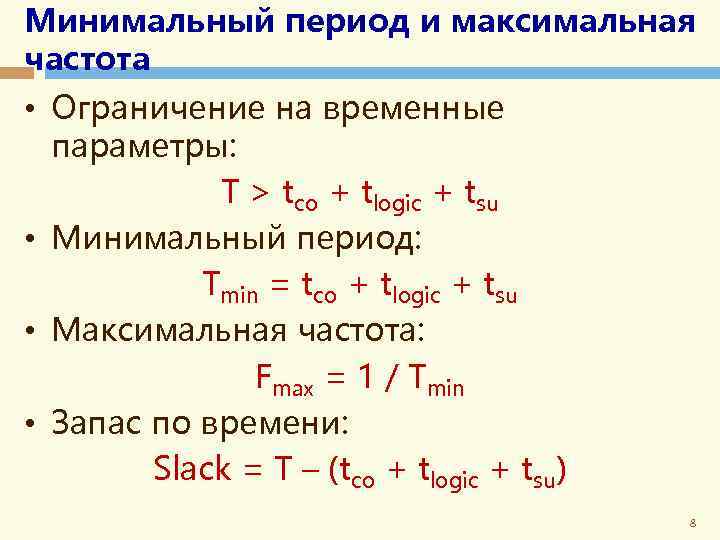

Минимальный период и максимальная частота • Ограничение на временные параметры: T > tco + tlogic + tsu • Минимальный период: Tmin = tco + tlogic + tsu • Максимальная частота: Fmax = 1 / Tmin • Запас по времени: Slack = T – (tco + tlogic + tsu) 8

Минимальный период и максимальная частота • Ограничение на временные параметры: T > tco + tlogic + tsu • Минимальный период: Tmin = tco + tlogic + tsu • Максимальная частота: Fmax = 1 / Tmin • Запас по времени: Slack = T – (tco + tlogic + tsu) 8

Критический путь • Путь – маршрут распространения данных от выхода данных одного регистра до входа данных другого • Время распространения: tpath = tco + tlogic + tsu • Критический путь – путь с наибольшим временем распространения tcritical_path • Максимально возможная частота схемы определяется критическим путем: Tmin = tcritical_path 9

Критический путь • Путь – маршрут распространения данных от выхода данных одного регистра до входа данных другого • Время распространения: tpath = tco + tlogic + tsu • Критический путь – путь с наибольшим временем распространения tcritical_path • Максимально возможная частота схемы определяется критическим путем: Tmin = tcritical_path 9

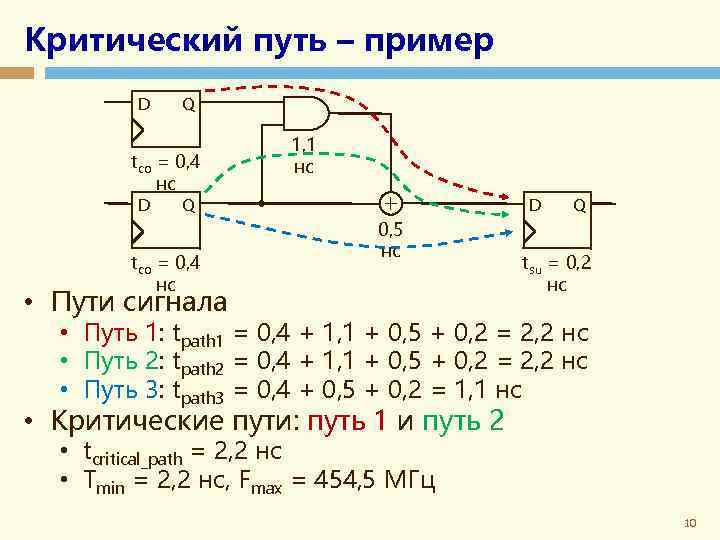

Критический путь – пример D Q tco = 0, 4 нс D 1, 1 нс Q tco = 0, 4 нс D 0, 5 нс • Пути сигнала Q tsu = 0, 2 нс • Путь 1: tpath 1 = 0, 4 + 1, 1 + 0, 5 + 0, 2 = 2, 2 нс • Путь 2: tpath 2 = 0, 4 + 1, 1 + 0, 5 + 0, 2 = 2, 2 нс • Путь 3: tpath 3 = 0, 4 + 0, 5 + 0, 2 = 1, 1 нс • Критические пути: путь 1 и путь 2 • tcritical_path = 2, 2 нс • Tmin = 2, 2 нс, Fmax = 454, 5 МГц 10

Критический путь – пример D Q tco = 0, 4 нс D 1, 1 нс Q tco = 0, 4 нс D 0, 5 нс • Пути сигнала Q tsu = 0, 2 нс • Путь 1: tpath 1 = 0, 4 + 1, 1 + 0, 5 + 0, 2 = 2, 2 нс • Путь 2: tpath 2 = 0, 4 + 1, 1 + 0, 5 + 0, 2 = 2, 2 нс • Путь 3: tpath 3 = 0, 4 + 0, 5 + 0, 2 = 1, 1 нс • Критические пути: путь 1 и путь 2 • tcritical_path = 2, 2 нс • Tmin = 2, 2 нс, Fmax = 454, 5 МГц 10

Задержка tlogic • Параметры tco и tsu в большинстве случаев фиксированы • Определяются технологией и примерно одинаковы для всех регистров • Для повышения быстродействия необходимо уменьшать tlogic • tlogic – время прохождения сигнала между регистрами • Задержка вычисления • Задержка распространения 11

Задержка tlogic • Параметры tco и tsu в большинстве случаев фиксированы • Определяются технологией и примерно одинаковы для всех регистров • Для повышения быстродействия необходимо уменьшать tlogic • tlogic – время прохождения сигнала между регистрами • Задержка вычисления • Задержка распространения 11

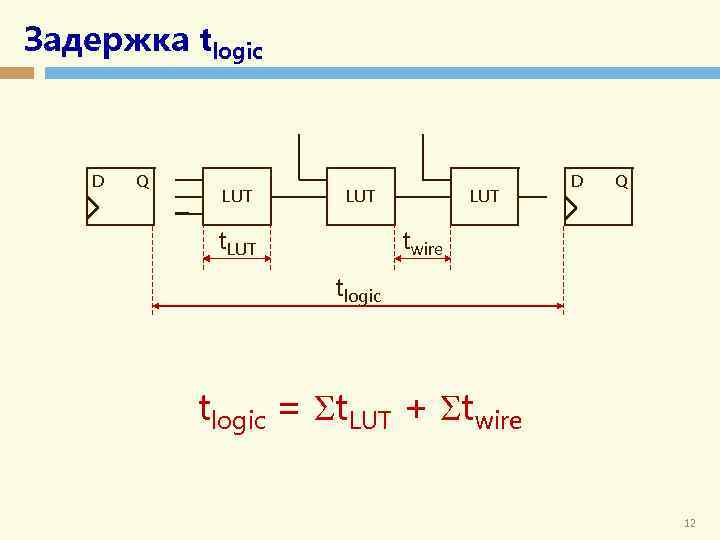

Задержка tlogic D Q LUT t. LUT D Q twire tlogic = t. LUT + twire 12

Задержка tlogic D Q LUT t. LUT D Q twire tlogic = t. LUT + twire 12

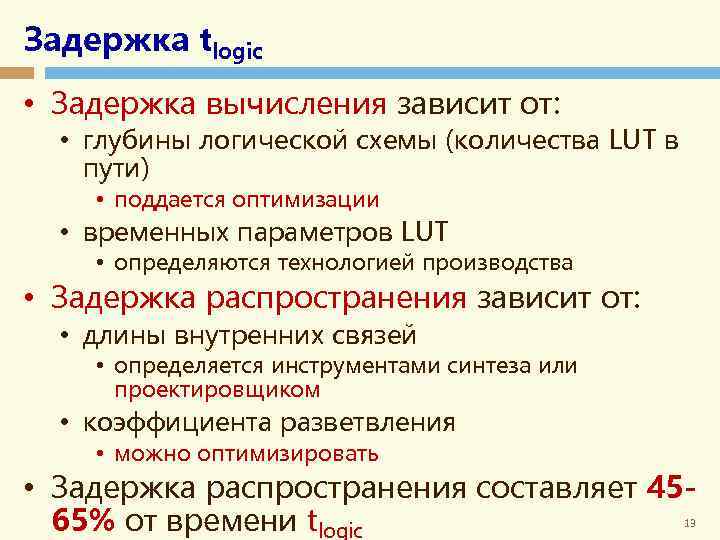

Задержка tlogic • Задержка вычисления зависит от: • глубины логической схемы (количества LUT в пути) • поддается оптимизации • временных параметров LUT • определяются технологией производства • Задержка распространения зависит от: • длины внутренних связей • определяется инструментами синтеза или проектировщиком • коэффициента разветвления • можно оптимизировать • Задержка распространения составляет 4565% от времени tlogic 13

Задержка tlogic • Задержка вычисления зависит от: • глубины логической схемы (количества LUT в пути) • поддается оптимизации • временных параметров LUT • определяются технологией производства • Задержка распространения зависит от: • длины внутренних связей • определяется инструментами синтеза или проектировщиком • коэффициента разветвления • можно оптимизировать • Задержка распространения составляет 4565% от времени tlogic 13

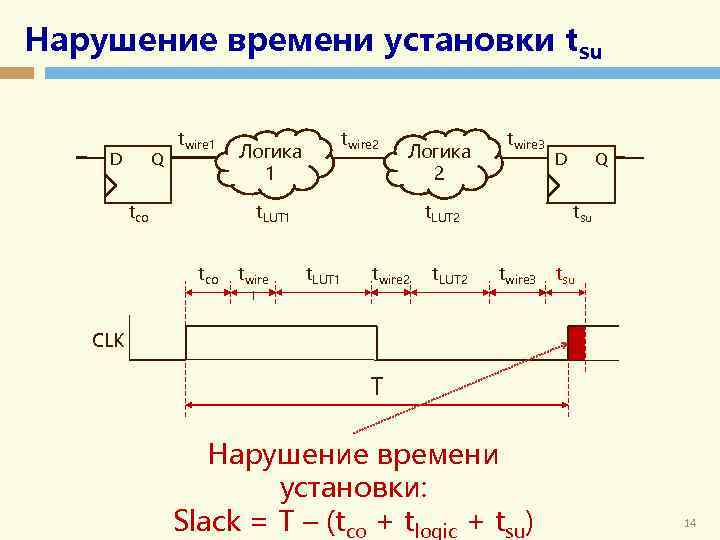

Нарушение времени установки tsu D Q twire 1 tco twire 2 Логика 1 Логика 2 t. LUT 1 tco twire 3 t. LUT 2 t. LUT 1 twire 2 t. LUT 2 D Q tsu twire 3 tsu 1 CLK T Нарушение времени установки: Slack = T – (tco + tlogic + tsu) 14

Нарушение времени установки tsu D Q twire 1 tco twire 2 Логика 1 Логика 2 t. LUT 1 tco twire 3 t. LUT 2 t. LUT 1 twire 2 t. LUT 2 D Q tsu twire 3 tsu 1 CLK T Нарушение времени установки: Slack = T – (tco + tlogic + tsu) 14

Время удержания th 15

Время удержания th 15

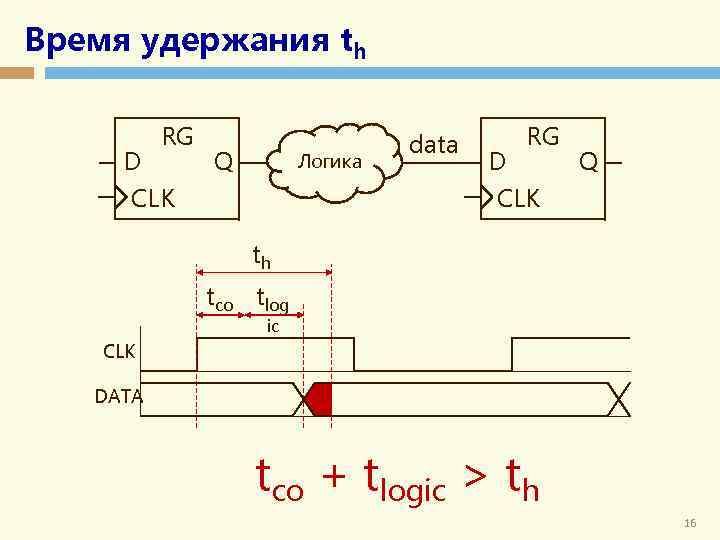

Время удержания th D RG Q Логика CLK data D RG Q CLK th tco tlog ic CLK DATA tco + tlogic > th 16

Время удержания th D RG Q Логика CLK data D RG Q CLK th tco tlog ic CLK DATA tco + tlogic > th 16

Нестабильность и сдвиг синхросигнала 17

Нестабильность и сдвиг синхросигнала 17

Параметры синхросигнала • Основные параметры синхросигнала: • период – время между двумя последовательными фронтами • сдвиг (skew) – сдвиг синхросигнала относительно «базового» сигнала • нестабильность (jitter) – случайные отклонения момента прихода фронта 18

Параметры синхросигнала • Основные параметры синхросигнала: • период – время между двумя последовательными фронтами • сдвиг (skew) – сдвиг синхросигнала относительно «базового» сигнала • нестабильность (jitter) – случайные отклонения момента прихода фронта 18

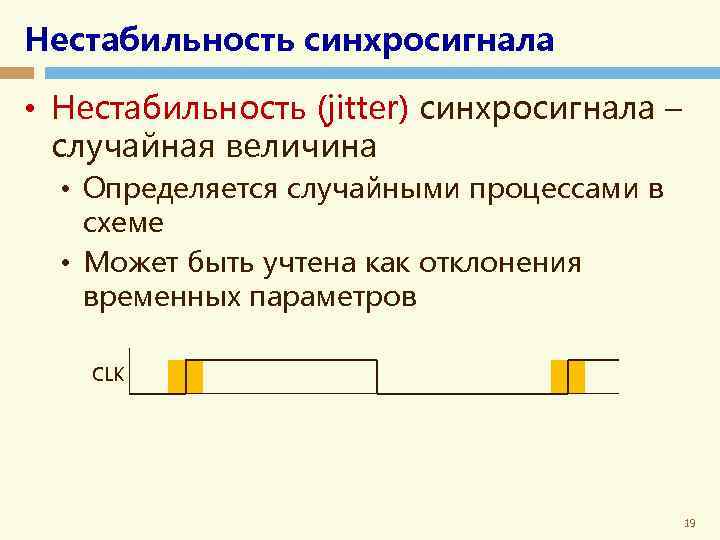

Нестабильность синхросигнала • Нестабильность (jitter) синхросигнала – случайная величина • Определяется случайными процессами в схеме • Может быть учтена как отклонения временных параметров CLK 19

Нестабильность синхросигнала • Нестабильность (jitter) синхросигнала – случайная величина • Определяется случайными процессами в схеме • Может быть учтена как отклонения временных параметров CLK 19

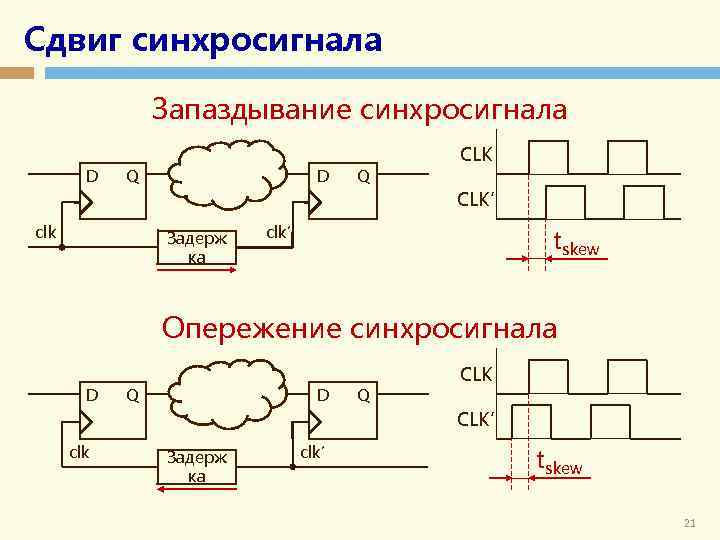

Сдвиг синхросигнала • Сдвиг (skew) синхросигнала – детерминированная величина • Отсчитывается от некоторого «базового» сигнала • Определяется особенностями схемы (задержками распространения сигнала) • Может быть учтен и скомпенсирован 20

Сдвиг синхросигнала • Сдвиг (skew) синхросигнала – детерминированная величина • Отсчитывается от некоторого «базового» сигнала • Определяется особенностями схемы (задержками распространения сигнала) • Может быть учтен и скомпенсирован 20

Сдвиг синхросигнала Запаздывание синхросигнала D Q CLK’ clk Задерж ка clk’ tskew Опережение синхросигнала D Q CLK’ clk Задерж ка clk’ tskew 21

Сдвиг синхросигнала Запаздывание синхросигнала D Q CLK’ clk Задерж ка clk’ tskew Опережение синхросигнала D Q CLK’ clk Задерж ка clk’ tskew 21

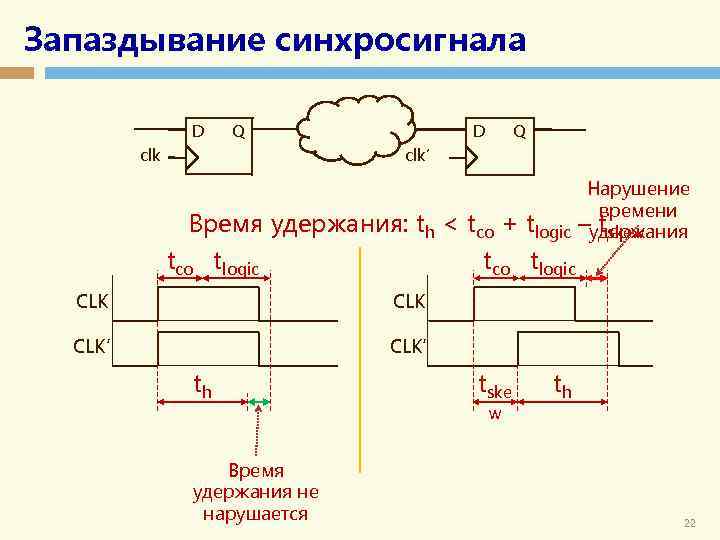

Запаздывание синхросигнала D Q clk’ Время удержания: th < tco + tco tlogic Нарушение времени tlogic –удержания tskew tco tlogic CLK CLK’ th tske th w Время удержания не нарушается 22

Запаздывание синхросигнала D Q clk’ Время удержания: th < tco + tco tlogic Нарушение времени tlogic –удержания tskew tco tlogic CLK CLK’ th tske th w Время удержания не нарушается 22

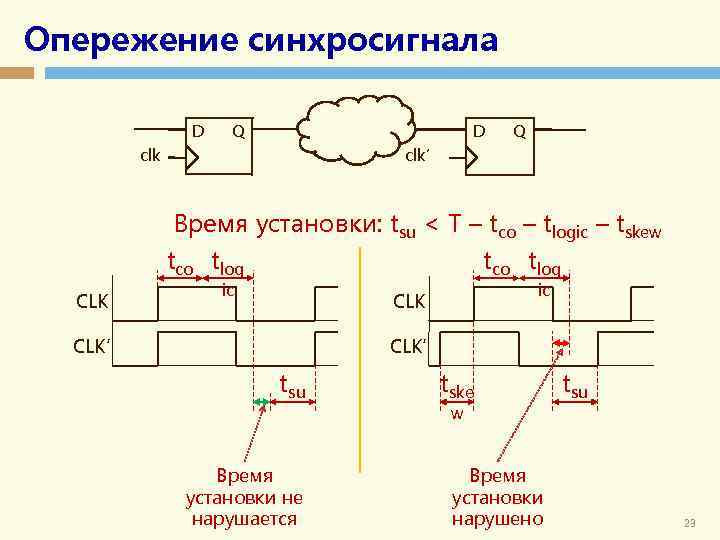

Опережение синхросигнала D Q D clk Q clk’ Время установки: tsu < T – tco – tlogic – tskew tco tlog CLK tco tlog ic ic CLK’ tsu tske tsu w Время установки не нарушается Время установки нарушено 23

Опережение синхросигнала D Q D clk Q clk’ Время установки: tsu < T – tco – tlogic – tskew tco tlog CLK tco tlog ic ic CLK’ tsu tske tsu w Время установки не нарушается Время установки нарушено 23

Устранение нарушений временных параметров 24

Устранение нарушений временных параметров 24

Уменьшение сдвига синхросигнала • Используйте выделенные линии для сигналов синхронизации • Сеть линий синхронизации оптимизирована для синфазного прохождения сигнала • Не используйте комбинационную логику (gated clocks) или регистры (ripple clocks) в цепях синхронизации • Для управления работой схемы используйте входы ENABLE или специализированные блоки 25

Уменьшение сдвига синхросигнала • Используйте выделенные линии для сигналов синхронизации • Сеть линий синхронизации оптимизирована для синфазного прохождения сигнала • Не используйте комбинационную логику (gated clocks) или регистры (ripple clocks) в цепях синхронизации • Для управления работой схемы используйте входы ENABLE или специализированные блоки 25

Устранение нарушений времени установки • Понизьте частоту работы схемы (увеличьте период) • Используйте конвейерную обработку • Введение промежуточных регистров позволит сократить задержку tlogic • Понизьте коэффициент разветвления • Quartus II позволяет делать это автоматически • Избегайте шифраторов приоритета • Используйте операторы CASE вместо IF в VHDL-коде, если это возможно 26

Устранение нарушений времени установки • Понизьте частоту работы схемы (увеличьте период) • Используйте конвейерную обработку • Введение промежуточных регистров позволит сократить задержку tlogic • Понизьте коэффициент разветвления • Quartus II позволяет делать это автоматически • Избегайте шифраторов приоритета • Используйте операторы CASE вместо IF в VHDL-коде, если это возможно 26

Устранение нарушений времени удержания • Скорее всего ничего сделать не удастся • Обычно не является проблемой в FPGA 27

Устранение нарушений времени удержания • Скорее всего ничего сделать не удастся • Обычно не является проблемой в FPGA 27

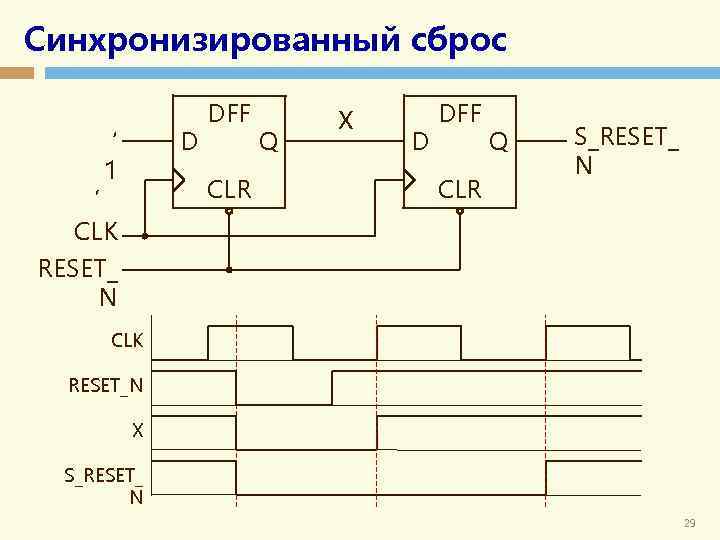

Схема синхронизированного сброса 28

Схема синхронизированного сброса 28

Синхронизированный сброс D ‘ 1 ’ CLK DFF CLR Q X D DFF CLR Q S_RESET_ N CLK RESET_N X S_RESET_ N 29

Синхронизированный сброс D ‘ 1 ’ CLK DFF CLR Q X D DFF CLR Q S_RESET_ N CLK RESET_N X S_RESET_ N 29

Дополнительная информация Best HDL Design Practices for Timing Closure http: //www. altera. com/education/training/course s/OHDL 1130 Design Guidelines for Optimal Results in FPGAs http: //www. altera. com/literature/cp/fpgasoptimal-results-396. pdf 30

Дополнительная информация Best HDL Design Practices for Timing Closure http: //www. altera. com/education/training/course s/OHDL 1130 Design Guidelines for Optimal Results in FPGAs http: //www. altera. com/literature/cp/fpgasoptimal-results-396. pdf 30