aeb4c97174fb78937fe43216c0e09711.ppt

- Количество слайдов: 21

Production Readiness Review of the MDT ROD Electronic Design Details Slide 1 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Production Readiness Review of the MDT ROD Electronic Design Details Slide 1 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

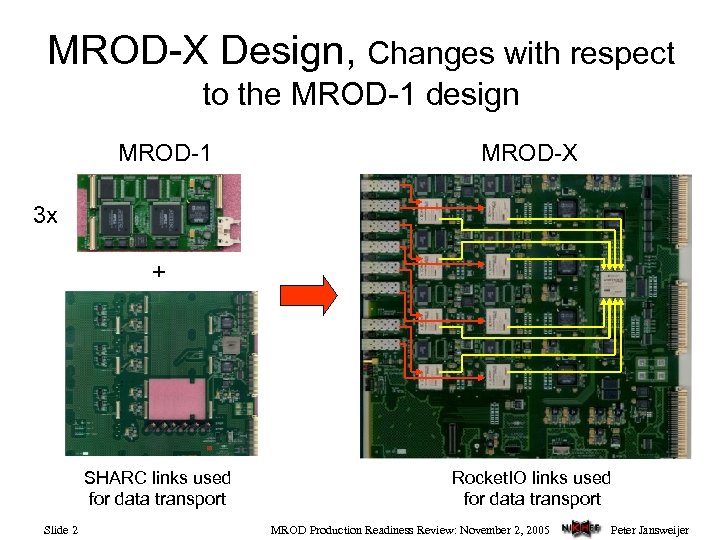

MROD-X Design, Changes with respect to the MROD-1 design MROD-1 MROD-X 3 x + SHARC links used for data transport Slide 2 Rocket. IO links used for data transport MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

MROD-X Design, Changes with respect to the MROD-1 design MROD-1 MROD-X 3 x + SHARC links used for data transport Slide 2 Rocket. IO links used for data transport MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

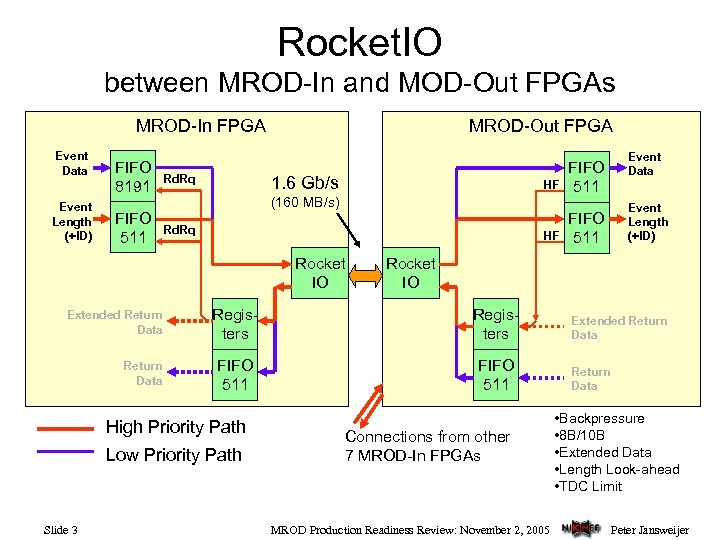

Rocket. IO between MROD-In and MOD-Out FPGAs MROD-In FPGA Event Data Event Length (+ID) FIFO 8191 FIFO 511 MROD-Out FPGA HF HF Rd. Rq 1. 6 Gb/s Return Data Rd. Rq Registers FIFO 511 Low Priority Path Event Data Event Length (+ID) Rocket IO Registers High Priority Path Slide 3 FIFO 511 (160 MB/s) Rocket IO Extended Return Data FIFO 511 Connections from other 7 MROD-In FPGAs MROD Production Readiness Review: November 2, 2005 Extended Return Data • Backpressure • 8 B/10 B • Extended Data • Length Look-ahead • TDC Limit Peter Jansweijer

Rocket. IO between MROD-In and MOD-Out FPGAs MROD-In FPGA Event Data Event Length (+ID) FIFO 8191 FIFO 511 MROD-Out FPGA HF HF Rd. Rq 1. 6 Gb/s Return Data Rd. Rq Registers FIFO 511 Low Priority Path Event Data Event Length (+ID) Rocket IO Registers High Priority Path Slide 3 FIFO 511 (160 MB/s) Rocket IO Extended Return Data FIFO 511 Connections from other 7 MROD-In FPGAs MROD Production Readiness Review: November 2, 2005 Extended Return Data • Backpressure • 8 B/10 B • Extended Data • Length Look-ahead • TDC Limit Peter Jansweijer

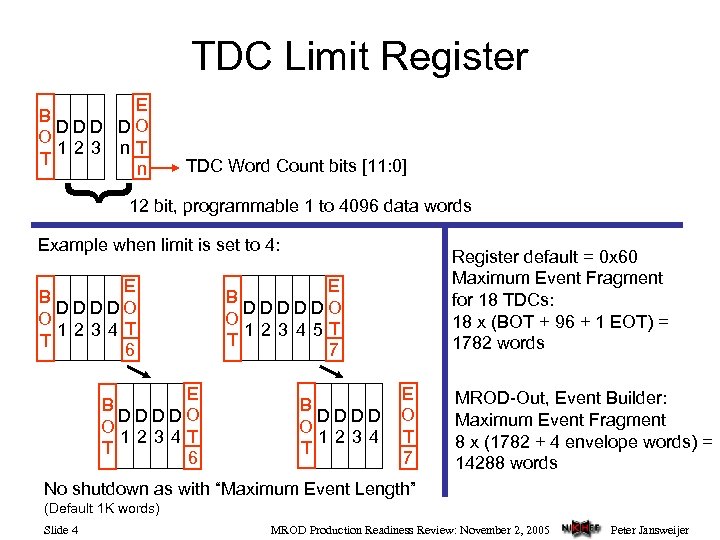

TDC Limit Register E B DDD DO O 123 n. T T n TDC Word Count bits [11: 0] } 12 bit, programmable 1 to 4096 data words Example when limit is set to 4: E B DDDDO O 1234 T T 6 Register default = 0 x 60 Maximum Event Fragment for 18 TDCs: 18 x (BOT + 96 + 1 EOT) = 1782 words E B DDDDDO O 12345 T T 7 B DDDD O 1234 T E O T 7 MROD-Out, Event Builder: Maximum Event Fragment 8 x (1782 + 4 envelope words) = 14288 words No shutdown as with “Maximum Event Length” (Default 1 K words) Slide 4 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

TDC Limit Register E B DDD DO O 123 n. T T n TDC Word Count bits [11: 0] } 12 bit, programmable 1 to 4096 data words Example when limit is set to 4: E B DDDDO O 1234 T T 6 Register default = 0 x 60 Maximum Event Fragment for 18 TDCs: 18 x (BOT + 96 + 1 EOT) = 1782 words E B DDDDDO O 12345 T T 7 B DDDD O 1234 T E O T 7 MROD-Out, Event Builder: Maximum Event Fragment 8 x (1782 + 4 envelope words) = 14288 words No shutdown as with “Maximum Event Length” (Default 1 K words) Slide 4 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

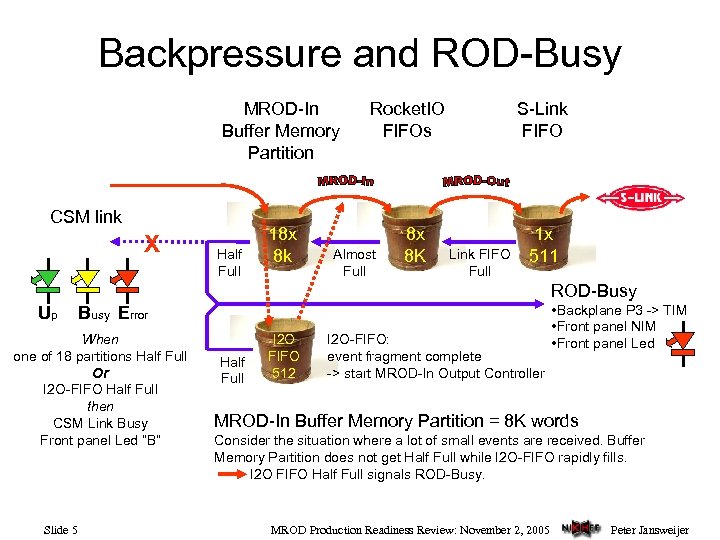

Backpressure and ROD-Busy MROD-In Buffer Memory Partition CSM link X Half Full 18 x 8 k Rocket. IO FIFOs Almost Full 8 x 8 K S-Link FIFO Full 1 x 511 ROD-Busy Up Busy Error When one of 18 partitions Half Full Or I 2 O-FIFO Half Full then CSM Link Busy Front panel Led “B” Slide 5 Half Full I 2 O FIFO 512 I 2 O-FIFO: event fragment complete -> start MROD-In Output Controller • Backplane P 3 -> TIM • Front panel NIM • Front panel Led MROD-In Buffer Memory Partition = 8 K words Consider the situation where a lot of small events are received. Buffer Memory Partition does not get Half Full while I 2 O-FIFO rapidly fills. I 2 O FIFO Half Full signals ROD-Busy. MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Backpressure and ROD-Busy MROD-In Buffer Memory Partition CSM link X Half Full 18 x 8 k Rocket. IO FIFOs Almost Full 8 x 8 K S-Link FIFO Full 1 x 511 ROD-Busy Up Busy Error When one of 18 partitions Half Full Or I 2 O-FIFO Half Full then CSM Link Busy Front panel Led “B” Slide 5 Half Full I 2 O FIFO 512 I 2 O-FIFO: event fragment complete -> start MROD-In Output Controller • Backplane P 3 -> TIM • Front panel NIM • Front panel Led MROD-In Buffer Memory Partition = 8 K words Consider the situation where a lot of small events are received. Buffer Memory Partition does not get Half Full while I 2 O-FIFO rapidly fills. I 2 O FIFO Half Full signals ROD-Busy. MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

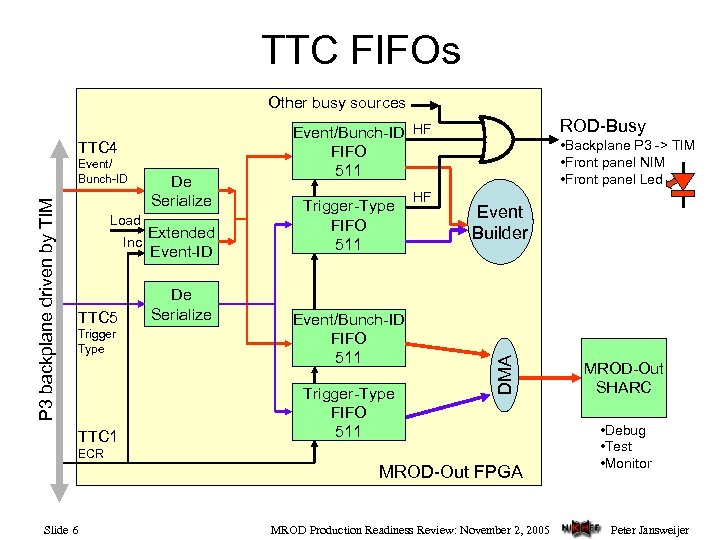

TTC FIFOs Other busy sources P 3 backplane driven by TIM Event/ Bunch-ID Load Inc TTC 5 Trigger Type TTC 1 De Serialize Extended Event-ID De Serialize Trigger-Type FIFO 511 Event/Bunch-ID FIFO 511 Trigger-Type FIFO 511 HF • Backplane P 3 -> TIM • Front panel NIM • Front panel Led Event Builder DMA TTC 4 ROD-Busy Event/Bunch-ID HF FIFO 511 ECR MROD-Out FPGA Slide 6 MROD Production Readiness Review: November 2, 2005 MROD-Out SHARC • Debug • Test • Monitor Peter Jansweijer

TTC FIFOs Other busy sources P 3 backplane driven by TIM Event/ Bunch-ID Load Inc TTC 5 Trigger Type TTC 1 De Serialize Extended Event-ID De Serialize Trigger-Type FIFO 511 Event/Bunch-ID FIFO 511 Trigger-Type FIFO 511 HF • Backplane P 3 -> TIM • Front panel NIM • Front panel Led Event Builder DMA TTC 4 ROD-Busy Event/Bunch-ID HF FIFO 511 ECR MROD-Out FPGA Slide 6 MROD Production Readiness Review: November 2, 2005 MROD-Out SHARC • Debug • Test • Monitor Peter Jansweijer

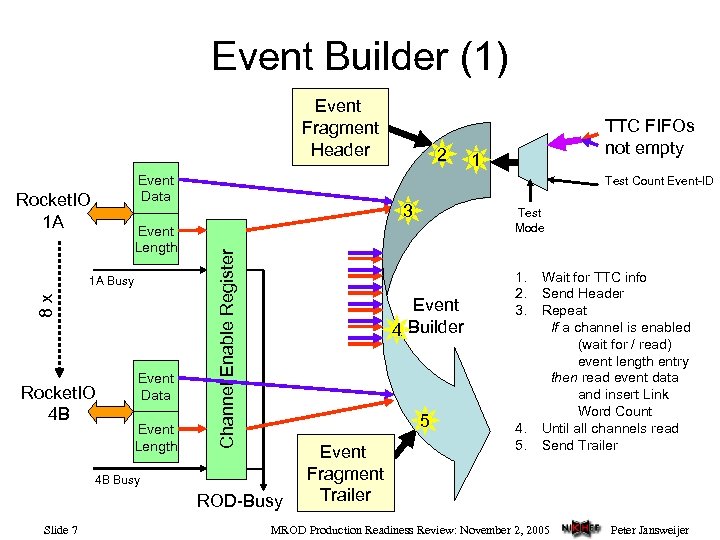

Event Builder (1) Event Fragment Header Event Data Event Length 8 x 1 A Busy Rocket. IO 4 B Event Data Event Length 3 Test Mode Event 4 Builder 5 4 B Busy ROD-Busy Slide 7 1 Test Count Event-ID Channel Enable Register Rocket. IO 1 A 2 TTC FIFOs not empty Event Fragment Trailer 1. 2. 3. 4. 5. Wait for TTC info Send Header Repeat If a channel is enabled (wait for / read) event length entry then read event data and insert Link Word Count Until all channels read Send Trailer MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Event Builder (1) Event Fragment Header Event Data Event Length 8 x 1 A Busy Rocket. IO 4 B Event Data Event Length 3 Test Mode Event 4 Builder 5 4 B Busy ROD-Busy Slide 7 1 Test Count Event-ID Channel Enable Register Rocket. IO 1 A 2 TTC FIFOs not empty Event Fragment Trailer 1. 2. 3. 4. 5. Wait for TTC info Send Header Repeat If a channel is enabled (wait for / read) event length entry then read event data and insert Link Word Count Until all channels read Send Trailer MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

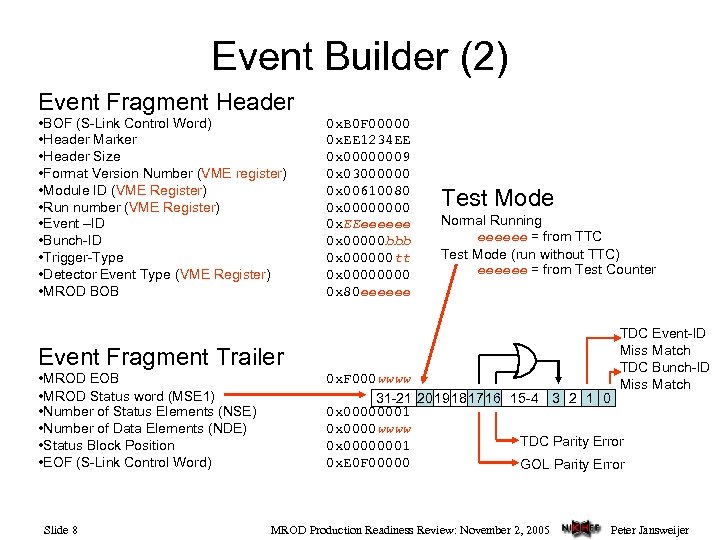

Event Builder (2) Event Fragment Header • BOF (S-Link Control Word) • Header Marker • Header Size • Format Version Number (VME register) • Module ID (VME Register) • Run number (VME Register) • Event –ID • Bunch-ID • Trigger-Type • Detector Event Type (VME Register) • MROD BOB 0 x. B 0 F 00000 0 x. EE 1234 EE 0 x 00000009 0 x 03000000 0 x 00610080 0 x 0000 0 x. EEeeeeee 0 x 00000 bbb 0 x 000000 tt 0 x 0000 0 x 80 eeeeee Test Mode Normal Running eeeeee = from TTC Test Mode (run without TTC) eeeeee = from Test Counter Event Fragment Trailer • MROD EOB • MROD Status word (MSE 1) • Number of Status Elements (NSE) • Number of Data Elements (NDE) • Status Block Position • EOF (S-Link Control Word) Slide 8 TDC Event-ID Miss Match TDC Bunch-ID Miss Match 0 x. F 000 wwww 31 -21 20 19 18 17 16 15 -4 3 2 1 0 0 x 00000001 0 x 0000 wwww TDC Parity Error 0 x 00000001 0 x. E 0 F 00000 GOL Parity Error MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Event Builder (2) Event Fragment Header • BOF (S-Link Control Word) • Header Marker • Header Size • Format Version Number (VME register) • Module ID (VME Register) • Run number (VME Register) • Event –ID • Bunch-ID • Trigger-Type • Detector Event Type (VME Register) • MROD BOB 0 x. B 0 F 00000 0 x. EE 1234 EE 0 x 00000009 0 x 03000000 0 x 00610080 0 x 0000 0 x. EEeeeeee 0 x 00000 bbb 0 x 000000 tt 0 x 0000 0 x 80 eeeeee Test Mode Normal Running eeeeee = from TTC Test Mode (run without TTC) eeeeee = from Test Counter Event Fragment Trailer • MROD EOB • MROD Status word (MSE 1) • Number of Status Elements (NSE) • Number of Data Elements (NDE) • Status Block Position • EOF (S-Link Control Word) Slide 8 TDC Event-ID Miss Match TDC Bunch-ID Miss Match 0 x. F 000 wwww 31 -21 20 19 18 17 16 15 -4 3 2 1 0 0 x 00000001 0 x 0000 wwww TDC Parity Error 0 x 00000001 0 x. E 0 F 00000 GOL Parity Error MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

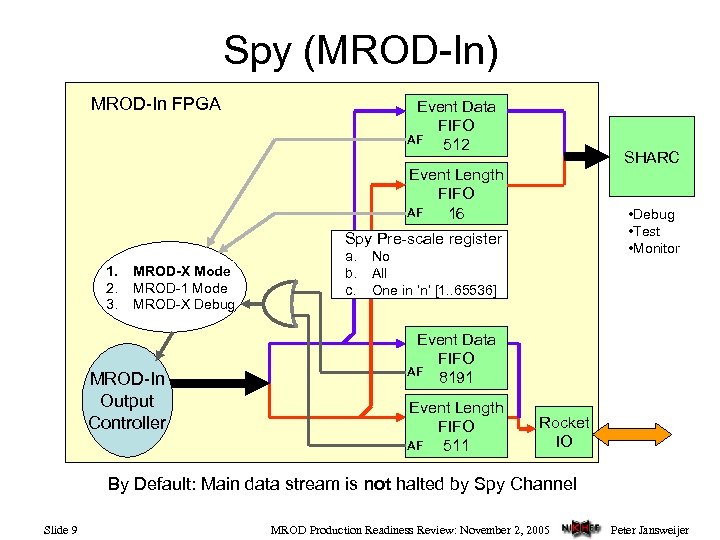

Spy (MROD-In) MROD-In FPGA Event Data FIFO AF 512 SHARC Event Length FIFO AF 16 • Debug • Test • Monitor Spy Pre-scale register 1. 2. 3. MROD-X Mode MROD-1 Mode MROD-X Debug MROD-In Output Controller a. b. c. No All One in ‘n’ [1. . 65536] Event Data FIFO AF 8191 Event Length FIFO AF 511 Rocket IO By Default: Main data stream is not halted by Spy Channel Slide 9 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Spy (MROD-In) MROD-In FPGA Event Data FIFO AF 512 SHARC Event Length FIFO AF 16 • Debug • Test • Monitor Spy Pre-scale register 1. 2. 3. MROD-X Mode MROD-1 Mode MROD-X Debug MROD-In Output Controller a. b. c. No All One in ‘n’ [1. . 65536] Event Data FIFO AF 8191 Event Length FIFO AF 511 Rocket IO By Default: Main data stream is not halted by Spy Channel Slide 9 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

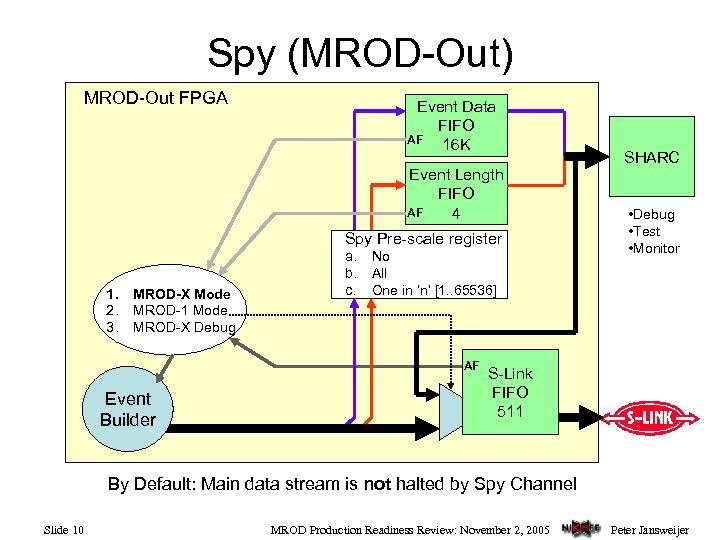

Spy (MROD-Out) MROD-Out FPGA Event Data FIFO AF 16 K Event Length FIFO AF 4 Spy Pre-scale register 1. 2. 3. MROD-X Mode MROD-1 Mode MROD-X Debug a. b. c. No All One in ‘n’ [1. . 65536] AF Event Builder SHARC • Debug • Test • Monitor S-Link FIFO 511 By Default: Main data stream is not halted by Spy Channel Slide 10 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Spy (MROD-Out) MROD-Out FPGA Event Data FIFO AF 16 K Event Length FIFO AF 4 Spy Pre-scale register 1. 2. 3. MROD-X Mode MROD-1 Mode MROD-X Debug a. b. c. No All One in ‘n’ [1. . 65536] AF Event Builder SHARC • Debug • Test • Monitor S-Link FIFO 511 By Default: Main data stream is not halted by Spy Channel Slide 10 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

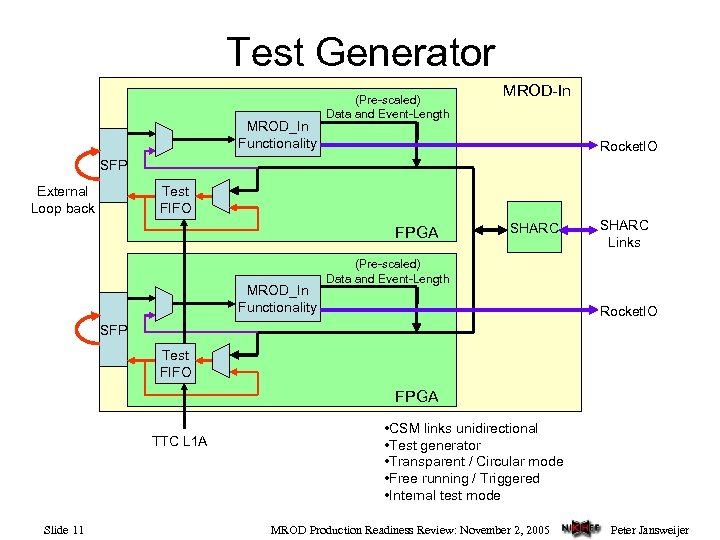

Test Generator MROD_In Functionality (Pre-scaled) Data and Event-Length MROD-In Rocket. IO SFP Test FIFO External Loop back FPGA MROD_In Functionality SHARC Links (Pre-scaled) Data and Event-Length Rocket. IO SFP Test FIFO FPGA TTC L 1 A Slide 11 • CSM links unidirectional • Test generator • Transparent / Circular mode • Free running / Triggered • Internal test mode MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Test Generator MROD_In Functionality (Pre-scaled) Data and Event-Length MROD-In Rocket. IO SFP Test FIFO External Loop back FPGA MROD_In Functionality SHARC Links (Pre-scaled) Data and Event-Length Rocket. IO SFP Test FIFO FPGA TTC L 1 A Slide 11 • CSM links unidirectional • Test generator • Transparent / Circular mode • Free running / Triggered • Internal test mode MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

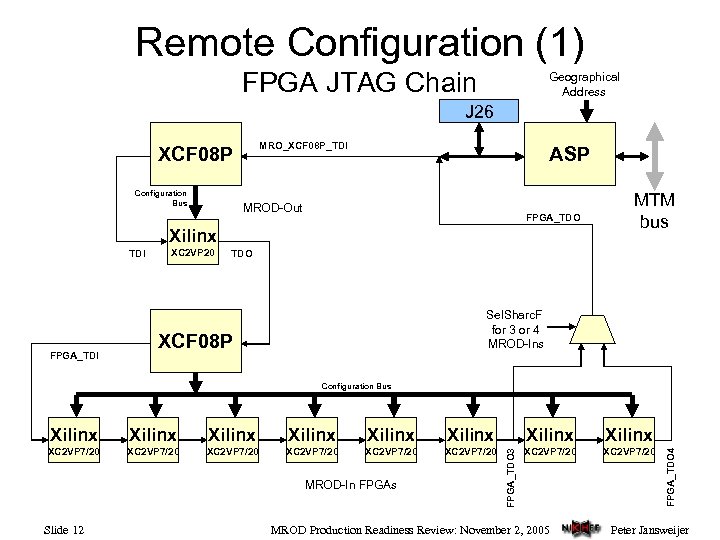

Remote Configuration (1) FPGA JTAG Chain Geographical Address J 26 MRO_XCF 08 P_TDI XCF 08 P Configuration Bus ASP MROD-Out FPGA_TDO Xilinx TDI FPGA_TDI XC 2 VP 20 MTM bus TDO Sel. Sharc. F for 3 or 4 MROD-Ins XCF 08 P Configuration Bus Xilinx Xilinx XC 2 VP 7/20 XC 2 VP 7/20 MROD-In FPGAs Slide 12 MROD Production Readiness Review: November 2, 2005 FPGA_TDO 4 Xilinx XC 2 VP 7/20 FPGA_TDO 3 Xilinx XC 2 VP 7/20 Peter Jansweijer

Remote Configuration (1) FPGA JTAG Chain Geographical Address J 26 MRO_XCF 08 P_TDI XCF 08 P Configuration Bus ASP MROD-Out FPGA_TDO Xilinx TDI FPGA_TDI XC 2 VP 20 MTM bus TDO Sel. Sharc. F for 3 or 4 MROD-Ins XCF 08 P Configuration Bus Xilinx Xilinx XC 2 VP 7/20 XC 2 VP 7/20 MROD-In FPGAs Slide 12 MROD Production Readiness Review: November 2, 2005 FPGA_TDO 4 Xilinx XC 2 VP 7/20 FPGA_TDO 3 Xilinx XC 2 VP 7/20 Peter Jansweijer

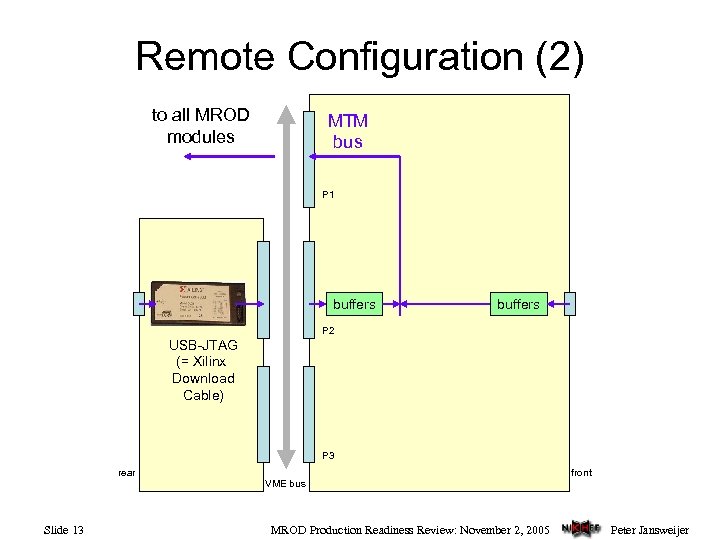

Remote Configuration (2) to all MROD modules MTM bus P 1 buffers P 2 USB-JTAG (= Xilinx Download Cable) P 3 rear front VME bus Slide 13 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Remote Configuration (2) to all MROD modules MTM bus P 1 buffers P 2 USB-JTAG (= Xilinx Download Cable) P 3 rear front VME bus Slide 13 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

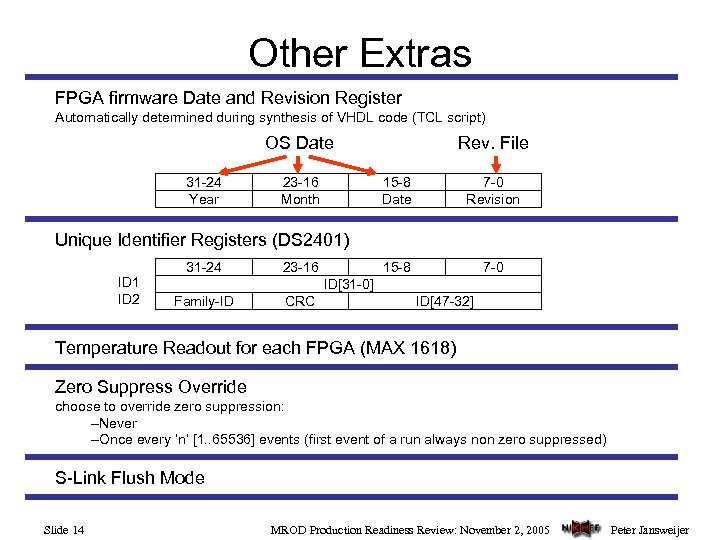

Other Extras FPGA firmware Date and Revision Register Automatically determined during synthesis of VHDL code (TCL script) OS Date 31 -24 Year 23 -16 Month Rev. File 15 -8 Date 7 -0 Revision 15 -8 7 -0 Unique Identifier Registers (DS 2401) ID 1 ID 2 31 -24 23 -16 ID[31 -0] Family-ID CRC ID[47 -32] Temperature Readout for each FPGA (MAX 1618) Zero Suppress Override choose to override zero suppression: –Never –Once every ‘n’ [1. . 65536] events (first event of a run always non zero suppressed) S-Link Flush Mode Slide 14 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Other Extras FPGA firmware Date and Revision Register Automatically determined during synthesis of VHDL code (TCL script) OS Date 31 -24 Year 23 -16 Month Rev. File 15 -8 Date 7 -0 Revision 15 -8 7 -0 Unique Identifier Registers (DS 2401) ID 1 ID 2 31 -24 23 -16 ID[31 -0] Family-ID CRC ID[47 -32] Temperature Readout for each FPGA (MAX 1618) Zero Suppress Override choose to override zero suppression: –Never –Once every ‘n’ [1. . 65536] events (first event of a run always non zero suppressed) S-Link Flush Mode Slide 14 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Production Readiness Review of the MDT ROD Prototype issues Slide 15 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Production Readiness Review of the MDT ROD Prototype issues Slide 15 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

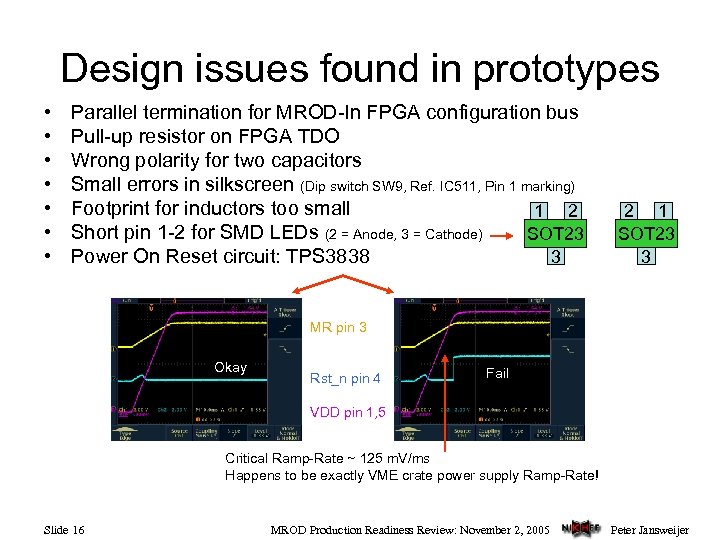

Design issues found in prototypes • • Parallel termination for MROD-In FPGA configuration bus Pull-up resistor on FPGA TDO Wrong polarity for two capacitors Small errors in silkscreen (Dip switch SW 9, Ref. IC 511, Pin 1 marking) Footprint for inductors too small 1 2 Short pin 1 -2 for SMD LEDs (2 = Anode, 3 = Cathode) SOT 23 3 Power On Reset circuit: TPS 3838 2 1 SOT 23 3 MR pin 3 Okay Rst_n pin 4 Fail VDD pin 1, 5 Critical Ramp-Rate ~ 125 m. V/ms Happens to be exactly VME crate power supply Ramp-Rate! Slide 16 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Design issues found in prototypes • • Parallel termination for MROD-In FPGA configuration bus Pull-up resistor on FPGA TDO Wrong polarity for two capacitors Small errors in silkscreen (Dip switch SW 9, Ref. IC 511, Pin 1 marking) Footprint for inductors too small 1 2 Short pin 1 -2 for SMD LEDs (2 = Anode, 3 = Cathode) SOT 23 3 Power On Reset circuit: TPS 3838 2 1 SOT 23 3 MR pin 3 Okay Rst_n pin 4 Fail VDD pin 1, 5 Critical Ramp-Rate ~ 125 m. V/ms Happens to be exactly VME crate power supply Ramp-Rate! Slide 16 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

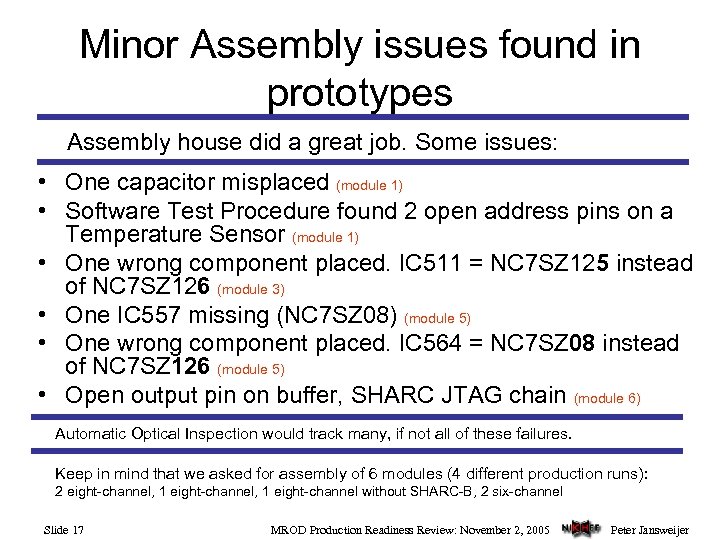

Minor Assembly issues found in prototypes Assembly house did a great job. Some issues: • One capacitor misplaced (module 1) • Software Test Procedure found 2 open address pins on a Temperature Sensor (module 1) • One wrong component placed. IC 511 = NC 7 SZ 125 instead of NC 7 SZ 126 (module 3) • One IC 557 missing (NC 7 SZ 08) (module 5) • One wrong component placed. IC 564 = NC 7 SZ 08 instead of NC 7 SZ 126 (module 5) • Open output pin on buffer, SHARC JTAG chain (module 6) Automatic Optical Inspection would track many, if not all of these failures. Keep in mind that we asked for assembly of 6 modules (4 different production runs): 2 eight-channel, 1 eight-channel without SHARC-B, 2 six-channel Slide 17 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Minor Assembly issues found in prototypes Assembly house did a great job. Some issues: • One capacitor misplaced (module 1) • Software Test Procedure found 2 open address pins on a Temperature Sensor (module 1) • One wrong component placed. IC 511 = NC 7 SZ 125 instead of NC 7 SZ 126 (module 3) • One IC 557 missing (NC 7 SZ 08) (module 5) • One wrong component placed. IC 564 = NC 7 SZ 08 instead of NC 7 SZ 126 (module 5) • Open output pin on buffer, SHARC JTAG chain (module 6) Automatic Optical Inspection would track many, if not all of these failures. Keep in mind that we asked for assembly of 6 modules (4 different production runs): 2 eight-channel, 1 eight-channel without SHARC-B, 2 six-channel Slide 17 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

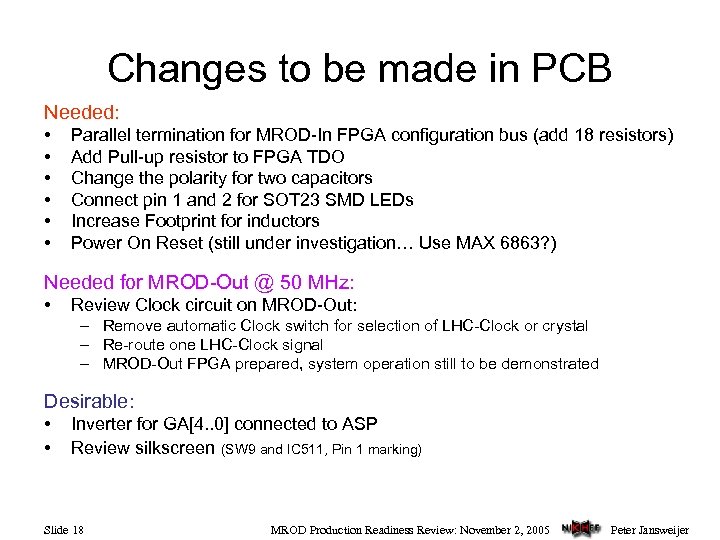

Changes to be made in PCB Needed: • • • Parallel termination for MROD-In FPGA configuration bus (add 18 resistors) Add Pull-up resistor to FPGA TDO Change the polarity for two capacitors Connect pin 1 and 2 for SOT 23 SMD LEDs Increase Footprint for inductors Power On Reset (still under investigation… Use MAX 6863? ) Needed for MROD-Out @ 50 MHz: • Review Clock circuit on MROD-Out: – Remove automatic Clock switch for selection of LHC-Clock or crystal – Re-route one LHC-Clock signal – MROD-Out FPGA prepared, system operation still to be demonstrated Desirable: • • Inverter for GA[4. . 0] connected to ASP Review silkscreen (SW 9 and IC 511, Pin 1 marking) Slide 18 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Changes to be made in PCB Needed: • • • Parallel termination for MROD-In FPGA configuration bus (add 18 resistors) Add Pull-up resistor to FPGA TDO Change the polarity for two capacitors Connect pin 1 and 2 for SOT 23 SMD LEDs Increase Footprint for inductors Power On Reset (still under investigation… Use MAX 6863? ) Needed for MROD-Out @ 50 MHz: • Review Clock circuit on MROD-Out: – Remove automatic Clock switch for selection of LHC-Clock or crystal – Re-route one LHC-Clock signal – MROD-Out FPGA prepared, system operation still to be demonstrated Desirable: • • Inverter for GA[4. . 0] connected to ASP Review silkscreen (SW 9 and IC 511, Pin 1 marking) Slide 18 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Thank you Slide 19 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

Thank you Slide 19 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

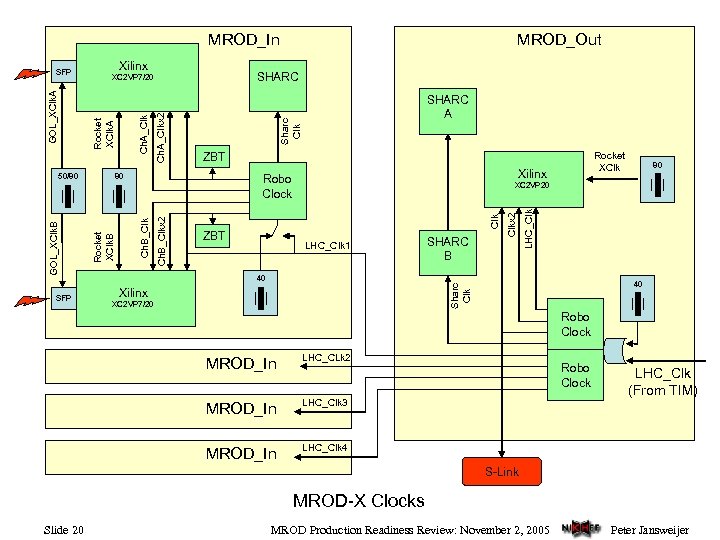

MROD_In Xilinx LHC_Clk 1 40 SHARC B LHC_Clk Ch. B_Clkx 2 ZBT 80 XC 2 VP 20 Clkx 2 Ch. A_Clk Sharc Clk Xilinx Robo Clock Ch. B_Clk Rocket XClk 40 Sharc Clk SFP SHARC A ZBT 80 Rocket XClk. B GOL_XClk. B 50/80 SHARC XC 2 VP 7/20 Rocket XClk. A GOL_XClk. A SFP MROD_Out Xilinx XC 2 VP 7/20 Robo Clock MROD_In LHC_CLk 2 MROD_In LHC_Clk 3 MROD_In LHC_Clk 4 Robo Clock LHC_Clk (From TIM) S-Link MROD-X Clocks Slide 20 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

MROD_In Xilinx LHC_Clk 1 40 SHARC B LHC_Clk Ch. B_Clkx 2 ZBT 80 XC 2 VP 20 Clkx 2 Ch. A_Clk Sharc Clk Xilinx Robo Clock Ch. B_Clk Rocket XClk 40 Sharc Clk SFP SHARC A ZBT 80 Rocket XClk. B GOL_XClk. B 50/80 SHARC XC 2 VP 7/20 Rocket XClk. A GOL_XClk. A SFP MROD_Out Xilinx XC 2 VP 7/20 Robo Clock MROD_In LHC_CLk 2 MROD_In LHC_Clk 3 MROD_In LHC_Clk 4 Robo Clock LHC_Clk (From TIM) S-Link MROD-X Clocks Slide 20 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

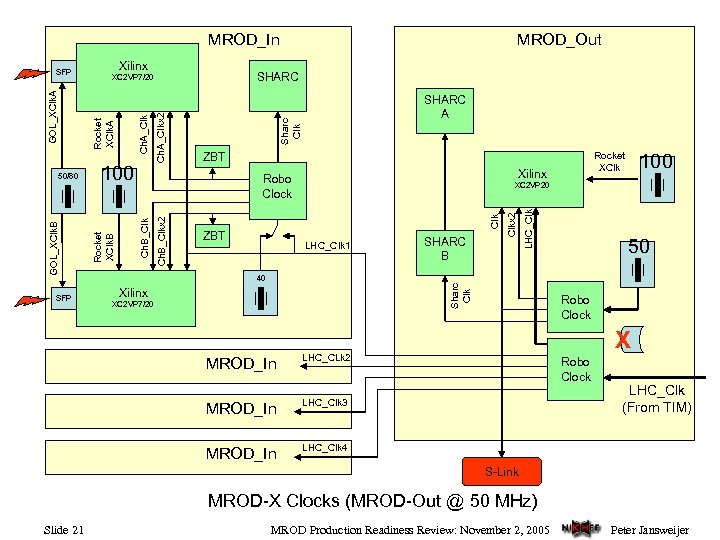

MROD_In Xilinx Sharc Clk Xilinx LHC_Clk 1 40 SHARC B LHC_Clk ZBT 100 XC 2 VP 20 Clk Ch. B_Clkx 2 Robo Clock Ch. B_Clk Rocket XClk ZBT Clkx 2 Ch. A_Clk SHARC A Sharc Clk SFP 100 Rocket XClk. B GOL_XClk. B 50/80 SHARC XC 2 VP 7/20 Rocket XClk. A GOL_XClk. A SFP MROD_Out Xilinx XC 2 VP 7/20 MROD_In X LHC_Clk 3 MROD_In Robo Clock LHC_CLk 2 MROD_In 50 LHC_Clk 4 Robo Clock LHC_Clk (From TIM) S-Link MROD-X Clocks (MROD-Out @ 50 MHz) Slide 21 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer

MROD_In Xilinx Sharc Clk Xilinx LHC_Clk 1 40 SHARC B LHC_Clk ZBT 100 XC 2 VP 20 Clk Ch. B_Clkx 2 Robo Clock Ch. B_Clk Rocket XClk ZBT Clkx 2 Ch. A_Clk SHARC A Sharc Clk SFP 100 Rocket XClk. B GOL_XClk. B 50/80 SHARC XC 2 VP 7/20 Rocket XClk. A GOL_XClk. A SFP MROD_Out Xilinx XC 2 VP 7/20 MROD_In X LHC_Clk 3 MROD_In Robo Clock LHC_CLk 2 MROD_In 50 LHC_Clk 4 Robo Clock LHC_Clk (From TIM) S-Link MROD-X Clocks (MROD-Out @ 50 MHz) Slide 21 MROD Production Readiness Review: November 2, 2005 Peter Jansweijer