лекция_16_Матричные .pptx

- Количество слайдов: 14

Процессоры не традиционных архитектур

Процессоры не традиционных архитектур

Матричные процессоры Матричными системами или матричными процессорами обычно понимается многопроцессорная система, в которой процессоры с помощью той или иной сети связи объединены в матрицу. Задача устройства управления матричным процессором совместно с операционной системой эффективная загрузка матрицы процессоров и эффективная (быстрая) передача промежуточных результатов. В качестве объектов параллелизма могут выступать этапы решения задачи, машинные команды или даже битовые операции, реализующие машинную команду.

Матричные процессоры Матричными системами или матричными процессорами обычно понимается многопроцессорная система, в которой процессоры с помощью той или иной сети связи объединены в матрицу. Задача устройства управления матричным процессором совместно с операционной системой эффективная загрузка матрицы процессоров и эффективная (быстрая) передача промежуточных результатов. В качестве объектов параллелизма могут выступать этапы решения задачи, машинные команды или даже битовые операции, реализующие машинную команду.

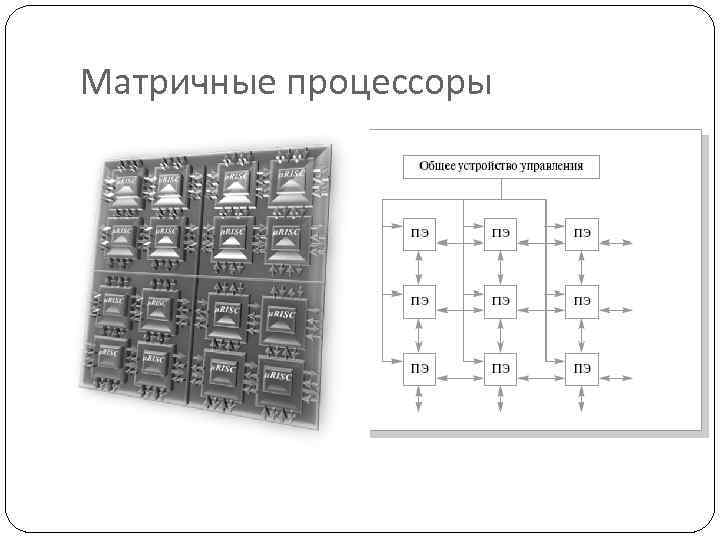

Матричные процессоры

Матричные процессоры

Однородные системы - параллелизм этапов задач В матричной системе элементами матрицы являются полные процессоры с собственной оперативной памятью. Вершины графа вычислительного процесса (этапы) задачи распределяются между процессорами матрицы, а указанные графом связи по управлению и данным реализуются с помощью соединительной сети. Эффективность функционирования такой системы требует однородности этапов (подзадач) по времени выполнения и однородности этапов по требуемым ресурсам, что и объясняет название однородные матричные системы. однородность аппаратной реализации должна быть согласована с однородностью подзадач.

Однородные системы - параллелизм этапов задач В матричной системе элементами матрицы являются полные процессоры с собственной оперативной памятью. Вершины графа вычислительного процесса (этапы) задачи распределяются между процессорами матрицы, а указанные графом связи по управлению и данным реализуются с помощью соединительной сети. Эффективность функционирования такой системы требует однородности этапов (подзадач) по времени выполнения и однородности этапов по требуемым ресурсам, что и объясняет название однородные матричные системы. однородность аппаратной реализации должна быть согласована с однородностью подзадач.

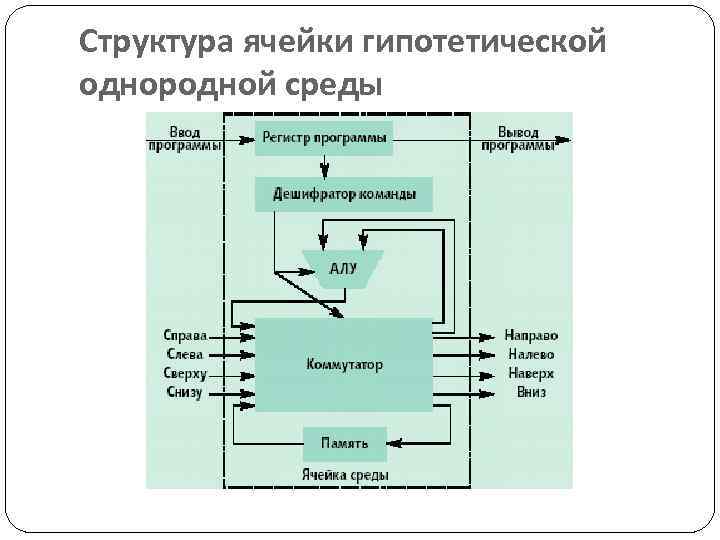

Структура ячейки гипотетической однородной среды

Структура ячейки гипотетической однородной среды

Описание работы В режиме «работа» ячейка выполняет команды над операндами, поступающими из информационных каналов или из внутренней, как правило, однобитной памяти. То, какие операнды использовать, и какую операцию выполнять над ними определяется дешифратором команды, который управляет АЛУ и коммутатором ячейки. Эта же команда определяет, на какие информационные выходы, и что надо выдавать из ячейки. Ячейка, как правило, выполняет следующие команды: транзит данных через ячейку с ее входов с записью или без записи в память ячейки; нет операции; суммирование с учетом или без учета переноса; логическая операция (суммирование по модулю 2, или, и, не -и); генерирование константы. Настройка ячеек может быть статической или динамической. В первом случае команды в регистр программы записываются извне. Во втором случае должен предусматриваться способ, как будет выполняться конфигурирование ячеек (т. е. выполняться загрузка регистров программы ячеек). Ячейки могут двояко воспринимать входную информацию. Когда ячейка формирует выходные сигналы сообразно с конфигурацией, она работает в «комбинационном» режиме или режиме обработки данных, как комбинационный логический блок. Может быть введен дополнительный режим работы ячейки, называемый «режимом модификации» , позволяющий интерпретировать входные данные как новое содержимое регистра программы. Ячейки входят в этот режим и выходят из него через скоординированный обмен с соседними ячейками. Во время этого скоординированного обмена соседняя ячейка предоставляет новую программу (таблицу истинности) для модифицируемой ячейки. Конфигурирование ячейки является чисто локальной операцией, в которой участвуют только две ячейки — та, которая имеет новое содержимое, и та, в которую это содержимое записывается. Благодаря локальности, операции конфигурирования могут производиться одновременно во множестве различных областей матрицы ячеек. Любая из ячеек матрицы может работать в любом из данных режимов. Не существует ячеек с заранее предопределенным режимом работы, он определяется данными от соседних ячеек на входах этой ячейки. В типовой сложной схеме матрица содержит ячейки, которые обрабатывают данные, и ячейки, которые участвуют в реконфигурации других ячеек. Функционирование системы включает тесную кооперацию, взаимодействие, обмен между комбинационными узлами модификации. Можно не только обрабатывать данные на наборе ячеек, но и заставлять ячейки считывать и записывать конфигурацию других ячеек, что позволяет создавать динамические самоконфигурируемые системы, чье поведение во время выполнения может изменяться в зависимости от локальных событий.

Описание работы В режиме «работа» ячейка выполняет команды над операндами, поступающими из информационных каналов или из внутренней, как правило, однобитной памяти. То, какие операнды использовать, и какую операцию выполнять над ними определяется дешифратором команды, который управляет АЛУ и коммутатором ячейки. Эта же команда определяет, на какие информационные выходы, и что надо выдавать из ячейки. Ячейка, как правило, выполняет следующие команды: транзит данных через ячейку с ее входов с записью или без записи в память ячейки; нет операции; суммирование с учетом или без учета переноса; логическая операция (суммирование по модулю 2, или, и, не -и); генерирование константы. Настройка ячеек может быть статической или динамической. В первом случае команды в регистр программы записываются извне. Во втором случае должен предусматриваться способ, как будет выполняться конфигурирование ячеек (т. е. выполняться загрузка регистров программы ячеек). Ячейки могут двояко воспринимать входную информацию. Когда ячейка формирует выходные сигналы сообразно с конфигурацией, она работает в «комбинационном» режиме или режиме обработки данных, как комбинационный логический блок. Может быть введен дополнительный режим работы ячейки, называемый «режимом модификации» , позволяющий интерпретировать входные данные как новое содержимое регистра программы. Ячейки входят в этот режим и выходят из него через скоординированный обмен с соседними ячейками. Во время этого скоординированного обмена соседняя ячейка предоставляет новую программу (таблицу истинности) для модифицируемой ячейки. Конфигурирование ячейки является чисто локальной операцией, в которой участвуют только две ячейки — та, которая имеет новое содержимое, и та, в которую это содержимое записывается. Благодаря локальности, операции конфигурирования могут производиться одновременно во множестве различных областей матрицы ячеек. Любая из ячеек матрицы может работать в любом из данных режимов. Не существует ячеек с заранее предопределенным режимом работы, он определяется данными от соседних ячеек на входах этой ячейки. В типовой сложной схеме матрица содержит ячейки, которые обрабатывают данные, и ячейки, которые участвуют в реконфигурации других ячеек. Функционирование системы включает тесную кооперацию, взаимодействие, обмен между комбинационными узлами модификации. Можно не только обрабатывать данные на наборе ячеек, но и заставлять ячейки считывать и записывать конфигурацию других ячеек, что позволяет создавать динамические самоконфигурируемые системы, чье поведение во время выполнения может изменяться в зависимости от локальных событий.

Матрицы волнового фронта данных параллелизм команд Этот подход к организации матричных систем основан на принципе управления по потоку данных. В матричном процессоре волнового фронта каждый элемент матрицы представляет собой самостоятельное АЛУ с назначенной командной ячейкой. Передавая результаты выполнения команд (поток данных), процессоры активируют друга, создавая динамическую по времени активную процессорную структуру

Матрицы волнового фронта данных параллелизм команд Этот подход к организации матричных систем основан на принципе управления по потоку данных. В матричном процессоре волнового фронта каждый элемент матрицы представляет собой самостоятельное АЛУ с назначенной командной ячейкой. Передавая результаты выполнения команд (поток данных), процессоры активируют друга, создавая динамическую по времени активную процессорную структуру

Классические матричные системы параллелизм объектов Классические матричные системы реализую принцип - «одиночный поток команд множественный поток данных» . Процессорная матрица состоит из множества процессорных элементов (ПЭ) и одного устройства управления (УУ). УУ одновременно передает всем ПЭ одну и ту же команду, поэтому на всех ПЭ одновременно выполняется одна и та же операция, но с разными данными. Для передачи данных между ПЭ используется синхронная сеть связи. Такая архитектура ориентирована, прежде всего, на задачи обработки матриц и обработки изображений.

Классические матричные системы параллелизм объектов Классические матричные системы реализую принцип - «одиночный поток команд множественный поток данных» . Процессорная матрица состоит из множества процессорных элементов (ПЭ) и одного устройства управления (УУ). УУ одновременно передает всем ПЭ одну и ту же команду, поэтому на всех ПЭ одновременно выполняется одна и та же операция, но с разными данными. Для передачи данных между ПЭ используется синхронная сеть связи. Такая архитектура ориентирована, прежде всего, на задачи обработки матриц и обработки изображений.

Система SOLOMON содержит 1024 процессорных элемента, которые соединены в виде матрицы: 32 х32. Каждый процессорный элемент матрицы включает в себя процессор, обеспечивающий выполнение последовательных поразрядных арифметических и логических операций, а также оперативное ЗУ емкостью 16 Кбайт. Длина слова – переменная от 1 до 128 разрядов. Разрядность слов устанавливается программно. По каналам связи от устройства управления передаются команды и общие константы. В процессорном элементе используется так называемая многомодальная логика, которая позволяет каждому процессорному элементу выполнять или не выполнять общую операцию в зависимости от значений обрабатываемых данных. В каждый момент все активные процессорные элементы выполняют одну и ту же операцию над данными, хранящимися в собственной памяти и имеющими один и тот

Система SOLOMON содержит 1024 процессорных элемента, которые соединены в виде матрицы: 32 х32. Каждый процессорный элемент матрицы включает в себя процессор, обеспечивающий выполнение последовательных поразрядных арифметических и логических операций, а также оперативное ЗУ емкостью 16 Кбайт. Длина слова – переменная от 1 до 128 разрядов. Разрядность слов устанавливается программно. По каналам связи от устройства управления передаются команды и общие константы. В процессорном элементе используется так называемая многомодальная логика, которая позволяет каждому процессорному элементу выполнять или не выполнять общую операцию в зависимости от значений обрабатываемых данных. В каждый момент все активные процессорные элементы выполняют одну и ту же операцию над данными, хранящимися в собственной памяти и имеющими один и тот

многомодальность заключается в том, что в каждом процессорном элементе имеется специальный регистр на 4 состояния – регистр моды. Мода (модальность) заносится в этот регистр от устройства управления. При выполнении последовательности команд модальность передается в коде операции и сравнивается с содержимым регистра моды. Если есть совпадения, то операция выполняется. В других случаях процессорный элемент не выполняет операцию, но может, в зависимости от кода, пересылать свои операнды соседнему процессорному элементу. Такой механизм позволяет выделить строку или столбец процессорных элементов, что очень полезно при операциях над матрицами. Взаимодействуют процессорные элементы с периферийным оборудованием через внешний процессор.

многомодальность заключается в том, что в каждом процессорном элементе имеется специальный регистр на 4 состояния – регистр моды. Мода (модальность) заносится в этот регистр от устройства управления. При выполнении последовательности команд модальность передается в коде операции и сравнивается с содержимым регистра моды. Если есть совпадения, то операция выполняется. В других случаях процессорный элемент не выполняет операцию, но может, в зависимости от кода, пересылать свои операнды соседнему процессорному элементу. Такой механизм позволяет выделить строку или столбец процессорных элементов, что очень полезно при операциях над матрицами. Взаимодействуют процессорные элементы с периферийным оборудованием через внешний процессор.

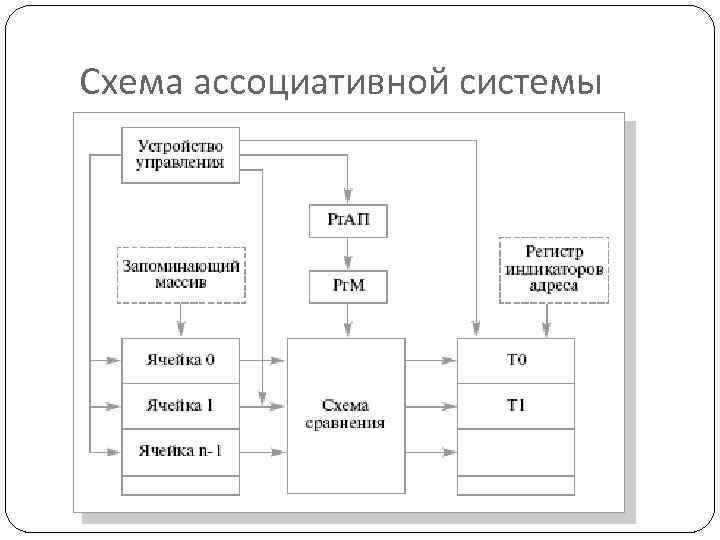

Ассоциативные процессоры Ассоциативный способ обработки данных позволяет преодолеть многие ограничения, присущие адресному доступу к памяти, за счет задания некоторого критерия отбора и проведения необходимых преобразований, только над теми данными, которые удовлетворяют этому критерию. Критерием отбора может быть совпадение с любым элементом данных, достаточным для выделения искомых данных из всех имеющихся. Поиск данных может происходить по фрагменту, имеющему большую или меньшую корреляцию с заданным элементом данных.

Ассоциативные процессоры Ассоциативный способ обработки данных позволяет преодолеть многие ограничения, присущие адресному доступу к памяти, за счет задания некоторого критерия отбора и проведения необходимых преобразований, только над теми данными, которые удовлетворяют этому критерию. Критерием отбора может быть совпадение с любым элементом данных, достаточным для выделения искомых данных из всех имеющихся. Поиск данных может происходить по фрагменту, имеющему большую или меньшую корреляцию с заданным элементом данных.

Ассоциативные системы относятся к классу: один поток команд – множество потоков данных (SIMD = Single Instruction Multiple Data). Эти системы включают большое число операционных устройств, способных одновременно по командам управляющего устройства вести обработку нескольких потоков данных. В ассоциативных вычислительных системах информация на обработку поступает от ассоциативных запоминающих устройств (АЗУ), характеризующихся тем, что информация в них выбирается не по определенному адресу, а по ее содержанию.

Ассоциативные системы относятся к классу: один поток команд – множество потоков данных (SIMD = Single Instruction Multiple Data). Эти системы включают большое число операционных устройств, способных одновременно по командам управляющего устройства вести обработку нескольких потоков данных. В ассоциативных вычислительных системах информация на обработку поступает от ассоциативных запоминающих устройств (АЗУ), характеризующихся тем, что информация в них выбирается не по определенному адресу, а по ее содержанию.

Схема ассоциативной системы

Схема ассоциативной системы

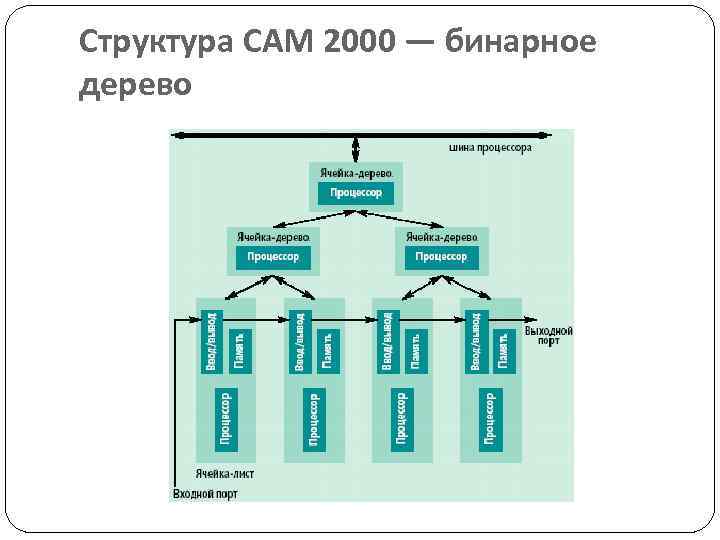

Структура САМ 2000 — бинарное дерево

Структура САМ 2000 — бинарное дерево