Процессор и ОП 1 курс.ppt

- Количество слайдов: 22

Процессор и оперативная память .

Процессор и оперативная память .

Процессор Центральный процессор — это основной рабочий компонент компьютера, который выполняет арифметические и логические операции, заданные программой, управляет вычислительным процессом и координирует работу всех устройств компьютера. Центральный процессор в общем случае содержит в себе: арифметико-логическое устройство; шины данных и шины адресов; регистры; счетчики команд; кэш — очень быструю память малого объема (от 8 до 512 Кбайт); математический сопроцессор чисел с плавающей точкой.

Процессор Центральный процессор — это основной рабочий компонент компьютера, который выполняет арифметические и логические операции, заданные программой, управляет вычислительным процессом и координирует работу всех устройств компьютера. Центральный процессор в общем случае содержит в себе: арифметико-логическое устройство; шины данных и шины адресов; регистры; счетчики команд; кэш — очень быструю память малого объема (от 8 до 512 Кбайт); математический сопроцессор чисел с плавающей точкой.

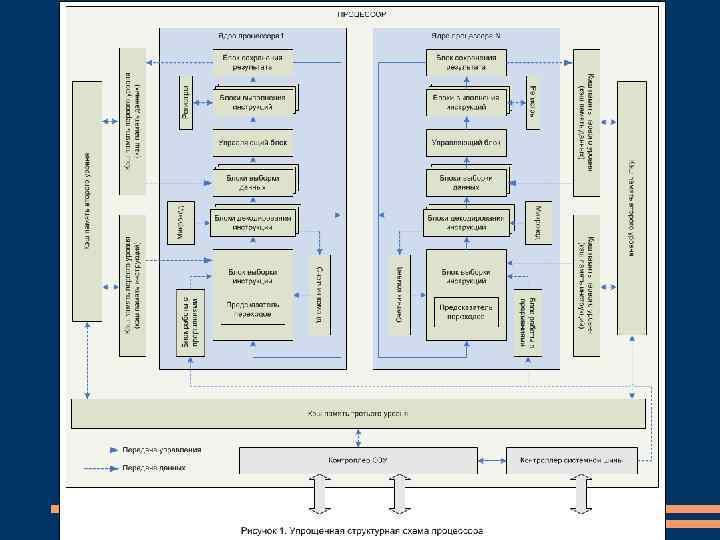

Современный процессор – это сложное и высокотехнологическое устройство, включающее в себя все самые последние достижения в области вычислительной техники и сопутствующих областей науки. Большинство современных процессоров состоит из: одного или нескольких ядер, осуществляющих выполнение всех инструкций; нескольких уровней КЭШ-памяти (обычно, 2 или три уровня), ускоряющих взаимодействие процессора с ОЗУ; контроллера системной шины (DMI, QPI, HT и т. д. )

Современный процессор – это сложное и высокотехнологическое устройство, включающее в себя все самые последние достижения в области вычислительной техники и сопутствующих областей науки. Большинство современных процессоров состоит из: одного или нескольких ядер, осуществляющих выполнение всех инструкций; нескольких уровней КЭШ-памяти (обычно, 2 или три уровня), ускоряющих взаимодействие процессора с ОЗУ; контроллера системной шины (DMI, QPI, HT и т. д. )

Процессоры характеризуется следующими параметрами: типом микроархитектуры; тактовой частотой; набором выполняемых команд; количеством уровней КЭШ-памяти и их объемом; типом и скоростью системной шины; размерами обрабатываемых слов; наличием или отсутствием встроенного контроллера памяти; типом поддерживаемой оперативной памяти; объемом адресуемой памяти; наличием или отсутствием встроенного графического ядра; энергопотреблением.

Процессоры характеризуется следующими параметрами: типом микроархитектуры; тактовой частотой; набором выполняемых команд; количеством уровней КЭШ-памяти и их объемом; типом и скоростью системной шины; размерами обрабатываемых слов; наличием или отсутствием встроенного контроллера памяти; типом поддерживаемой оперативной памяти; объемом адресуемой памяти; наличием или отсутствием встроенного графического ядра; энергопотреблением.

Архитектура процессора Процессор состоит из ячеек. В ячейках процессора данные не хранятся, а обрабатываются. Во время обработки они могут изменяться самыми разными способами. Ячейки процессора называются регистрами. Регистр выполняет функцию кратковременного хранения числа или команды. Над содержимым некоторых регистров специальные электронные схемы могут выполнять некоторые манипуляции. Например, "вырезать" отдельные части команды для последующего их использования или выполнять определенные арифметические операции над числами. Основным элементом регистра является электронная схема, называемая триггером, которая способна хранить одну двоичную цифру (разряд).

Архитектура процессора Процессор состоит из ячеек. В ячейках процессора данные не хранятся, а обрабатываются. Во время обработки они могут изменяться самыми разными способами. Ячейки процессора называются регистрами. Регистр выполняет функцию кратковременного хранения числа или команды. Над содержимым некоторых регистров специальные электронные схемы могут выполнять некоторые манипуляции. Например, "вырезать" отдельные части команды для последующего их использования или выполнять определенные арифметические операции над числами. Основным элементом регистра является электронная схема, называемая триггером, которая способна хранить одну двоичную цифру (разряд).

Ядро процессора – это его основная часть, содержащая все функциональные блоки и осуществляющая выполнение всех логических и арифметических операций. Каждое ядро процессора состоит из нескольких функциональных блоков: блока выборки инструкций; блоков декодирования инструкций; блоков выборки данных; управляющего блока; блоков выполнения инструкций; блоков сохранения результатов; блока работы с прерываниями; ПЗУ, содержащего микрокод; набора регистров; счетчика команд.

Ядро процессора – это его основная часть, содержащая все функциональные блоки и осуществляющая выполнение всех логических и арифметических операций. Каждое ядро процессора состоит из нескольких функциональных блоков: блока выборки инструкций; блоков декодирования инструкций; блоков выборки данных; управляющего блока; блоков выполнения инструкций; блоков сохранения результатов; блока работы с прерываниями; ПЗУ, содержащего микрокод; набора регистров; счетчика команд.

Блок выборки инструкций осуществляет считывание инструкций по адресу, указанному в счетчике команд. Обычно, за такт он считывает несколько инструкций. Количество считываемых инструкций обусловлено количеством блоков декодирования, так как необходимо на каждом такте работы максимально загрузить блоки декодирования. Для того чтобы блок выборки инструкций работал оптимально, в ядре процессора имеется предсказатель переходов. Предсказатель переходов пытается определить, какая последовательность команд будет выполняться после совершения перехода. Это необходимо, чтобы после условного перехода максимально нагрузить конвейер ядра процессора.

Блок выборки инструкций осуществляет считывание инструкций по адресу, указанному в счетчике команд. Обычно, за такт он считывает несколько инструкций. Количество считываемых инструкций обусловлено количеством блоков декодирования, так как необходимо на каждом такте работы максимально загрузить блоки декодирования. Для того чтобы блок выборки инструкций работал оптимально, в ядре процессора имеется предсказатель переходов. Предсказатель переходов пытается определить, какая последовательность команд будет выполняться после совершения перехода. Это необходимо, чтобы после условного перехода максимально нагрузить конвейер ядра процессора.

Блоки декодирования – это блоки, которые занимаются декодированием инструкций, т. е. определяют, что надо сделать процессору, и какие дополнительные данные нужны для выполнения инструкции. Блоки выборки данных осуществляют выборку данных из КЭШ-памяти или ОЗУ, необходимых для выполнения текущих инструкций. Обычно, каждое процессорное ядро содержит несколько блоков выборки данных. Например, в процессорах Intel Core используется по два блока выборки данных для каждого ядра. Управляющий блок на основании декодированных инструкций управляет работой блоков выполнения инструкций, распределяет нагрузку между ними, обеспечивает своевременное и верное выполнение инструкций. Это один из наиболее важных блоков ядра процессора.

Блоки декодирования – это блоки, которые занимаются декодированием инструкций, т. е. определяют, что надо сделать процессору, и какие дополнительные данные нужны для выполнения инструкции. Блоки выборки данных осуществляют выборку данных из КЭШ-памяти или ОЗУ, необходимых для выполнения текущих инструкций. Обычно, каждое процессорное ядро содержит несколько блоков выборки данных. Например, в процессорах Intel Core используется по два блока выборки данных для каждого ядра. Управляющий блок на основании декодированных инструкций управляет работой блоков выполнения инструкций, распределяет нагрузку между ними, обеспечивает своевременное и верное выполнение инструкций. Это один из наиболее важных блоков ядра процессора.

Блоки выполнения инструкций включают в себя несколько разнотипных блоков: ALU – арифметическое логическое устройство; FPU – устройство по выполнению операций с плавающей точкой; блоки для обработки расширения наборов инструкций. Дополнительные инструкции используются для ускорения обработки потоков данных, шифрования и дешифрования, кодирования видео и так далее. Для этого в ядро процессора вводят дополнительные регистры и наборы логики. На данный момент наиболее популярными расширениями наборов инструкция являются: MMX (Multimedia Extensions ) – набор инструкций, разработанный компанией Intel, для ускорения кодирования и декодирования потоковых аудио и видео-данных; SSE (Streaming SIMD Extensions) – набор инструкций, разработанный компанией Intel, для выполнения одной и той же последовательности операций над множеством данных с распараллеливанием вычислительного процесса. Наборы команд постоянно совершенствуются, и на данный момент имеются ревизии: SSE, SSE 2, SSE 3, SSE 4; ATA (Application Targeted Accelerator) – набор инструкций, разработанный компанией Intel, для ускорения работы специализированного программного обеспечения и снижения энергопотребления при работе с такими программами. Эти инструкции могут использоваться, например, при расчете контрольных сумм или поиска данных; 3 DNow – набор инструкций, разработанный компанией AMD, для расширения возможностей набора инструкций MMX; AES (Advanced Encryption Standard) – набор инструкций, разработанный компанией Intel, для ускорения работы приложений, использующих шифрование данных по одноименному алгоритму.

Блоки выполнения инструкций включают в себя несколько разнотипных блоков: ALU – арифметическое логическое устройство; FPU – устройство по выполнению операций с плавающей точкой; блоки для обработки расширения наборов инструкций. Дополнительные инструкции используются для ускорения обработки потоков данных, шифрования и дешифрования, кодирования видео и так далее. Для этого в ядро процессора вводят дополнительные регистры и наборы логики. На данный момент наиболее популярными расширениями наборов инструкция являются: MMX (Multimedia Extensions ) – набор инструкций, разработанный компанией Intel, для ускорения кодирования и декодирования потоковых аудио и видео-данных; SSE (Streaming SIMD Extensions) – набор инструкций, разработанный компанией Intel, для выполнения одной и той же последовательности операций над множеством данных с распараллеливанием вычислительного процесса. Наборы команд постоянно совершенствуются, и на данный момент имеются ревизии: SSE, SSE 2, SSE 3, SSE 4; ATA (Application Targeted Accelerator) – набор инструкций, разработанный компанией Intel, для ускорения работы специализированного программного обеспечения и снижения энергопотребления при работе с такими программами. Эти инструкции могут использоваться, например, при расчете контрольных сумм или поиска данных; 3 DNow – набор инструкций, разработанный компанией AMD, для расширения возможностей набора инструкций MMX; AES (Advanced Encryption Standard) – набор инструкций, разработанный компанией Intel, для ускорения работы приложений, использующих шифрование данных по одноименному алгоритму.

Блок сохранения результатов обеспечивает запись результата выполнения инструкции в ОЗУ по адресу, указанному в обрабатываемой инструкции. Блок работы с прерываниями. Работа с прерываниями – одна из важнейших задач процессора, позволяющая ему своевременно реагировать на события, прерывать ход работы программы и выполнять требуемые от него действия. Благодаря наличию прерываний, процессор способен к псевдопараллельной работе, т. е. к, так называемой, многозадачности. Обработка прерываний происходит следующим образом. Процессор перед началом каждого цикла работы проверяет наличие запроса на прерывание. Если есть прерывание для обработки, процессор сохраняет в стек адрес инструкции, которую он должен был выполнить, и данные, полученные после выполнения последней инструкции, и переходит к выполнению функции обработки прерывания. После окончания выполнения функции обработки прерывания, из стека считываются сохраненные в него данные, и процессор возобновляет выполнение восстановленной задачи.

Блок сохранения результатов обеспечивает запись результата выполнения инструкции в ОЗУ по адресу, указанному в обрабатываемой инструкции. Блок работы с прерываниями. Работа с прерываниями – одна из важнейших задач процессора, позволяющая ему своевременно реагировать на события, прерывать ход работы программы и выполнять требуемые от него действия. Благодаря наличию прерываний, процессор способен к псевдопараллельной работе, т. е. к, так называемой, многозадачности. Обработка прерываний происходит следующим образом. Процессор перед началом каждого цикла работы проверяет наличие запроса на прерывание. Если есть прерывание для обработки, процессор сохраняет в стек адрес инструкции, которую он должен был выполнить, и данные, полученные после выполнения последней инструкции, и переходит к выполнению функции обработки прерывания. После окончания выполнения функции обработки прерывания, из стека считываются сохраненные в него данные, и процессор возобновляет выполнение восстановленной задачи.

Принцип работы ядра процессора 1. 2. 3. 4. 5. 6. 7. Блок выборки инструкций проверяет наличие прерываний. Если прерывание есть, то данные регистров и счетчика команд заносятся в стек, а в счетчик команд заносится адрес команды обработчика прерываний. По окончанию работы функции обработки прерываний, данные из стека будут восстановлены; Блок выборки инструкций из счетчика команд считывает адрес команды, предназначенной для выполнения. По этому адресу из КЭШ-памяти или ОЗУ считывается команда. Полученные данные передаются в блок декодирования; Блок декодирования команд расшифровывает команду, при необходимости используя для интерпретации команды записанный в ПЗУ микрокод. Если это команда перехода, то в счетчик команд записывается адрес перехода и управление передается в блок выборки инструкций (пункт 1), иначе счетчик команд увеличивается на размер команды (для процессора с длинной команды 32 бита – на 4) и передает управление в блок выборки данных; Блок выборки данных считывает из КЭШ-памяти или ОЗУ требуемые для выполнения команды данные и передает управление планировщику; Управляющий блок определяет, какому блоку выполнения инструкций обработать текущую задачу, и передает управление этому блоку; Блоки выполнения инструкций выполняют требуемые командой действия и передают управление блоку сохранения результатов; При необходимости сохранения результатов в ОЗУ, блок сохранения результатов выполняет требуемые для этого действия и передает управление блоку выборки инструкций (пункт 1).

Принцип работы ядра процессора 1. 2. 3. 4. 5. 6. 7. Блок выборки инструкций проверяет наличие прерываний. Если прерывание есть, то данные регистров и счетчика команд заносятся в стек, а в счетчик команд заносится адрес команды обработчика прерываний. По окончанию работы функции обработки прерываний, данные из стека будут восстановлены; Блок выборки инструкций из счетчика команд считывает адрес команды, предназначенной для выполнения. По этому адресу из КЭШ-памяти или ОЗУ считывается команда. Полученные данные передаются в блок декодирования; Блок декодирования команд расшифровывает команду, при необходимости используя для интерпретации команды записанный в ПЗУ микрокод. Если это команда перехода, то в счетчик команд записывается адрес перехода и управление передается в блок выборки инструкций (пункт 1), иначе счетчик команд увеличивается на размер команды (для процессора с длинной команды 32 бита – на 4) и передает управление в блок выборки данных; Блок выборки данных считывает из КЭШ-памяти или ОЗУ требуемые для выполнения команды данные и передает управление планировщику; Управляющий блок определяет, какому блоку выполнения инструкций обработать текущую задачу, и передает управление этому блоку; Блоки выполнения инструкций выполняют требуемые командой действия и передают управление блоку сохранения результатов; При необходимости сохранения результатов в ОЗУ, блок сохранения результатов выполняет требуемые для этого действия и передает управление блоку выборки инструкций (пункт 1).

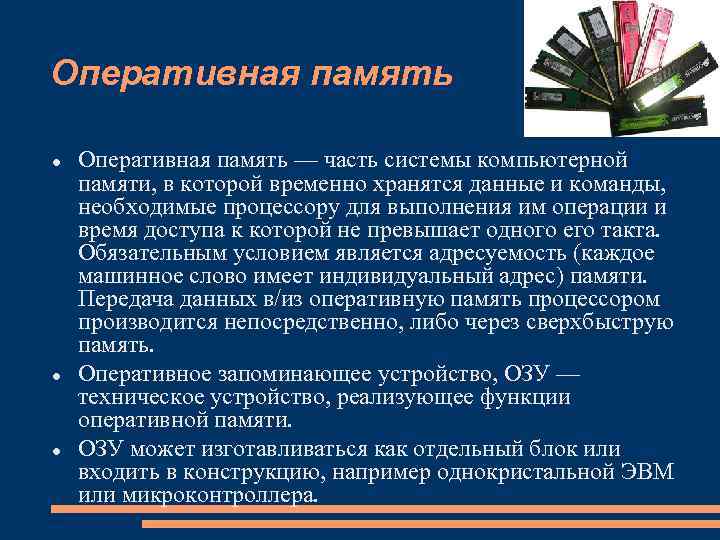

Оперативная память Оперативная память — часть системы компьютерной памяти, в которой временно хранятся данные и команды, необходимые процессору для выполнения им операции и время доступа к которой не превышает одного его такта. Обязательным условием является адресуемость (каждое машинное слово имеет индивидуальный адрес) памяти. Передача данных в/из оперативную память процессором производится непосредственно, либо через сверхбыструю память. Оперативное запоминающее устройство, ОЗУ — техническое устройство, реализующее функции оперативной памяти. ОЗУ может изготавливаться как отдельный блок или входить в конструкцию, например однокристальной ЭВМ или микроконтроллера.

Оперативная память Оперативная память — часть системы компьютерной памяти, в которой временно хранятся данные и команды, необходимые процессору для выполнения им операции и время доступа к которой не превышает одного его такта. Обязательным условием является адресуемость (каждое машинное слово имеет индивидуальный адрес) памяти. Передача данных в/из оперативную память процессором производится непосредственно, либо через сверхбыструю память. Оперативное запоминающее устройство, ОЗУ — техническое устройство, реализующее функции оперативной памяти. ОЗУ может изготавливаться как отдельный блок или входить в конструкцию, например однокристальной ЭВМ или микроконтроллера.

Память динамического типа (англ. DRAM (Dynamic RAM)) Экономичный вид памяти. Для хранения разряда (бита или трита) используется схема, состоящая из одного конденсатора и одного транзистора (в некоторых вариациях конденсаторов два). Такой вид памяти решает, во-первых, проблему дороговизны (один конденсатор и один транзистор дешевле нескольких транзисторов) и вовторых, компактности (там, где в SRAM размещается один триггер, то есть один бит, можно уместить восемь конденсаторов и транзисторов). Так как для регенерации памяти периодически приостанавливаются все операции с памятью, это значительно снижает производительность данного вида ОЗУ.

Память динамического типа (англ. DRAM (Dynamic RAM)) Экономичный вид памяти. Для хранения разряда (бита или трита) используется схема, состоящая из одного конденсатора и одного транзистора (в некоторых вариациях конденсаторов два). Такой вид памяти решает, во-первых, проблему дороговизны (один конденсатор и один транзистор дешевле нескольких транзисторов) и вовторых, компактности (там, где в SRAM размещается один триггер, то есть один бит, можно уместить восемь конденсаторов и транзисторов). Так как для регенерации памяти периодически приостанавливаются все операции с памятью, это значительно снижает производительность данного вида ОЗУ.

Память статического типа (англ. SRAM (Static RAM)) ОЗУ, собранное на триггерах, называется статической памятью с произвольным доступом или просто статической памятью. Достоинство этого вида памяти — скорость. Поскольку триггеры собраны на вентилях, а время задержки вентиля очень мало, то и переключение состояния триггера происходит очень быстро. Данный вид памяти не лишён недостатков. Во-первых, группа транзисторов, входящих в состав триггера, обходится дороже, даже если они вытравляются миллионами на одной кремниевой подложке. Кроме того, группа транзисторов занимает гораздо больше места, поскольку между транзисторами, которые образуют триггер, должны быть вытравлены линии связи. Используется для сверхбыстрого ОЗУ.

Память статического типа (англ. SRAM (Static RAM)) ОЗУ, собранное на триггерах, называется статической памятью с произвольным доступом или просто статической памятью. Достоинство этого вида памяти — скорость. Поскольку триггеры собраны на вентилях, а время задержки вентиля очень мало, то и переключение состояния триггера происходит очень быстро. Данный вид памяти не лишён недостатков. Во-первых, группа транзисторов, входящих в состав триггера, обходится дороже, даже если они вытравляются миллионами на одной кремниевой подложке. Кроме того, группа транзисторов занимает гораздо больше места, поскольку между транзисторами, которые образуют триггер, должны быть вытравлены линии связи. Используется для сверхбыстрого ОЗУ.

DIMM (Dual In-line Memory Module) 64 -разрядные модули памяти DIMM (Dual In-line Memory Module) появились в 1997 г. У этого поколения модулей памяти насчитывается 168 контактов, расположенных с двух сторон текстолитовой платы (по 84 контакта с каждой стороны).

DIMM (Dual In-line Memory Module) 64 -разрядные модули памяти DIMM (Dual In-line Memory Module) появились в 1997 г. У этого поколения модулей памяти насчитывается 168 контактов, расположенных с двух сторон текстолитовой платы (по 84 контакта с каждой стороны).

Для идентификации типа модуля форм-фактора DIMM по объему памяти и типу используемых микросхем на модуле устанавливается микросхема флэш-памяти с записанной в нее служебной информацией (SPD— Serial Presence Detect), доступ к которой происходит по интерфейсу 1~С. Чтобы нельзя было установить неподходящий тип DIMM-модуля, в текстолитовой плате модуля делается несколько прорезей (ключей) среди контактных площадок, а также справа и слева в зоне элементов фиксации модуля на системной плате. Для механической идентификации различных DIMM-модулей используется сдвиг положения двух ключей в текстолитовой плате модуля, расположенных среди контактных площадок. Основное назначение этих ключей — не дать установить в разъем DIMM-модуль с неподходящим напряжением питания микросхем памяти. Кроме того, расположение ключа или ключей определяет наличие или отсутствие буфера данных и т. д. Для модернизированных модулей DIMM типа DDR SDRAM число контактов увеличено до 184.

Для идентификации типа модуля форм-фактора DIMM по объему памяти и типу используемых микросхем на модуле устанавливается микросхема флэш-памяти с записанной в нее служебной информацией (SPD— Serial Presence Detect), доступ к которой происходит по интерфейсу 1~С. Чтобы нельзя было установить неподходящий тип DIMM-модуля, в текстолитовой плате модуля делается несколько прорезей (ключей) среди контактных площадок, а также справа и слева в зоне элементов фиксации модуля на системной плате. Для механической идентификации различных DIMM-модулей используется сдвиг положения двух ключей в текстолитовой плате модуля, расположенных среди контактных площадок. Основное назначение этих ключей — не дать установить в разъем DIMM-модуль с неподходящим напряжением питания микросхем памяти. Кроме того, расположение ключа или ключей определяет наличие или отсутствие буфера данных и т. д. Для модернизированных модулей DIMM типа DDR SDRAM число контактов увеличено до 184.

Динамическая оперативная память (DRAM – Dynamic Random Access Memory) – энергозависимая полупроводниковая память с произвольным доступом. На данный момент – это основной тип оперативной памяти, используемый в современных персональных компьютерах и обеспечивающий наилучший показатель отношения цена-качество по сравнению с другими типами оперативной памяти Динамическая оперативная память (DRAM – Dynamic Random Access Memory) – энергозависимая память с произвольным доступом, каждая ячейка которой состоит из одного конденсатора и нескольких транзисторов. Конденсатор хранит один бит данных, а транзисторы играют роль ключей, удерживающих заряд в конденсаторе и разрешающих доступ к конденсатору при чтении и записи данных.

Динамическая оперативная память (DRAM – Dynamic Random Access Memory) – энергозависимая полупроводниковая память с произвольным доступом. На данный момент – это основной тип оперативной памяти, используемый в современных персональных компьютерах и обеспечивающий наилучший показатель отношения цена-качество по сравнению с другими типами оперативной памяти Динамическая оперативная память (DRAM – Dynamic Random Access Memory) – энергозависимая память с произвольным доступом, каждая ячейка которой состоит из одного конденсатора и нескольких транзисторов. Конденсатор хранит один бит данных, а транзисторы играют роль ключей, удерживающих заряд в конденсаторе и разрешающих доступ к конденсатору при чтении и записи данных.

На работу с такими модулями рассчитаны различные модификации процессоров Pentium 4 и Celeron, а также Athlon и Semptron. Для идентификации напряжения питания модулей DDR SDRAM служат соответствующие ключи. На модулях типа Registered DIMM (с буферизацией данных) между контактами и микросхемами DRAM устанавливается одна или две микросхемы временного хранения данных. В низкопрофильных модулях микросхемы буферизации устанавливаются в середине модуля (или под основными микросхемами). Так как скоростные микросхемы памяти, как и процессоры, выделяют очень много тепла, то наиболее продвинутые модули оснащаются радиаторами.

На работу с такими модулями рассчитаны различные модификации процессоров Pentium 4 и Celeron, а также Athlon и Semptron. Для идентификации напряжения питания модулей DDR SDRAM служат соответствующие ключи. На модулях типа Registered DIMM (с буферизацией данных) между контактами и микросхемами DRAM устанавливается одна или две микросхемы временного хранения данных. В низкопрофильных модулях микросхемы буферизации устанавливаются в середине модуля (или под основными микросхемами). Так как скоростные микросхемы памяти, как и процессоры, выделяют очень много тепла, то наиболее продвинутые модули оснащаются радиаторами.

В некоторых тяжелых случаях необходимо использование принудительного охлаждения модулей, в частности, если выполняется разгон памяти. В модулях DDR 2 SDRAM число контактов увеличено до 240 Для идентификации модулей DDR 2 SDRAM служат соответствующие ключи. В модулях DDR 3 SDRAM число контактов оставлено 240, как и у модулей DDR 2, но изменено положение ключа. По разводке контактов и напряжению питания модули DDR 2 и DDR 3 несовместимы. Ключ у модулей DDR 3 сдвинут относительно ключа DDR 2 примерно на десяток контактных площадок. Внимание! Не увеличивайте напряжение питания модулей памяти DDR 3 при работе с процессором Intel Core i 7 выше 1, 65 В, так как это может вывести из строя входные цепи процессора.

В некоторых тяжелых случаях необходимо использование принудительного охлаждения модулей, в частности, если выполняется разгон памяти. В модулях DDR 2 SDRAM число контактов увеличено до 240 Для идентификации модулей DDR 2 SDRAM служат соответствующие ключи. В модулях DDR 3 SDRAM число контактов оставлено 240, как и у модулей DDR 2, но изменено положение ключа. По разводке контактов и напряжению питания модули DDR 2 и DDR 3 несовместимы. Ключ у модулей DDR 3 сдвинут относительно ключа DDR 2 примерно на десяток контактных площадок. Внимание! Не увеличивайте напряжение питания модулей памяти DDR 3 при работе с процессором Intel Core i 7 выше 1, 65 В, так как это может вывести из строя входные цепи процессора.

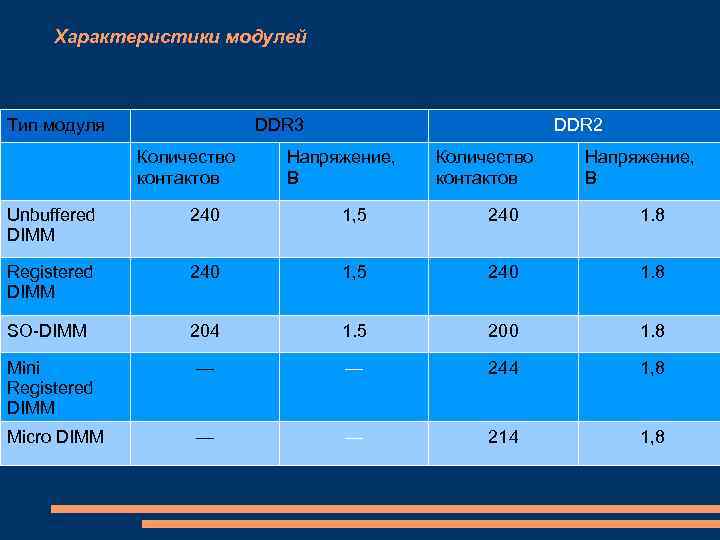

Характеристики модулей Тип модуля DDR 3 Количество контактов DDR 2 Напряжение, В Количество контактов Напряжение, В Unbuffered DIMM 240 1, 5 240 1. 8 Registered DIMM 240 1, 5 240 1. 8 SO-DIMM 204 1. 5 200 1. 8 Mini Registered DIMM — — 244 1, 8 Micro DIMM — — 214 1, 8

Характеристики модулей Тип модуля DDR 3 Количество контактов DDR 2 Напряжение, В Количество контактов Напряжение, В Unbuffered DIMM 240 1, 5 240 1. 8 Registered DIMM 240 1, 5 240 1. 8 SO-DIMM 204 1. 5 200 1. 8 Mini Registered DIMM — — 244 1, 8 Micro DIMM — — 214 1, 8