УБЗ2-1_12.ppt

- Количество слайдов: 26

Предмет: “УСТРІЙ ТА БОЙОВЕ ЗАСТОСУВАННЯ КЗА 86 Ж 6” Тема 2. Типові елементи та вузли апаратури Заняття 1. Принцип побудови основних функціональних вузлів Навчальні питання: 1. Призначення, склад, принцип роботи регістрів (ТЕЗ ЛУШ-0 -011). 2. Призначення, склад, принцип роботи. Лічильники (ТЕЗ-ЛУШ-0 -022), суматори (ТЕЗ ЛУШ-0 -009), шифратори (ТЕЗ ЛУШ-1 -016), дешифратори ( ТЕЗ ЛУШ-0 -008 ), аналоговий (ТЕЗ АНШ-118). 1

Література 1. 2. 3. Лекція. Робочий зошит студента. Устрій та бойове застосування КЗА 86 Ж 6. Частина І. К. , - 2001. - 206 с. 2

1. Призначення, склад, принцип роботи регістрів (ТЕЗ ЛУШ-0 -011) ТЕЗ-ЛУШ-0 -011 (регістр) призначений для записування, тимчасового зберігання та видачі інформації. В ТЕЗi 16 синхронних тригерів типу DV. Входи D 1 -D 16 – iнформацiйнi входи тригерів, 1÷ 16 – парафазнi виходи вiдповiдних тригерів. Входи синхронізації тригерів об'єднані та підключені до контакту роз`єднання «СИНХРОНИЗАЦИЯ» (С). 50 R 15 C 61 11 5 12 6 10 7 46 17 21 18 22 16 23 29 55 30 56 60 28 68 59 65 64 42 53 54 41 49 43 VA V 1 D 1 V 2 D 2 V 3 D 3 V 4 D 4 V 5 D 5 V 6 D 6 V 7 D 7 V 8 D 8 VB V 9 D 10 V 10 D 1 1 D V 11 12 D 1 3 D V 12 14 D 1 5 D 16 RG 0 -011 4 1 3 9 2 8 14 3 13 20 4 19 25 5 24 27 6 26 32 7 31 34 8 33 69 9 70 66 10 67 62 11 63 57 12 58 51 13 52 47 14 48 44 15 45 39 16 40 3

50 R 15 C 61 Для керування синхронізацією служать входи «ГРУППОВОЕ РАЗРЕШЕНИЕ» (Va, Vb) i «РАЗРЕШЕНИЕ» (V 1 -V 8, V 9 -V 12). 11 5 12 6 10 7 46 17 21 18 22 16 23 29 55 30 56 60 28 68 59 65 64 42 53 54 41 49 43 VA V 1 D 1 V 2 D 2 V 3 D 3 V 4 D 4 V 5 D 5 V 6 D 6 V 7 D 7 V 8 D 8 VB V 9 D 10 V 10 D 1 1 D V 11 12 D 1 3 D V 12 14 D 1 5 D 16 RG 0 -011 4 1 3 9 2 8 14 3 13 20 4 19 25 5 24 27 6 26 32 7 31 34 8 33 69 9 70 66 10 67 62 11 63 57 12 58 51 13 52 47 14 48 44 15 45 39 16 40 4

В групі тригерів 1 - 8 керування синхронiзацiею проводиться або: сигналом на вході Va – паралельно у 8 тригерах, сигналами на входах V 1 -V 8 – в кожному тригері окремо. При цьому в першому випадку входи V 1 -V 8, а у другому – вхід Va повинен бути з`єднаний з корпусом. В групі тригерів 9+16 аналогічне призначення мають вхід V 6 та входи V 9 -V 12 для чотирьох пар тригерів. 50 R 15 C 61 11 5 12 6 10 7 46 17 21 18 22 16 23 29 55 30 56 60 28 68 59 65 64 42 53 54 41 49 43 VA V 1 D 1 V 2 D 2 V 3 D 3 V 4 D 4 V 5 D 5 V 6 D 6 V 7 D 7 V 8 D 8 VB V 9 D 10 V 10 D 1 1 D V 11 12 D 1 3 D V 12 14 D 1 5 D 16 RG 0 -011 4 1 3 9 2 8 14 3 13 20 4 19 25 5 24 27 6 26 32 7 31 34 8 33 69 9 70 66 10 67 62 11 63 57 12 58 51 13 52 47 14 48 44 15 45 39 16 40 5

50 R 15 C 61 Скидання регістру в нульове положення здiснюється асинхронно сигналом логічного нуля на вході «УСТАНОВКА В НУЛЬ» (R), який надходить одночасно на всі 16 тригерів. 11 5 12 6 10 7 46 17 21 18 22 16 23 29 55 30 56 60 28 68 59 65 64 42 53 54 41 49 43 VA V 1 D 1 V 2 D 2 V 3 D 3 V 4 D 4 V 5 D 5 V 6 D 6 V 7 D 7 V 8 D 8 VB V 9 D 10 V 10 D 1 1 D V 11 12 D 1 3 D V 12 14 D 1 5 D 16 RG 0 -011 4 1 3 9 2 8 14 3 13 20 4 19 25 5 24 27 6 26 32 7 31 34 8 33 69 9 70 66 10 67 62 11 63 57 12 58 51 13 52 47 14 48 44 15 45 39 16 40 6

Входи 50 1 1 133 ЛА 6 У 43 Б 2 1 9 133 ЛА 6 У 43 Б 2 6 R 1 1 133 ЛА 6 У 26 Б 10 0 1 15 61 1 133 ЛА 6 У 44 Е 6 1 1 & 13 133 ЛА 3 1 12 У 30 1 C 1 4 133 ЛА 6 У 25 В 10 3 X 1 Гн 5 6 1 11 Гн 12 t Va tn+1 Qn+1 8 n V 1 D 1 1 1 133 ЛА 6 У 27 А 8 6 X 1 0 0 0 0 0 1 3 12 133 ЛА 6 У 28 Е 8 X 0 9 1 133 ЛА 6 У 44 Е 6 1 0 1 1 11 9 133 ЛА 6 У 45 Е 10 0 Qn Гн 1 8 50 R 15 C 61 Гн 4 8 11 5 12 6 10 7 46 17 21 18 22 16 Qn 0 1 23 29 55 30 56 60 28 68 Б 6 11 & 1 133 ЛА 3 2 У 1 А 5 3 4 & 5 133 ЛА 4 3 У 18 А 3 Гн 14 11 Представлена таблиця iстинностi DV & тригера 3 &при 9 & 1 8 10 5 10 133 ЛА 4 8 133 ЛА 3 2 133 ЛР 1 9 У 2 синхронiзацiєю керуваннi 11 У 19 У 10 4 Б 3 Б 5 Б 9 сигналом на входi Vа (паралельно & & 1 у 8 тригерах) 3 1 6 5 133 ЛА 3 9 133 ЛР 1 6 2 У 2 Б 5 133 ЛА 3 4 У 2 Б 5 10 У 10 Б 9 Виходи 6 3 8 4 59 65 64 42 53 54 41 49 43 VA V 1 D 1 V 2 D 2 V 3 D 3 V 4 D 4 V 5 D 5 V 6 D 6 V 7 D 7 V 8 D 8 VB V 9 D 10 V 10 D 1 1 D V 11 12 D 1 3 D V 12 14 D 1 5 D 16 RG 0 -011 4 1 3 9 2 8 14 3 13 20 4 19 25 5 24 27 6 26 32 7 31 34 8 33 69 9 70 66 10 67 62 11 63 57 12 58 51 13 52 47 14 48 44 15 45 39 16 40 7

Входи 50 R 0 1 1 133 ЛА 6 У 43 Б 2 1 1 133 ЛА 6 У 26 Б 10 1 6 0 3 1 9 133 ЛА 6 У 43 Б 2 1 4 133 ЛА 6 У 25 В 10 Гн 12 8 0 tn R 1 6 1 1 133 ЛА 6 У 27 А 8 1 3 12 133 ЛА 6 У 28 Е 8 15 c 59 VA 11 V 1 0 5 D 1 1 & 12 133 ЛА 3 13 У 30 Б 6 & 2 133 ЛА 3 1 У 23 В 2 9 & 10 133 ЛА 4 11 У 19 Б 3 & 1 133 ЛА 3 2 У 2 Б 5 11 9 1 133 ЛА 6 У 45 Е 10 1 9 133 ЛА 6 У 44 Е 6 6 3 4 & 5 133 ЛА 4 3 У 34 В 8 1 8 3 V 1 D 1 Qn+1 Гн 4 8 0 0 X X 0 1 1 0 0 0 Qn 1 0 1 Qn 1 1 8 1 1 1 Гн 1 11 0 Va 0 0 1 1 Гн 5 1 1 133 ЛА 6 У 44 Е 6 1 0 C tn+1 0 0 1 1 Гн 14 6 1 & 10 133 ЛА 3 9 У 2 Б 5 & 5 133 ЛА 3 4 У 2 Б 5 8 6 0 1 3 & 1 2 133 ЛР 1 У 10 4 Б 9 1 & 1 9 133 ЛР 1 У 10 10 Б 9 Виходи 6 3 1 вих 8 4 1 вих 1 0 8

Вхо 50 R 1 1 д и 133 ЛА 6 У 43 Б 2 1 1 133 ЛА 6 У 26 Б 10 1 9 133 ЛА 6 У 43 Б 2 6 1 4 133 ЛА 6 У 25 В 10 3 Гн 12 8 6 tn 1 1 133 ЛА 6 У 27 А 8 3 12 1 133 ЛА 6 У 28 Е 8 Гн 5 15 S 61 VA 11 V 1 5 D 1 1 1 133 ЛА 6 У 44 Е 6 & 13 133 ЛА 3 12 У 30 Б 6 & 1 133 ЛА 3 2 У 1 А 5 9 & 10 133 ЛА 4 11 У 19 Б 3 & 1 133 ЛА 3 2 У 2 Б 5 1 9 133 ЛА 6 У 44 Е 6 6 11 9 1 133 ЛА 6 У 45 Е 10 Гн 4 3 Гн 1 8 8 3 & 5 133 ЛА 3 4 У 2 Б 5 8 6 1 & 1 9 133 ЛР 1 У 10 10 Б 9 D 1 Qn+1 X 0 0 Qn 1 0 0 1 Qn 0 1 6 3 & 1 2 133 ЛР 1 У 10 4 Б 9 Va V 1 0 X 0 1 1 0 Гн 14 & 10 133 ЛА 3 9 У 2 Б 5 C 1 1 0 8 11 4 & 5 133 ЛА 4 3 У 18 А 3 R tn+1 Виход 6 3 и 1 вих 8 Представлена таблиця iстинностi DV тригера при керуваннi синхронiзацiею сигналом на входi V 1 (iндивидуально одним тригером). 4 1 вих 9

2. Призначення, склад, принцип роботи. Лічильник (ТЕЗ-ЛУШ-0 -022), суматор (ТЕЗ ЛУШ-0 -009), шифратор (ТЕЗ ЛУШ-1 -016), дешифратор ( ТЕЗ ЛУШ-0 -008 ), аналоговий (ТЕЗ АНШ-118) 10

ТЕЗ-ЛУШ-0 -022 (лічильник) – призначений для реверсивного рахунку. ТЕЗ мiстить 4 чотирьохрозряднi лічильника з паралельним переносом. Iнверсiйнi входи R 1, R 2 служать для встановлення лічильникiв в нуль. Перший та другий лічильники встановлюються в нуль при логiчному « 0» на входi R 2. Встановка в нуль вiдбувається з перевагою, та по її закiнченнi на входi R 1, R 2 повинна бути подана логiчна « 1» . 11

Лічильники побудованi на JКтригерах. Записування розрядiв початкового числа (входи D 0 -D 3) виконується паралельно та асинхронно, попереднє встановлення в нуль не потрiбне. Для встановлення служать входи «ЗАПИСЬ» (ЗАП), «ПЛЮС 1» (+1), «МИНУС 1» (-1). Виходи всiх розрядiв (0 +3) – однофазнi, лише прямi. Переповнення лiчильника iдентифiкуеться двома сигналами: потенцiальним сигналом «ПЕРЕНОС» (Р) та iмпульсним сигналом «ПЕРЕНОС СИНХРОНИЗИРЕМЫЙ» (РС 12 логiчний добуток РЛС).

З лiчильникiв ТЕЗа-ЛУШ-0 -022 шляхом безпосереднього їх з`єднання можна побудувати багатотетраднi лічильники розряднiстю до 16. Для цiєї цiлi передбаченi входи «ПЕРЕНОС» (Р 0 до другого, третього та четвертого личильникiв. Побудову багатотетрадного лiчильника необхідно виконувати слiдуючим чином. Розташувати лiчильники ТЕЗа-ЛУШ-0 -022 згiдно старшинства тетрад в порядку зростання числа виходiв «Р» . 13

Пiдключити до входiв Р кожної тетради виходи Р попереднiх тетрад. Використати в якостi молодшої тетради перший лiчильник, який немає виходiв Р. Об`єднати однойменнi входи С, Р, ЗАП, +1, -1. У лiчильника будь-якої розрядностi невикористанi входи Р повиннi бути з`єднані до Иоп. При побудовi лiчильникiв великої розрядностi необхiднi додатковi мiкросхеми для складання переносiв у п`яту i т. д. тетради, та необхiдно враховувати вiдповiдне збiльшення часу. 14

ТЕЗ-ЛУШ-0 -009 (суматор) являє собою комбінаційну схему, передбачену для алгебраїчного додавання (А + Б) двох чисел, а також для виконання порозрядних операцій «I» , «АБО» , «ДОДАВАННЯ ПО МОДУЛЮ 2» . При додаваннi числа повиннi бути поданi на входи суматора (А, Б) у додатковому кодi. Результат отримується в додатковому коді на виходах Е. Можна подати один з доданкiв у зворотньому кодi та одночасно пiдключити його знаковий розряд до тих входiв «ПЕРЕНОС» (Р), якi на рис. 5 позначенi «ПЛЮС 1» (+1). 15

Дiя А-Б реалiзується як складання А + (-Б). Якщо виходити з додаткових кодiв чисел А, Б (наприклад, числа зчитуються з пам`ятi у додатковому кодi), то зручно зробити слiдуючим чином: проiнвертувати додатковий вхід вiднiмаємого Б i подати на входи Б, а до виходiв +1 пiдвести сигнал логiчна « 1» . Для керування служать входи «РАЗРЕШЕНИЕ И» (И), «РАЗРЕШЕНИЕ ИЛИ» (ИЛИ), «РАЗРЕШЕНИЕ СЛОЖЕНИЯ ПО МОДУЛЮ 2» (+), «УСТАНОВКА В НУЛЬ» (R). 16

З метою побудови з ТЕЗ-ЛУШ-0009 багатотетрадних суматорiв надпаралельного типу на роз`єднання ТЕЗу виведенi сигнали «ПЕРЕНОС СТАРШЕЙ ТЕТРАДЫ» (Р 1), «ПЕРЕНОС МЛАДШЕЙ ТЕТРАДЫ» (Р 2), «РАЗРЕШЕНИЕ СКВОЗНОГО ПЕРЕНОСА СТАРШЕЙ И МЛАДШЕЙ ТЕТРАД» (V 1, V 2); крiм того iснує сiм входiв «ПЕРЕНОС» (Р 1 + Р 7) та десять входiв «РАЗРЕШЕНИЕ» (V 1 V 10). 17

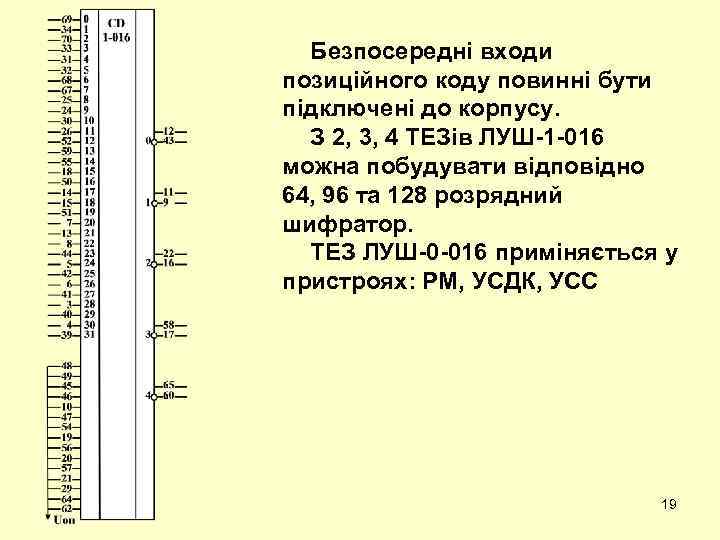

ТЕЗ-ЛУШ-1 -016 (шифратор) передбачений для перетворення 32 розрядного позиційного коду, що містить одиницю лише у одному розряді, у 5 -розрядний двiйковий код. На виходах 0 + 4 ТЕЗ ЛУШ-1 -016 встановлюється парафазний двiйковий код номера входа (одного з входiв 0 + 31 позицiйного кода), що знаходиться у станi логiчної « 1» . 18

Безпосереднi входи позицiйного коду повиннi бути пiдключенi до корпусу. З 2, 3, 4 ТЕЗiв ЛУШ-1 -016 можна побудувати вiдповiдно 64, 96 та 128 розрядний шифратор. ТЕЗ ЛУШ-0 -016 примiняється у пристроях: РМ, УСДК, УСС 19

ТЕЗ ЛУШ-0 -008 (дешифратор) передбачено для перетворення двiйкового N-розрядного парафазного коду в 2 N-розрядний код, що містить одиницю лише в одному розряді. 20

В залежностi вiд схеми включення, ТЕЗ ЛУШ-0 -008 може бути використаний у слiдуючих режимах: • 4 дешифратора на 3 входа, • 2 дешифратора на 4 входа, • 1 дешифратор на 5 входiв. Кожний дешифратор має керуючий вхiд V. Якщо сигнал на входi V – логiчний « 0» , виконується дешифрування. Якщо ж сигнал на входi V – логiчна « 1» , то на вiдповiдних виходах виникають сигнали логiчного « 0» незалежно вiд вхiдного коду. ТЕЗ ЛУШ-0 -008 в КЗА 86 Ж 6 примiняється в слiдуючих пристроях; 21 РМ, СВ, УИ, УОИ, УСДК.

ТЕЗ-АНШ-118 (перетворювач напруга – код) призначений для перетворення напруги у пропорцiйний йому позицiйний код, в якому номер розряду, що мiстить одиницю, пропорцiйний до числа, яке вiдображається. Цей код на виходах ТЕЗа запам'ятовується тригерами, якi встановлюються в нуль при подачi на вхід «УСТАНОВКА В НУЛЬ» (R) сигналу логiчної « 1» та приймають iнформацiю при подачi на вхід «СИНХРОНИЗАЦИЯ» (С) сигналу 22 логiчного « 0» .

При прийомi iнформацiї на входi R повинен бути присутнiм сигнал логiчного « 0» . Один ТЕЗ-АНШ-118 дозволяє отримати восьмирозрядний позицiйний код, який вiдповiдає трьохрозрядному двiйковому коду. Далi перетворення позицiйного коду в двiйковий здiйснюється за допомогою шифратора ТЕЗ-ЛУШ-1 -016. 23

В залежностi вiд величин еталонних напруг Ео 1 та Ео 2 можна побудувати перетворювач напруг на рiзнi вхiднi напруги в межах вiд -1, 6 В до -8 В. При цьому рiзниця напруг Ео 1 та Ео 2 визначає максимальну величину змiни перетворюємої вхiдної напруги, а величина Ео 2 – початковий вхiдний рiвень, при перевищеннi якого виконується перетворення. 24

Для отримання 16 -ти, 32 -х розрядного позицiйного коду використовуються вiдповiдно 2 або 4 ТЕЗ-АНШ-118. Дiапазон напруг, що перетворюються, не залежить вiд кiлькостi розрядiв та визначається величинами Ео 1 та Ео 2. 25

ТЕЗ-АНШ-118 дозволяє використовувати один з розрядiв у якостi схеми порiвняння двох аналогових сигналiв А 1 та В 1 (компара 2626 тор), що не перебiльшують по абсолютнiй величинi 9 В. При цьому останнi сiм розрядiв можуть бути використанi по своєму прямому призначенню. 26

УБЗ2-1_12.ppt