f3bf75351a4c18ebd144782996cd73cf.ppt

- Количество слайдов: 21

Practical Aspects of Reliability Analysis for IC Designs T. Pompl, C. Schlünder, M. Hommel, H. Nielen, J. Schneider

Purpose Address practical links between IC design and reliability of IC operation. Demonstrate state of the art aspects as well as future issues. Direct input of experts working in the field of process reliability and ESD. What’s required in EDA tools to promote design-in reliability?

Outline Gate oxide integrity Device reliability Interconnect reliability Electrostatic discharge (ESD) Summary

Gate oxide integrity: Overshoot events Each electric stress consumes oxide lifetime; degradation is cumulative! Main driver of degradation is the voltage drop across gate oxide (other driver: temp. , active area). Statistical nature: qualified for e. g. <10 ppm failure @[Vdd, 10 y, 10 mm 2, 100°C]. Voltage overshoot is an additional electric stress. Analysis of voltage overshoot between any terminal and gate (guideline: > 10% of Vdd). Needed: voltage amplitude, duty cycle, device type, terminals (e. g. gate and drain).

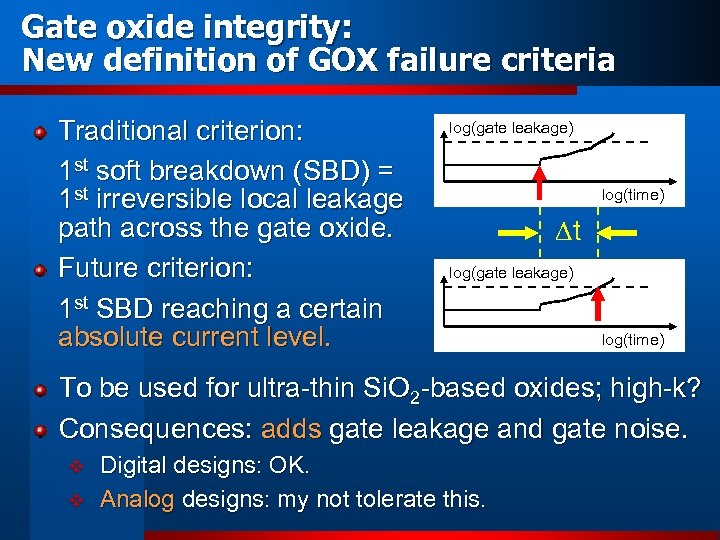

Gate oxide integrity: New definition of GOX failure criteria Traditional criterion: 1 st soft breakdown (SBD) = 1 st irreversible local leakage path across the gate oxide. Future criterion: 1 st SBD reaching a certain absolute current level. log(gate leakage) log(time) Dt log(gate leakage) log(time) To be used for ultra-thin Si. O 2 -based oxides; high-k? Consequences: adds gate leakage and gate noise. v v Digital designs: OK. Analog designs: my not tolerate this.

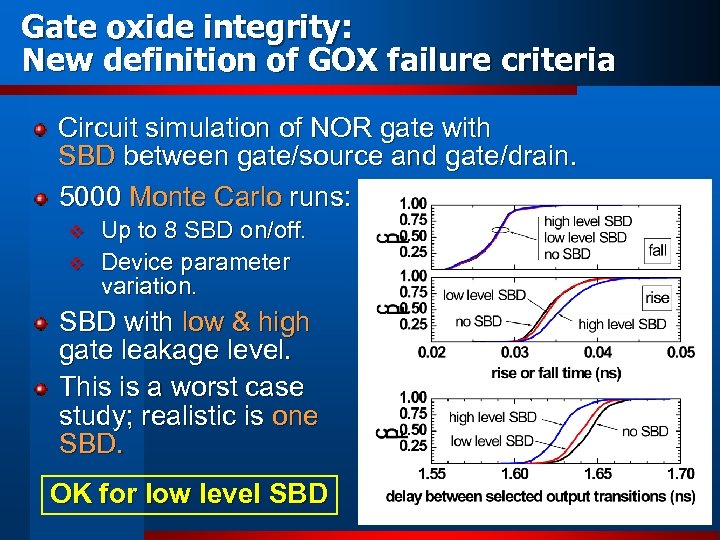

Gate oxide integrity: New definition of GOX failure criteria Circuit simulation of NOR gate with SBD between gate/source and gate/drain. 5000 Monte Carlo runs: v v Up to 8 SBD on/off. Device parameter variation. SBD with low & high gate leakage level. This is a worst case study; realistic is one SBD. OK for low level SBD

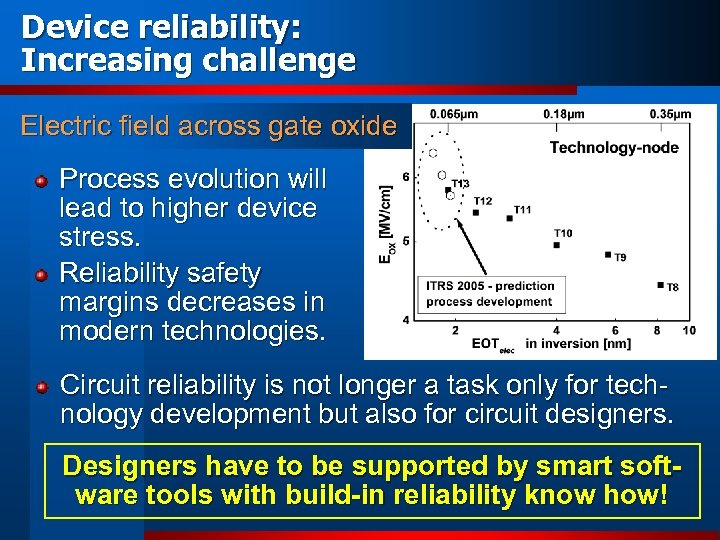

Device reliability: Increasing challenge Electric field across gate oxide Process evolution will lead to higher device stress. Reliability safety margins decreases in modern technologies. Circuit reliability is not longer a task only for technology development but also for circuit designers. Designers have to be supported by smart software tools with build-in reliability know how!

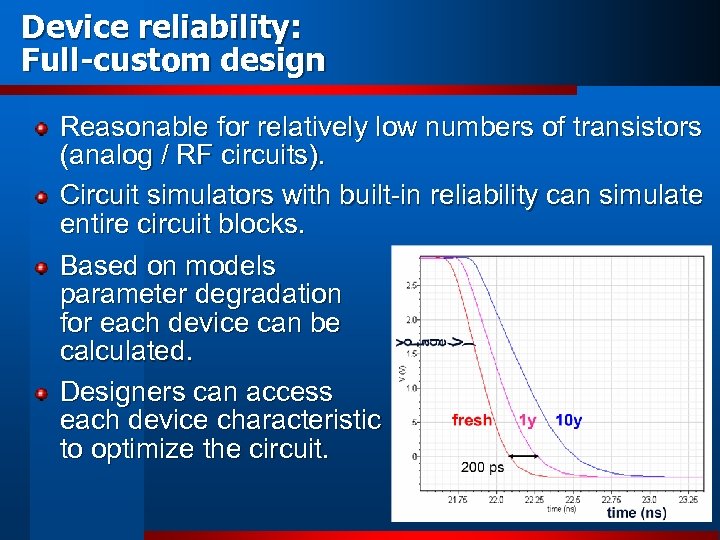

Device reliability: Full-custom design Reasonable for relatively low numbers of transistors (analog / RF circuits). Circuit simulators with built-in reliability can simulate entire circuit blocks. Based on models parameter degradation for each device can be calculated. Designers can access each device characteristic to optimize the circuit.

Device reliability: Constrains for semi-custom design For digital applications a more automated design approach is used. Library elements are placed automatically. Designers don’t know in advance where a single element is placed. No direct access. Thus, it’s difficult to manually determine reasonable operation conditions for single library elements. A single library element is used in many different sub-circuits, and within, is exposed to a lot of different applications/operation conditions. For all of these combinations a delay-calc. would be necessary, since digital design is delay driven.

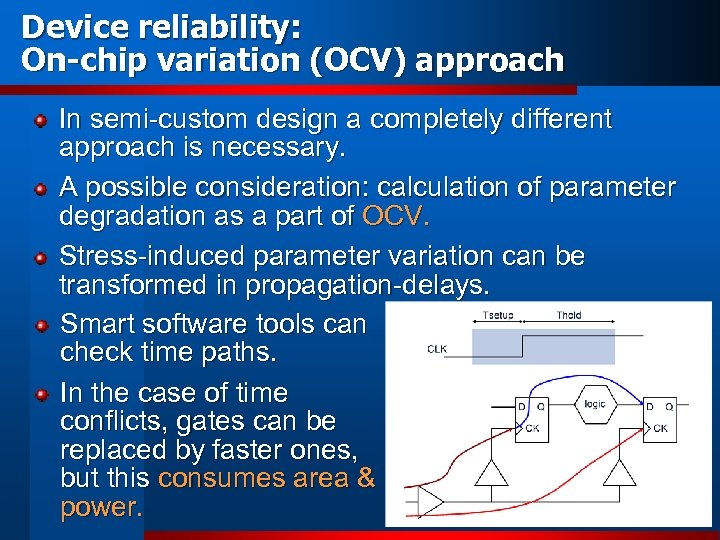

Device reliability: On-chip variation (OCV) approach In semi-custom design a completely different approach is necessary. A possible consideration: calculation of parameter degradation as a part of OCV. Stress-induced parameter variation can be transformed in propagation-delays. Smart software tools can check time paths. In the case of time conflicts, gates can be replaced by faster ones, but this consumes area & power.

Interconnect reliability: Critical layout structures Electromigration v Single vias connected to … Wide metal lines with … v Current flow in downstream direction. v Stress-induced voiding v v Single vias connected to … Wide metal plates or slitted plates. Breakdown of Inter-metal dielectric v v Metal lines with minimum pitch, operated at … Maximal potential difference of neighbored lines.

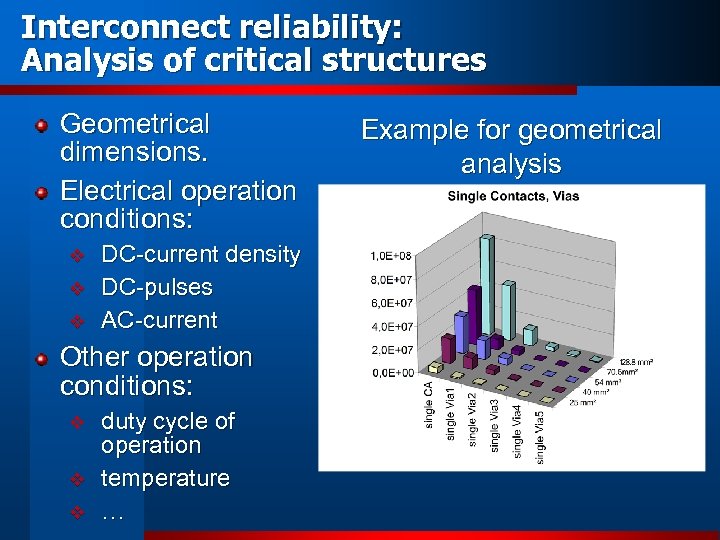

Interconnect reliability: Analysis of critical structures Geometrical dimensions. Electrical operation conditions: v v v DC-current density DC-pulses AC-current Other operation conditions: v v v duty cycle of operation temperature … Example for geometrical analysis

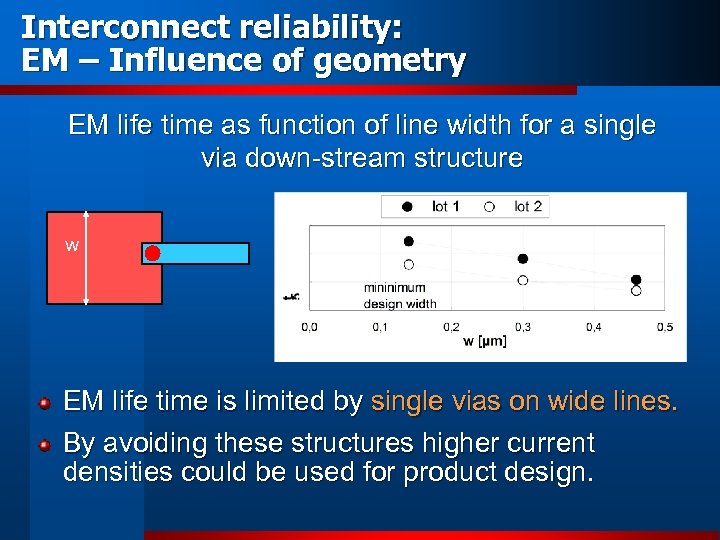

Interconnect reliability: EM – Influence of geometry EM life time as function of line width for a single via down-stream structure w EM life time is limited by single vias on wide lines. By avoiding these structures higher current densities could be used for product design.

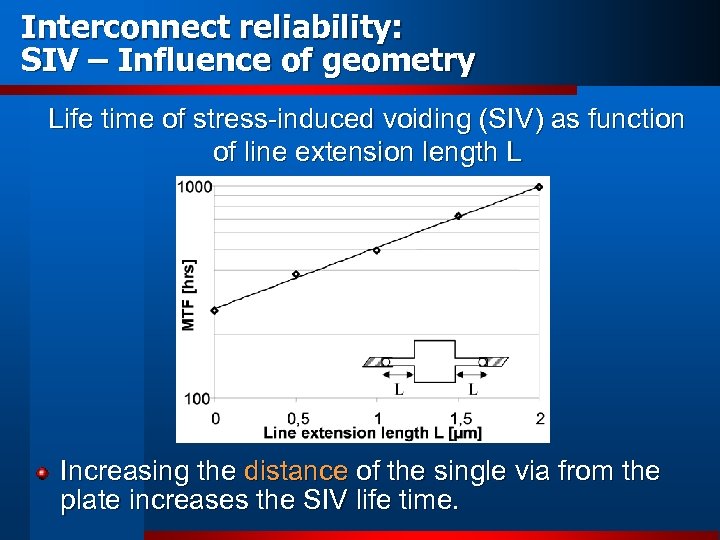

Interconnect reliability: SIV – Influence of geometry Life time of stress-induced voiding (SIV) as function of line extension length L Increasing the distance of the single via from the plate increases the SIV life time.

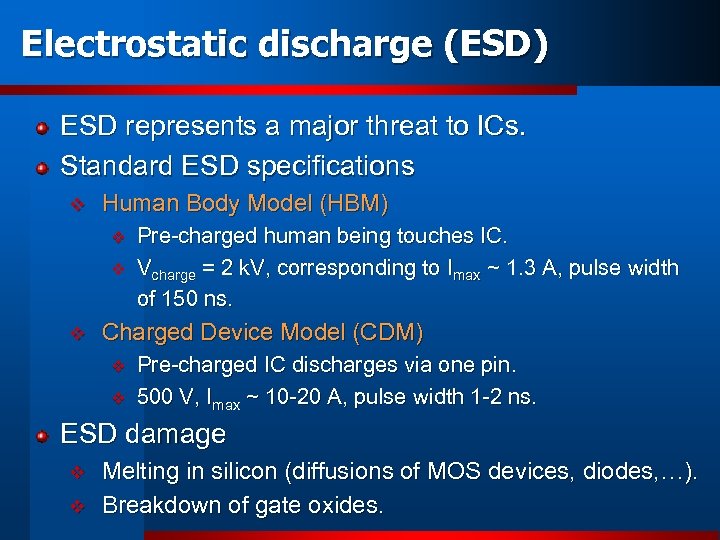

Electrostatic discharge (ESD) ESD represents a major threat to ICs. Standard ESD specifications v Human Body Model (HBM) v v v Pre-charged human being touches IC. Vcharge = 2 k. V, corresponding to Imax ~ 1. 3 A, pulse width of 150 ns. Charged Device Model (CDM) v v Pre-charged IC discharges via one pin. 500 V, Imax ~ 10 -20 A, pulse width 1 -2 ns. ESD damage v v Melting in silicon (diffusions of MOS devices, diodes, …). Breakdown of gate oxides.

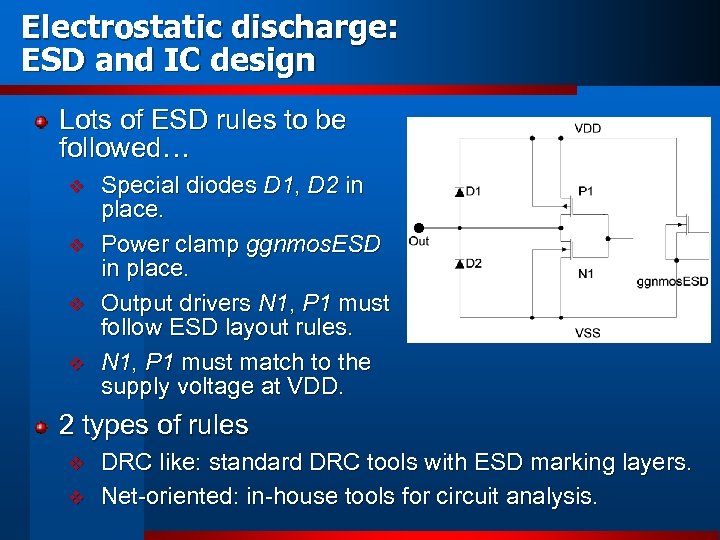

Electrostatic discharge: ESD and IC design Lots of ESD rules to be followed… v v Special diodes D 1, D 2 in place. Power clamp ggnmos. ESD in place. Output drivers N 1, P 1 must follow ESD layout rules. N 1, P 1 must match to the supply voltage at VDD. 2 types of rules v v DRC like: standard DRC tools with ESD marking layers. Net-oriented: in-house tools for circuit analysis.

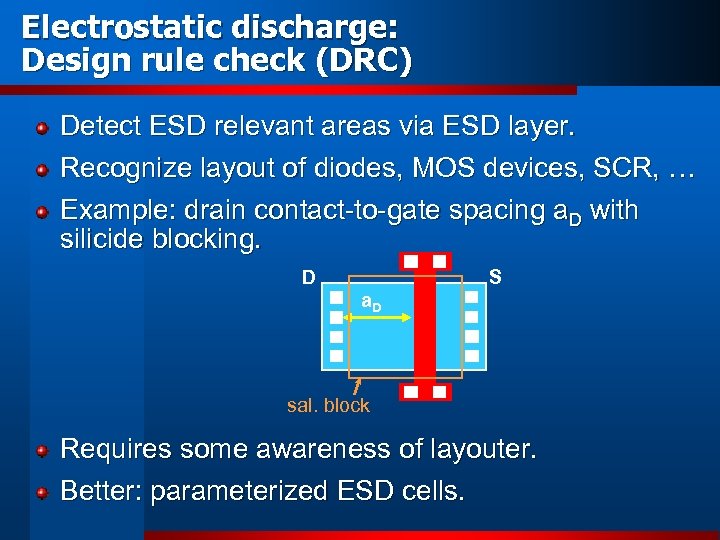

Electrostatic discharge: Design rule check (DRC) Detect ESD relevant areas via ESD layer. Recognize layout of diodes, MOS devices, SCR, … Example: drain contact-to-gate spacing a. D with silicide blocking. D S a. D sal. block Requires some awareness of layouter. Better: parameterized ESD cells.

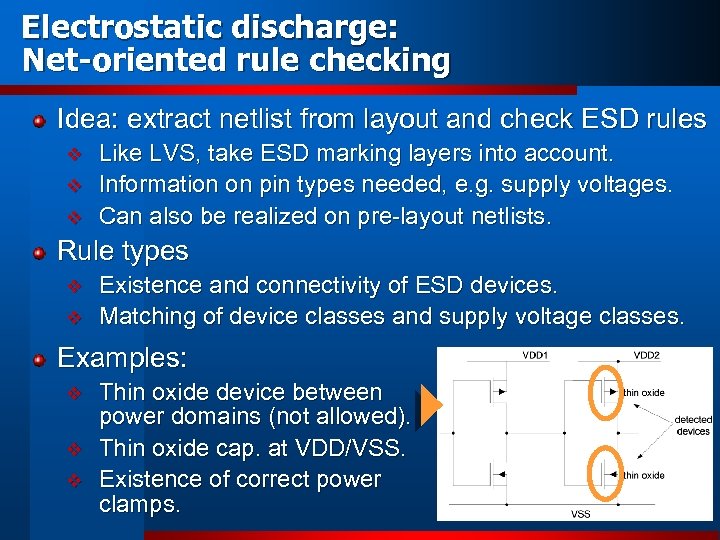

Electrostatic discharge: Net-oriented rule checking Idea: extract netlist from layout and check ESD rules v v v Like LVS, take ESD marking layers into account. Information on pin types needed, e. g. supply voltages. Can also be realized on pre-layout netlists. Rule types v v Existence and connectivity of ESD devices. Matching of device classes and supply voltage classes. Examples: v v v Thin oxide device between power domains (not allowed). Thin oxide cap. at VDD/VSS. Existence of correct power clamps.

Electrostatic discharge: ESD awareness of future EDA tools ESD DRC is OK with existing DRC tools. No commercial tools for net-oriented ESD rules available. v v Should be imbedded in design flow. Need for infrastructure: ESD pin types, power domains, ESD endangered interfaces. Also for pre-layout-synthesis checks. Should work on data of a whole IC. Tool for IR-drop analysis of ESD pulses. v Find bad metallization, ESD endangered positions on IC, … Auto-placement of ESD cells according to some formalized guidelines would be great!

Summary Gate oxide reliability v v Identify voltage overshoot events. New gate oxide failure criteria to be considered. Device reliability v v Increasing electric field; NBTI becomes design issue. Simulation using degraded devices: constraints for semi -custom design OCV approach. Interconnect reliability v v Control via placing to improve EM & SIV. Identify metal line with minimal pitch (TDDB risk). ESD v v Net-orientated ESD rules, IR-drop analysis. Automated placement of ESD and I/O cells.

f3bf75351a4c18ebd144782996cd73cf.ppt