de6904246d39b509052d1f9d38f925e9.ppt

- Количество слайдов: 19

Power 6 Presentation Power of P 6 Anita Devadason June 11 th, 2007 © 2007 IBM Corporation

Power 6 Presentation Power of P 6 Anita Devadason June 11 th, 2007 © 2007 IBM Corporation

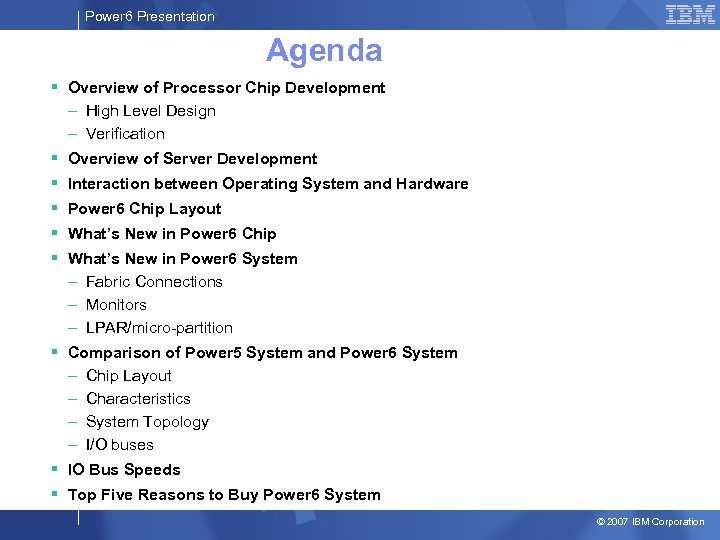

Power 6 Presentation Agenda § Overview of Processor Chip Development – High Level Design – Verification § § § Overview of Server Development Interaction between Operating System and Hardware Power 6 Chip Layout What’s New in Power 6 Chip What’s New in Power 6 System – Fabric Connections – Monitors – LPAR/micro-partition § Comparison of Power 5 System and Power 6 System – – Chip Layout Characteristics System Topology I/O buses § IO Bus Speeds § Top Five Reasons to Buy Power 6 System © 2007 IBM Corporation

Power 6 Presentation Agenda § Overview of Processor Chip Development – High Level Design – Verification § § § Overview of Server Development Interaction between Operating System and Hardware Power 6 Chip Layout What’s New in Power 6 Chip What’s New in Power 6 System – Fabric Connections – Monitors – LPAR/micro-partition § Comparison of Power 5 System and Power 6 System – – Chip Layout Characteristics System Topology I/O buses § IO Bus Speeds § Top Five Reasons to Buy Power 6 System © 2007 IBM Corporation

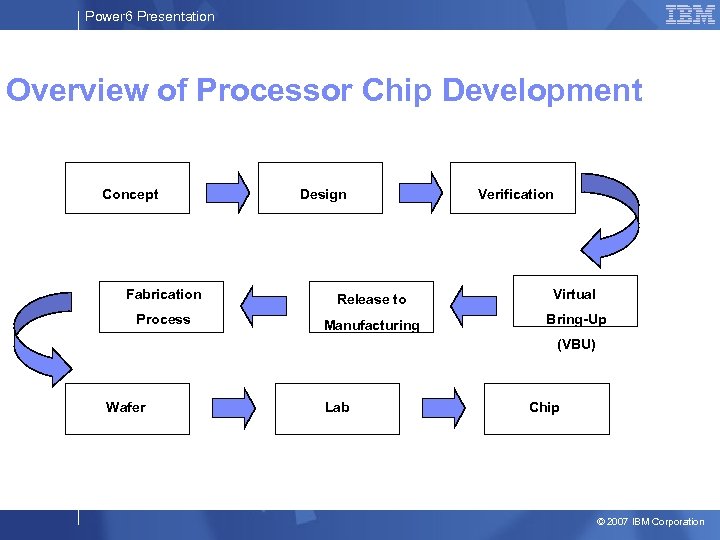

Power 6 Presentation Overview of Processor Chip Development Concept Design Verification Fabrication Release to Virtual Process Manufacturing Bring-Up (VBU) Wafer Lab Chip © 2007 IBM Corporation

Power 6 Presentation Overview of Processor Chip Development Concept Design Verification Fabrication Release to Virtual Process Manufacturing Bring-Up (VBU) Wafer Lab Chip © 2007 IBM Corporation

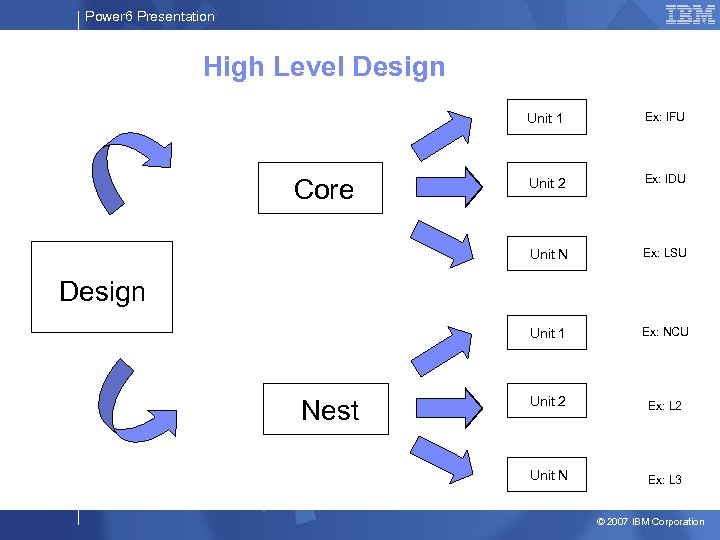

Power 6 Presentation High Level Design Unit 1 Unit 2 Ex: IDU Unit N Ex: LSU Unit 1 Core Ex: IFU Ex: NCU Unit 2 Ex: L 2 Unit N Ex: L 3 Design Nest © 2007 IBM Corporation

Power 6 Presentation High Level Design Unit 1 Unit 2 Ex: IDU Unit N Ex: LSU Unit 1 Core Ex: IFU Ex: NCU Unit 2 Ex: L 2 Unit N Ex: L 3 Design Nest © 2007 IBM Corporation

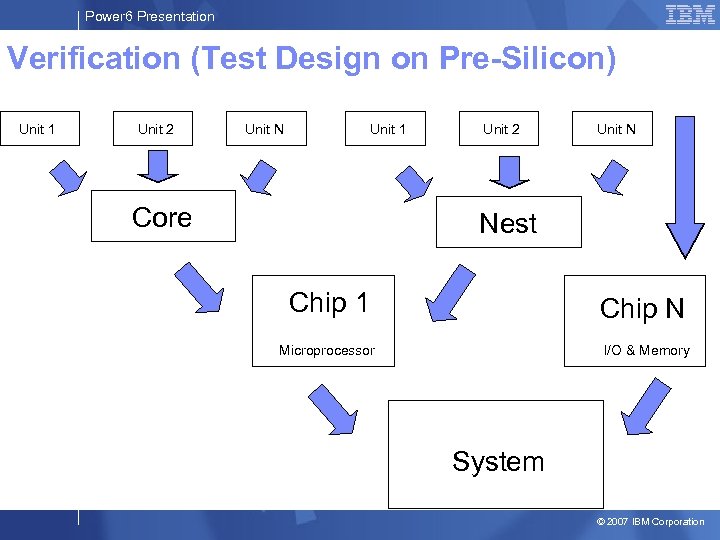

Power 6 Presentation Verification (Test Design on Pre-Silicon) Unit 1 Unit 2 Unit N Unit 1 Core Unit 2 Unit N Nest Chip 1 Chip N Microprocessor I/O & Memory System © 2007 IBM Corporation

Power 6 Presentation Verification (Test Design on Pre-Silicon) Unit 1 Unit 2 Unit N Unit 1 Core Unit 2 Unit N Nest Chip 1 Chip N Microprocessor I/O & Memory System © 2007 IBM Corporation

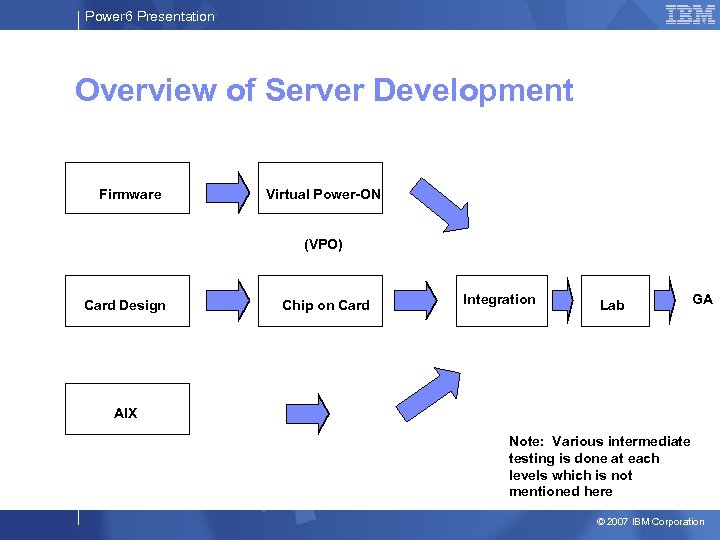

Power 6 Presentation Overview of Server Development Firmware Virtual Power-ON (VPO) Card Design Chip on Card Integration Lab GA AIX Note: Various intermediate testing is done at each levels which is not mentioned here © 2007 IBM Corporation

Power 6 Presentation Overview of Server Development Firmware Virtual Power-ON (VPO) Card Design Chip on Card Integration Lab GA AIX Note: Various intermediate testing is done at each levels which is not mentioned here © 2007 IBM Corporation

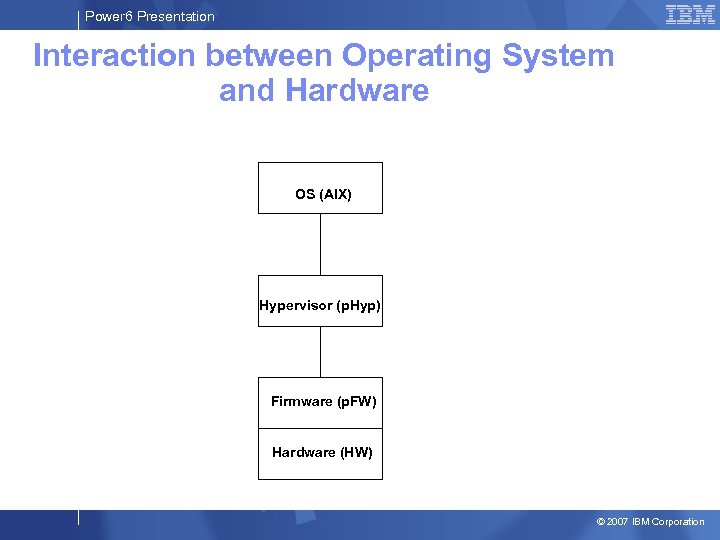

Power 6 Presentation Interaction between Operating System and Hardware OS (AIX) Hypervisor (p. Hyp) Firmware (p. FW) Hardware (HW) © 2007 IBM Corporation

Power 6 Presentation Interaction between Operating System and Hardware OS (AIX) Hypervisor (p. Hyp) Firmware (p. FW) Hardware (HW) © 2007 IBM Corporation

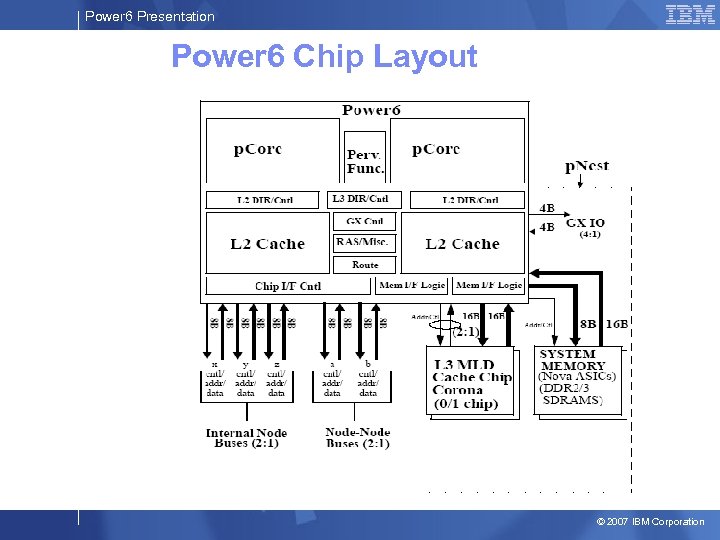

Power 6 Presentation Power 6 Chip Layout © 2007 IBM Corporation

Power 6 Presentation Power 6 Chip Layout © 2007 IBM Corporation

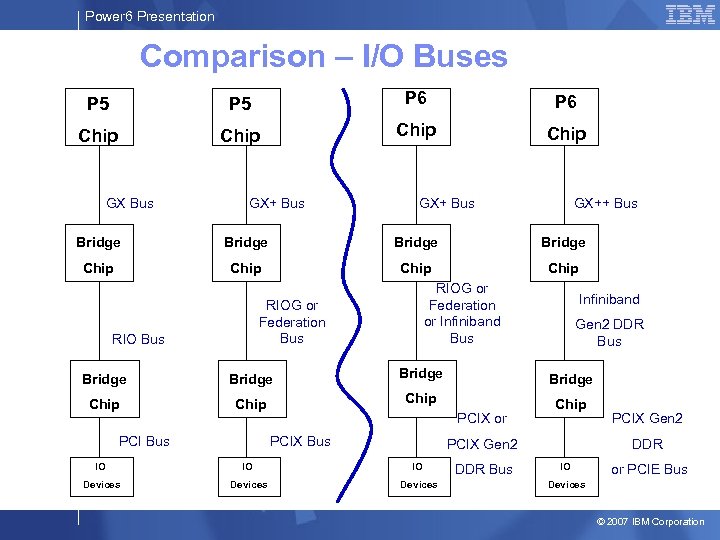

Power 6 Presentation What’s New in Power 6 Chip § § § § § New Technology (11 s) Supports both Little and Big Endian Supports page sizes of 4 K, 64 K, 16 M, and 16 G New decimal floating point operations for performance and accuracy Enhanced data pre-fetching for performance VMX (Vector Multimedia e. Xtension) for accelerated graphics Error detection and recovery mechanisms similar to system z Enhanced power and thermal control including power savings Local/Global Address Broadcast in system bus for better performance Supports both GX+ and GX++ for legacy and new I/O protocols – GX+ uses RIOG, Federation, or Infiniband (2. 5 GHz) – GX++ uses Infiniband Gen 2 DDR (5. 0 GHz) § Multiple shared processor pools (target 4 Q 07 with AIX 5. 4) so we can group multiple Oracle applications into one shared pool. At the moment, we have one shared processor pool. § Shared memory pools will be available (target 4 Q 07 with AIX 5. 4) © 2007 IBM Corporation

Power 6 Presentation What’s New in Power 6 Chip § § § § § New Technology (11 s) Supports both Little and Big Endian Supports page sizes of 4 K, 64 K, 16 M, and 16 G New decimal floating point operations for performance and accuracy Enhanced data pre-fetching for performance VMX (Vector Multimedia e. Xtension) for accelerated graphics Error detection and recovery mechanisms similar to system z Enhanced power and thermal control including power savings Local/Global Address Broadcast in system bus for better performance Supports both GX+ and GX++ for legacy and new I/O protocols – GX+ uses RIOG, Federation, or Infiniband (2. 5 GHz) – GX++ uses Infiniband Gen 2 DDR (5. 0 GHz) § Multiple shared processor pools (target 4 Q 07 with AIX 5. 4) so we can group multiple Oracle applications into one shared pool. At the moment, we have one shared processor pool. § Shared memory pools will be available (target 4 Q 07 with AIX 5. 4) © 2007 IBM Corporation

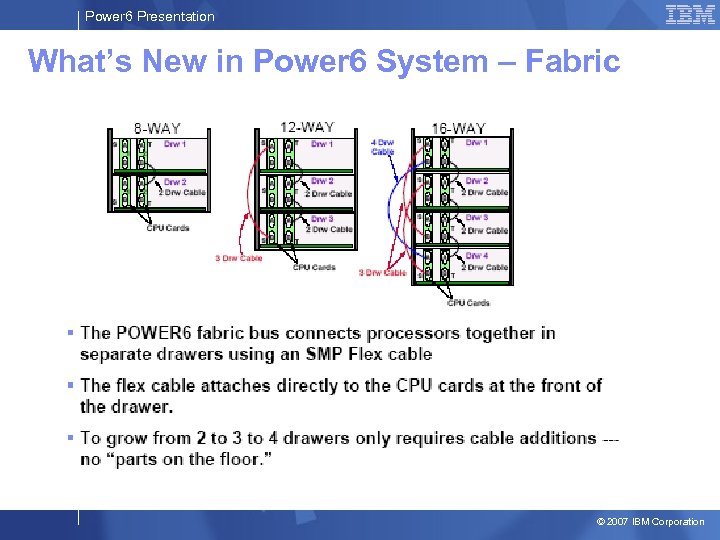

Power 6 Presentation What’s New in Power 6 System – Fabric © 2007 IBM Corporation

Power 6 Presentation What’s New in Power 6 System – Fabric © 2007 IBM Corporation

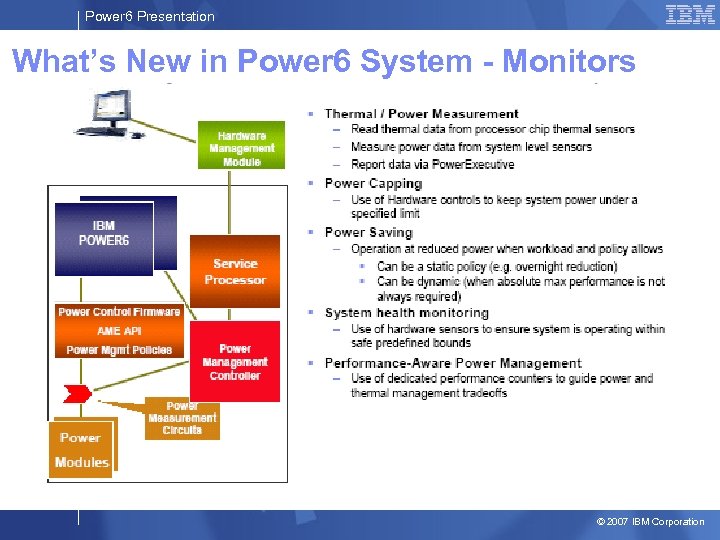

Power 6 Presentation What’s New in Power 6 System - Monitors © 2007 IBM Corporation

Power 6 Presentation What’s New in Power 6 System - Monitors © 2007 IBM Corporation

Power 6 Presentation What’s New in Power 6 System – LPAR DLPAR – Dynamic Logical Partitions which means partitions can switch on the fly (available in P 5 also) Source Partition Null Partition Target Partiton Micro-partition – minimum 1/10 th of a core Active micro-partition can move between servers with no loss of service © 2007 IBM Corporation

Power 6 Presentation What’s New in Power 6 System – LPAR DLPAR – Dynamic Logical Partitions which means partitions can switch on the fly (available in P 5 also) Source Partition Null Partition Target Partiton Micro-partition – minimum 1/10 th of a core Active micro-partition can move between servers with no loss of service © 2007 IBM Corporation

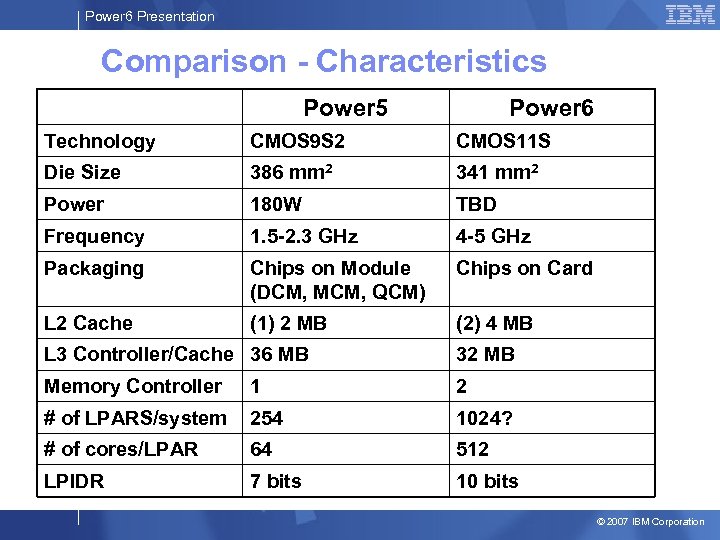

Power 6 Presentation Comparison - Characteristics Power 5 Power 6 Technology CMOS 9 S 2 CMOS 11 S Die Size 386 mm 2 341 mm 2 Power 180 W TBD Frequency 1. 5 -2. 3 GHz 4 -5 GHz Packaging Chips on Module (DCM, MCM, QCM) Chips on Card L 2 Cache (1) 2 MB (2) 4 MB L 3 Controller/Cache 36 MB 32 MB Memory Controller 1 2 # of LPARS/system 254 1024? # of cores/LPAR 64 512 LPIDR 7 bits 10 bits © 2007 IBM Corporation

Power 6 Presentation Comparison - Characteristics Power 5 Power 6 Technology CMOS 9 S 2 CMOS 11 S Die Size 386 mm 2 341 mm 2 Power 180 W TBD Frequency 1. 5 -2. 3 GHz 4 -5 GHz Packaging Chips on Module (DCM, MCM, QCM) Chips on Card L 2 Cache (1) 2 MB (2) 4 MB L 3 Controller/Cache 36 MB 32 MB Memory Controller 1 2 # of LPARS/system 254 1024? # of cores/LPAR 64 512 LPIDR 7 bits 10 bits © 2007 IBM Corporation

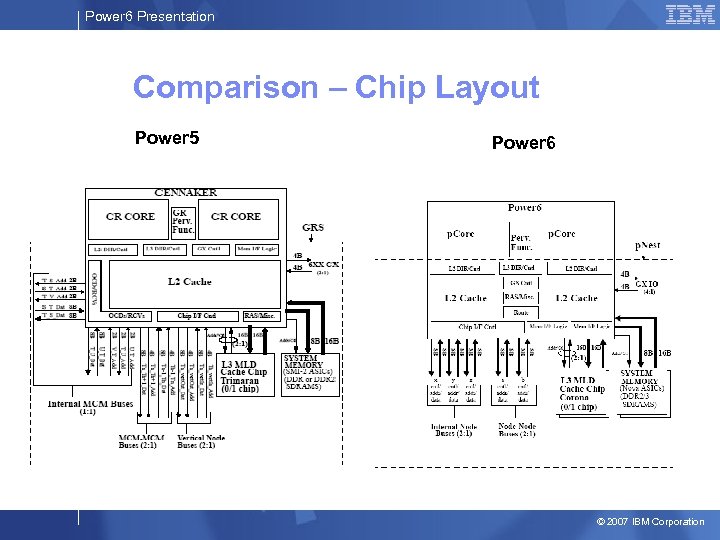

Power 6 Presentation Comparison – Chip Layout Power 5 Power 6 © 2007 IBM Corporation

Power 6 Presentation Comparison – Chip Layout Power 5 Power 6 © 2007 IBM Corporation

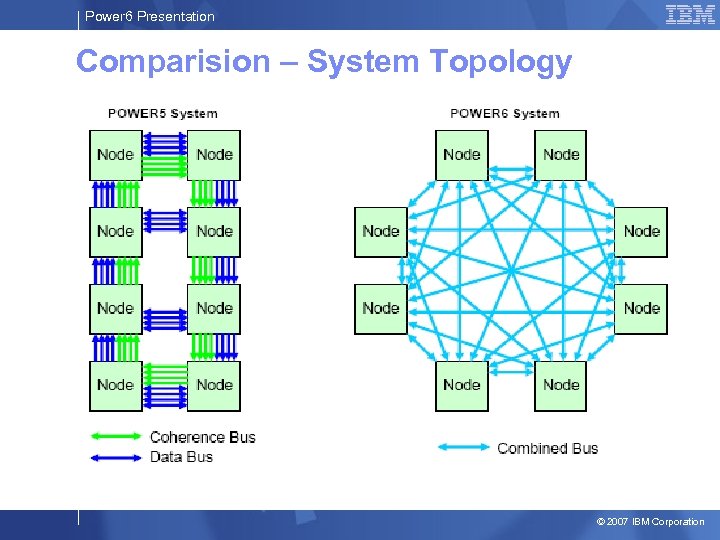

Power 6 Presentation Comparision – System Topology © 2007 IBM Corporation

Power 6 Presentation Comparision – System Topology © 2007 IBM Corporation

Power 6 Presentation Comparison – I/O Buses P 5 P 6 Chip GX Bus GX++ Bus Bridge Chip RIOG or Federation or Infiniband Bus RIOG or Federation Bus RIO Bus Bridge Chip PCI Bus Gen 2 DDR Bus Bridge PCIX or PCIX Bus Infiniband Chip PCIX Gen 2 IO IO IO Devices DDR Bus PCIX Gen 2 DDR IO or PCIE Bus Devices © 2007 IBM Corporation

Power 6 Presentation Comparison – I/O Buses P 5 P 6 Chip GX Bus GX++ Bus Bridge Chip RIOG or Federation or Infiniband Bus RIOG or Federation Bus RIO Bus Bridge Chip PCI Bus Gen 2 DDR Bus Bridge PCIX or PCIX Bus Infiniband Chip PCIX Gen 2 IO IO IO Devices DDR Bus PCIX Gen 2 DDR IO or PCIE Bus Devices © 2007 IBM Corporation

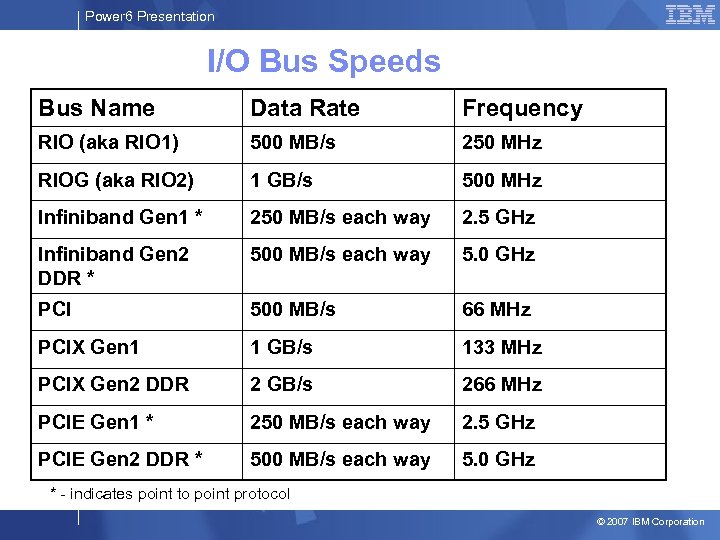

Power 6 Presentation I/O Bus Speeds Bus Name Data Rate Frequency RIO (aka RIO 1) 500 MB/s 250 MHz RIOG (aka RIO 2) 1 GB/s 500 MHz Infiniband Gen 1 * 250 MB/s each way 2. 5 GHz Infiniband Gen 2 DDR * 500 MB/s each way 5. 0 GHz PCI 500 MB/s 66 MHz PCIX Gen 1 1 GB/s 133 MHz PCIX Gen 2 DDR 2 GB/s 266 MHz PCIE Gen 1 * 250 MB/s each way 2. 5 GHz PCIE Gen 2 DDR * 500 MB/s each way 5. 0 GHz * - indicates point to point protocol © 2007 IBM Corporation

Power 6 Presentation I/O Bus Speeds Bus Name Data Rate Frequency RIO (aka RIO 1) 500 MB/s 250 MHz RIOG (aka RIO 2) 1 GB/s 500 MHz Infiniband Gen 1 * 250 MB/s each way 2. 5 GHz Infiniband Gen 2 DDR * 500 MB/s each way 5. 0 GHz PCI 500 MB/s 66 MHz PCIX Gen 1 1 GB/s 133 MHz PCIX Gen 2 DDR 2 GB/s 266 MHz PCIE Gen 1 * 250 MB/s each way 2. 5 GHz PCIE Gen 2 DDR * 500 MB/s each way 5. 0 GHz * - indicates point to point protocol © 2007 IBM Corporation

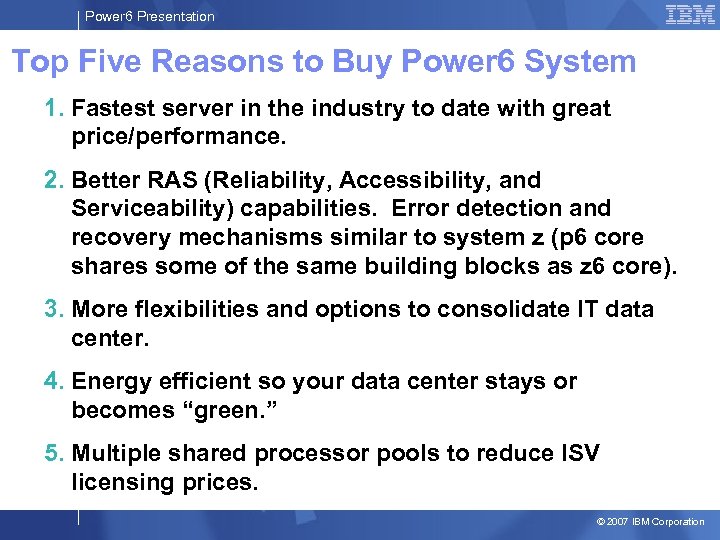

Power 6 Presentation Top Five Reasons to Buy Power 6 System 1. Fastest server in the industry to date with great price/performance. 2. Better RAS (Reliability, Accessibility, and Serviceability) capabilities. Error detection and recovery mechanisms similar to system z (p 6 core shares some of the same building blocks as z 6 core). 3. More flexibilities and options to consolidate IT data center. 4. Energy efficient so your data center stays or becomes “green. ” 5. Multiple shared processor pools to reduce ISV licensing prices. © 2007 IBM Corporation

Power 6 Presentation Top Five Reasons to Buy Power 6 System 1. Fastest server in the industry to date with great price/performance. 2. Better RAS (Reliability, Accessibility, and Serviceability) capabilities. Error detection and recovery mechanisms similar to system z (p 6 core shares some of the same building blocks as z 6 core). 3. More flexibilities and options to consolidate IT data center. 4. Energy efficient so your data center stays or becomes “green. ” 5. Multiple shared processor pools to reduce ISV licensing prices. © 2007 IBM Corporation

Power 6 Presentation Disclaimer Information in this presentation is from STG development and this does not indicate the future direction of how products would ship since products could change or be withdrawn without notice. This information was put together to educate people within IBM. © 2007 IBM Corporation

Power 6 Presentation Disclaimer Information in this presentation is from STG development and this does not indicate the future direction of how products would ship since products could change or be withdrawn without notice. This information was put together to educate people within IBM. © 2007 IBM Corporation