6e666ce3c8ed998e97aa049d5bb7c057.ppt

- Количество слайдов: 10

PIF (PId Front end chip) status D. Breton, C. Beigbeder, A. El Berni, V. Tocut, LAL/IN 2 P 3 Orsay H. Lebbolo LPNHE/IN 2 P 3 Paris V. Tocut, A. El Berni, Super. B, Frascati 12/2012

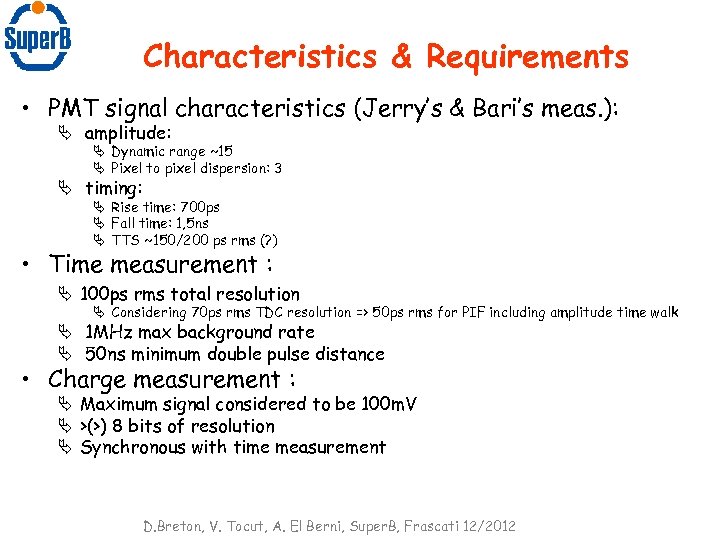

Characteristics & Requirements • PMT signal characteristics (Jerry’s & Bari’s meas. ): Ä amplitude: Ä Dynamic range ~15 Ä Pixel to pixel dispersion: 3 Ä timing: Ä Rise time: 700 ps Ä Fall time: 1, 5 ns Ä TTS ~150/200 ps rms (? ) • Time measurement : Ä 100 ps rms total resolution Ä Considering 70 ps rms TDC resolution => 50 ps rms for PIF including amplitude time walk Ä 1 MHz max background rate Ä 50 ns minimum double pulse distance • Charge measurement : Ä Maximum signal considered to be 100 m. V Ä >(>) 8 bits of resolution Ä Synchronous with time measurement D. Breton, V. Tocut, A. El Berni, Super. B, Frascati 12/2012

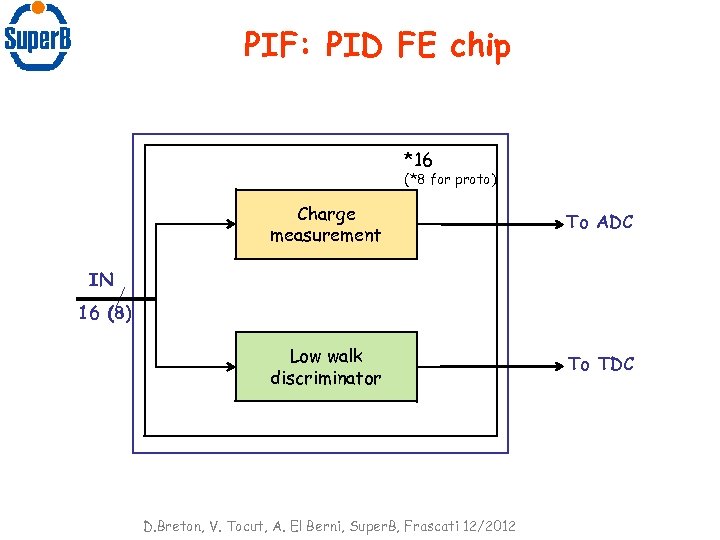

PIF: PID FE chip *16 (*8 for proto) Charge measurement To ADC Low walk discriminator To TDC IN 16 (8) D. Breton, V. Tocut, A. El Berni, Super. B, Frascati 12/2012

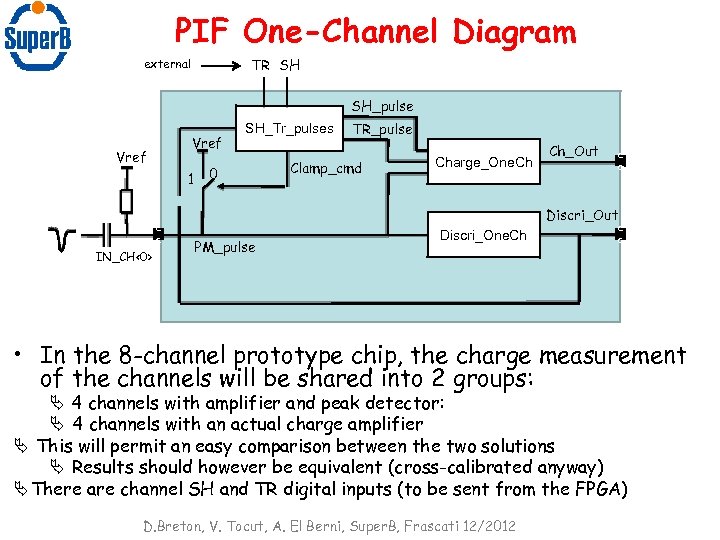

PIF One-Channel Diagram TR SH external SH_pulse Vref 1 c c IN_CH<0> SH_Tr_pulses 0 TR_pulse Clamp_cmd Charge_One. Ch Ch_Out c c Discri_Out PM_pulse Discri_One. Ch c c • In the 8 -channel prototype chip, the charge measurement of the channels will be shared into 2 groups: Ä 4 channels with amplifier and peak detector: Ä 4 channels with an actual charge amplifier Ä This will permit an easy comparison between the two solutions Ä Results should however be equivalent (cross-calibrated anyway) Ä There are channel SH and TR digital inputs (to be sent from the FPGA) D. Breton, V. Tocut, A. El Berni, Super. B, Frascati 12/2012

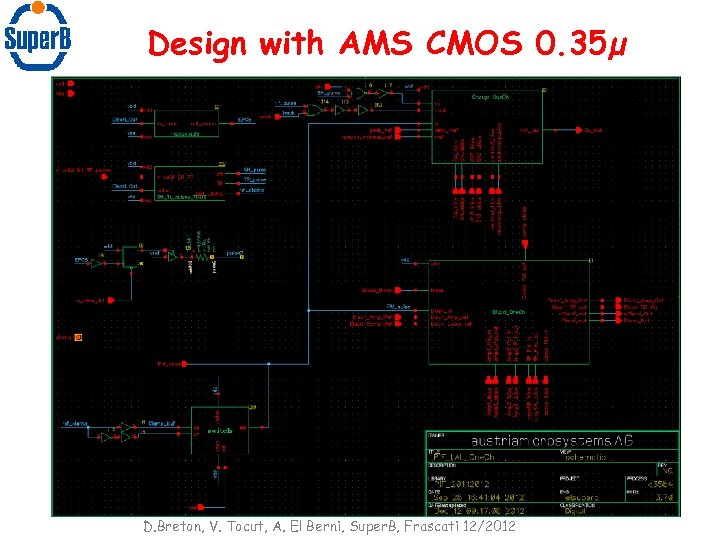

Design with AMS CMOS 0. 35µ D. Breton, V. Tocut, A. El Berni, Super. B, Frascati 12/2012

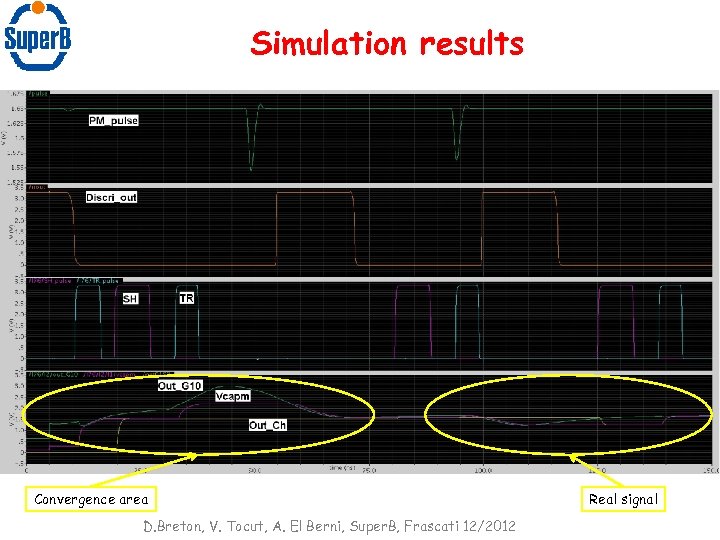

Simulation results Convergence area D. Breton, V. Tocut, A. El Berni, Super. B, Frascati 12/2012 Real signal

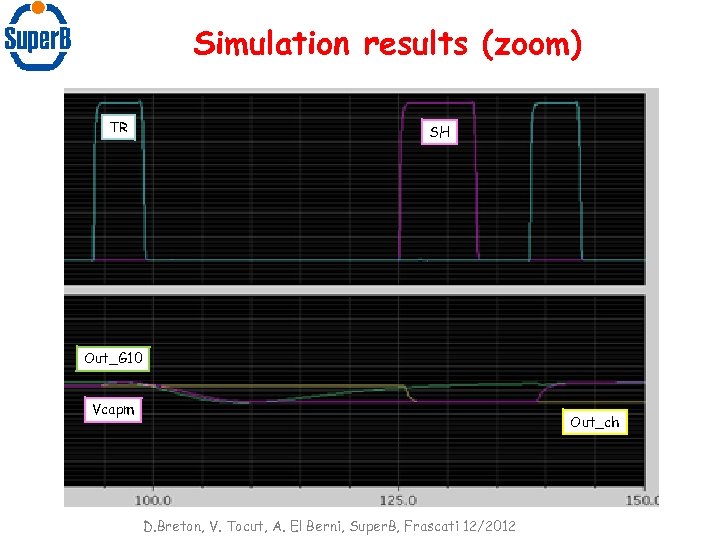

Simulation results (zoom) TR SH Out_G 10 Vcapm Out_ch D. Breton, V. Tocut, A. El Berni, Super. B, Frascati 12/2012

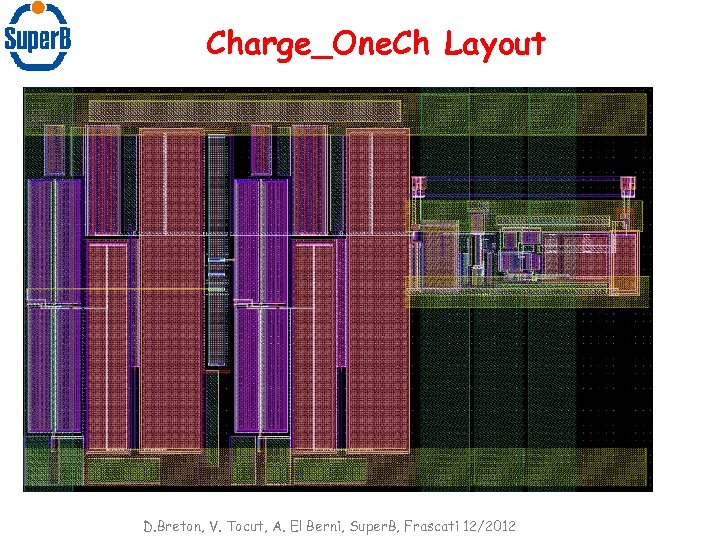

Charge_One. Ch Layout D. Breton, V. Tocut, A. El Berni, Super. B, Frascati 12/2012

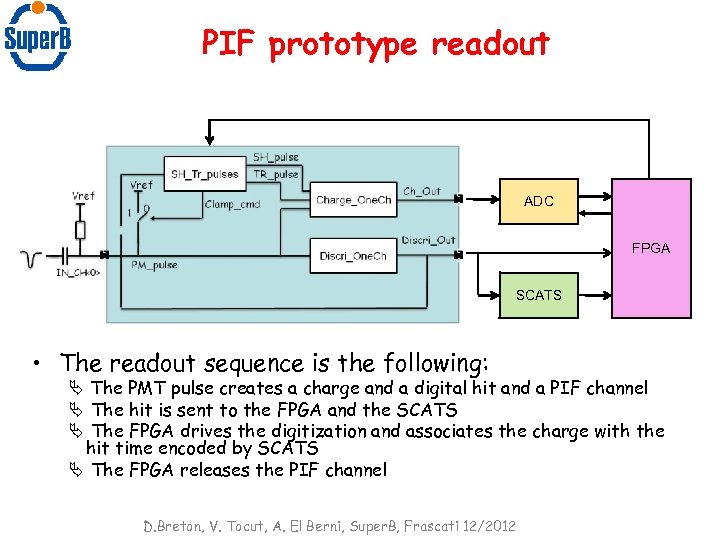

PIF prototype readout ADC FPGA SCATS • The readout sequence is the following: Ä The PMT pulse creates a charge and a digital hit and a PIF channel Ä The hit is sent to the FPGA and the SCATS Ä The FPGA drives the digitization and associates the charge with the hit time encoded by SCATS Ä The FPGA releases the PIF channel D. Breton, V. Tocut, A. El Berni, Super. B, Frascati 12/2012

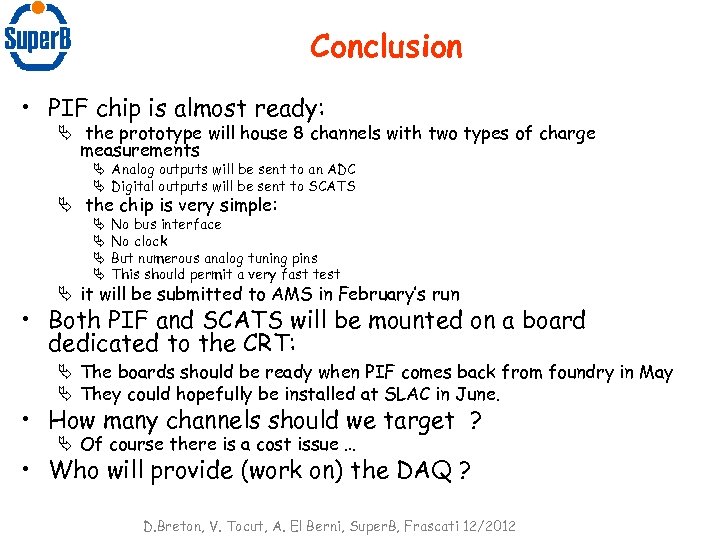

Conclusion • PIF chip is almost ready: Ä the prototype will house 8 channels with two types of charge measurements Ä Analog outputs will be sent to an ADC Ä Digital outputs will be sent to SCATS Ä the chip is very simple: Ä Ä No bus interface No clock But numerous analog tuning pins This should permit a very fast test Ä it will be submitted to AMS in February’s run • Both PIF and SCATS will be mounted on a board dedicated to the CRT: Ä The boards should be ready when PIF comes back from foundry in May Ä They could hopefully be installed at SLAC in June. • How many channels should we target ? Ä Of course there is a cost issue … • Who will provide (work on) the DAQ ? D. Breton, V. Tocut, A. El Berni, Super. B, Frascati 12/2012

6e666ce3c8ed998e97aa049d5bb7c057.ppt