f01e14f8398040afbb56f1722f6f1267.ppt

- Количество слайдов: 25

PEDS: Parallel Error Detection Scheme for TCAM Devices David Hay, Politecnico di Torino Joint work with Anat Bremler Barr (IDC, Israel), Danny Hendler (BGU, Israel) and Ron Roth (Technion, Israel) Supported by a Cisco grant 20/6/2008

PEDS: Parallel Error Detection Scheme for TCAM Devices David Hay, Politecnico di Torino Joint work with Anat Bremler Barr (IDC, Israel), Danny Hendler (BGU, Israel) and Ron Roth (Technion, Israel) Supported by a Cisco grant 20/6/2008

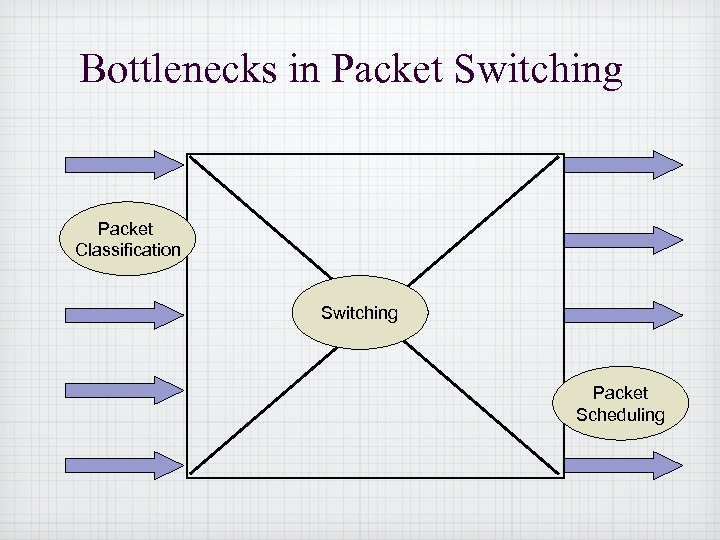

Bottlenecks in Packet Switching Packet Classification Switching Packet Scheduling

Bottlenecks in Packet Switching Packet Classification Switching Packet Scheduling

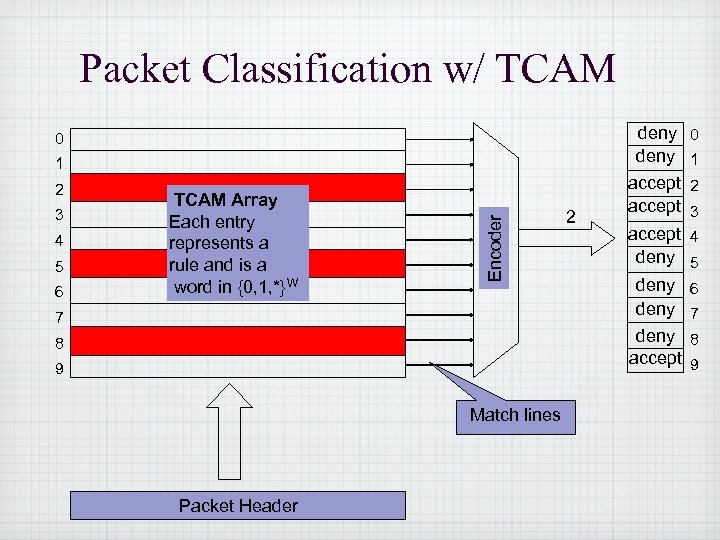

Packet Classification w/ TCAM 0 2 3 4 5 6 TCAM Array Each entry represents a rule and is a word in {0, 1, *}W Encoder 1 7 8 9 Match lines Packet Header 2 deny accept 0 1 2 3 accept 4 deny 5 deny accept 6 7 8 9

Packet Classification w/ TCAM 0 2 3 4 5 6 TCAM Array Each entry represents a rule and is a word in {0, 1, *}W Encoder 1 7 8 9 Match lines Packet Header 2 deny accept 0 1 2 3 accept 4 deny 5 deny accept 6 7 8 9

TCAM Dimensions n 100, 000 -200, 000 rules (rows) n Each entry is 100 -150 ternary symbols (column) n This leaves few dozens (~36) extra symbols in each entry, that can be used to optimize TCAM performance

TCAM Dimensions n 100, 000 -200, 000 rules (rows) n Each entry is 100 -150 ternary symbols (column) n This leaves few dozens (~36) extra symbols in each entry, that can be used to optimize TCAM performance

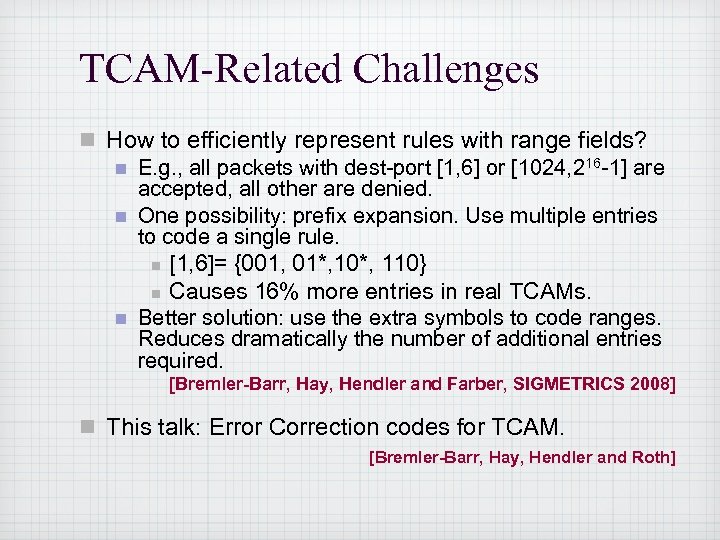

TCAM-Related Challenges n How to efficiently represent rules with range fields? n E. g. , all packets with dest-port [1, 6] or [1024, 216 -1] are accepted, all other are denied. n One possibility: prefix expansion. Use multiple entries to code a single rule. n [1, 6]= {001, 01*, 10*, 110} n Causes 16% more entries in real TCAMs. n Better solution: use the extra symbols to code ranges. Reduces dramatically the number of additional entries required. [Bremler-Barr, Hay, Hendler and Farber, SIGMETRICS 2008] n This talk: Error Correction codes for TCAM. [Bremler-Barr, Hay, Hendler and Roth]

TCAM-Related Challenges n How to efficiently represent rules with range fields? n E. g. , all packets with dest-port [1, 6] or [1024, 216 -1] are accepted, all other are denied. n One possibility: prefix expansion. Use multiple entries to code a single rule. n [1, 6]= {001, 01*, 10*, 110} n Causes 16% more entries in real TCAMs. n Better solution: use the extra symbols to code ranges. Reduces dramatically the number of additional entries required. [Bremler-Barr, Hay, Hendler and Farber, SIGMETRICS 2008] n This talk: Error Correction codes for TCAM. [Bremler-Barr, Hay, Hendler and Roth]

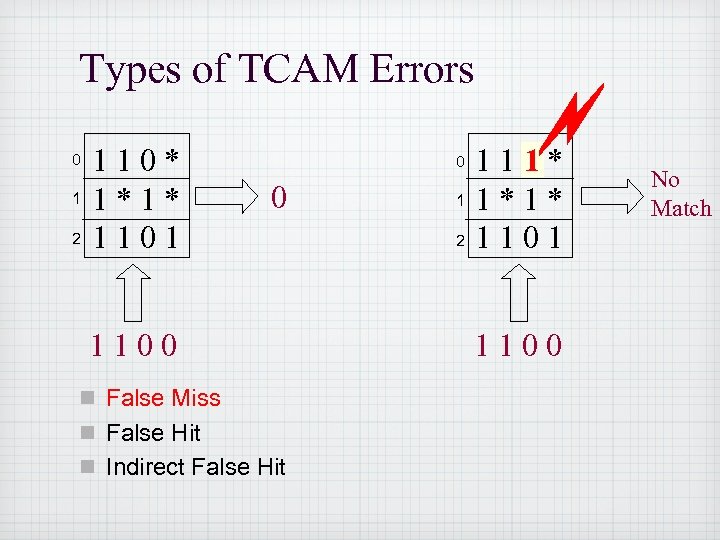

Types of TCAM Errors 0 1 2 110* 1*1* 1101 0 0 1100 n False Miss n False Hit n Indirect False Hit 1 2 1 110* 1*1* 1101 1100 No Match

Types of TCAM Errors 0 1 2 110* 1*1* 1101 0 0 1100 n False Miss n False Hit n Indirect False Hit 1 2 1 110* 1*1* 1101 1100 No Match

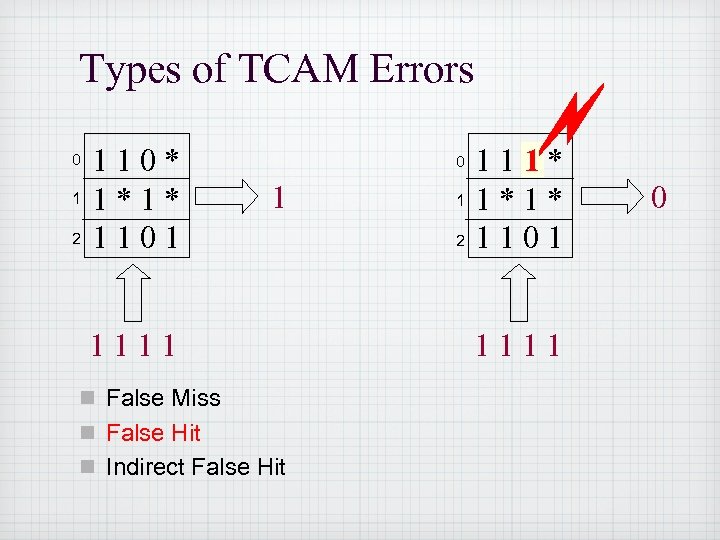

Types of TCAM Errors 0 1 2 110* 1*1* 1101 0 1 1111 n False Miss n False Hit n Indirect False Hit 1 2 1 110* 1*1* 1101 1111 0

Types of TCAM Errors 0 1 2 110* 1*1* 1101 0 1 1111 n False Miss n False Hit n Indirect False Hit 1 2 1 110* 1*1* 1101 1111 0

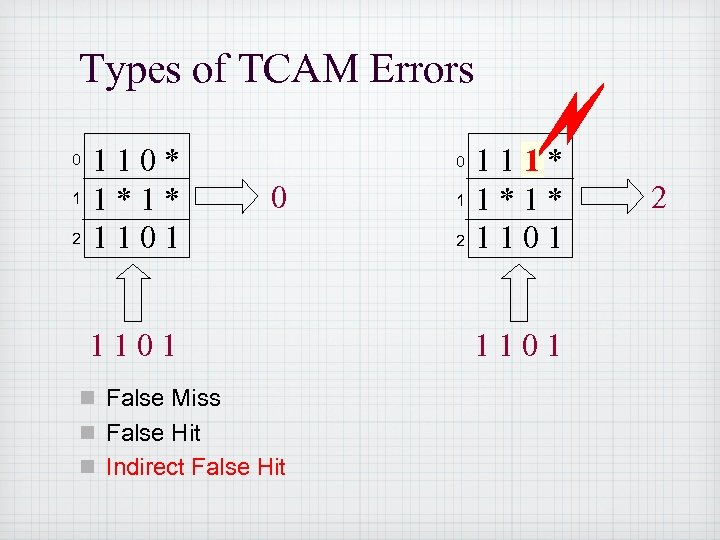

Types of TCAM Errors 0 1 2 110* 1*1* 1101 0 0 1101 n False Miss n False Hit n Indirect False Hit 1 2 1 110* 1*1* 1101 2

Types of TCAM Errors 0 1 2 110* 1*1* 1101 0 0 1101 n False Miss n False Hit n Indirect False Hit 1 2 1 110* 1*1* 1101 2

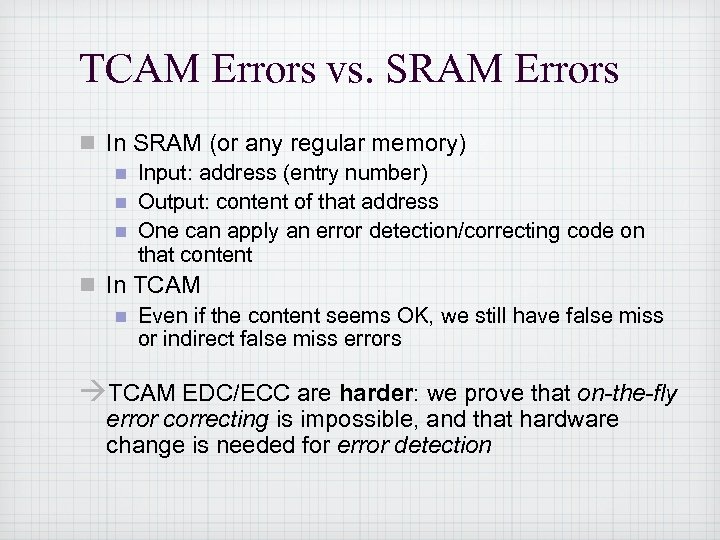

TCAM Errors vs. SRAM Errors n In SRAM (or any regular memory) n Input: address (entry number) n Output: content of that address n One can apply an error detection/correcting code on that content n In TCAM n Even if the content seems OK, we still have false miss or indirect false miss errors TCAM EDC/ECC are harder: we prove that on-the-fly error correcting is impossible, and that hardware change is needed for error detection

TCAM Errors vs. SRAM Errors n In SRAM (or any regular memory) n Input: address (entry number) n Output: content of that address n One can apply an error detection/correcting code on that content n In TCAM n Even if the content seems OK, we still have false miss or indirect false miss errors TCAM EDC/ECC are harder: we prove that on-the-fly error correcting is impossible, and that hardware change is needed for error detection

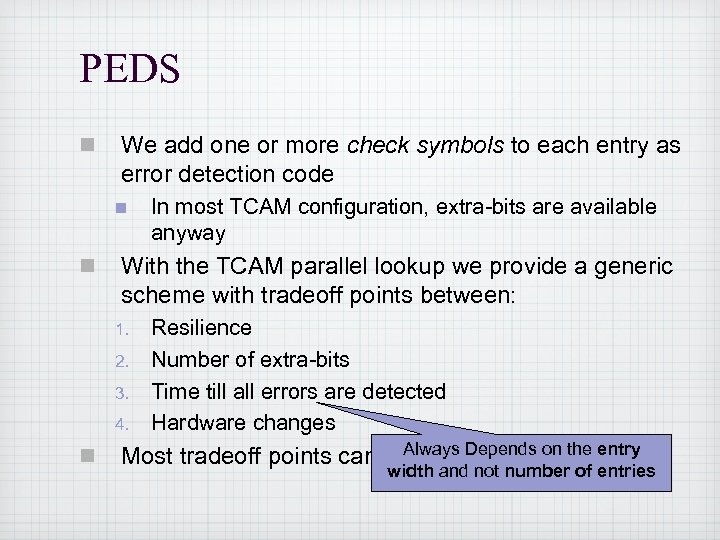

PEDS n We add one or more check symbols to each entry as error detection code n n With the TCAM parallel lookup we provide a generic scheme with tradeoff points between: 1. 2. 3. 4. n In most TCAM configuration, extra-bits are available anyway Resilience Number of extra-bits Time till all errors are detected Hardware changes Always Depends on the entry Most tradeoff points can be set after deployment width and not number of entries

PEDS n We add one or more check symbols to each entry as error detection code n n With the TCAM parallel lookup we provide a generic scheme with tradeoff points between: 1. 2. 3. 4. n In most TCAM configuration, extra-bits are available anyway Resilience Number of extra-bits Time till all errors are detected Hardware changes Always Depends on the entry Most tradeoff points can be set after deployment width and not number of entries

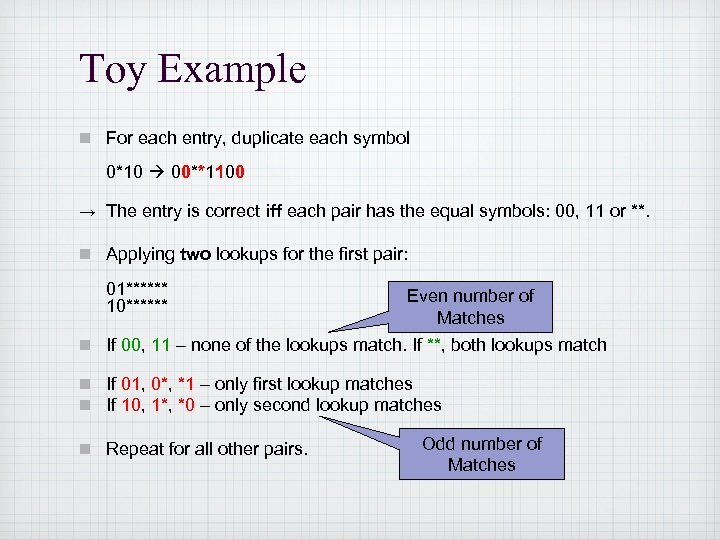

Toy Example n For each entry, duplicate each symbol 0*10 00**1100 → The entry is correct iff each pair has the equal symbols: 00, 11 or **. n Applying two lookups for the first pair: 01****** 10****** Even number of Matches n If 00, 11 – none of the lookups match. If **, both lookups match n If 01, 0*, *1 – only first lookup matches n If 10, 1*, *0 – only second lookup matches n Repeat for all other pairs. Odd number of Matches

Toy Example n For each entry, duplicate each symbol 0*10 00**1100 → The entry is correct iff each pair has the equal symbols: 00, 11 or **. n Applying two lookups for the first pair: 01****** 10****** Even number of Matches n If 00, 11 – none of the lookups match. If **, both lookups match n If 01, 0*, *1 – only first lookup matches n If 10, 1*, *0 – only second lookup matches n Repeat for all other pairs. Odd number of Matches

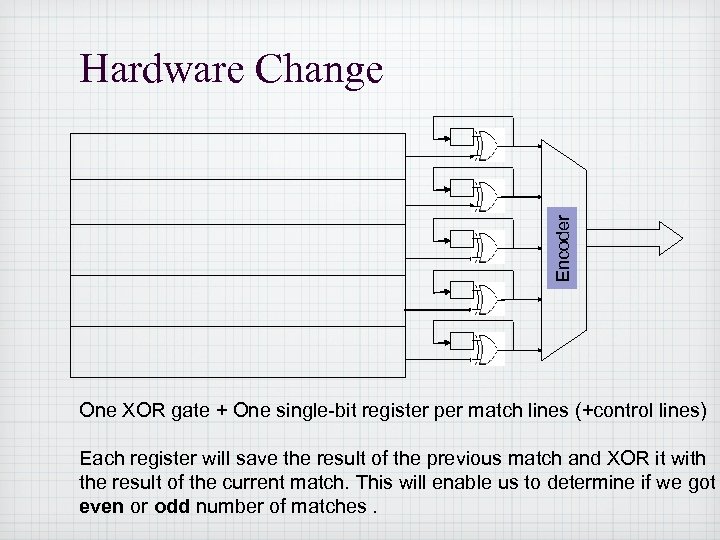

Encoder Hardware Change One XOR gate + One single-bit register per match lines (+control lines) Each register will save the result of the previous match and XOR it with the result of the current match. This will enable us to determine if we got even or odd number of matches.

Encoder Hardware Change One XOR gate + One single-bit register per match lines (+control lines) Each register will save the result of the previous match and XOR it with the result of the current match. This will enable us to determine if we got even or odd number of matches.

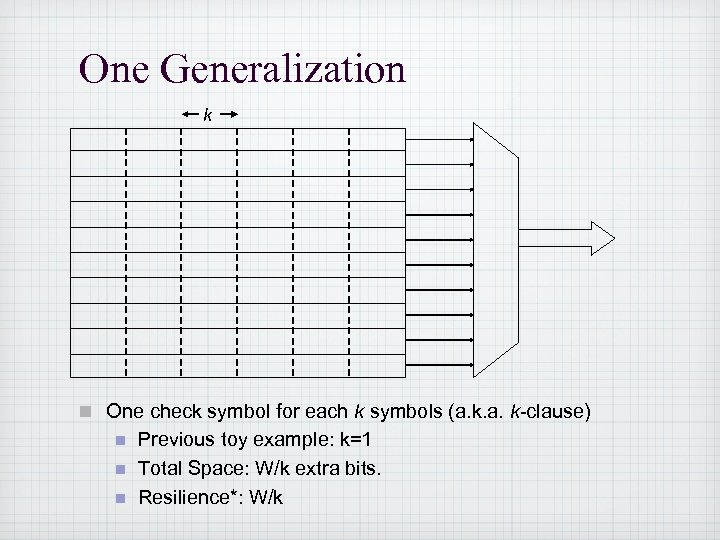

One Generalization k n One check symbol for each k symbols (a. k-clause) n n n Previous toy example: k=1 Total Space: W/k extra bits. Resilience*: W/k

One Generalization k n One check symbol for each k symbols (a. k-clause) n n n Previous toy example: k=1 Total Space: W/k extra bits. Resilience*: W/k

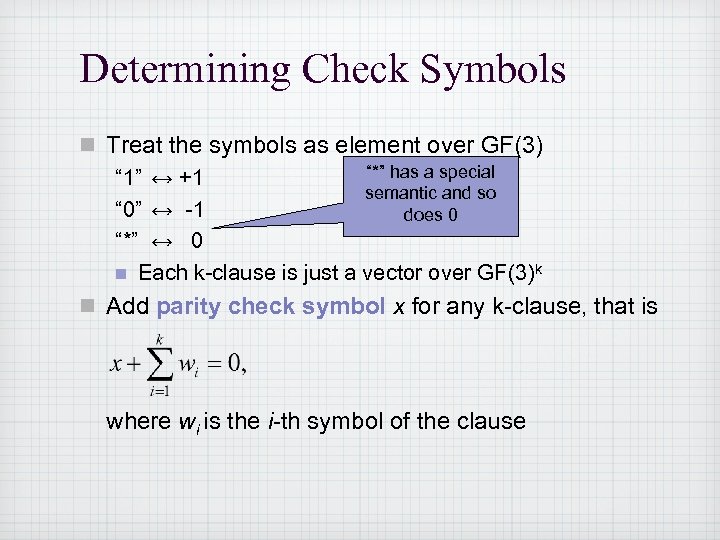

Determining Check Symbols n Treat the symbols as element over GF(3) “*” has a special “ 1” ↔ +1 semantic and so “ 0” ↔ -1 does 0 “*” ↔ 0 n Each k-clause is just a vector over GF(3)k n Add parity check symbol x for any k-clause, that is where wi is the i-th symbol of the clause

Determining Check Symbols n Treat the symbols as element over GF(3) “*” has a special “ 1” ↔ +1 semantic and so “ 0” ↔ -1 does 0 “*” ↔ 0 n Each k-clause is just a vector over GF(3)k n Add parity check symbol x for any k-clause, that is where wi is the i-th symbol of the clause

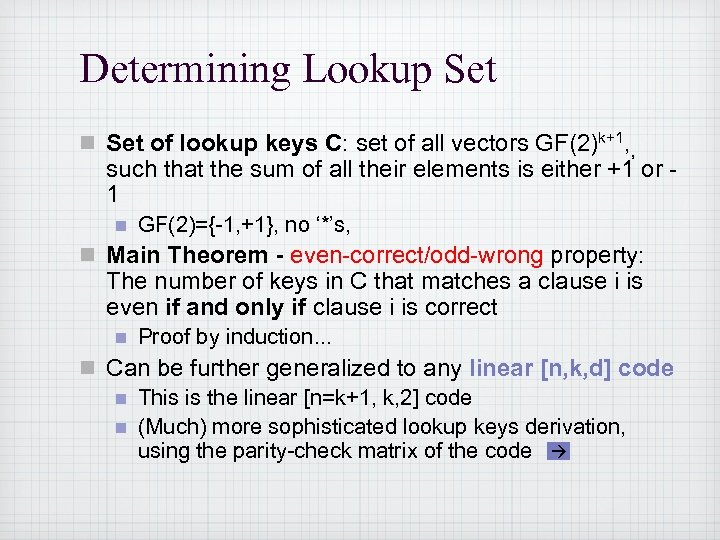

Determining Lookup Set n Set of lookup keys C: set of all vectors GF(2)k+1, , such that the sum of all their elements is either +1 or 1 n GF(2)={-1, +1}, no ‘*’s, n Main Theorem - even-correct/odd-wrong property: The number of keys in C that matches a clause i is even if and only if clause i is correct n Proof by induction. . . n Can be further generalized to any linear [n, k, d] code n This is the linear [n=k+1, k, 2] code n (Much) more sophisticated lookup keys derivation, using the parity-check matrix of the code

Determining Lookup Set n Set of lookup keys C: set of all vectors GF(2)k+1, , such that the sum of all their elements is either +1 or 1 n GF(2)={-1, +1}, no ‘*’s, n Main Theorem - even-correct/odd-wrong property: The number of keys in C that matches a clause i is even if and only if clause i is correct n Proof by induction. . . n Can be further generalized to any linear [n, k, d] code n This is the linear [n=k+1, k, 2] code n (Much) more sophisticated lookup keys derivation, using the parity-check matrix of the code

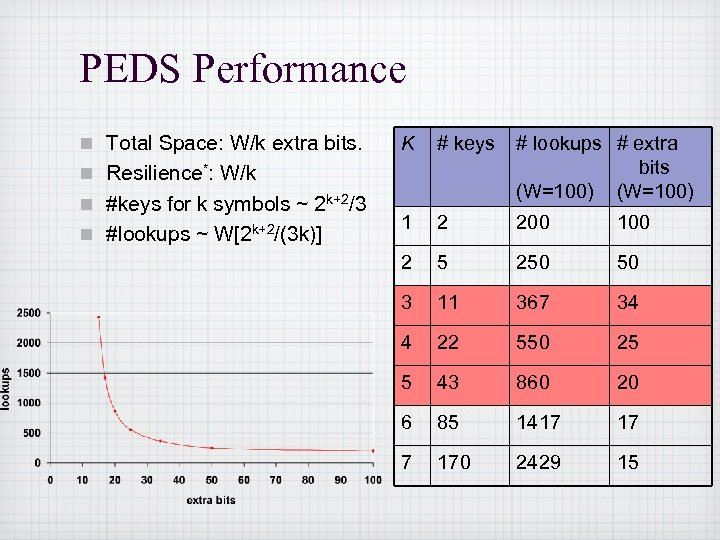

PEDS Performance n Total Space: W/k extra bits. K # keys # lookups # extra bits (W=100) 1 2 200 100 2 5 250 50 3 11 367 34 4 22 550 25 5 43 860 20 6 85 1417 170 2429 15 n Resilience*: W/k n #keys for k symbols ~ 2 k+2/3 n #lookups ~ W[2 k+2/(3 k)]

PEDS Performance n Total Space: W/k extra bits. K # keys # lookups # extra bits (W=100) 1 2 200 100 2 5 250 50 3 11 367 34 4 22 550 25 5 43 860 20 6 85 1417 170 2429 15 n Resilience*: W/k n #keys for k symbols ~ 2 k+2/3 n #lookups ~ W[2 k+2/(3 k)]

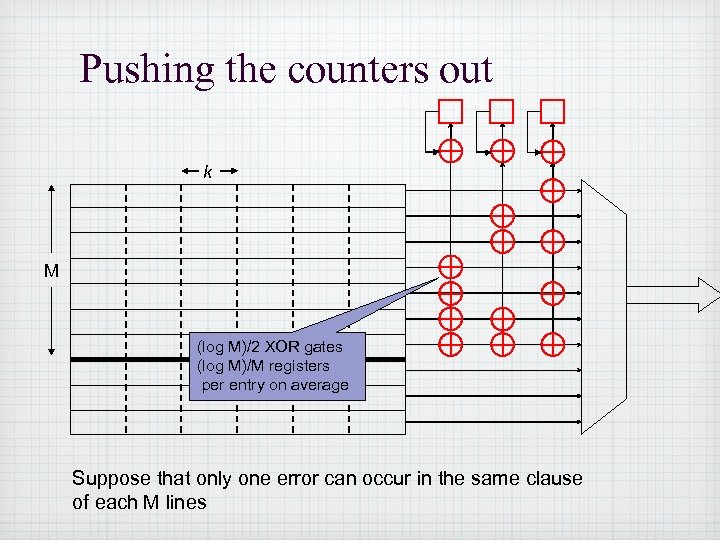

Pushing the counters out k M (log M)/2 XOR gates (log M)/M registers per entry on average Suppose that only one error can occur in the same clause of each M lines

Pushing the counters out k M (log M)/2 XOR gates (log M)/M registers per entry on average Suppose that only one error can occur in the same clause of each M lines

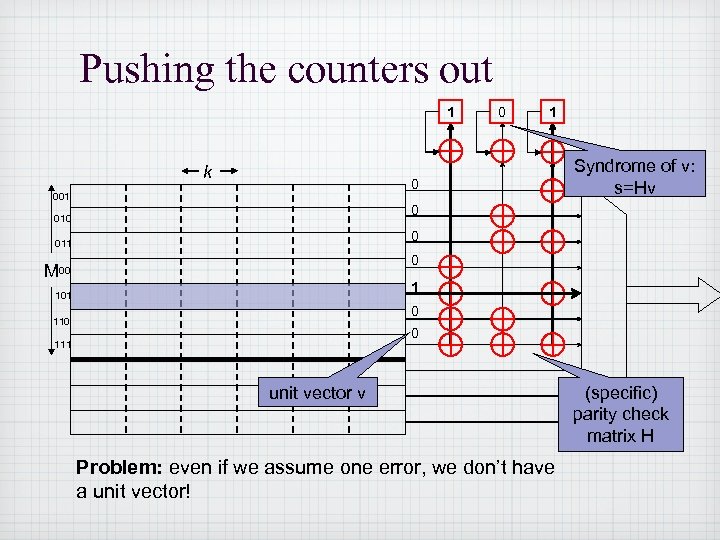

Pushing the counters out 1 k 0 1 0 001 Syndrome of v: s=Hv 0 010 0 011 0 100 M 1 101 0 110 0 111 unit vector v Problem: even if we assume one error, we don’t have a unit vector! (specific) parity check matrix H

Pushing the counters out 1 k 0 1 0 001 Syndrome of v: s=Hv 0 010 0 011 0 100 M 1 101 0 110 0 111 unit vector v Problem: even if we assume one error, we don’t have a unit vector! (specific) parity check matrix H

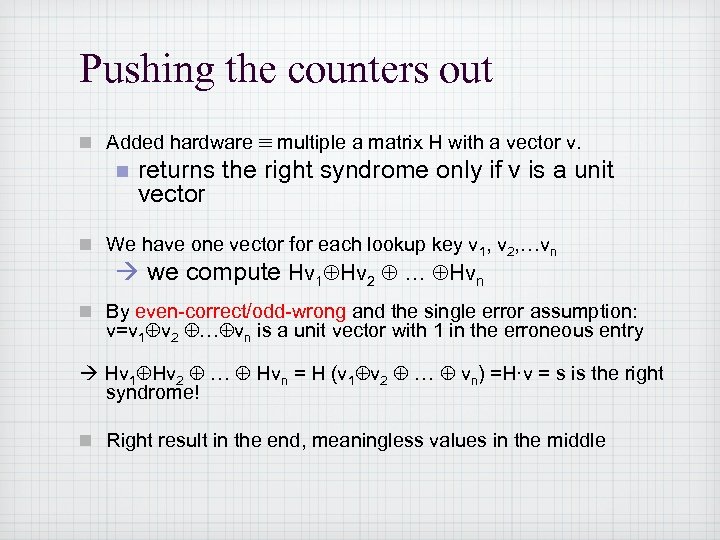

Pushing the counters out multiple a matrix H with a vector v. n returns the right syndrome only if v is a unit vector n Added hardware n We have one vector for each lookup key v 1, v 2, …vn we compute Hv 1 Hv 2 … Hvn n By even-correct/odd-wrong and the single error assumption: v=v 1 v 2 … vn is a unit vector with 1 in the erroneous entry Hv 1 Hv 2 … Hvn = H (v 1 v 2 … vn) =H·v = s is the right syndrome! n Right result in the end, meaningless values in the middle

Pushing the counters out multiple a matrix H with a vector v. n returns the right syndrome only if v is a unit vector n Added hardware n We have one vector for each lookup key v 1, v 2, …vn we compute Hv 1 Hv 2 … Hvn n By even-correct/odd-wrong and the single error assumption: v=v 1 v 2 … vn is a unit vector with 1 in the erroneous entry Hv 1 Hv 2 … Hvn = H (v 1 v 2 … vn) =H·v = s is the right syndrome! n Right result in the end, meaningless values in the middle

Wrap-up n Detecting all errors using the built-in parallel lookup of the TCAM n The number of lookups is a function of W, the width of the TCAM word, and not the number of entries in the database. n Requires a hardware change, but only in the peripheral circuitry of the TCAM chip n More generalizations and constructions in the paper… n n Using other codes Using 3 -mod counter to reduce time (=hardware-time tradeoff)

Wrap-up n Detecting all errors using the built-in parallel lookup of the TCAM n The number of lookups is a function of W, the width of the TCAM word, and not the number of entries in the database. n Requires a hardware change, but only in the peripheral circuitry of the TCAM chip n More generalizations and constructions in the paper… n n Using other codes Using 3 -mod counter to reduce time (=hardware-time tradeoff)

Thank You

Thank You

![Using other codes - Preliminaries n (Ternary) linear code [n, k, d] is a Using other codes - Preliminaries n (Ternary) linear code [n, k, d] is a](https://present5.com/presentation/f01e14f8398040afbb56f1722f6f1267/image-23.jpg) Using other codes - Preliminaries n (Ternary) linear code [n, k, d] is a set of 3 k vectors of length n over GF(3) that: n n n forms a linear space over GF(3) have minimum Hamming distance d encodes words in GF(3)k to words in GF(3)n n Each linear code has a parity check matrix H n The linear code C is H’s right kernel: C= {v GF(3)n|Hv. T=0} n If the rows of H are h 1, h 2, . . . , hr this is equivalent to: v is error free if and only if for each i, hiv. T=0

Using other codes - Preliminaries n (Ternary) linear code [n, k, d] is a set of 3 k vectors of length n over GF(3) that: n n n forms a linear space over GF(3) have minimum Hamming distance d encodes words in GF(3)k to words in GF(3)n n Each linear code has a parity check matrix H n The linear code C is H’s right kernel: C= {v GF(3)n|Hv. T=0} n If the rows of H are h 1, h 2, . . . , hr this is equivalent to: v is error free if and only if for each i, hiv. T=0

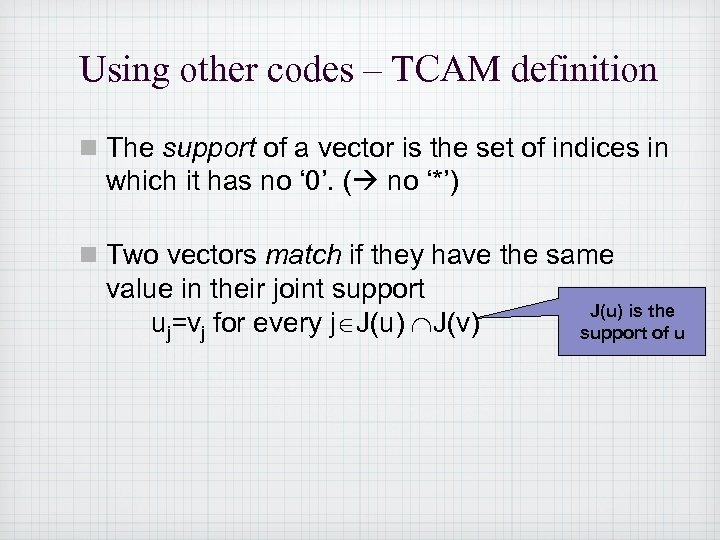

Using other codes – TCAM definition n The support of a vector is the set of indices in which it has no ‘ 0’. ( no ‘*’) n Two vectors match if they have the same value in their joint support uj=vj for every j J(u) J(v) J(u) is the support of u

Using other codes – TCAM definition n The support of a vector is the set of indices in which it has no ‘ 0’. ( no ‘*’) n Two vectors match if they have the same value in their joint support uj=vj for every j J(u) J(v) J(u) is the support of u

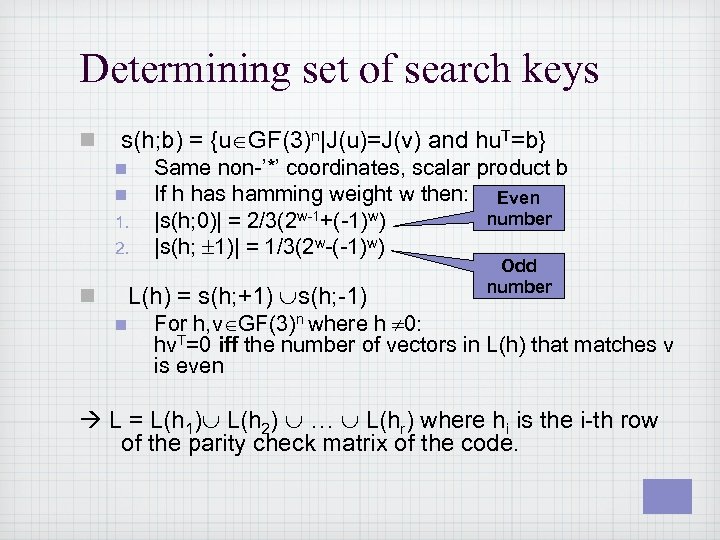

Determining set of search keys n s(h; b) = {u GF(3)n|J(u)=J(v) and hu. T=b} n n 1. 2. n Same non-’*’ coordinates, scalar product b If h has hamming weight w then: Even number |s(h; 0)| = 2/3(2 w-1+(-1)w) |s(h; 1)| = 1/3(2 w-(-1)w) L(h) = s(h; +1) s(h; -1) n Odd number For h, v GF(3)n where h 0: hv. T=0 iff the number of vectors in L(h) that matches v is even L = L(h 1) L(h 2) … L(hr) where hi is the i-th row of the parity check matrix of the code.

Determining set of search keys n s(h; b) = {u GF(3)n|J(u)=J(v) and hu. T=b} n n 1. 2. n Same non-’*’ coordinates, scalar product b If h has hamming weight w then: Even number |s(h; 0)| = 2/3(2 w-1+(-1)w) |s(h; 1)| = 1/3(2 w-(-1)w) L(h) = s(h; +1) s(h; -1) n Odd number For h, v GF(3)n where h 0: hv. T=0 iff the number of vectors in L(h) that matches v is even L = L(h 1) L(h 2) … L(hr) where hi is the i-th row of the parity check matrix of the code.