83d09ab14355d7b2d7cd7aaabbae3302.ppt

- Количество слайдов: 48

Paul Scherrer Institute, Switzerland Stefan Ritt Waveform Digitizing in the Giga-sample Range with Switched Capacitor Arrays

Paul Scherrer Institute, Switzerland Stefan Ritt Waveform Digitizing in the Giga-sample Range with Switched Capacitor Arrays

Stefan Ritt

Stefan Ritt

Stefan Ritt

Stefan Ritt

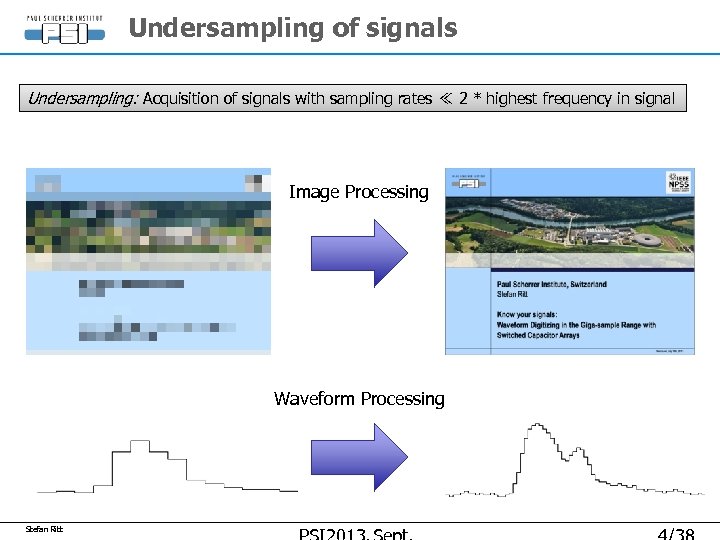

Undersampling of signals Undersampling: Acquisition of signals with sampling rates ≪ 2 * highest frequency in signal Image Processing Waveform Processing Stefan Ritt

Undersampling of signals Undersampling: Acquisition of signals with sampling rates ≪ 2 * highest frequency in signal Image Processing Waveform Processing Stefan Ritt

What is the problem? Stefan Ritt

What is the problem? Stefan Ritt

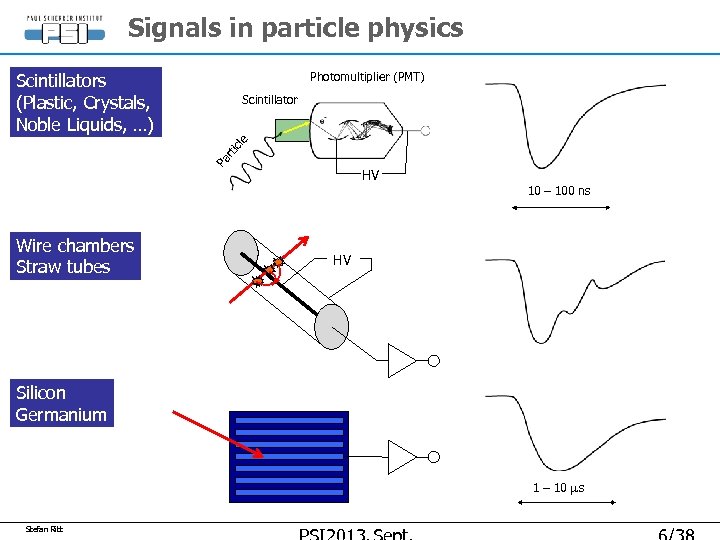

Signals in particle physics Scintillators (Plastic, Crystals, Noble Liquids, …) Photomultiplier (PMT) Pa r tic le Scintillator HV 10 – 100 ns Wire chambers Straw tubes HV Silicon Germanium 1 – 10 ms Stefan Ritt

Signals in particle physics Scintillators (Plastic, Crystals, Noble Liquids, …) Photomultiplier (PMT) Pa r tic le Scintillator HV 10 – 100 ns Wire chambers Straw tubes HV Silicon Germanium 1 – 10 ms Stefan Ritt

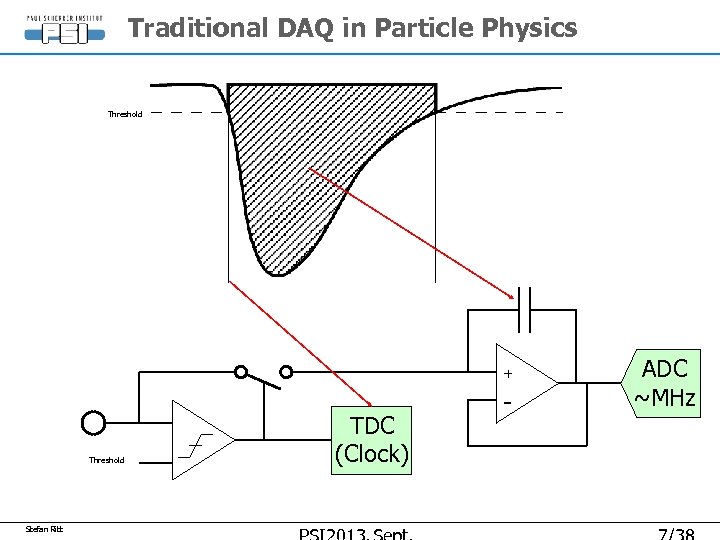

Traditional DAQ in Particle Physics Threshold + Threshold Stefan Ritt TDC (Clock) - ADC ~MHz

Traditional DAQ in Particle Physics Threshold + Threshold Stefan Ritt TDC (Clock) - ADC ~MHz

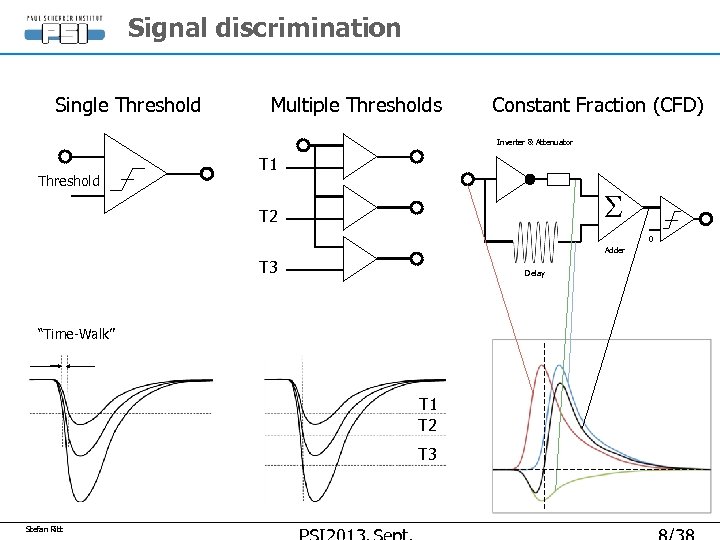

Signal discrimination Single Threshold Multiple Thresholds Constant Fraction (CFD) Inverter & Attenuator Threshold T 1 S T 2 0 Adder T 3 Delay “Time-Walk” T 1 T 2 T 3 Stefan Ritt

Signal discrimination Single Threshold Multiple Thresholds Constant Fraction (CFD) Inverter & Attenuator Threshold T 1 S T 2 0 Adder T 3 Delay “Time-Walk” T 1 T 2 T 3 Stefan Ritt

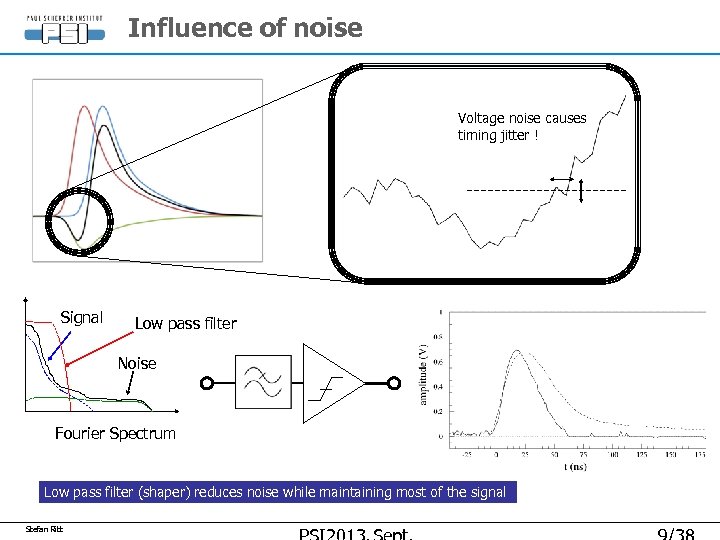

Influence of noise Voltage noise causes timing jitter ! Signal Low pass filter Noise Fourier Spectrum Low pass filter (shaper) reduces noise while maintaining most of the signal Stefan Ritt

Influence of noise Voltage noise causes timing jitter ! Signal Low pass filter Noise Fourier Spectrum Low pass filter (shaper) reduces noise while maintaining most of the signal Stefan Ritt

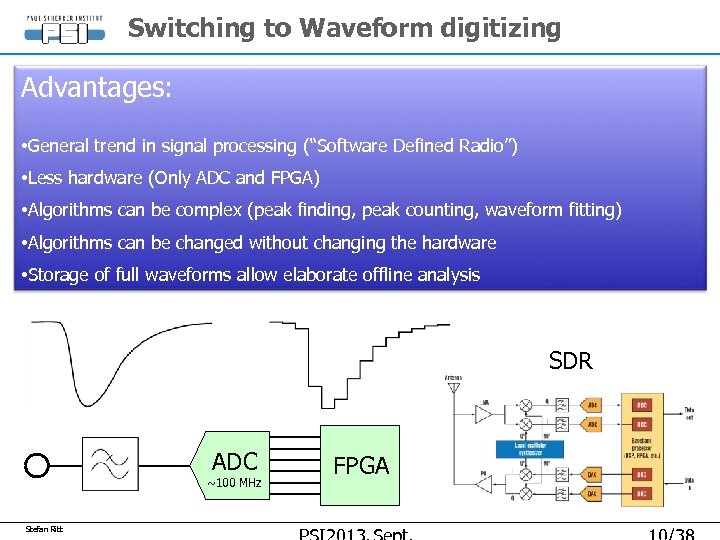

Switching to Waveform digitizing Advantages: • General trend in signal processing (“Software Defined Radio”) • Less hardware (Only ADC and FPGA) • Algorithms can be complex (peak finding, peak counting, waveform fitting) • Algorithms can be changed without changing the hardware • Storage of full waveforms allow elaborate offline analysis SDR ADC ~100 MHz Stefan Ritt FPGA

Switching to Waveform digitizing Advantages: • General trend in signal processing (“Software Defined Radio”) • Less hardware (Only ADC and FPGA) • Algorithms can be complex (peak finding, peak counting, waveform fitting) • Algorithms can be changed without changing the hardware • Storage of full waveforms allow elaborate offline analysis SDR ADC ~100 MHz Stefan Ritt FPGA

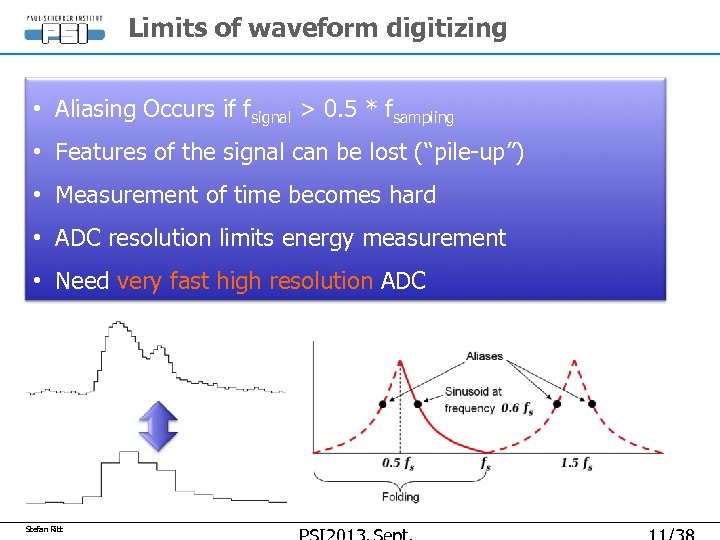

Limits of waveform digitizing • Aliasing Occurs if fsignal > 0. 5 * fsampling • Features of the signal can be lost (“pile-up”) • Measurement of time becomes hard • ADC resolution limits energy measurement • Need very fast high resolution ADC Stefan Ritt

Limits of waveform digitizing • Aliasing Occurs if fsignal > 0. 5 * fsampling • Features of the signal can be lost (“pile-up”) • Measurement of time becomes hard • ADC resolution limits energy measurement • Need very fast high resolution ADC Stefan Ritt

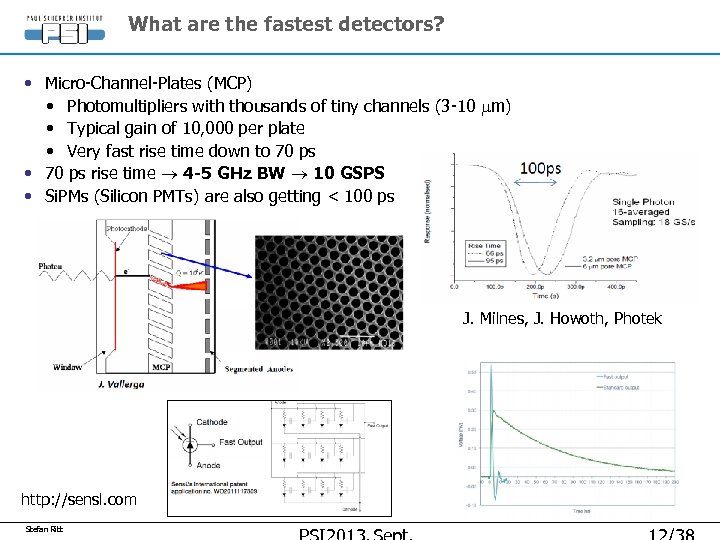

What are the fastest detectors? • Micro-Channel-Plates (MCP) • Photomultipliers with thousands of tiny channels (3 -10 mm) • Typical gain of 10, 000 per plate • Very fast rise time down to 70 ps • 70 ps rise time 4 -5 GHz BW 10 GSPS • Si. PMs (Silicon PMTs) are also getting < 100 ps J. Milnes, J. Howoth, Photek http: //sensl. com Stefan Ritt

What are the fastest detectors? • Micro-Channel-Plates (MCP) • Photomultipliers with thousands of tiny channels (3 -10 mm) • Typical gain of 10, 000 per plate • Very fast rise time down to 70 ps • 70 ps rise time 4 -5 GHz BW 10 GSPS • Si. PMs (Silicon PMTs) are also getting < 100 ps J. Milnes, J. Howoth, Photek http: //sensl. com Stefan Ritt

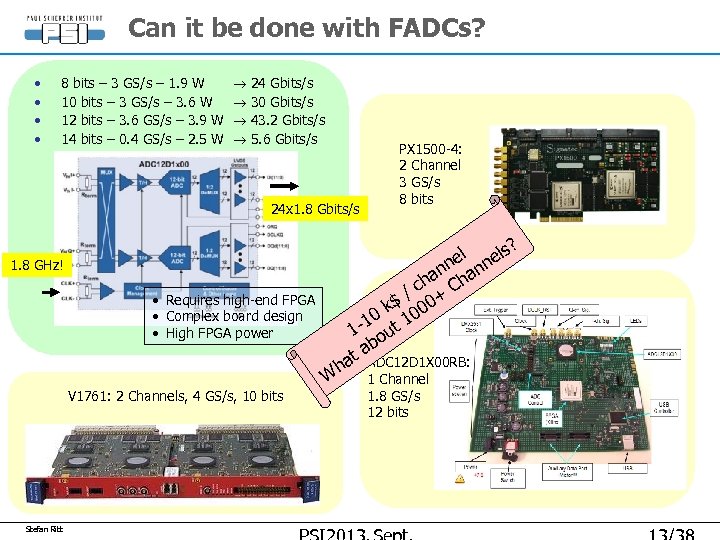

Can it be done with FADCs? • • 8 bits – 3 GS/s – 1. 9 W 10 bits – 3 GS/s – 3. 6 W 12 bits – 3. 6 GS/s – 3. 9 W 14 bits – 0. 4 GS/s – 2. 5 W 24 Gbits/s 30 Gbits/s 43. 2 Gbits/s 5. 6 Gbits/s 24 x 1. 8 Gbits/s ls? l e e nn a ch Ch $ / 00+ k 10 t 10 1 - ou b ta ha ADC 12 D 1 X 00 RB: 1. 8 GHz! • Requires high-end FPGA • Complex board design • High FPGA power W V 1761: 2 Channels, 4 GS/s, 10 bits Stefan Ritt PX 1500 -4: 2 Channel 3 GS/s 8 bits 1 Channel 1. 8 GS/s 12 bits

Can it be done with FADCs? • • 8 bits – 3 GS/s – 1. 9 W 10 bits – 3 GS/s – 3. 6 W 12 bits – 3. 6 GS/s – 3. 9 W 14 bits – 0. 4 GS/s – 2. 5 W 24 Gbits/s 30 Gbits/s 43. 2 Gbits/s 5. 6 Gbits/s 24 x 1. 8 Gbits/s ls? l e e nn a ch Ch $ / 00+ k 10 t 10 1 - ou b ta ha ADC 12 D 1 X 00 RB: 1. 8 GHz! • Requires high-end FPGA • Complex board design • High FPGA power W V 1761: 2 Channels, 4 GS/s, 10 bits Stefan Ritt PX 1500 -4: 2 Channel 3 GS/s 8 bits 1 Channel 1. 8 GS/s 12 bits

Tool to solve it Stefan Ritt

Tool to solve it Stefan Ritt

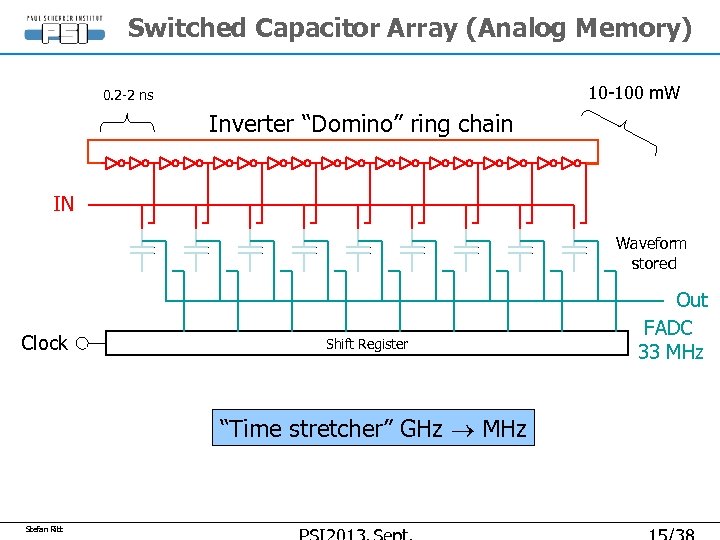

Switched Capacitor Array (Analog Memory) 10 -100 m. W 0. 2 -2 ns Inverter “Domino” ring chain IN Waveform stored Clock Shift Register “Time stretcher” GHz MHz Stefan Ritt Out FADC 33 MHz

Switched Capacitor Array (Analog Memory) 10 -100 m. W 0. 2 -2 ns Inverter “Domino” ring chain IN Waveform stored Clock Shift Register “Time stretcher” GHz MHz Stefan Ritt Out FADC 33 MHz

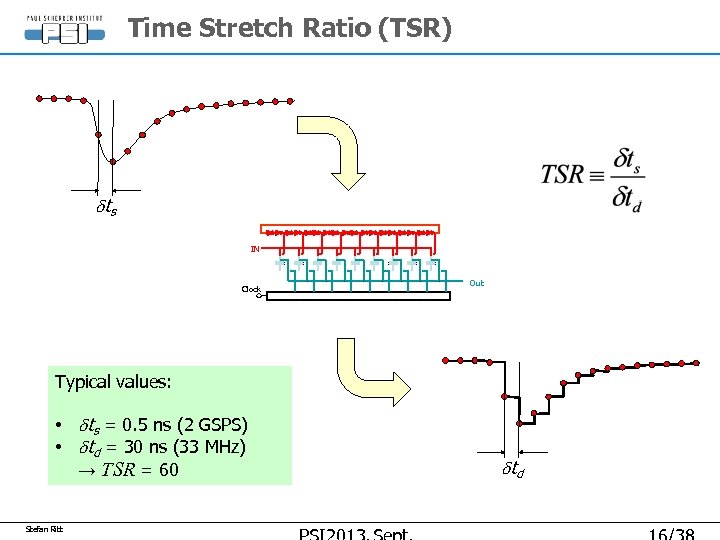

Time Stretch Ratio (TSR) dts IN Clock Out Typical values: • dts = 0. 5 ns (2 GSPS) • dtd = 30 ns (33 MHz) → TSR = 60 Stefan Ritt dtd

Time Stretch Ratio (TSR) dts IN Clock Out Typical values: • dts = 0. 5 ns (2 GSPS) • dtd = 30 ns (33 MHz) → TSR = 60 Stefan Ritt dtd

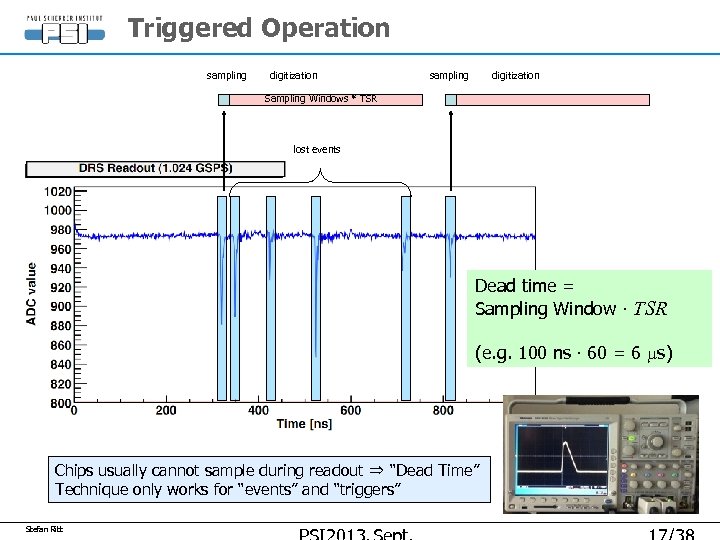

Triggered Operation sampling digitization Sampling Windows * TSR lost events Dead time = Sampling Window ∙ TSR (e. g. 100 ns ∙ 60 = 6 ms) Chips usually cannot sample during readout ⇒ “Dead Time” Technique only works for “events” and “triggers” Stefan Ritt

Triggered Operation sampling digitization Sampling Windows * TSR lost events Dead time = Sampling Window ∙ TSR (e. g. 100 ns ∙ 60 = 6 ms) Chips usually cannot sample during readout ⇒ “Dead Time” Technique only works for “events” and “triggers” Stefan Ritt

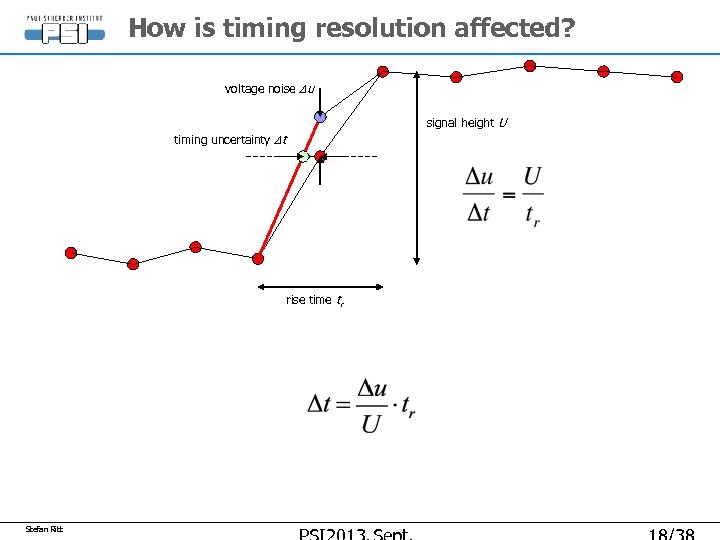

How is timing resolution affected? voltage noise Du signal height U timing uncertainty Dt rise time tr Stefan Ritt

How is timing resolution affected? voltage noise Du signal height U timing uncertainty Dt rise time tr Stefan Ritt

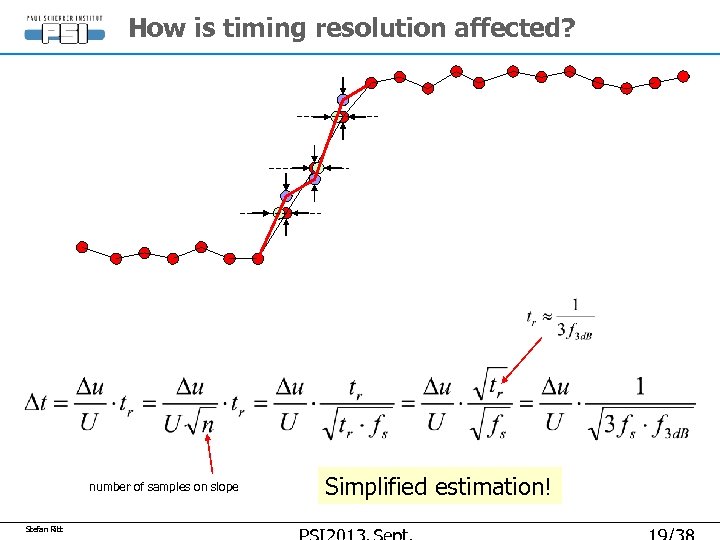

How is timing resolution affected? number of samples on slope Stefan Ritt Simplified estimation!

How is timing resolution affected? number of samples on slope Stefan Ritt Simplified estimation!

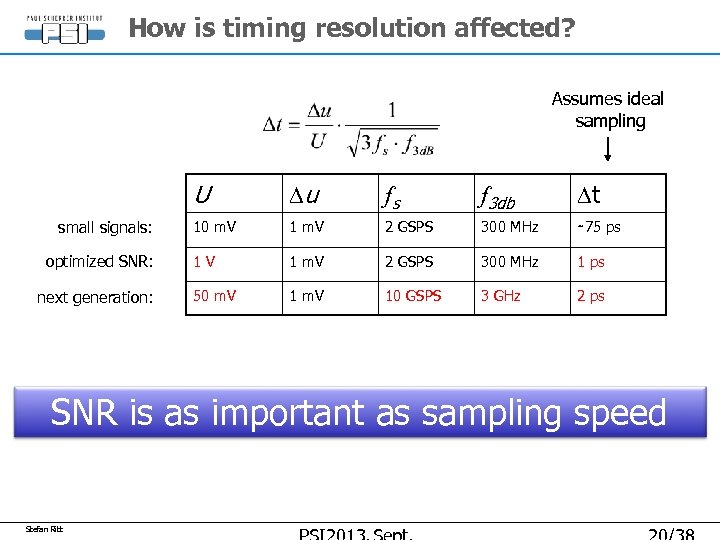

How is timing resolution affected? Assumes ideal sampling U small signals: optimized SNR: next generation: Du fs f 3 db Dt 10 m. V 1 m. V 2 GSPS 300 MHz ∼ 75 ps 1 V 1 m. V 2 GSPS 300 MHz 1 ps 50 m. V 10 GSPS 3 GHz 2 ps SNR is as important as sampling speed Stefan Ritt

How is timing resolution affected? Assumes ideal sampling U small signals: optimized SNR: next generation: Du fs f 3 db Dt 10 m. V 1 m. V 2 GSPS 300 MHz ∼ 75 ps 1 V 1 m. V 2 GSPS 300 MHz 1 ps 50 m. V 10 GSPS 3 GHz 2 ps SNR is as important as sampling speed Stefan Ritt

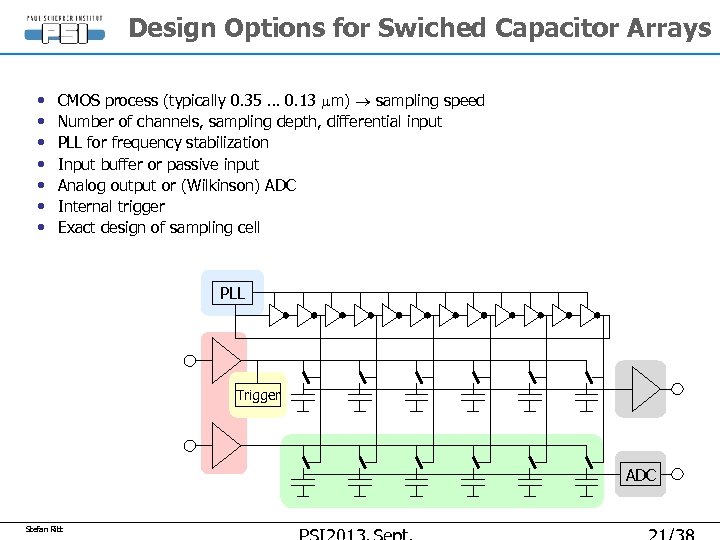

Design Options for Swiched Capacitor Arrays • • CMOS process (typically 0. 35 … 0. 13 mm) sampling speed Number of channels, sampling depth, differential input PLL for frequency stabilization Input buffer or passive input Analog output or (Wilkinson) ADC Internal trigger Exact design of sampling cell PLL Trigger ADC Stefan Ritt

Design Options for Swiched Capacitor Arrays • • CMOS process (typically 0. 35 … 0. 13 mm) sampling speed Number of channels, sampling depth, differential input PLL for frequency stabilization Input buffer or passive input Analog output or (Wilkinson) ADC Internal trigger Exact design of sampling cell PLL Trigger ADC Stefan Ritt

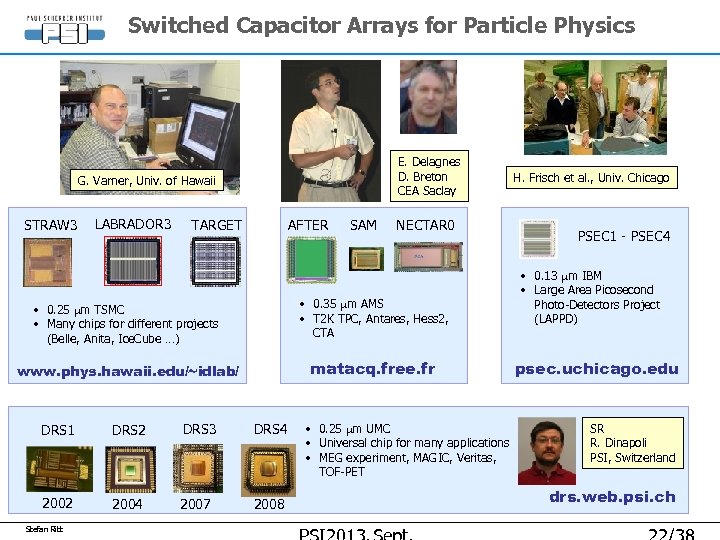

Switched Capacitor Arrays for Particle Physics E. Delagnes D. Breton CEA Saclay G. Varner, Univ. of Hawaii STRAW 3 LABRADOR 3 TARGET AFTER SAM NECTAR 0 • 0. 25 mm TSMC • Many chips for different projects (Belle, Anita, Ice. Cube …) • 0. 35 mm AMS • T 2 K TPC, Antares, Hess 2, CTA www. phys. hawaii. edu/~idlab/ matacq. free. fr DRS 1 DRS 2 DRS 3 DRS 4 2002 2004 2007 2008 Stefan Ritt • 0. 25 mm UMC • Universal chip for many applications • MEG experiment, MAGIC, Veritas, TOF-PET H. Frisch et al. , Univ. Chicago PSEC 1 - PSEC 4 • 0. 13 mm IBM • Large Area Picosecond Photo-Detectors Project (LAPPD) psec. uchicago. edu SR R. Dinapoli PSI, Switzerland drs. web. psi. ch

Switched Capacitor Arrays for Particle Physics E. Delagnes D. Breton CEA Saclay G. Varner, Univ. of Hawaii STRAW 3 LABRADOR 3 TARGET AFTER SAM NECTAR 0 • 0. 25 mm TSMC • Many chips for different projects (Belle, Anita, Ice. Cube …) • 0. 35 mm AMS • T 2 K TPC, Antares, Hess 2, CTA www. phys. hawaii. edu/~idlab/ matacq. free. fr DRS 1 DRS 2 DRS 3 DRS 4 2002 2004 2007 2008 Stefan Ritt • 0. 25 mm UMC • Universal chip for many applications • MEG experiment, MAGIC, Veritas, TOF-PET H. Frisch et al. , Univ. Chicago PSEC 1 - PSEC 4 • 0. 13 mm IBM • Large Area Picosecond Photo-Detectors Project (LAPPD) psec. uchicago. edu SR R. Dinapoli PSI, Switzerland drs. web. psi. ch

What can we do with that tool? Stefan Ritt

What can we do with that tool? Stefan Ritt

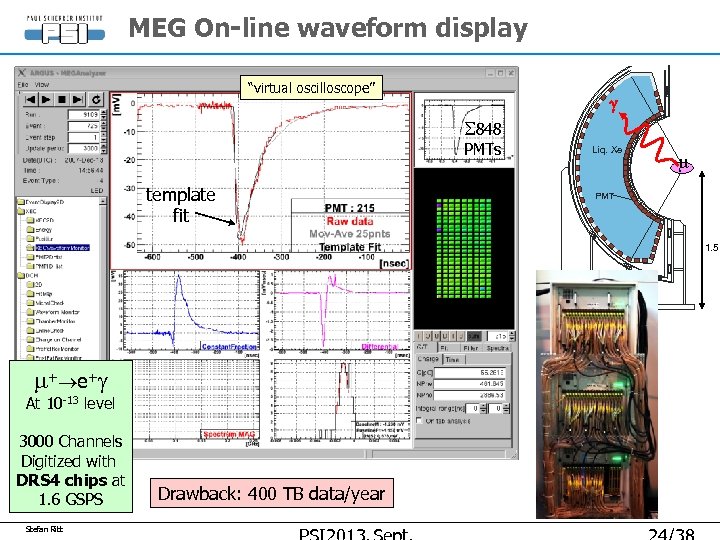

MEG On-line waveform display “virtual oscilloscope” g S 848 PMTs template fit Liq. Xe m PMT 1. 5 m m+ e+g At 10 -13 level 3000 Channels Digitized with DRS 4 chips at 1. 6 GSPS Stefan Ritt Drawback: 400 TB data/year

MEG On-line waveform display “virtual oscilloscope” g S 848 PMTs template fit Liq. Xe m PMT 1. 5 m m+ e+g At 10 -13 level 3000 Channels Digitized with DRS 4 chips at 1. 6 GSPS Stefan Ritt Drawback: 400 TB data/year

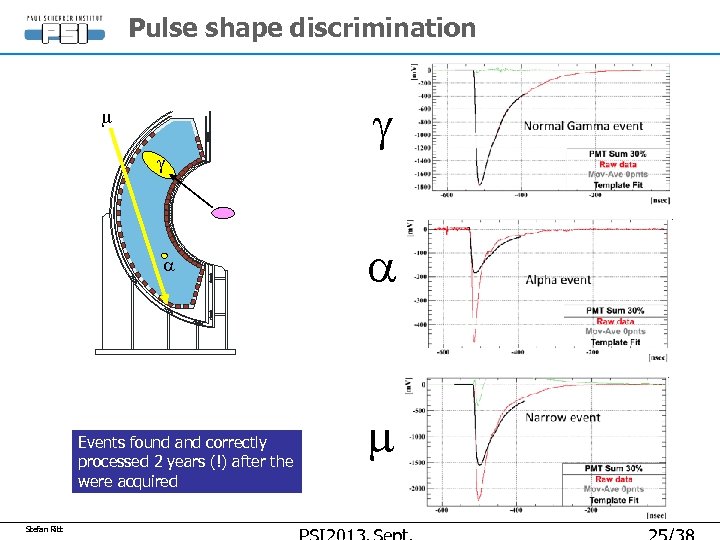

Pulse shape discrimination m g a Events found and correctly processed 2 years (!) after the were acquired Stefan Ritt g a m

Pulse shape discrimination m g a Events found and correctly processed 2 years (!) after the were acquired Stefan Ritt g a m

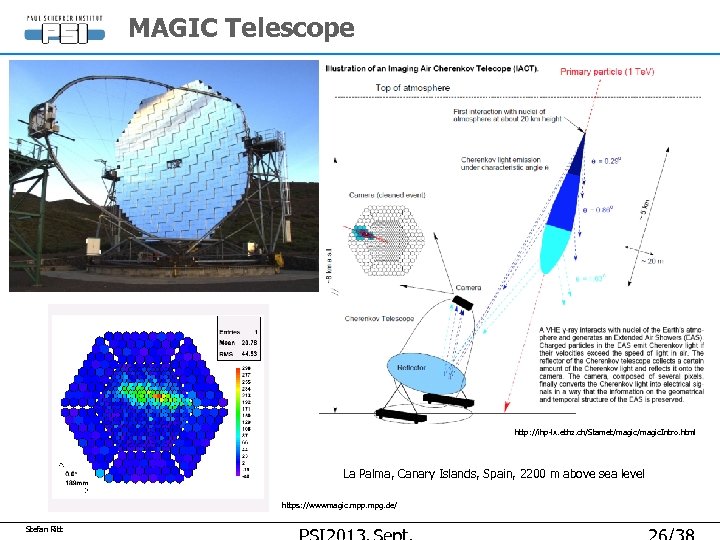

MAGIC Telescope http: //ihp-lx. ethz. ch/Stamet/magic. Intro. html La Palma, Canary Islands, Spain, 2200 m above sea level https: //wwwmagic. mpp. mpg. de/ Stefan Ritt

MAGIC Telescope http: //ihp-lx. ethz. ch/Stamet/magic. Intro. html La Palma, Canary Islands, Spain, 2200 m above sea level https: //wwwmagic. mpp. mpg. de/ Stefan Ritt

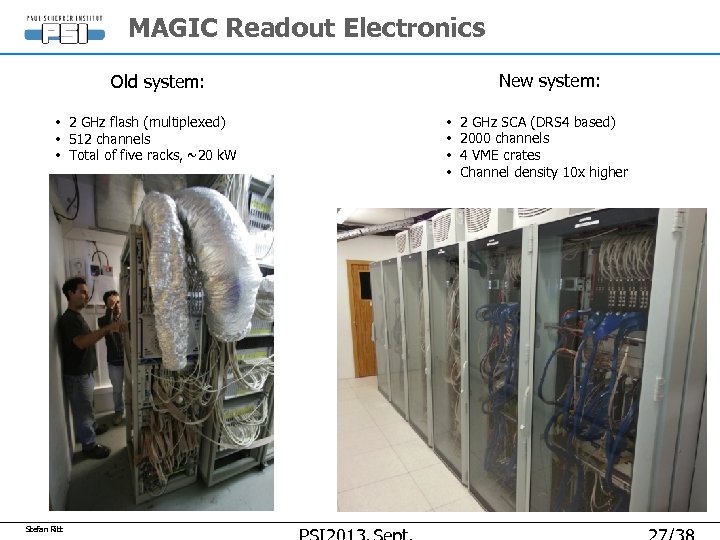

MAGIC Readout Electronics New system: Old system: • 2 GHz flash (multiplexed) • 512 channels • Total of five racks, ~20 k. W Stefan Ritt • • 2 GHz SCA (DRS 4 based) 2000 channels 4 VME crates Channel density 10 x higher

MAGIC Readout Electronics New system: Old system: • 2 GHz flash (multiplexed) • 512 channels • Total of five racks, ~20 k. W Stefan Ritt • • 2 GHz SCA (DRS 4 based) 2000 channels 4 VME crates Channel density 10 x higher

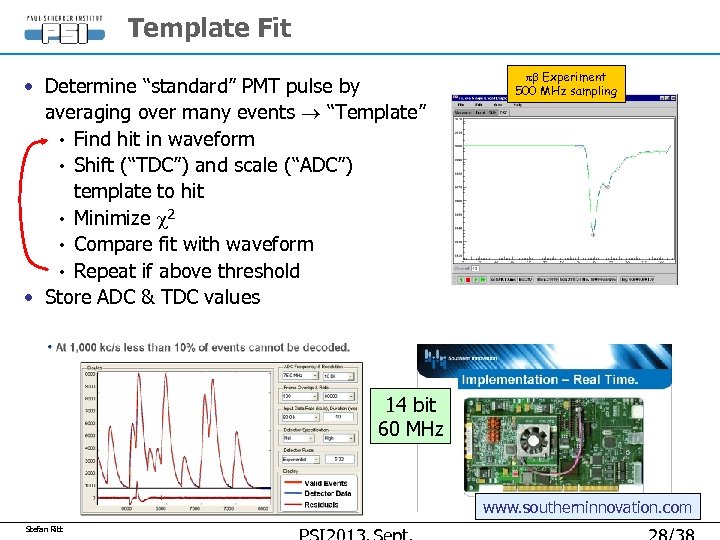

Template Fit • Determine “standard” PMT pulse by averaging over many events “Template” • Find hit in waveform • Shift (“TDC”) and scale (“ADC”) template to hit • Minimize c 2 • Compare fit with waveform • Repeat if above threshold • Store ADC & TDC values pb Experiment 500 MHz sampling 14 bit 60 MHz www. southerninnovation. com Stefan Ritt

Template Fit • Determine “standard” PMT pulse by averaging over many events “Template” • Find hit in waveform • Shift (“TDC”) and scale (“ADC”) template to hit • Minimize c 2 • Compare fit with waveform • Repeat if above threshold • Store ADC & TDC values pb Experiment 500 MHz sampling 14 bit 60 MHz www. southerninnovation. com Stefan Ritt

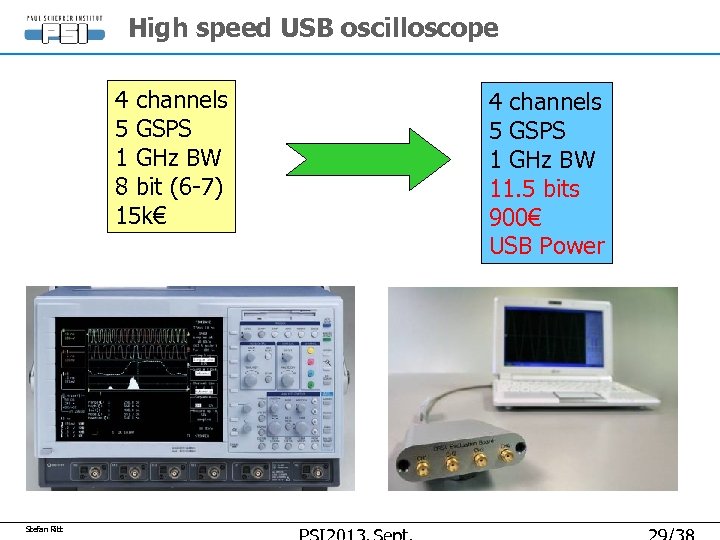

High speed USB oscilloscope 4 channels 5 GSPS 1 GHz BW 8 bit (6 -7) 15 k€ Stefan Ritt 4 channels 5 GSPS 1 GHz BW 11. 5 bits 900€ USB Power

High speed USB oscilloscope 4 channels 5 GSPS 1 GHz BW 8 bit (6 -7) 15 k€ Stefan Ritt 4 channels 5 GSPS 1 GHz BW 11. 5 bits 900€ USB Power

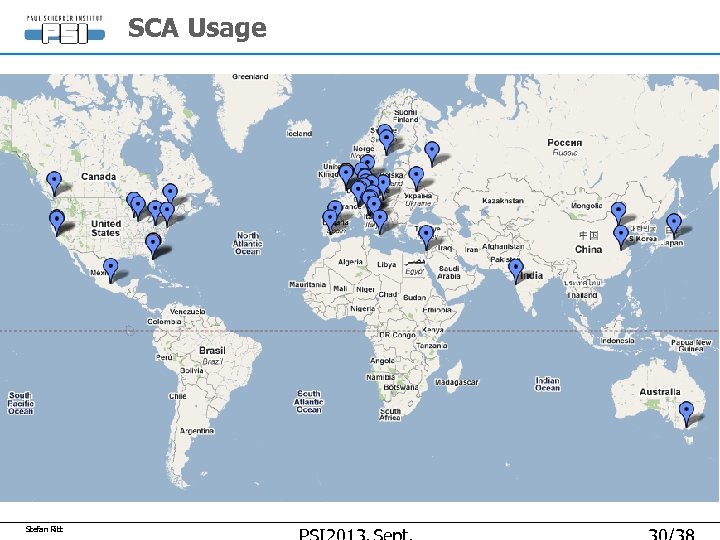

SCA Usage Stefan Ritt

SCA Usage Stefan Ritt

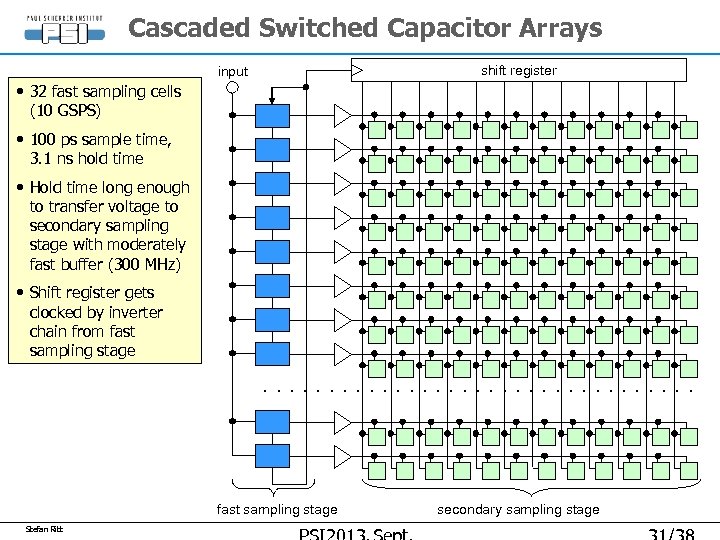

Cascaded Switched Capacitor Arrays shift register input • 32 fast sampling cells (10 GSPS) • 100 ps sample time, 3. 1 ns hold time • Hold time long enough to transfer voltage to secondary sampling stage with moderately fast buffer (300 MHz) • Shift register gets clocked by inverter chain from fast sampling stage . . . . fast sampling stage Stefan Ritt secondary sampling stage

Cascaded Switched Capacitor Arrays shift register input • 32 fast sampling cells (10 GSPS) • 100 ps sample time, 3. 1 ns hold time • Hold time long enough to transfer voltage to secondary sampling stage with moderately fast buffer (300 MHz) • Shift register gets clocked by inverter chain from fast sampling stage . . . . fast sampling stage Stefan Ritt secondary sampling stage

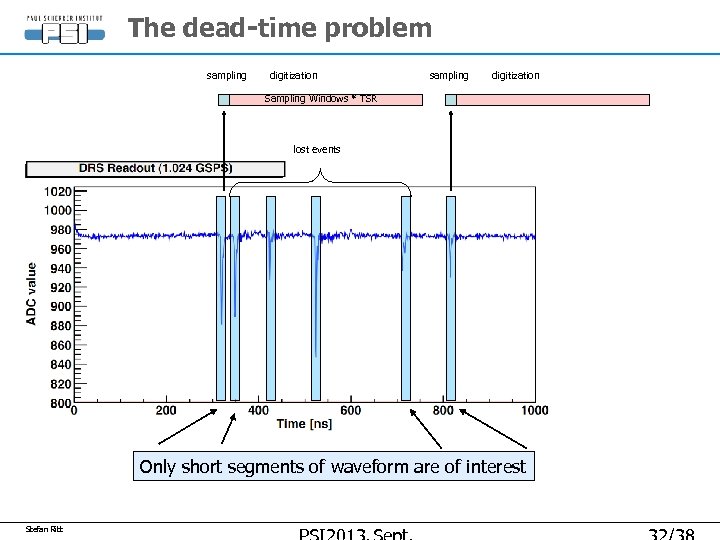

The dead-time problem sampling digitization Sampling Windows * TSR lost events Only short segments of waveform are of interest Stefan Ritt

The dead-time problem sampling digitization Sampling Windows * TSR lost events Only short segments of waveform are of interest Stefan Ritt

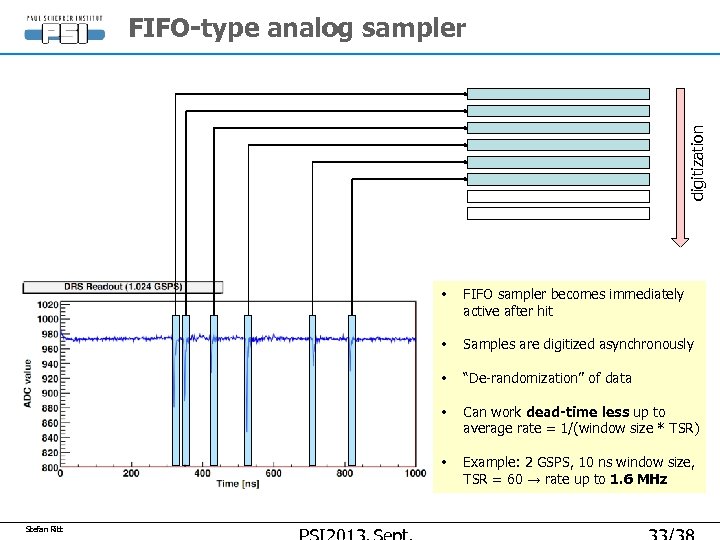

digitization FIFO-type analog sampler • • Samples are digitized asynchronously • “De-randomization” of data • Can work dead-time less up to average rate = 1/(window size * TSR) • Stefan Ritt FIFO sampler becomes immediately active after hit Example: 2 GSPS, 10 ns window size, TSR = 60 → rate up to 1. 6 MHz

digitization FIFO-type analog sampler • • Samples are digitized asynchronously • “De-randomization” of data • Can work dead-time less up to average rate = 1/(window size * TSR) • Stefan Ritt FIFO sampler becomes immediately active after hit Example: 2 GSPS, 10 ns window size, TSR = 60 → rate up to 1. 6 MHz

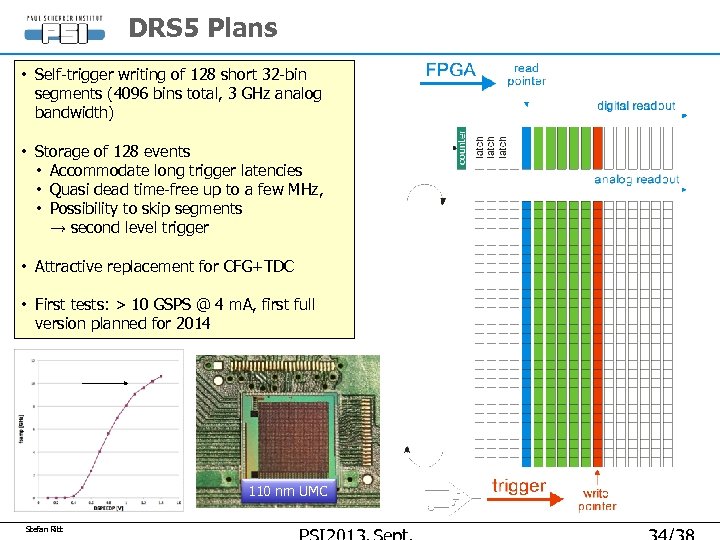

DRS 5 Plans • Self-trigger writing of 128 short 32 -bin segments (4096 bins total, 3 GHz analog bandwidth) • Storage of 128 events • Accommodate long trigger latencies • Quasi dead time-free up to a few MHz, • Possibility to skip segments → second level trigger • Attractive replacement for CFG+TDC • First tests: > 10 GSPS @ 4 m. A, first full version planned for 2014 110 nm UMC Stefan Ritt

DRS 5 Plans • Self-trigger writing of 128 short 32 -bin segments (4096 bins total, 3 GHz analog bandwidth) • Storage of 128 events • Accommodate long trigger latencies • Quasi dead time-free up to a few MHz, • Possibility to skip segments → second level trigger • Attractive replacement for CFG+TDC • First tests: > 10 GSPS @ 4 m. A, first full version planned for 2014 110 nm UMC Stefan Ritt

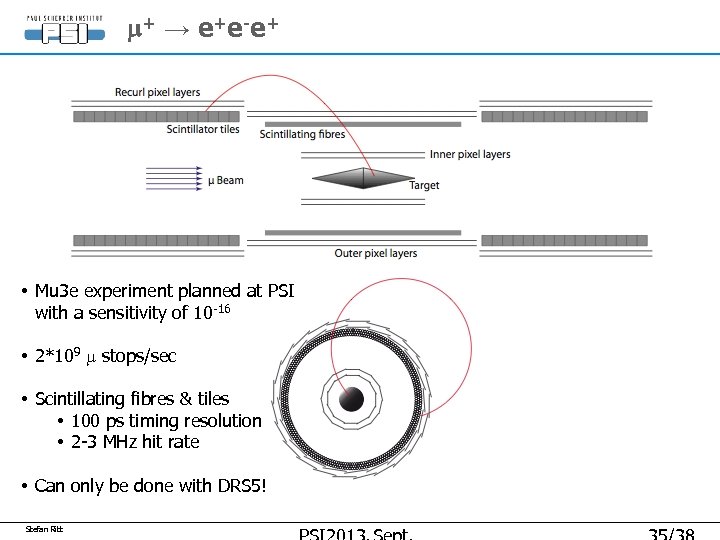

m + → e + e -e + • Mu 3 e experiment planned at PSI with a sensitivity of 10 -16 • 2*109 m stops/sec • Scintillating fibres & tiles • 100 ps timing resolution • 2 -3 MHz hit rate • Can only be done with DRS 5! Stefan Ritt

m + → e + e -e + • Mu 3 e experiment planned at PSI with a sensitivity of 10 -16 • 2*109 m stops/sec • Scintillating fibres & tiles • 100 ps timing resolution • 2 -3 MHz hit rate • Can only be done with DRS 5! Stefan Ritt

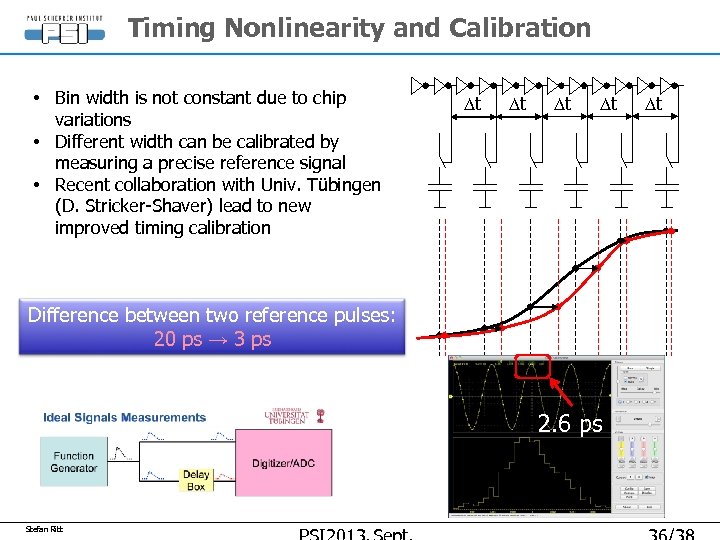

Timing Nonlinearity and Calibration • Bin width is not constant due to chip variations • Different width can be calibrated by measuring a precise reference signal • Recent collaboration with Univ. Tübingen (D. Stricker-Shaver) lead to new improved timing calibration Dt Dt Difference between two reference pulses: 20 ps → 3 ps 2. 6 ps Stefan Ritt Dt

Timing Nonlinearity and Calibration • Bin width is not constant due to chip variations • Different width can be calibrated by measuring a precise reference signal • Recent collaboration with Univ. Tübingen (D. Stricker-Shaver) lead to new improved timing calibration Dt Dt Difference between two reference pulses: 20 ps → 3 ps 2. 6 ps Stefan Ritt Dt

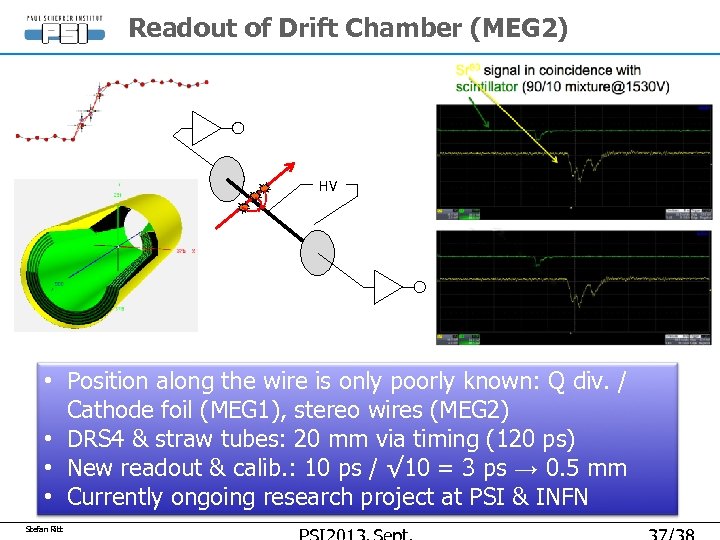

Readout of Drift Chamber (MEG 2) HV • Position along the wire is only poorly known: Q div. / Cathode foil (MEG 1), stereo wires (MEG 2) • DRS 4 & straw tubes: 20 mm via timing (120 ps) • New readout & calib. : 10 ps / √ 10 = 3 ps → 0. 5 mm • Currently ongoing research project at PSI & INFN Stefan Ritt

Readout of Drift Chamber (MEG 2) HV • Position along the wire is only poorly known: Q div. / Cathode foil (MEG 1), stereo wires (MEG 2) • DRS 4 & straw tubes: 20 mm via timing (120 ps) • New readout & calib. : 10 ps / √ 10 = 3 ps → 0. 5 mm • Currently ongoing research project at PSI & INFN Stefan Ritt

Conclusions • SCA technology offers tremendous opportunities • Several chips and boards are on the market for evaluation • New series of chips on the horizon might change frontend electronics significantly Stefan Ritt

Conclusions • SCA technology offers tremendous opportunities • Several chips and boards are on the market for evaluation • New series of chips on the horizon might change frontend electronics significantly Stefan Ritt

Backup Slides Stefan Ritt

Backup Slides Stefan Ritt

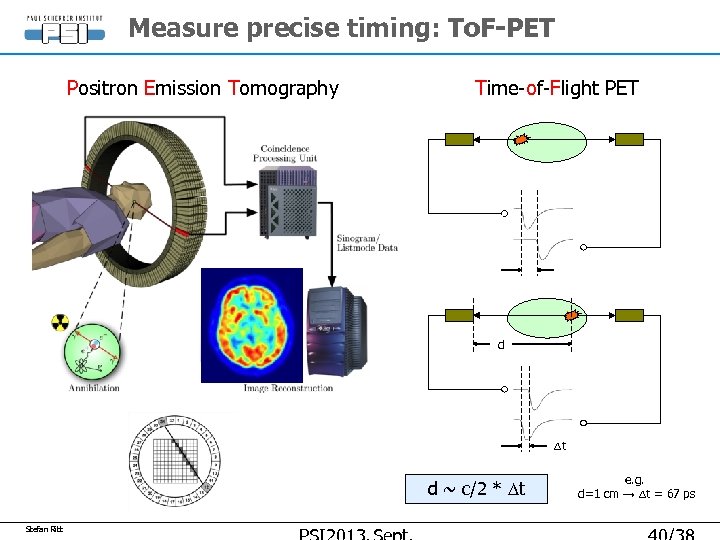

Measure precise timing: To. F-PET Positron Emission Tomography Time-of-Flight PET d Dt d ~ c/2 * Dt Stefan Ritt e. g. d=1 cm → Dt = 67 ps

Measure precise timing: To. F-PET Positron Emission Tomography Time-of-Flight PET d Dt d ~ c/2 * Dt Stefan Ritt e. g. d=1 cm → Dt = 67 ps

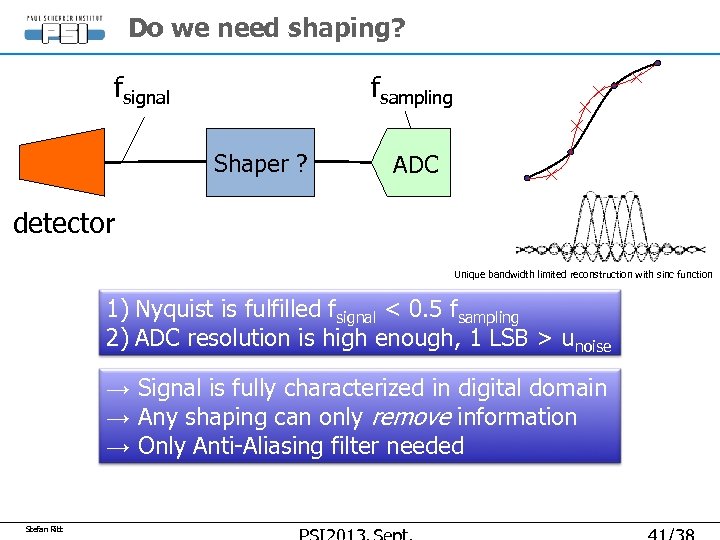

Do we need shaping? fsignal fsampling Shaper ? ADC detector Unique bandwidth limited reconstruction with sinc function 1) Nyquist is fulfilled fsignal < 0. 5 fsampling 2) ADC resolution is high enough, 1 LSB > unoise → Signal is fully characterized in digital domain → Any shaping can only remove information → Only Anti-Aliasing filter needed Stefan Ritt

Do we need shaping? fsignal fsampling Shaper ? ADC detector Unique bandwidth limited reconstruction with sinc function 1) Nyquist is fulfilled fsignal < 0. 5 fsampling 2) ADC resolution is high enough, 1 LSB > unoise → Signal is fully characterized in digital domain → Any shaping can only remove information → Only Anti-Aliasing filter needed Stefan Ritt

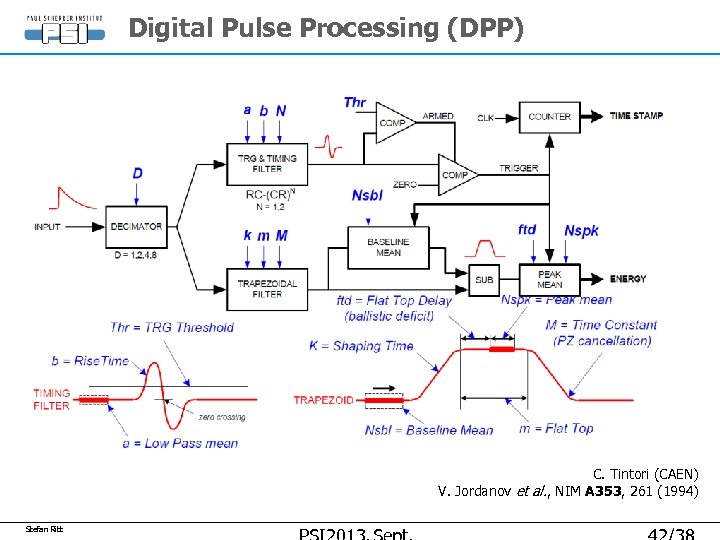

Digital Pulse Processing (DPP) C. Tintori (CAEN) V. Jordanov et al. , NIM A 353, 261 (1994) Stefan Ritt

Digital Pulse Processing (DPP) C. Tintori (CAEN) V. Jordanov et al. , NIM A 353, 261 (1994) Stefan Ritt

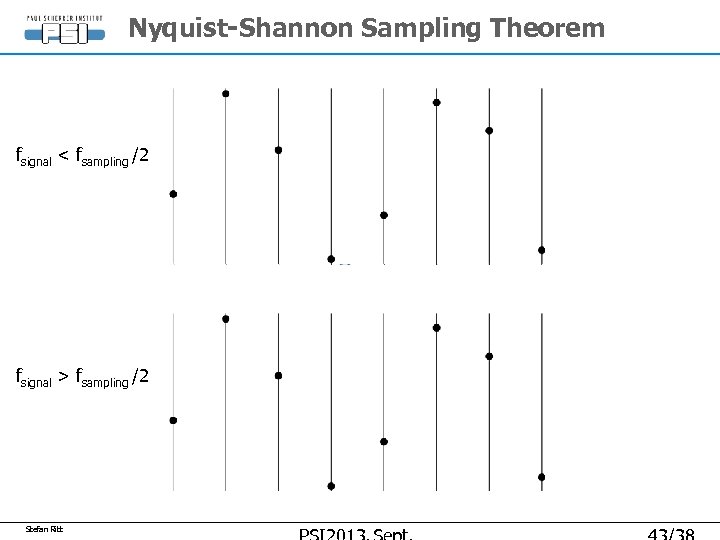

Nyquist-Shannon Sampling Theorem fsignal < fsampling /2 fsignal > fsampling /2 Stefan Ritt

Nyquist-Shannon Sampling Theorem fsignal < fsampling /2 fsignal > fsampling /2 Stefan Ritt

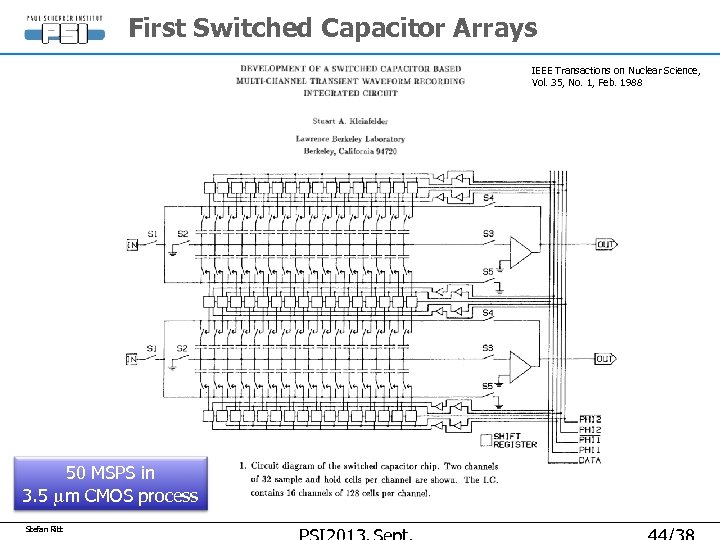

First Switched Capacitor Arrays IEEE Transactions on Nuclear Science, Vol. 35, No. 1, Feb. 1988 50 MSPS in 3. 5 mm CMOS process Stefan Ritt

First Switched Capacitor Arrays IEEE Transactions on Nuclear Science, Vol. 35, No. 1, Feb. 1988 50 MSPS in 3. 5 mm CMOS process Stefan Ritt

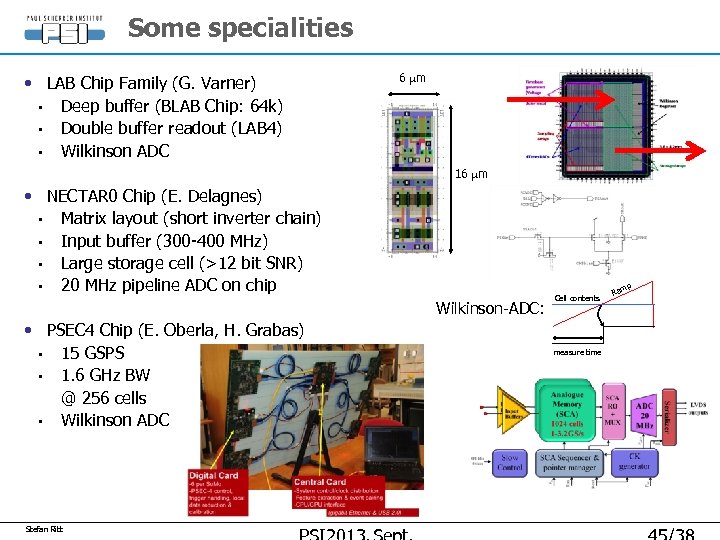

Some specialities • LAB Chip Family (G. Varner) • Deep buffer (BLAB Chip: 64 k) • Double buffer readout (LAB 4) • Wilkinson ADC 6 mm 16 mm • NECTAR 0 Chip (E. Delagnes) • Matrix layout (short inverter chain) • Input buffer (300 -400 MHz) • Large storage cell (>12 bit SNR) • 20 MHz pipeline ADC on chip p Wilkinson-ADC: • PSEC 4 Chip (E. Oberla, H. Grabas) • 15 GSPS • 1. 6 GHz BW @ 256 cells • Wilkinson ADC Stefan Ritt Cell contents measure time Ram

Some specialities • LAB Chip Family (G. Varner) • Deep buffer (BLAB Chip: 64 k) • Double buffer readout (LAB 4) • Wilkinson ADC 6 mm 16 mm • NECTAR 0 Chip (E. Delagnes) • Matrix layout (short inverter chain) • Input buffer (300 -400 MHz) • Large storage cell (>12 bit SNR) • 20 MHz pipeline ADC on chip p Wilkinson-ADC: • PSEC 4 Chip (E. Oberla, H. Grabas) • 15 GSPS • 1. 6 GHz BW @ 256 cells • Wilkinson ADC Stefan Ritt Cell contents measure time Ram

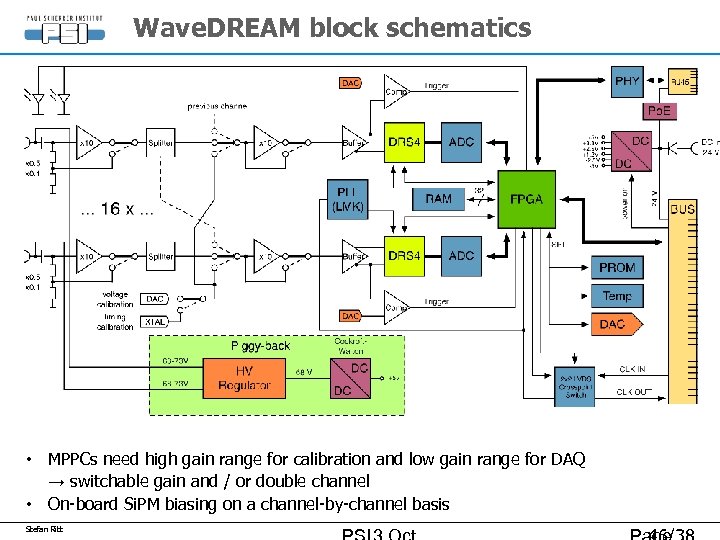

Wave. DREAM block schematics • MPPCs need high gain range for calibration and low gain range for DAQ → switchable gain and / or double channel • On-board Si. PM biasing on a channel-by-channel basis Stefan Ritt

Wave. DREAM block schematics • MPPCs need high gain range for calibration and low gain range for DAQ → switchable gain and / or double channel • On-board Si. PM biasing on a channel-by-channel basis Stefan Ritt

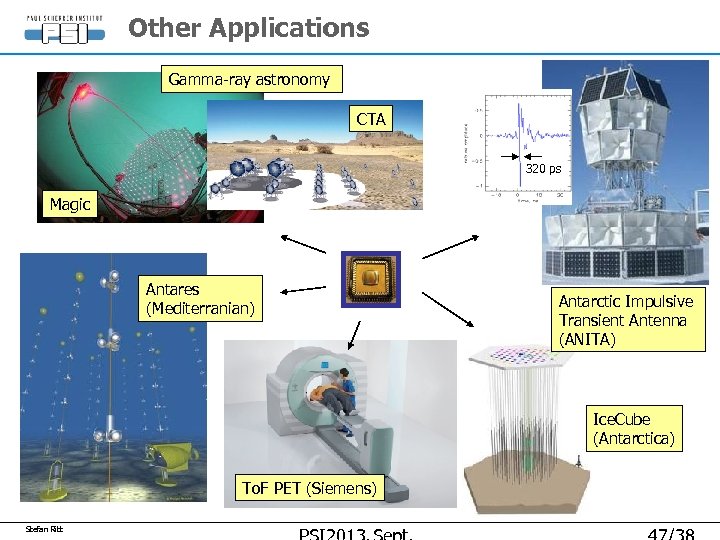

Other Applications Gamma-ray astronomy CTA 320 ps Magic Antares (Mediterranian) Antarctic Impulsive Transient Antenna (ANITA) Ice. Cube (Antarctica) To. F PET (Siemens) Stefan Ritt

Other Applications Gamma-ray astronomy CTA 320 ps Magic Antares (Mediterranian) Antarctic Impulsive Transient Antenna (ANITA) Ice. Cube (Antarctica) To. F PET (Siemens) Stefan Ritt

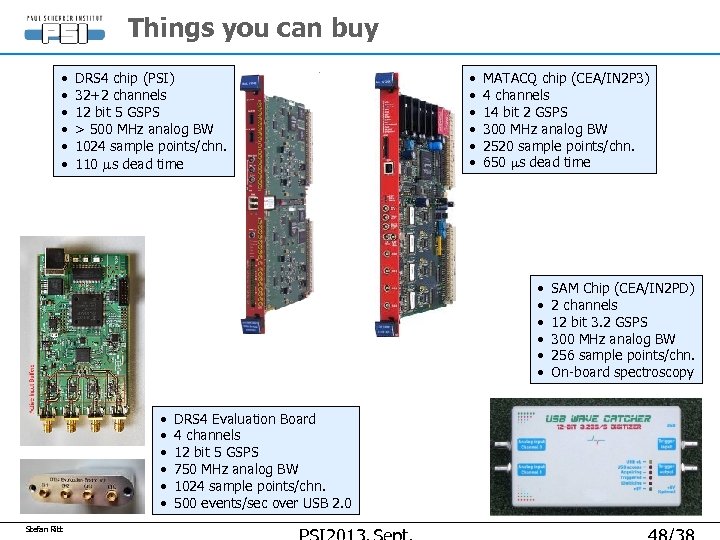

Things you can buy • • • DRS 4 chip (PSI) 32+2 channels 12 bit 5 GSPS > 500 MHz analog BW 1024 sample points/chn. 110 ms dead time • • • MATACQ chip (CEA/IN 2 P 3) 4 channels 14 bit 2 GSPS 300 MHz analog BW 2520 sample points/chn. 650 ms dead time • • • Stefan Ritt DRS 4 Evaluation Board 4 channels 12 bit 5 GSPS 750 MHz analog BW 1024 sample points/chn. 500 events/sec over USB 2. 0 SAM Chip (CEA/IN 2 PD) 2 channels 12 bit 3. 2 GSPS 300 MHz analog BW 256 sample points/chn. On-board spectroscopy

Things you can buy • • • DRS 4 chip (PSI) 32+2 channels 12 bit 5 GSPS > 500 MHz analog BW 1024 sample points/chn. 110 ms dead time • • • MATACQ chip (CEA/IN 2 P 3) 4 channels 14 bit 2 GSPS 300 MHz analog BW 2520 sample points/chn. 650 ms dead time • • • Stefan Ritt DRS 4 Evaluation Board 4 channels 12 bit 5 GSPS 750 MHz analog BW 1024 sample points/chn. 500 events/sec over USB 2. 0 SAM Chip (CEA/IN 2 PD) 2 channels 12 bit 3. 2 GSPS 300 MHz analog BW 256 sample points/chn. On-board spectroscopy