de6bfbb8f18f2c5e72cd863f757650b4.ppt

- Количество слайдов: 15

Panel Mode ISP Dudley Hiller Uwharrie Test Solutions LLC 30 -JUN-15 • • This presentation describes an In-System Programming technique that is gaining popularity on the Teradyne Test Station and GR 228 X, due to its increased throughput and cost savings. The advantage of Panel Mode ISP is you program all the units in the panel in the same time it takes to program a single unit. As with any new process there are new complications. This slide show describes the technique, the benefits, the complications and ways to overcome them.

Panel Mode ISP Dudley Hiller Uwharrie Test Solutions LLC 30 -JUN-15 • • This presentation describes an In-System Programming technique that is gaining popularity on the Teradyne Test Station and GR 228 X, due to its increased throughput and cost savings. The advantage of Panel Mode ISP is you program all the units in the panel in the same time it takes to program a single unit. As with any new process there are new complications. This slide show describes the technique, the benefits, the complications and ways to overcome them.

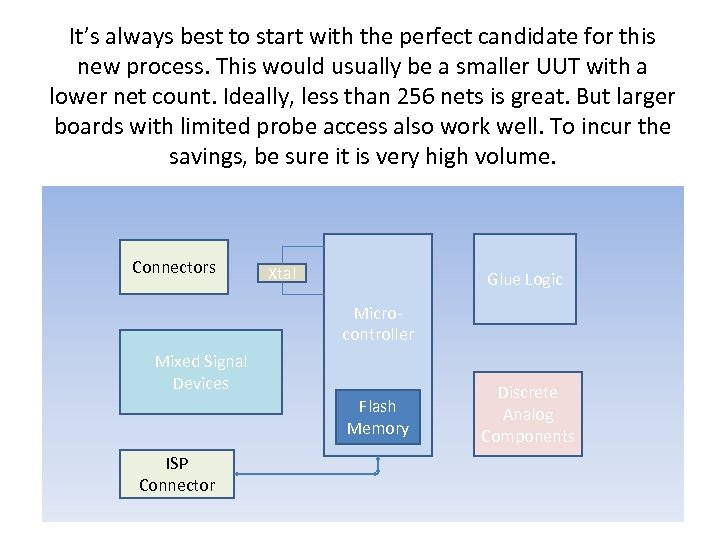

It’s always best to start with the perfect candidate for this new process. This would usually be a smaller UUT with a lower net count. Ideally, less than 256 nets is great. But larger boards with limited probe access also work well. To incur the savings, be sure it is very high volume. Connectors Xtal Glue Logic Microcontroller Mixed Signal Devices Flash Memory ISP Connector Discrete Analog Components

It’s always best to start with the perfect candidate for this new process. This would usually be a smaller UUT with a lower net count. Ideally, less than 256 nets is great. But larger boards with limited probe access also work well. To incur the savings, be sure it is very high volume. Connectors Xtal Glue Logic Microcontroller Mixed Signal Devices Flash Memory ISP Connector Discrete Analog Components

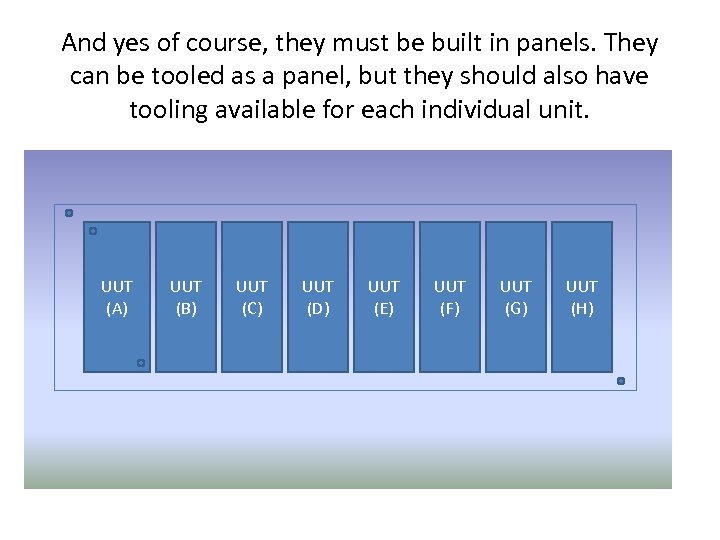

And yes of course, they must be built in panels. They can be tooled as a panel, but they should also have tooling available for each individual unit. UUT (A) UUT (B) UUT (C) UUT (D) UUT (E) UUT (F) UUT (G) UUT (H)

And yes of course, they must be built in panels. They can be tooled as a panel, but they should also have tooling available for each individual unit. UUT (A) UUT (B) UUT (C) UUT (D) UUT (E) UUT (F) UUT (G) UUT (H)

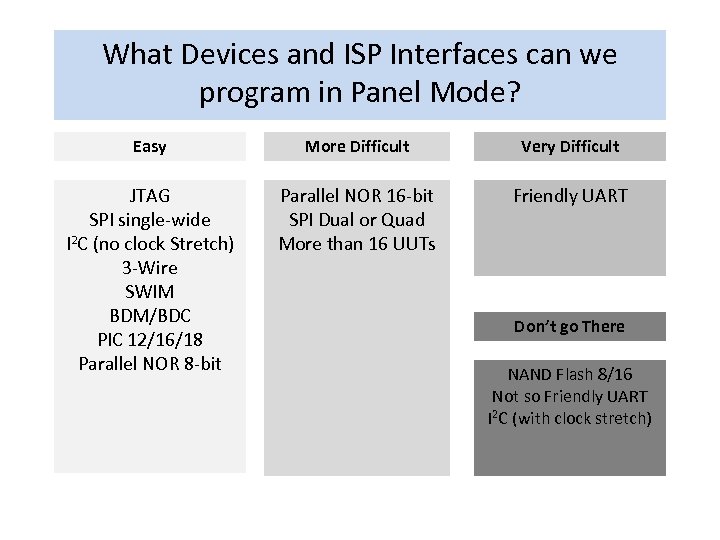

What Devices and ISP Interfaces can we program in Panel Mode? Easy More Difficult Very Difficult JTAG SPI single-wide I 2 C (no clock Stretch) 3 -Wire SWIM BDM/BDC PIC 12/16/18 Parallel NOR 8 -bit Parallel NOR 16 -bit SPI Dual or Quad More than 16 UUTs Friendly UART Don’t go There NAND Flash 8/16 Not so Friendly UART I 2 C (with clock stretch)

What Devices and ISP Interfaces can we program in Panel Mode? Easy More Difficult Very Difficult JTAG SPI single-wide I 2 C (no clock Stretch) 3 -Wire SWIM BDM/BDC PIC 12/16/18 Parallel NOR 8 -bit Parallel NOR 16 -bit SPI Dual or Quad More than 16 UUTs Friendly UART Don’t go There NAND Flash 8/16 Not so Friendly UART I 2 C (with clock stretch)

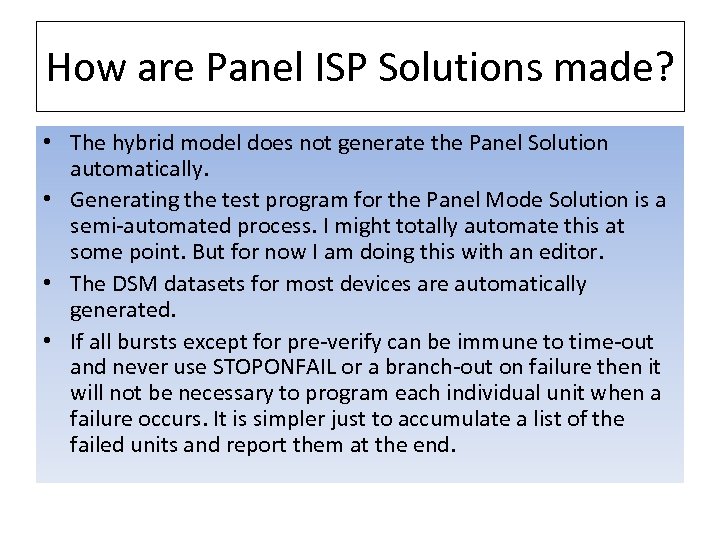

How are Panel ISP Solutions made? • The hybrid model does not generate the Panel Solution automatically. • Generating the test program for the Panel Mode Solution is a semi-automated process. I might totally automate this at some point. But for now I am doing this with an editor. • The DSM datasets for most devices are automatically generated. • If all bursts except for pre-verify can be immune to time-out and never use STOPONFAIL or a branch-out on failure then it will not be necessary to program each individual unit when a failure occurs. It is simpler just to accumulate a list of the failed units and report them at the end.

How are Panel ISP Solutions made? • The hybrid model does not generate the Panel Solution automatically. • Generating the test program for the Panel Mode Solution is a semi-automated process. I might totally automate this at some point. But for now I am doing this with an editor. • The DSM datasets for most devices are automatically generated. • If all bursts except for pre-verify can be immune to time-out and never use STOPONFAIL or a branch-out on failure then it will not be necessary to program each individual unit when a failure occurs. It is simpler just to accumulate a list of the failed units and report them at the end.

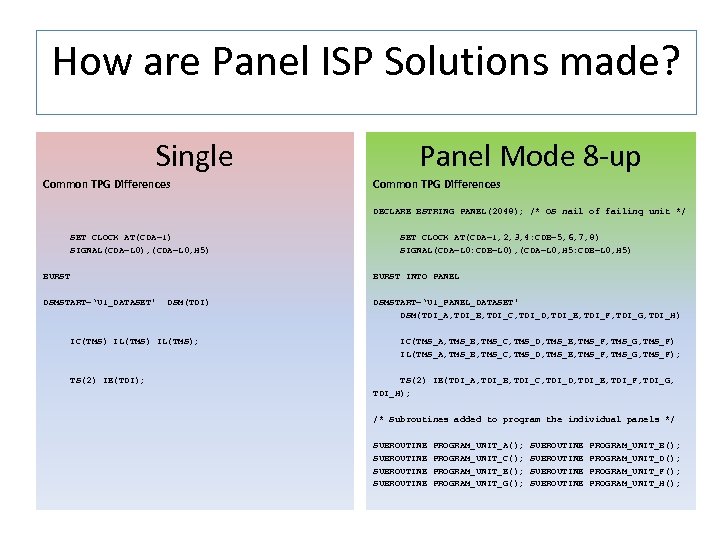

How are Panel ISP Solutions made? Single Common TPG Differences Panel Mode 8 -up Common TPG Differences DECLARE BSTRING PANEL(2048); /* OS nail of failing unit */ SET CLOCK AT(CDA=1) SIGNAL(CDA=L 0), (CDA=L 0, H 5) BURST SET CLOCK AT(CDA=1, 2, 3, 4: CDB=5, 6, 7, 8) SIGNAL(CDA=L 0: CDB=L 0), (CDA=L 0, H 5: CDB=L 0, H 5) BURST INTO PANEL DSMSTART=‘U 1_DATASET' DSM(TDI) IC(TMS) IL(TMS); TS(2) IE(TDI); DSMSTART=‘U 1_PANEL_DATASET' DSM(TDI_A, TDI_B, TDI_C, TDI_D, TDI_E, TDI_F, TDI_G, TDI_H) IC(TMS_A, TMS_B, TMS_C, TMS_D, TMS_E, TMS_F, TMS_G, TMS_F) IL(TMS_A, TMS_B, TMS_C, TMS_D, TMS_E, TMS_F, TMS_G, TMS_F); TS(2) IE(TDI_A, TDI_B, TDI_C, TDI_D, TDI_E, TDI_F, TDI_G, TDI_H); /* Subroutines added to program the individual panels */ SUBROUTINE PROGRAM_UNIT_A(); PROGRAM_UNIT_C(); PROGRAM_UNIT_E(); PROGRAM_UNIT_G(); SUBROUTINE PROGRAM_UNIT_B(); PROGRAM_UNIT_D(); PROGRAM_UNIT_F(); PROGRAM_UNIT_H();

How are Panel ISP Solutions made? Single Common TPG Differences Panel Mode 8 -up Common TPG Differences DECLARE BSTRING PANEL(2048); /* OS nail of failing unit */ SET CLOCK AT(CDA=1) SIGNAL(CDA=L 0), (CDA=L 0, H 5) BURST SET CLOCK AT(CDA=1, 2, 3, 4: CDB=5, 6, 7, 8) SIGNAL(CDA=L 0: CDB=L 0), (CDA=L 0, H 5: CDB=L 0, H 5) BURST INTO PANEL DSMSTART=‘U 1_DATASET' DSM(TDI) IC(TMS) IL(TMS); TS(2) IE(TDI); DSMSTART=‘U 1_PANEL_DATASET' DSM(TDI_A, TDI_B, TDI_C, TDI_D, TDI_E, TDI_F, TDI_G, TDI_H) IC(TMS_A, TMS_B, TMS_C, TMS_D, TMS_E, TMS_F, TMS_G, TMS_F) IL(TMS_A, TMS_B, TMS_C, TMS_D, TMS_E, TMS_F, TMS_G, TMS_F); TS(2) IE(TDI_A, TDI_B, TDI_C, TDI_D, TDI_E, TDI_F, TDI_G, TDI_H); /* Subroutines added to program the individual panels */ SUBROUTINE PROGRAM_UNIT_A(); PROGRAM_UNIT_C(); PROGRAM_UNIT_E(); PROGRAM_UNIT_G(); SUBROUTINE PROGRAM_UNIT_B(); PROGRAM_UNIT_D(); PROGRAM_UNIT_F(); PROGRAM_UNIT_H();

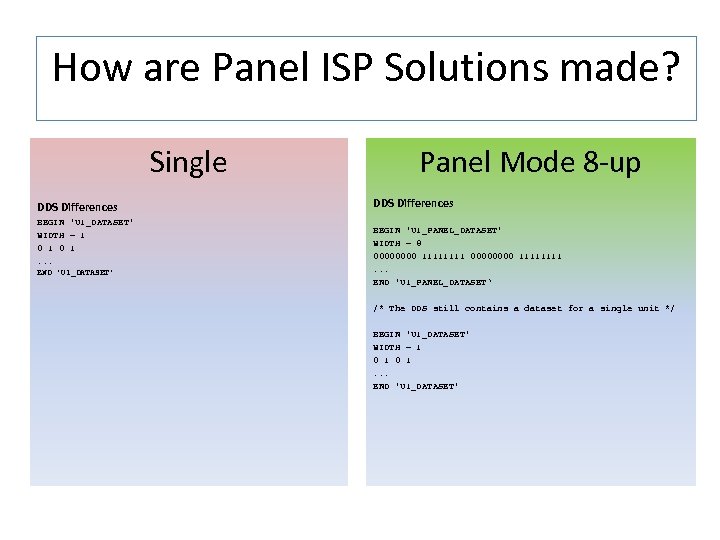

How are Panel ISP Solutions made? Single DDS Differences BEGIN 'U 1_DATASET' WIDTH = 1 0 1. . . END 'U 1_DATASET' Panel Mode 8 -up DDS Differences BEGIN 'U 1_PANEL_DATASET' WIDTH = 8 00000000 11111111. . . END 'U 1_PANEL_DATASET‘ /* The DDS still contains a dataset for a single unit */ BEGIN 'U 1_DATASET' WIDTH = 1 0 1. . . END 'U 1_DATASET'

How are Panel ISP Solutions made? Single DDS Differences BEGIN 'U 1_DATASET' WIDTH = 1 0 1. . . END 'U 1_DATASET' Panel Mode 8 -up DDS Differences BEGIN 'U 1_PANEL_DATASET' WIDTH = 8 00000000 11111111. . . END 'U 1_PANEL_DATASET‘ /* The DDS still contains a dataset for a single unit */ BEGIN 'U 1_DATASET' WIDTH = 1 0 1. . . END 'U 1_DATASET'

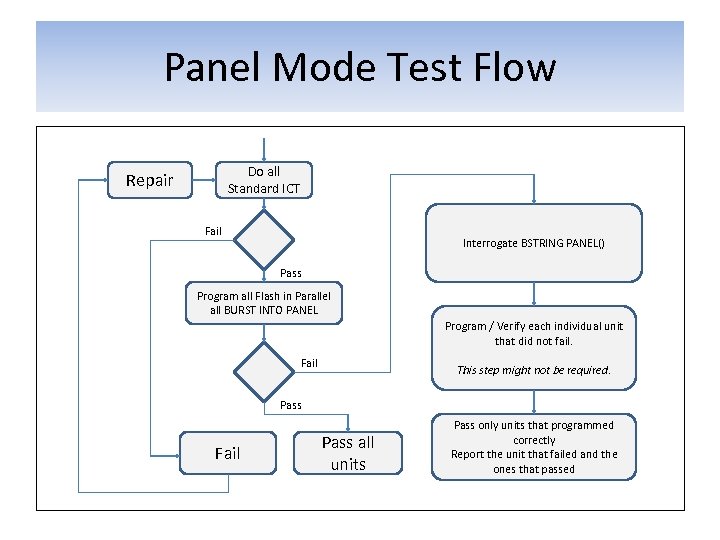

Panel Mode Test Flow Do all Standard ICT Repair Fail Interrogate BSTRING PANEL() Pass Program all Flash in Parallel all BURST INTO PANEL Program / Verify each individual unit that did not fail. Fail This step might not be required. Pass Fail Pass all units Pass only units that programmed correctly Report the unit that failed and the ones that passed

Panel Mode Test Flow Do all Standard ICT Repair Fail Interrogate BSTRING PANEL() Pass Program all Flash in Parallel all BURST INTO PANEL Program / Verify each individual unit that did not fail. Fail This step might not be required. Pass Fail Pass all units Pass only units that programmed correctly Report the unit that failed and the ones that passed

Cost to add Panel Mode ISP • I charge between $500. 00 USD and $2000. 00 beyond the price of the ISP model, to make a panel solution. This price depends on the number of units, and whether or not the panel needs to be wired up and functionally tested, or that task is passed along to the Board Test Engineer. • The cost of a fixture will increase a significant amount, as an 8 -up panel will need 8 times as many sockets, probes, wires and drilled locations. • The Test Engineer who develops the board test should also charge more, as the Test Program and the Panel Mode Nail. Assign becomes more complex.

Cost to add Panel Mode ISP • I charge between $500. 00 USD and $2000. 00 beyond the price of the ISP model, to make a panel solution. This price depends on the number of units, and whether or not the panel needs to be wired up and functionally tested, or that task is passed along to the Board Test Engineer. • The cost of a fixture will increase a significant amount, as an 8 -up panel will need 8 times as many sockets, probes, wires and drilled locations. • The Test Engineer who develops the board test should also charge more, as the Test Program and the Panel Mode Nail. Assign becomes more complex.

Nail-Assign Panel-Assign Requirement • If you do a panel of more that 2 -up, the panel mode assignment must be done in the Unconstrained Mode. See: Test. Station™ Panel Test, Serial Numbering, and Split Fixturing Manual. If you do the Offset Mode Panel. Assign, you will end up with a DSM mux conflict that you cannot resolve. – My opinion of Unconstrained Mode only is evolving. I am willing to try the offset mode. But we will need to wire dual resources to the pins that connect to the Deep Serial Memory. • I prefer to choose the set of nails to be used on the ISP signals of each unit (typically 4 -5 nails). Then the Board Test Engineer can force the Nail-Assign and Panel-Assign using an NDB or other Navigatetm method to force the assignment. • I can functionally test the panel mode programming with the same nail set used by the fixture.

Nail-Assign Panel-Assign Requirement • If you do a panel of more that 2 -up, the panel mode assignment must be done in the Unconstrained Mode. See: Test. Station™ Panel Test, Serial Numbering, and Split Fixturing Manual. If you do the Offset Mode Panel. Assign, you will end up with a DSM mux conflict that you cannot resolve. – My opinion of Unconstrained Mode only is evolving. I am willing to try the offset mode. But we will need to wire dual resources to the pins that connect to the Deep Serial Memory. • I prefer to choose the set of nails to be used on the ISP signals of each unit (typically 4 -5 nails). Then the Board Test Engineer can force the Nail-Assign and Panel-Assign using an NDB or other Navigatetm method to force the assignment. • I can functionally test the panel mode programming with the same nail set used by the fixture.

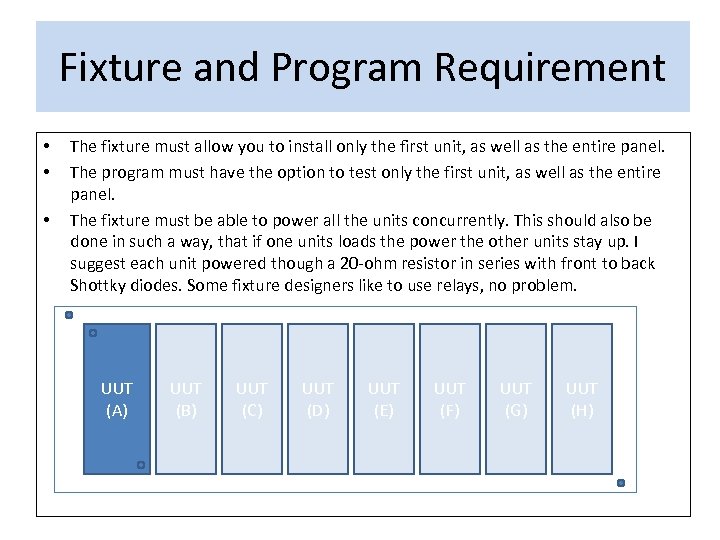

Fixture and Program Requirement • • • The fixture must allow you to install only the first unit, as well as the entire panel. The program must have the option to test only the first unit, as well as the entire panel. The fixture must be able to power all the units concurrently. This should also be done in such a way, that if one units loads the power the other units stay up. I suggest each unit powered though a 20 -ohm resistor in series with front to back Shottky diodes. Some fixture designers like to use relays, no problem. UUT (A) UUT (B) UUT (C) UUT (D) UUT (E) UUT (F) UUT (G) UUT (H)

Fixture and Program Requirement • • • The fixture must allow you to install only the first unit, as well as the entire panel. The program must have the option to test only the first unit, as well as the entire panel. The fixture must be able to power all the units concurrently. This should also be done in such a way, that if one units loads the power the other units stay up. I suggest each unit powered though a 20 -ohm resistor in series with front to back Shottky diodes. Some fixture designers like to use relays, no problem. UUT (A) UUT (B) UUT (C) UUT (D) UUT (E) UUT (F) UUT (G) UUT (H)

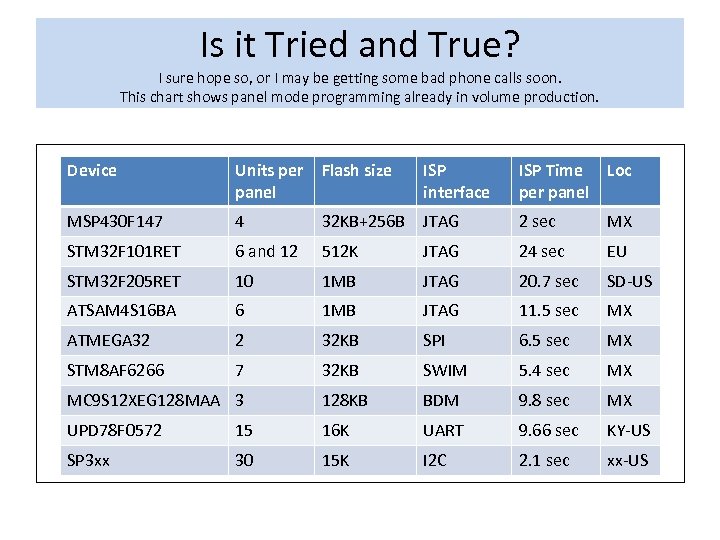

Is it Tried and True? I sure hope so, or I may be getting some bad phone calls soon. This chart shows panel mode programming already in volume production. Device Units per panel Flash size ISP interface ISP Time Loc per panel MSP 430 F 147 4 32 KB+256 B JTAG 2 sec MX STM 32 F 101 RET 6 and 12 512 K JTAG 24 sec EU STM 32 F 205 RET 10 1 MB JTAG 20. 7 sec SD-US ATSAM 4 S 16 BA 6 1 MB JTAG 11. 5 sec MX ATMEGA 32 2 32 KB SPI 6. 5 sec MX STM 8 AF 6266 7 32 KB SWIM 5. 4 sec MX MC 9 S 12 XEG 128 MAA 3 128 KB BDM 9. 8 sec MX UPD 78 F 0572 15 16 K UART 9. 66 sec KY-US SP 3 xx 30 15 K I 2 C 2. 1 sec xx-US

Is it Tried and True? I sure hope so, or I may be getting some bad phone calls soon. This chart shows panel mode programming already in volume production. Device Units per panel Flash size ISP interface ISP Time Loc per panel MSP 430 F 147 4 32 KB+256 B JTAG 2 sec MX STM 32 F 101 RET 6 and 12 512 K JTAG 24 sec EU STM 32 F 205 RET 10 1 MB JTAG 20. 7 sec SD-US ATSAM 4 S 16 BA 6 1 MB JTAG 11. 5 sec MX ATMEGA 32 2 32 KB SPI 6. 5 sec MX STM 8 AF 6266 7 32 KB SWIM 5. 4 sec MX MC 9 S 12 XEG 128 MAA 3 128 KB BDM 9. 8 sec MX UPD 78 F 0572 15 16 K UART 9. 66 sec KY-US SP 3 xx 30 15 K I 2 C 2. 1 sec xx-US

Any Disadvantage? Yes some… • Up-front DFT requirements, and convincing CAD designers to do them. • The up-front costs could be prohibitive, if your volume is not high enough. • Your process gets messy if your ICT yield falls below 99%. Separation and re-test as singles may be required at times. • Operators have to be trained to understand which units passed and which units failed if all units did not successfully program and verify • Separation from panel happens after ICT, so ICT will not detect separation damage to the unit. Be careful there.

Any Disadvantage? Yes some… • Up-front DFT requirements, and convincing CAD designers to do them. • The up-front costs could be prohibitive, if your volume is not high enough. • Your process gets messy if your ICT yield falls below 99%. Separation and re-test as singles may be required at times. • Operators have to be trained to understand which units passed and which units failed if all units did not successfully program and verify • Separation from panel happens after ICT, so ICT will not detect separation damage to the unit. Be careful there.

The Economic Breakdown Example using STM 32 F 407 with 1 Mbyte Flash Single Mode • Execution time for single piece 11. 5 seconds Panel Mode 8 -up • • • Your CM after he programs 1 million pieces individually Execution time for 8 pieces 11. 5 seconds Time saved, 80. 5 seconds per panel or 10. 0 seconds per piece. Cost savings at $72 USD per hour at ICT: $0. 20 per unit, $200, 000 per 1 million units Things your CM can do with the savings Or I can supply an account number where they can wire-transfer what they don’t need

The Economic Breakdown Example using STM 32 F 407 with 1 Mbyte Flash Single Mode • Execution time for single piece 11. 5 seconds Panel Mode 8 -up • • • Your CM after he programs 1 million pieces individually Execution time for 8 pieces 11. 5 seconds Time saved, 80. 5 seconds per panel or 10. 0 seconds per piece. Cost savings at $72 USD per hour at ICT: $0. 20 per unit, $200, 000 per 1 million units Things your CM can do with the savings Or I can supply an account number where they can wire-transfer what they don’t need

Conclusion Panel Mode ISP The Jury’s still out Decide if it’s right for your process

Conclusion Panel Mode ISP The Jury’s still out Decide if it’s right for your process