Pamięc RAM Denys Bykovskyi ETI 3. 3

Literatura • Józef Kalisz – Podstawy Elektroniki Cyfrowej • Baranowski J. et. al. Układy Elektroniczne cz. 3 – Układy i systemy cyfrowe • www. wikipedia. org (ang. ) • http: //galaxy. uci. agh. edu. pl/~jamro/tc

Pamięci • RAM (Random Access Memory) Statyczne (SRAM) -Asynchroniczne -Synchroniczne Dynamiczne (DRAM) -Asynchroniczne (historia) - Synchroniczne SDRAM, DDR 2, DDR 3, RAM-BUS (RDRAM), XDR-DRAM Specjalizowane FIFO (First-In First-Out) LIFO (Last-In First-Out – stos) CAM (Content-Addressable Memory) LUT (Look-Up Table) (pamięć ROM/RAM)

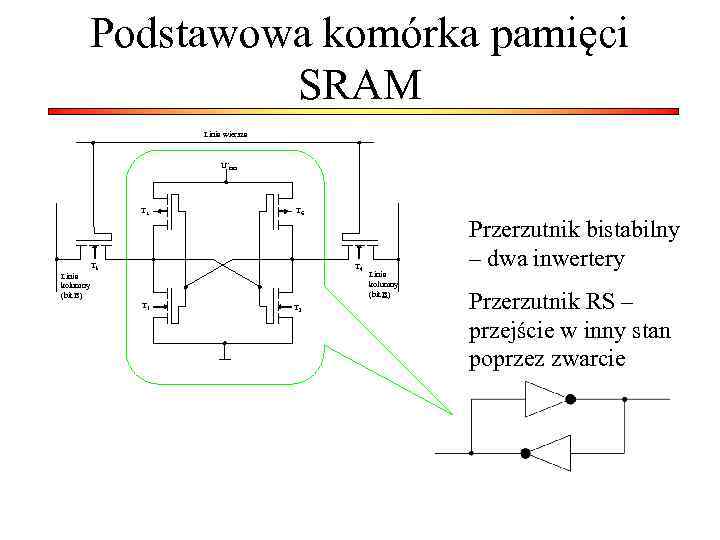

Podstawowa komórka pamięci SRAM Linia wiersza U’DD T 5 T 6 T 3 T 4 Linia kolumny (bit B) T 1 T 2 Linia kolumny (bit B) Przerzutnik bistabilny – dwa inwertery Przerzutnik RS – przejście w inny stan poprzez zwarcie

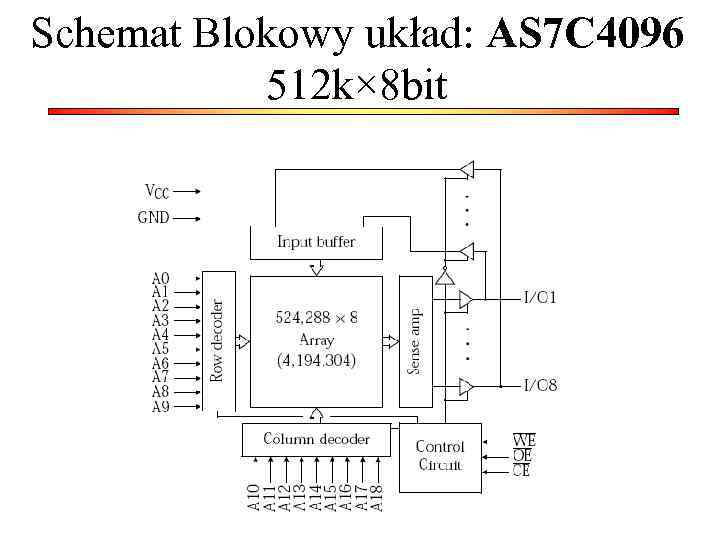

Schemat Blokowy układ: AS 7 C 4096 512 k× 8 bit

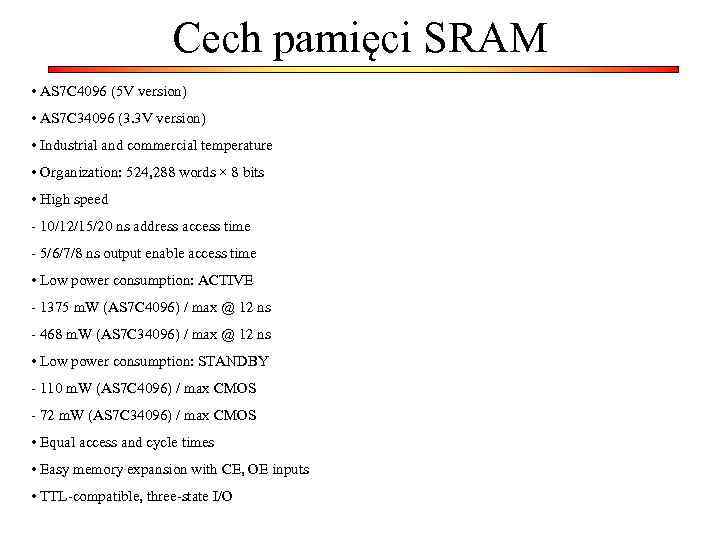

Cech pamięci SRAM • AS 7 C 4096 (5 V version) • AS 7 C 34096 (3. 3 V version) • Industrial and commercial temperature • Organization: 524, 288 words × 8 bits • High speed - 10/12/15/20 ns address access time - 5/6/7/8 ns output enable access time • Low power consumption: ACTIVE - 1375 m. W (AS 7 C 4096) / max @ 12 ns - 468 m. W (AS 7 C 34096) / max @ 12 ns • Low power consumption: STANDBY - 110 m. W (AS 7 C 4096) / max CMOS - 72 m. W (AS 7 C 34096) / max CMOS • Equal access and cycle times • Easy memory expansion with CE, OE inputs • TTL-compatible, three-state I/O

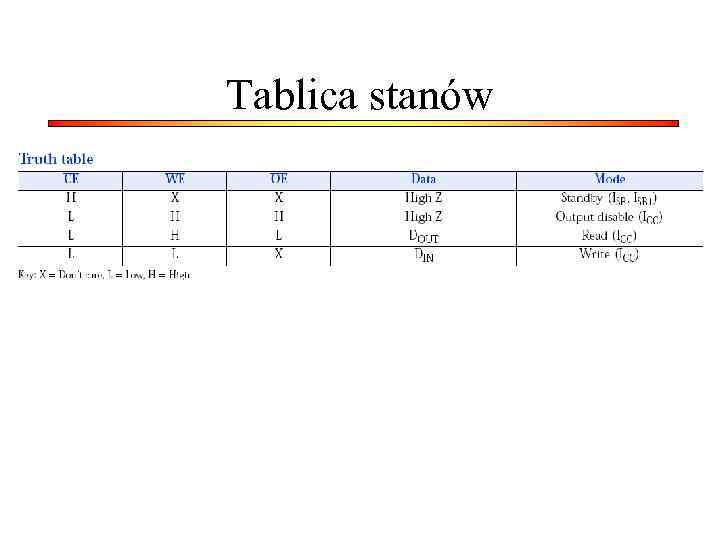

Tablica stanów

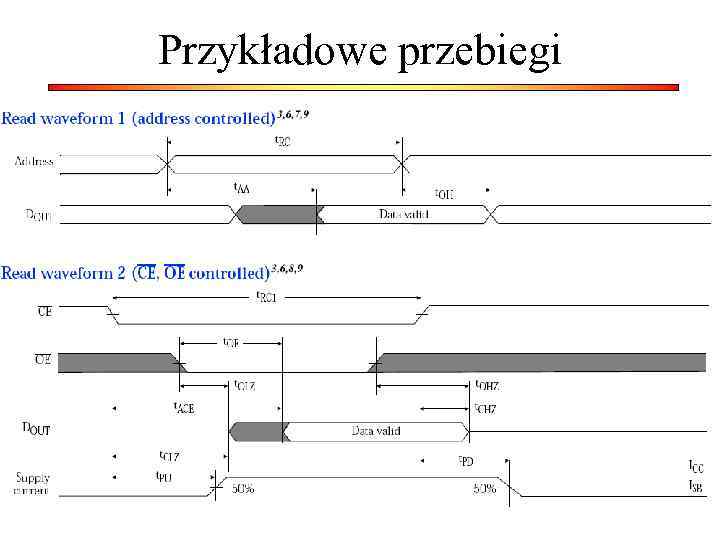

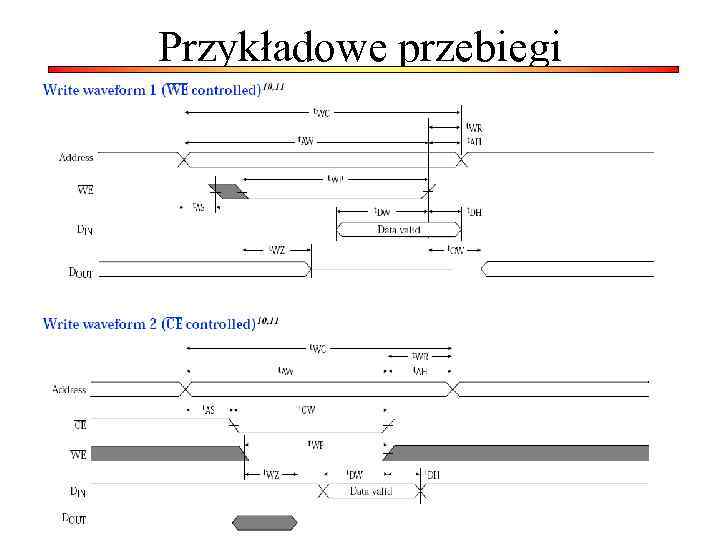

Przykładowe przebiegi

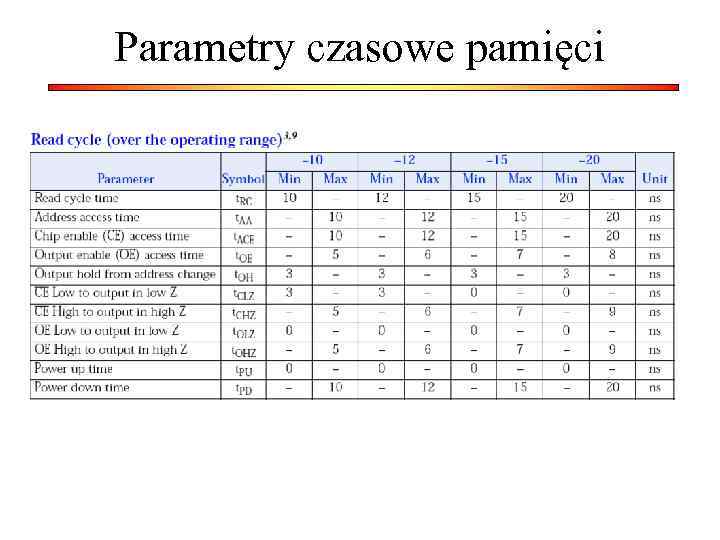

Parametry czasowe pamięci

Przykładowe przebiegi

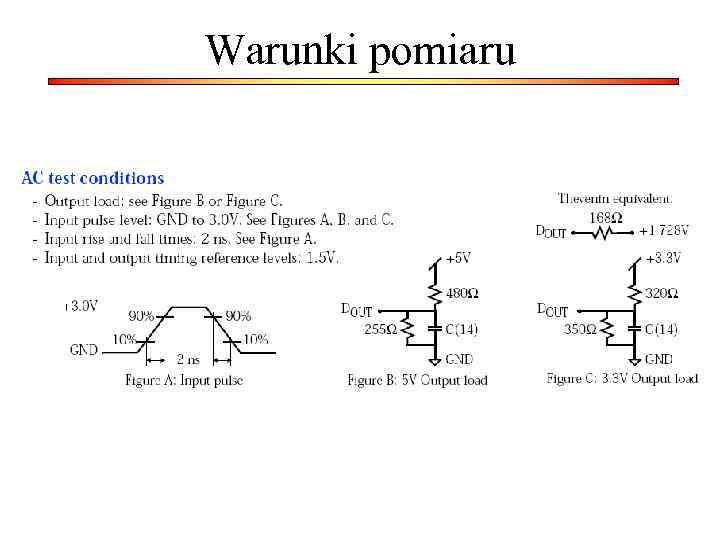

Warunki pomiaru

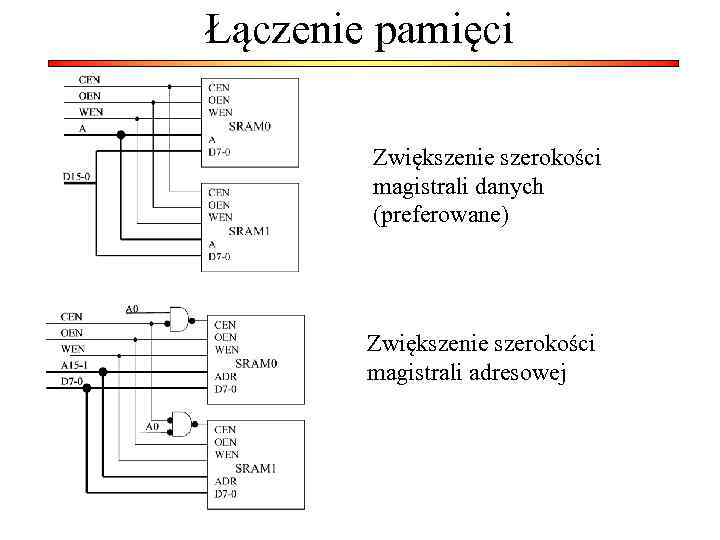

Łączenie pamięci Zwiększenie szerokości magistrali danych (preferowane) Zwiększenie szerokości magistrali adresowej

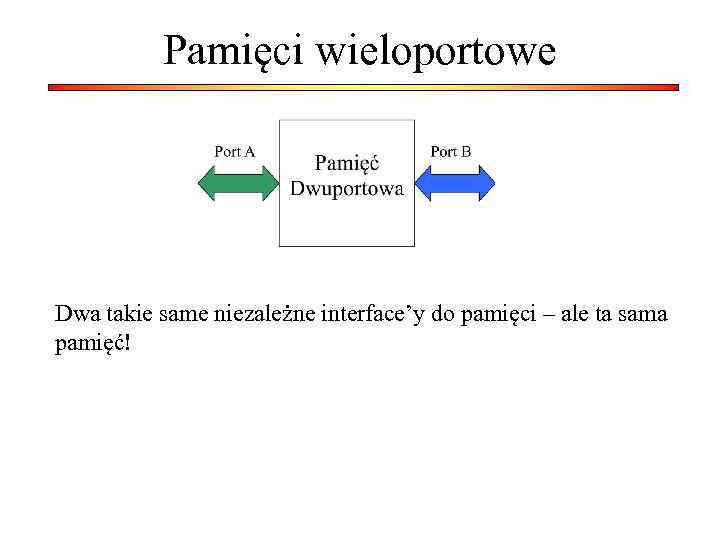

Pamięci wieloportowe Dwa takie same niezależne interface’y do pamięci – ale ta sama pamięć!

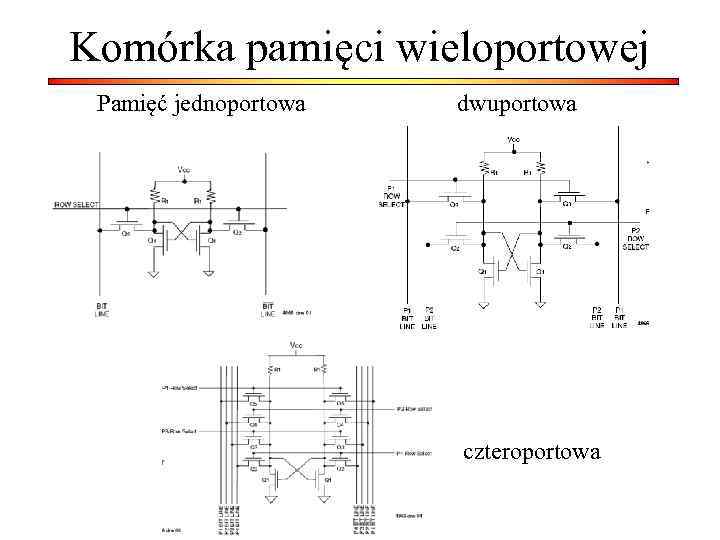

Komórka pamięci wieloportowej Pamięć jednoportowa dwuportowa czteroportowa

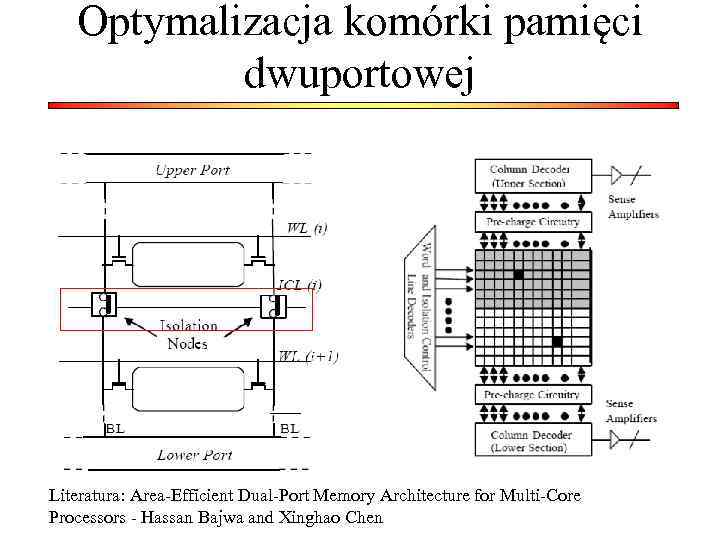

Optymalizacja komórki pamięci dwuportowej Literatura: Area-Efficient Dual-Port Memory Architecture for Multi-Core Processors - Hassan Bajwa and Xinghao Chen

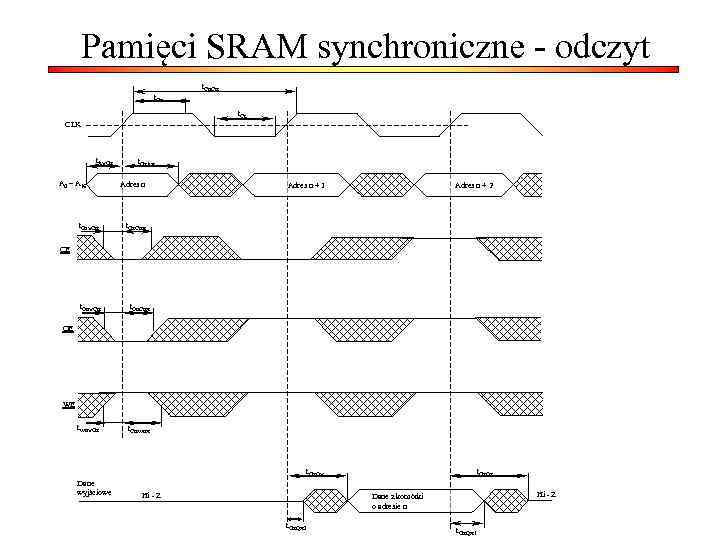

Pamięci SRAM synchroniczne - odczyt t. CHCH t. CL CLK t. AVCH A 0 – A 16 t. CHAX Adres n + 2 t. CHQV t. CEVCH Adres n + 1 t. CHQZ t. CHCEX CE t. OEVCH t. OHCEX t. WEVCH t. CHWEX OE WE Dane wyjściowe Hi - Z Dane z komórki o adresie n t. CHQX 2 t. CHQX 1

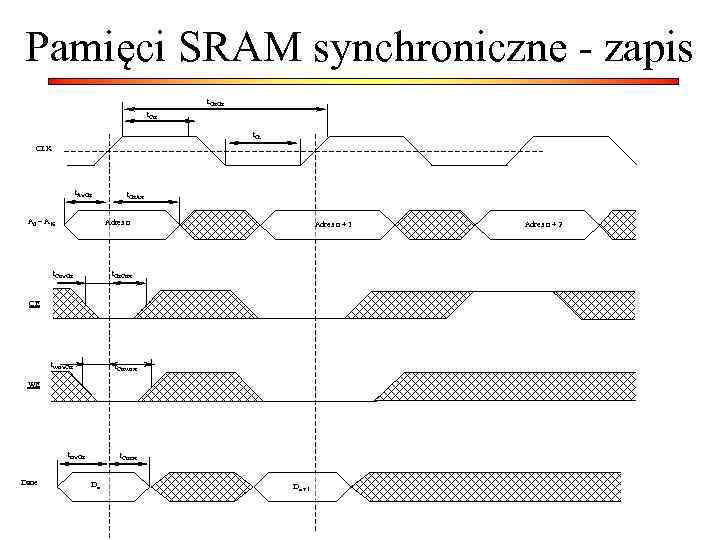

Pamięci SRAM synchroniczne - zapis t. CHCH t. CL CLK t. AVCH A 0 – A 16 t. CHAX Adres n t. CEVCH Adres n + 1 t. CHCEX CE t. WEVCH t. CHWEX WE t. DVCH Dane t. CHDX Dn Dn + 1 Adres n + 2

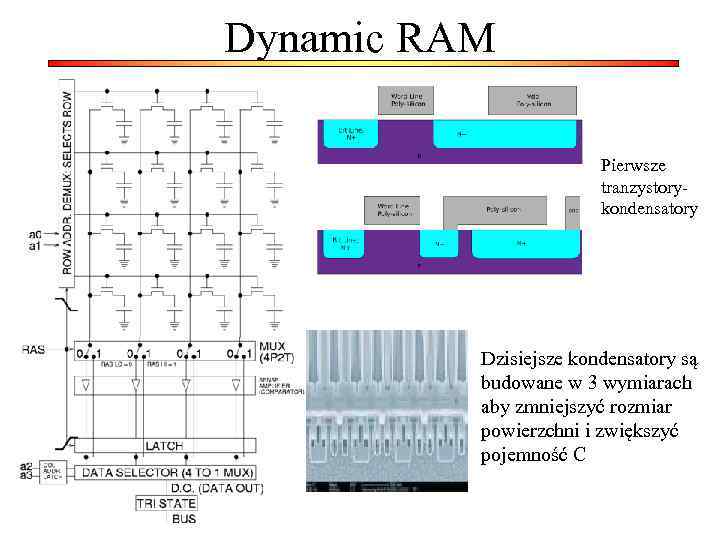

Dynamic RAM Pierwsze tranzystorykondensatory Dzisiejsze kondensatory są budowane w 3 wymiarach aby zmniejszyć rozmiar powierzchni i zwiększyć pojemność C

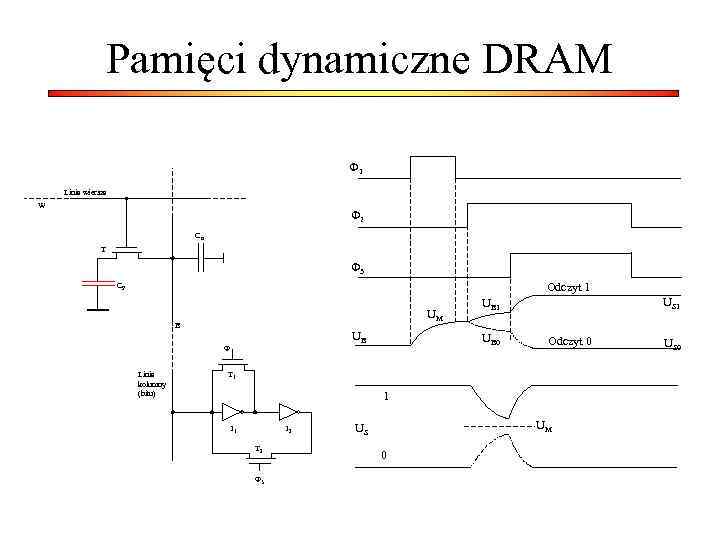

Pamięci dynamiczne DRAM Ф 1 Linia wiersza W Ф 2 CB T Ф 3 Odczyt 1 CS UM B UB Ф 1 Linia kolumny (bitu) US 1 UB 0 Odczyt 0 T 1 1 I 2 T 2 Ф 3 UM US 0

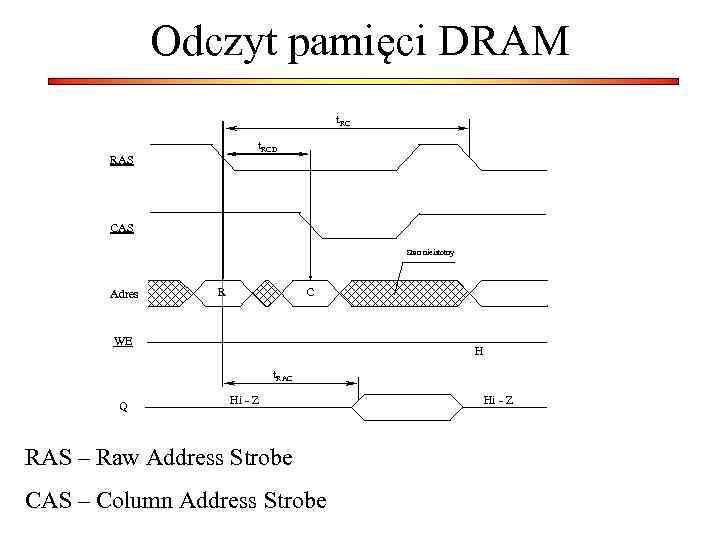

Odczyt pamięci DRAM t. RCD RAS CAS Stan nieistotny Adres R C WE H t. RAC Q Hi - Z RAS – Raw Address Strobe CAS – Column Address Strobe Hi - Z

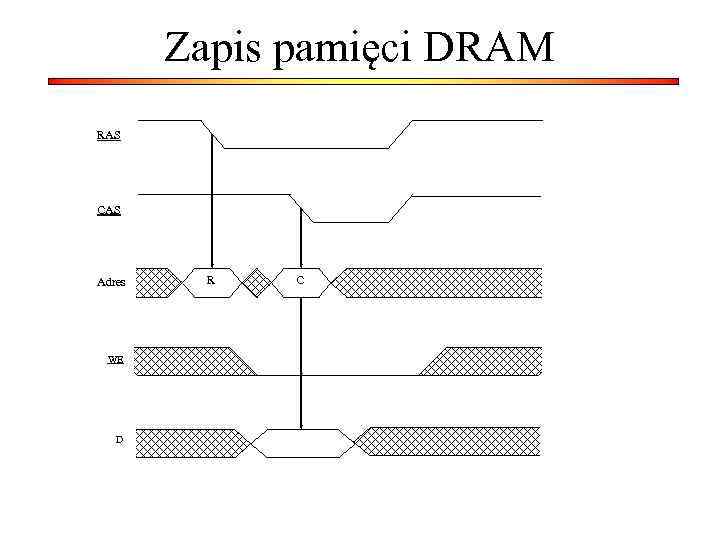

Zapis pamięci DRAM RAS CAS Adres WE D R C

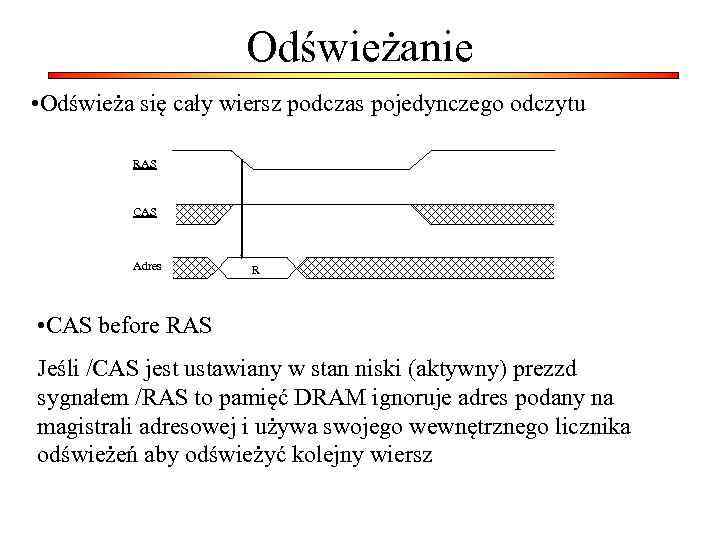

Odświeżanie • Odświeża się cały wiersz podczas pojedynczego odczytu RAS CAS Adres R • CAS before RAS Jeśli /CAS jest ustawiany w stan niski (aktywny) prezzd sygnałem /RAS to pamięć DRAM ignoruje adres podany na magistrali adresowej i używa swojego wewnętrznego licznika odświeżeń aby odświeżyć kolejny wiersz

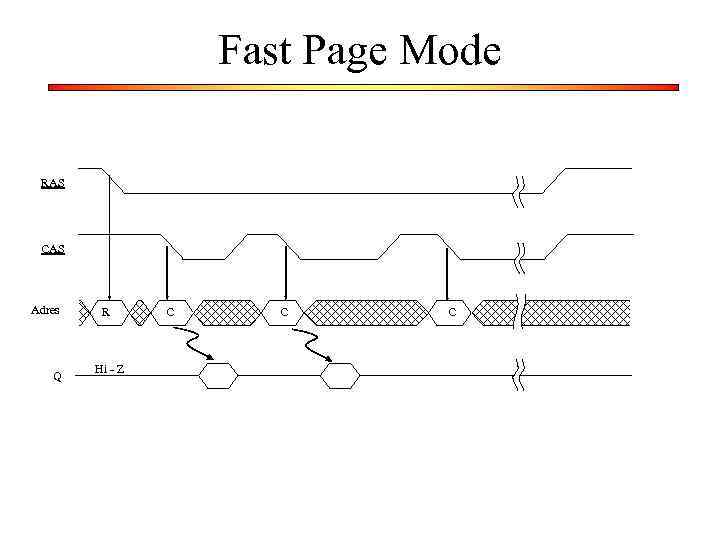

Fast Page Mode RAS CAS Adres Q R Hi - Z C C C

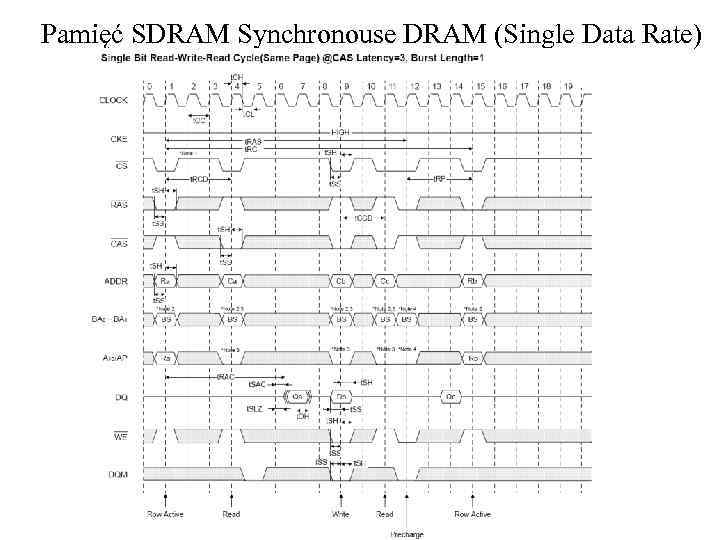

Pamięć SDRAM Synchronouse DRAM (Single Data Rate)

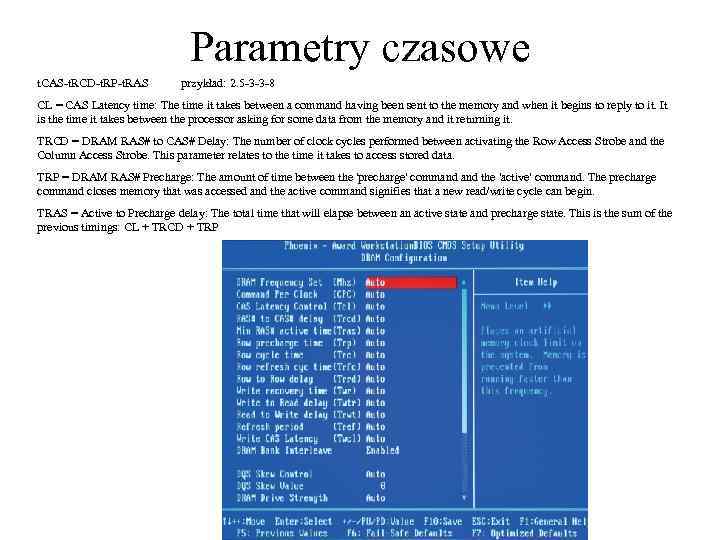

Parametry czasowe t. CAS-t. RCD-t. RP-t. RAS przykład: 2. 5 -3 -3 -8 CL = CAS Latency time: The time it takes between a command having been sent to the memory and when it begins to reply to it. It is the time it takes between the processor asking for some data from the memory and it returning it. TRCD = DRAM RAS# to CAS# Delay: The number of clock cycles performed between activating the Row Access Strobe and the Column Access Strobe. This parameter relates to the time it takes to access stored data. TRP = DRAM RAS# Precharge: The amount of time between the 'precharge' command the 'active' command. The precharge command closes memory that was accessed and the active command signifies that a new read/write cycle can begin. TRAS = Active to Precharge delay: The total time that will elapse between an active state and precharge state. This is the sum of the previous timings: CL + TRCD + TRP

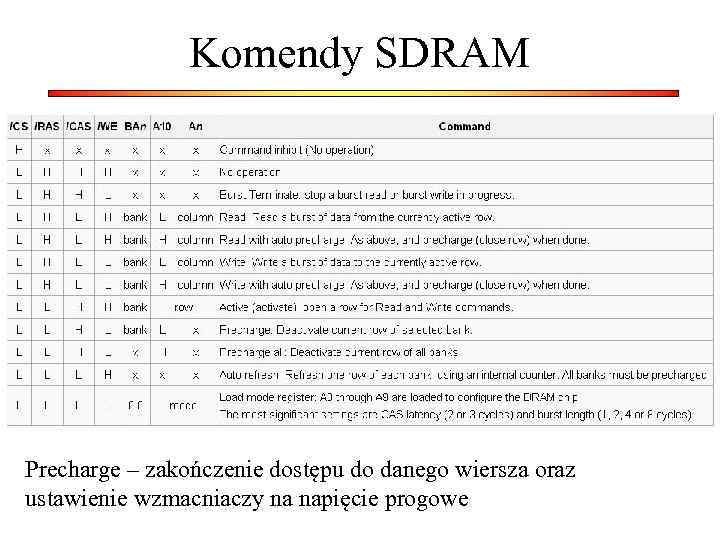

Komendy SDRAM Precharge – zakończenie dostępu do danego wiersza oraz ustawienie wzmacniaczy na napięcie progowe

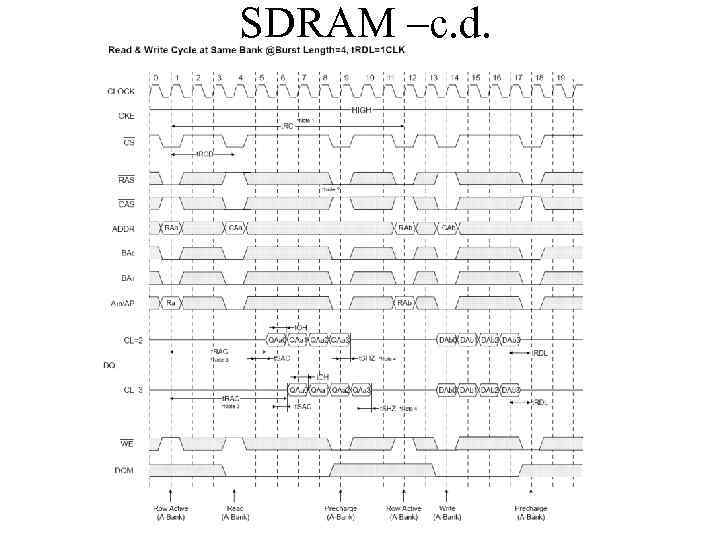

SDRAM –c. d.

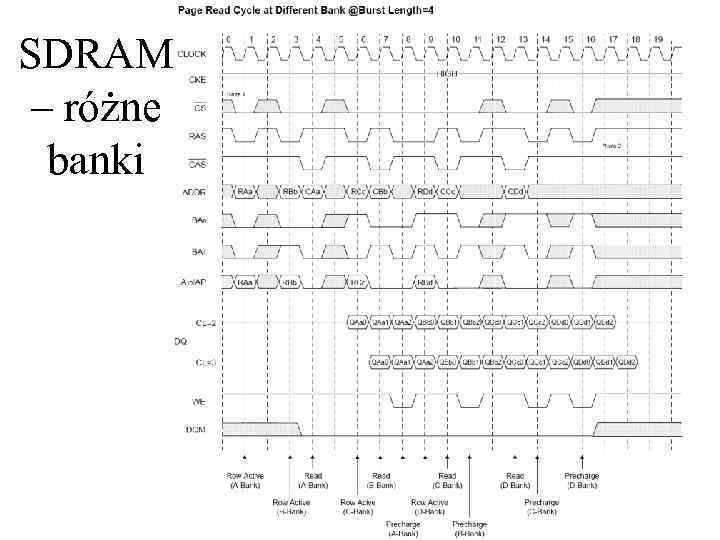

SDRAM – różne banki

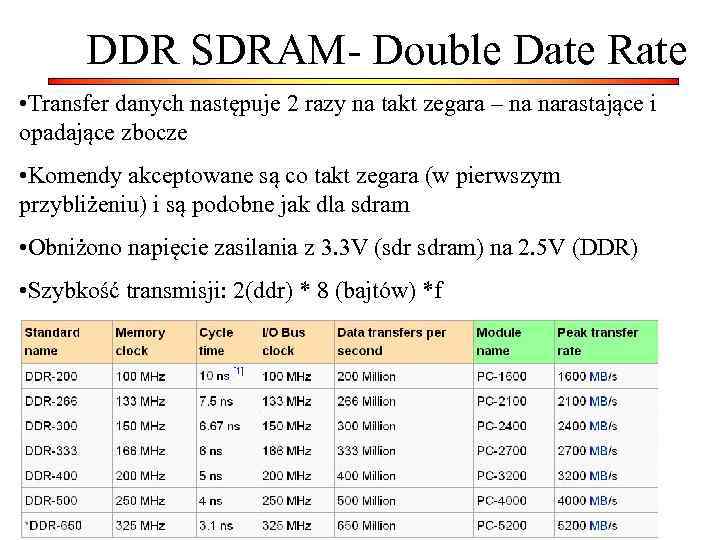

DDR SDRAM- Double Date Rate • Transfer danych następuje 2 razy na takt zegara – na narastające i opadające zbocze • Komendy akceptowane są co takt zegara (w pierwszym przybliżeniu) i są podobne jak dla sdram • Obniżono napięcie zasilania z 3. 3 V (sdr sdram) na 2. 5 V (DDR) • Szybkość transmisji: 2(ddr) * 8 (bajtów) *f

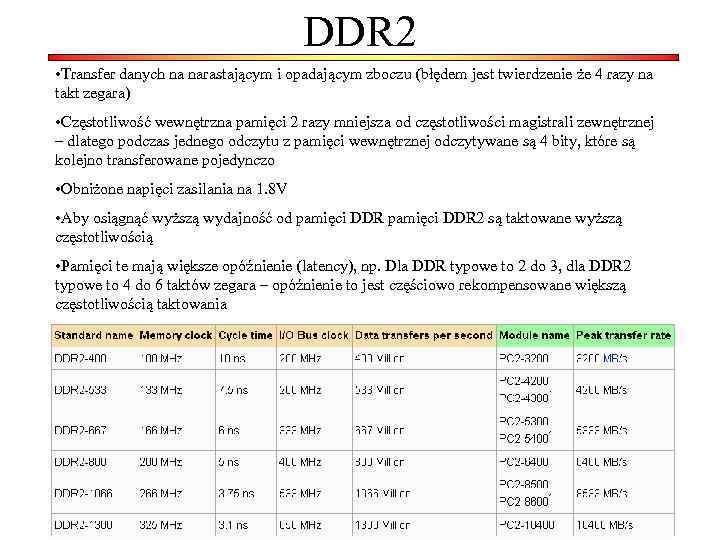

DDR 2 • Transfer danych na narastającym i opadającym zboczu (błędem jest twierdzenie że 4 razy na takt zegara) • Częstotliwość wewnętrzna pamięci 2 razy mniejsza od częstotliwości magistrali zewnętrznej – dlatego podczas jednego odczytu z pamięci wewnętrznej odczytywane są 4 bity, które są kolejno transferowane pojedynczo • Obniżone napięci zasilania na 1. 8 V • Aby osiągnąć wyższą wydajność od pamięci DDR 2 są taktowane wyższą częstotliwością • Pamięci te mają większe opóźnienie (latency), np. Dla DDR typowe to 2 do 3, dla DDR 2 typowe to 4 do 6 taktów zegara – opóźnienie to jest częściowo rekompensowane większą częstotliwością taktowania

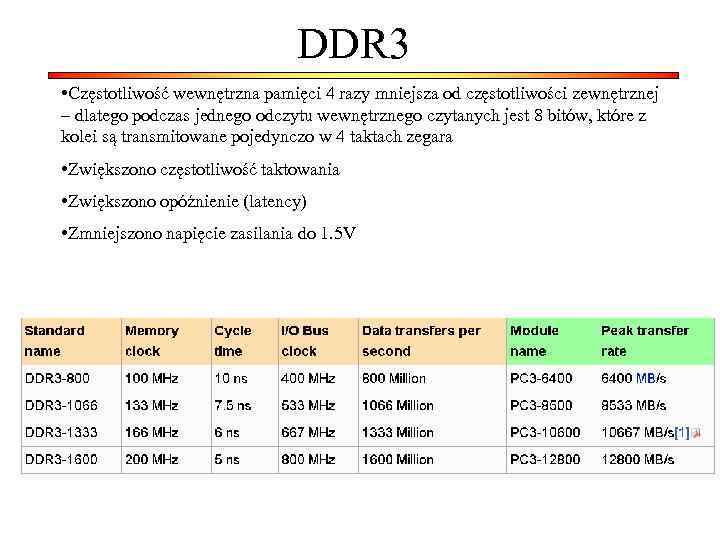

DDR 3 • Częstotliwość wewnętrzna pamięci 4 razy mniejsza od częstotliwości zewnętrznej – dlatego podczas jednego odczytu wewnętrznego czytanych jest 8 bitów, które z kolei są transmitowane pojedynczo w 4 taktach zegara • Zwiększono częstotliwość taktowania • Zwiększono opóźnienie (latency) • Zmniejszono napięcie zasilania do 1. 5 V

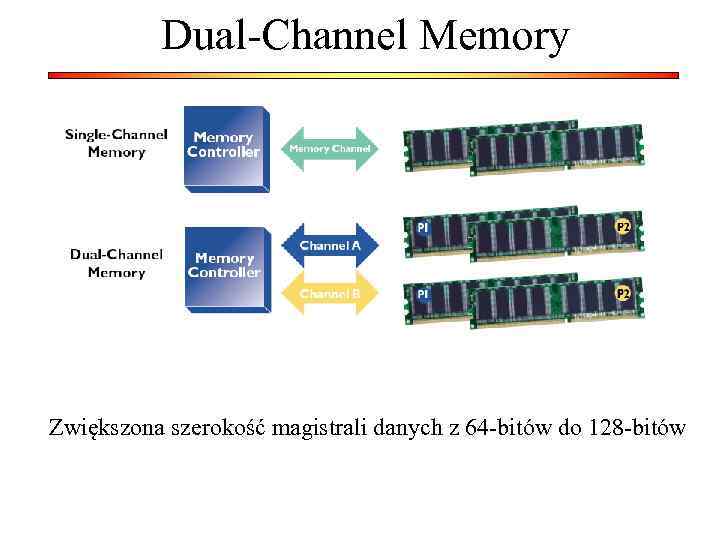

Dual-Channel Memory Zwiększona szerokość magistrali danych z 64 -bitów do 128 -bitów

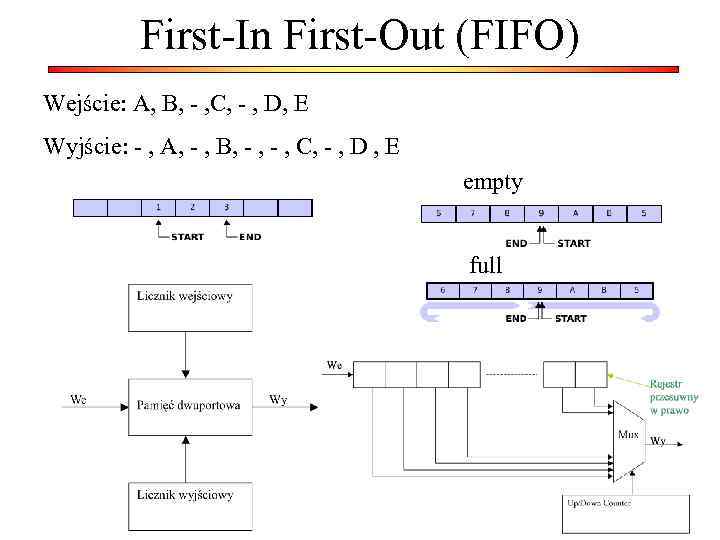

First-In First-Out (FIFO) Wejście: A, B, - , C, - , D, E Wyjście: - , A, - , B, - , C, - , D , E empty full

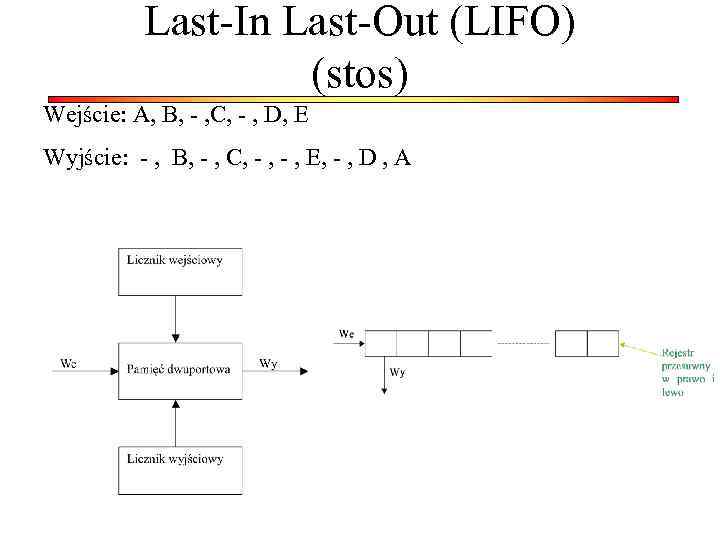

Last-In Last-Out (LIFO) (stos) Wejście: A, B, - , C, - , D, E Wyjście: - , B, - , C, - , E, - , D , A

Content-addressable memory (CAM) Podajemy wartość danej a pamięć CAM zwraca adres (lub adresy) pod którymi znajduje się podane dana W konsekwencji należy przeszukać całą pamięć aby otrzymać adres pod którym znajduje się podana

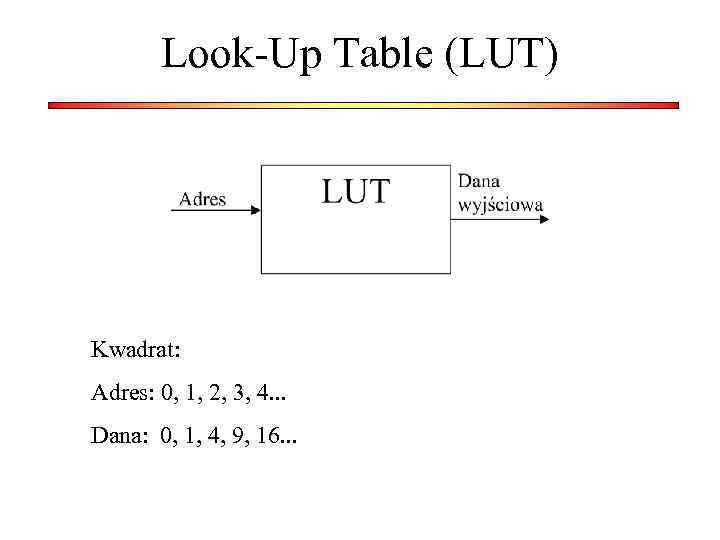

Look-Up Table (LUT) Kwadrat: Adres: 0, 1, 2, 3, 4. . . Dana: 0, 1, 4, 9, 16. . .

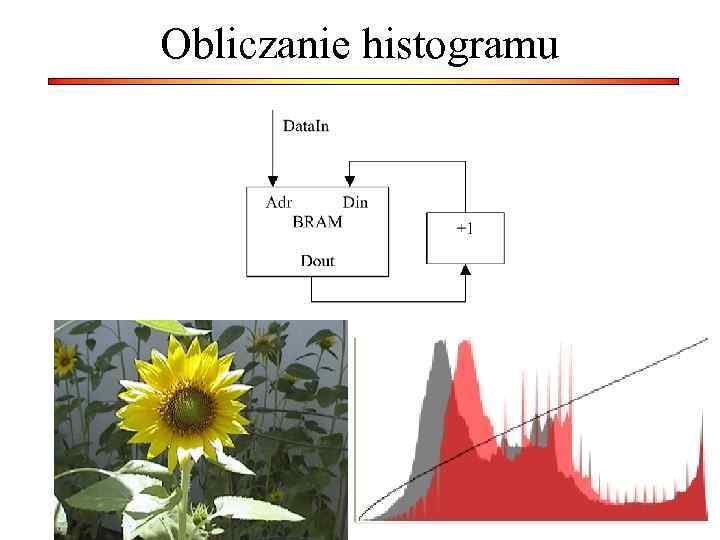

Obliczanie histogramu