f611dec0abdfffab51c40d9530fbd76e.ppt

- Количество слайдов: 28

P-ILC Stato delle cose v caratterizzazione del prototipo in 130 nm (Pv, Mi) Sblocco s. j. 50 + 3 k. EUR (produzione chip + scheda digital I/O V 1495 CAEN) v EUDET (Fe, Mi) v attivita’ sui Si. PM (Roma I & LNF) v Attivita’ a Lecce v programma 2009 Massimo Caccia Riunione CSN 1 Ferrara, 19 Maggio 2008

P-ILC Stato delle cose v caratterizzazione del prototipo in 130 nm (Pv, Mi) Sblocco s. j. 50 + 3 k. EUR (produzione chip + scheda digital I/O V 1495 CAEN) v EUDET (Fe, Mi) v attivita’ sui Si. PM (Roma I & LNF) v Attivita’ a Lecce v programma 2009 Massimo Caccia Riunione CSN 1 Ferrara, 19 Maggio 2008

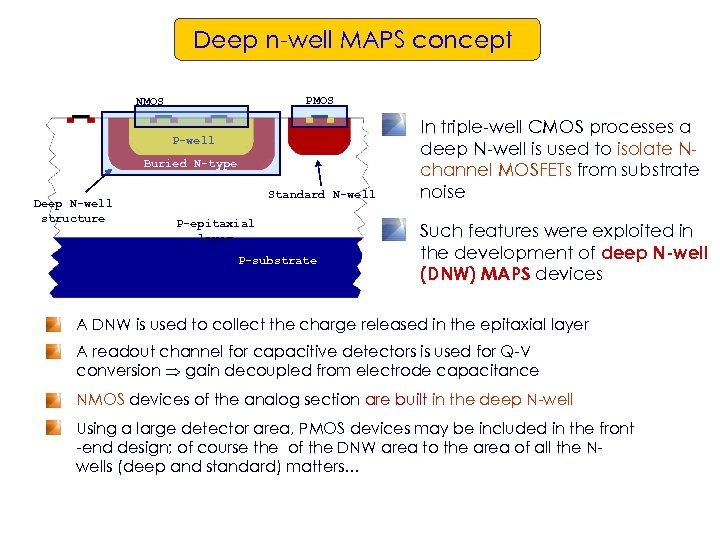

Deep n-well MAPS concept PMOS NMOS P-well Buried N-type layer Deep N-well structure Standard N-well P-epitaxial layer P-substrate In triple-well CMOS processes a deep N-well is used to isolate Nchannel MOSFETs from substrate noise Such features were exploited in the development of deep N-well (DNW) MAPS devices A DNW is used to collect the charge released in the epitaxial layer A readout channel for capacitive detectors is used for Q-V conversion gain decoupled from electrode capacitance NMOS devices of the analog section are built in the deep N-well Using a large detector area, PMOS devices may be included in the front -end design; of course the of the DNW area to the area of all the Nwells (deep and standard) matters…

Deep n-well MAPS concept PMOS NMOS P-well Buried N-type layer Deep N-well structure Standard N-well P-epitaxial layer P-substrate In triple-well CMOS processes a deep N-well is used to isolate Nchannel MOSFETs from substrate noise Such features were exploited in the development of deep N-well (DNW) MAPS devices A DNW is used to collect the charge released in the epitaxial layer A readout channel for capacitive detectors is used for Q-V conversion gain decoupled from electrode capacitance NMOS devices of the analog section are built in the deep N-well Using a large detector area, PMOS devices may be included in the front -end design; of course the of the DNW area to the area of all the Nwells (deep and standard) matters…

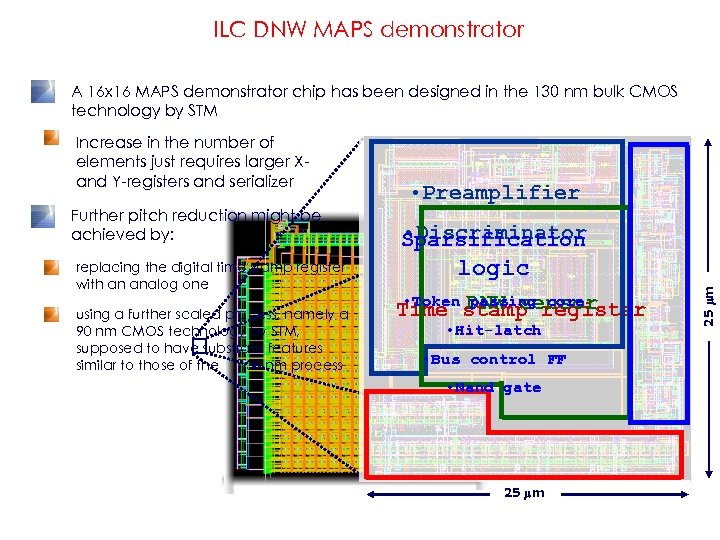

ILC DNW MAPS demonstrator A 16 x 16 MAPS demonstrator chip has been designed in the 130 nm bulk CMOS technology by STM Further pitch reduction might be achieved by: replacing the digital time stamp register with an analog one using a further scaled process, namely a 90 nm CMOS technology by STM, supposed to have substrate features similar to those of the 130 nm process • Preamplifier • Discriminator Sparsification logic • Token DNW sensor passing core Time stamp register • Hit-latch • Bus control FF • Nand gate 25 mm Increase in the number of elements just requires larger Xand Y-registers and serializer

ILC DNW MAPS demonstrator A 16 x 16 MAPS demonstrator chip has been designed in the 130 nm bulk CMOS technology by STM Further pitch reduction might be achieved by: replacing the digital time stamp register with an analog one using a further scaled process, namely a 90 nm CMOS technology by STM, supposed to have substrate features similar to those of the 130 nm process • Preamplifier • Discriminator Sparsification logic • Token DNW sensor passing core Time stamp register • Hit-latch • Bus control FF • Nand gate 25 mm Increase in the number of elements just requires larger Xand Y-registers and serializer

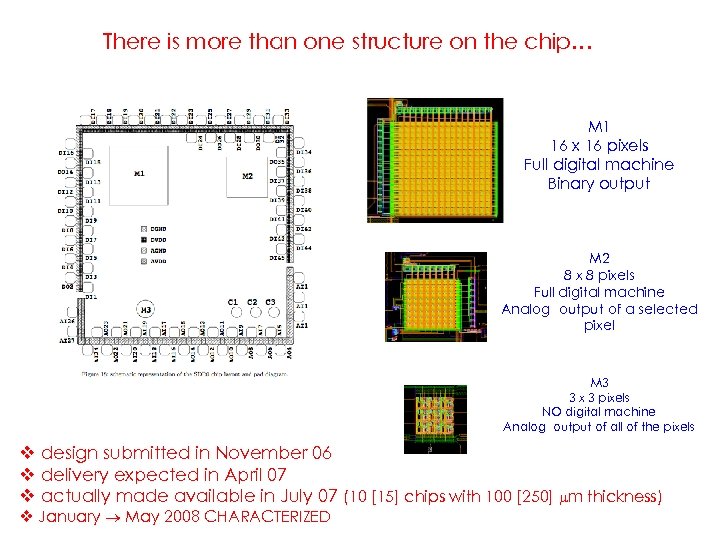

There is more than one structure on the chip… M 1 16 x 16 pixels Full digital machine Binary output M 2 8 x 8 pixels Full digital machine Analog output of a selected pixel M 3 3 x 3 pixels NO digital machine Analog output of all of the pixels v design submitted in November 06 v delivery expected in April 07 v actually made available in July 07 (10 [15] chips with 100 [250] m thickness) v January May 2008 CHARACTERIZED

There is more than one structure on the chip… M 1 16 x 16 pixels Full digital machine Binary output M 2 8 x 8 pixels Full digital machine Analog output of a selected pixel M 3 3 x 3 pixels NO digital machine Analog output of all of the pixels v design submitted in November 06 v delivery expected in April 07 v actually made available in July 07 (10 [15] chips with 100 [250] m thickness) v January May 2008 CHARACTERIZED

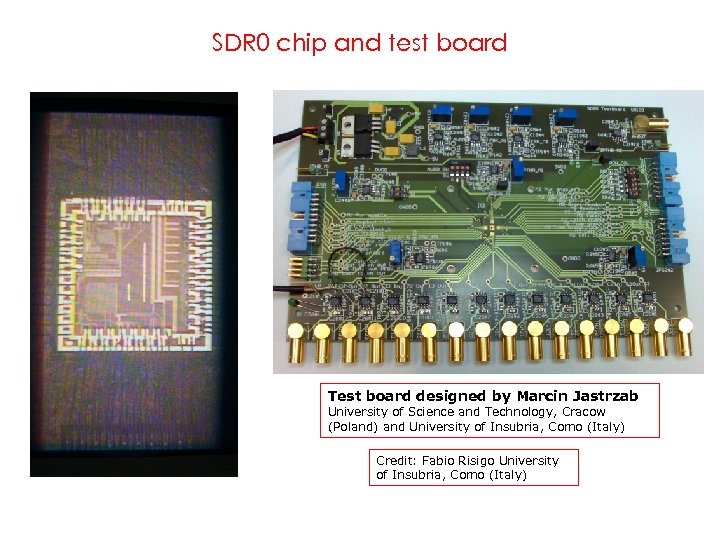

SDR 0 chip and test board Test board designed by Marcin Jastrzab University of Science and Technology, Cracow (Poland) and University of Insubria, Como (Italy) Credit: Fabio Risigo University of Insubria, Como (Italy)

SDR 0 chip and test board Test board designed by Marcin Jastrzab University of Science and Technology, Cracow (Poland) and University of Insubria, Como (Italy) Credit: Fabio Risigo University of Insubria, Como (Italy)

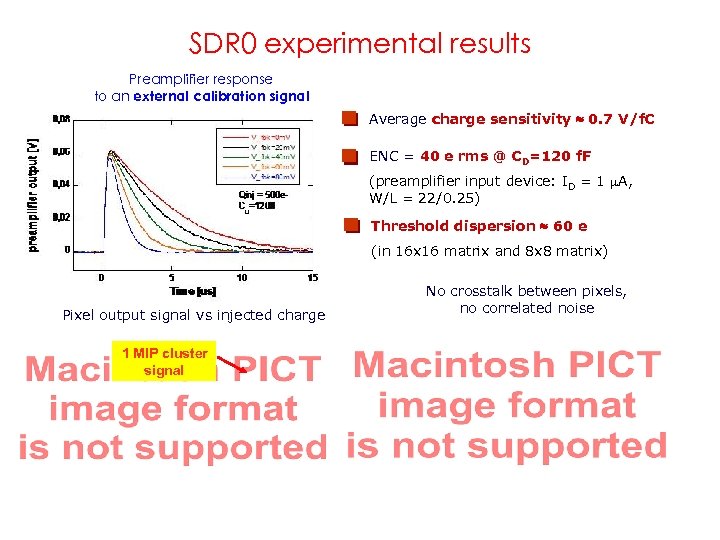

SDR 0 experimental results Preamplifier response to an external calibration signal Average charge sensitivity 0. 7 V/f. C ENC = 40 e rms @ CD=120 f. F (preamplifier input device: ID = 1 A, W/L = 22/0. 25) Threshold dispersion 60 e (in 16 x 16 matrix and 8 x 8 matrix) Pixel output signal vs injected charge 1 MIP cluster signal No crosstalk between pixels, no correlated noise

SDR 0 experimental results Preamplifier response to an external calibration signal Average charge sensitivity 0. 7 V/f. C ENC = 40 e rms @ CD=120 f. F (preamplifier input device: ID = 1 A, W/L = 22/0. 25) Threshold dispersion 60 e (in 16 x 16 matrix and 8 x 8 matrix) Pixel output signal vs injected charge 1 MIP cluster signal No crosstalk between pixels, no correlated noise

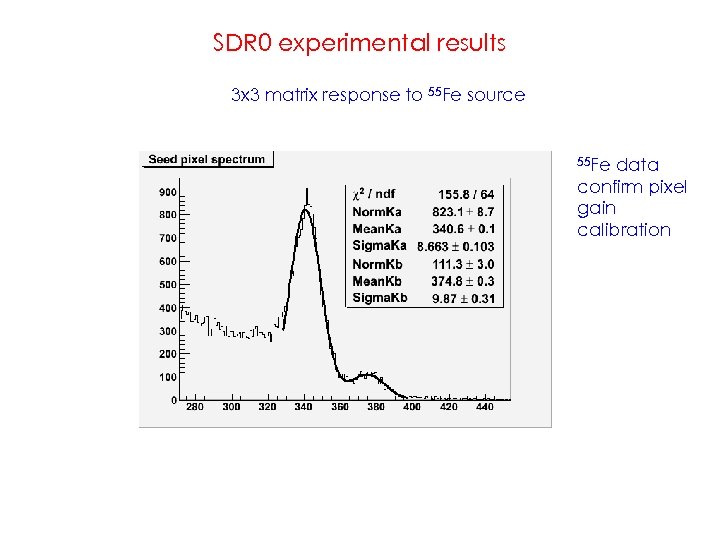

SDR 0 experimental results 3 x 3 matrix response to 55 Fe source 55 Fe data confirm pixel gain calibration

SDR 0 experimental results 3 x 3 matrix response to 55 Fe source 55 Fe data confirm pixel gain calibration

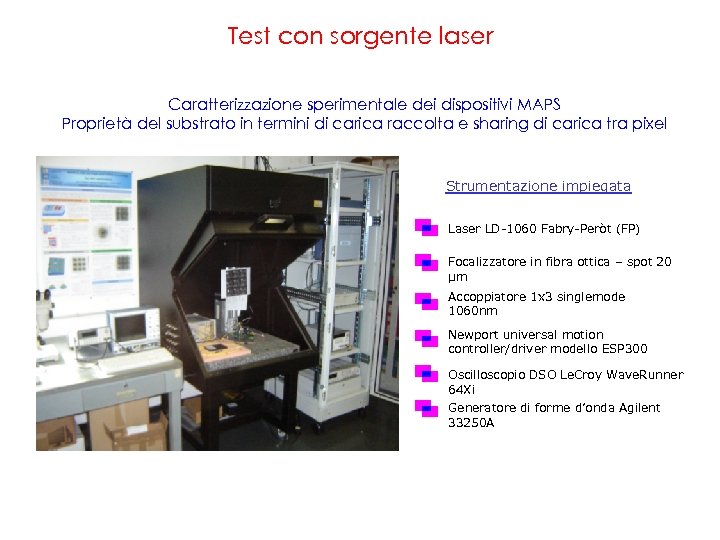

Test con sorgente laser Caratterizzazione sperimentale dei dispositivi MAPS Proprietà del substrato in termini di carica raccolta e sharing di carica tra pixel Strumentazione impiegata Laser LD-1060 Fabry-Peròt (FP) Focalizzatore in fibra ottica – spot 20 µm Accoppiatore 1 x 3 singlemode 1060 nm Newport universal motion controller/driver modello ESP 300 Oscilloscopio DSO Le. Croy Wave. Runner 64 Xi Generatore di forme d’onda Agilent 33250 A

Test con sorgente laser Caratterizzazione sperimentale dei dispositivi MAPS Proprietà del substrato in termini di carica raccolta e sharing di carica tra pixel Strumentazione impiegata Laser LD-1060 Fabry-Peròt (FP) Focalizzatore in fibra ottica – spot 20 µm Accoppiatore 1 x 3 singlemode 1060 nm Newport universal motion controller/driver modello ESP 300 Oscilloscopio DSO Le. Croy Wave. Runner 64 Xi Generatore di forme d’onda Agilent 33250 A

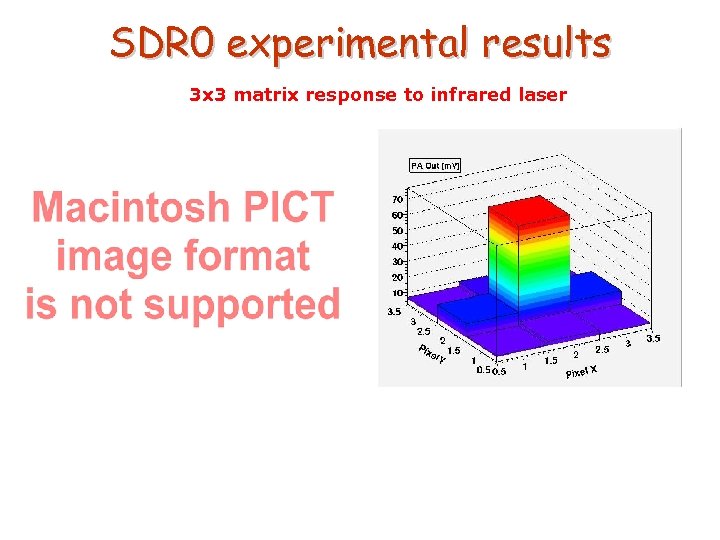

SDR 0 experimental results 3 x 3 matrix response to infrared laser

SDR 0 experimental results 3 x 3 matrix response to infrared laser

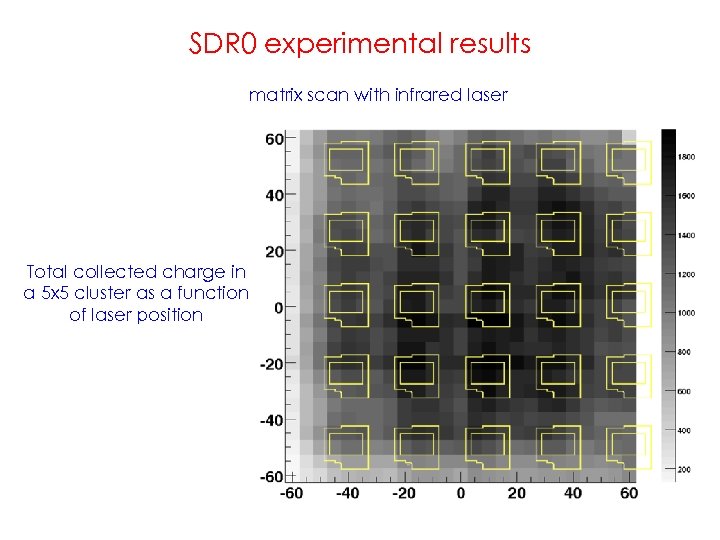

SDR 0 experimental results matrix scan with infrared laser Total collected charge in a 5 x 5 cluster as a function of laser position

SDR 0 experimental results matrix scan with infrared laser Total collected charge in a 5 x 5 cluster as a function of laser position

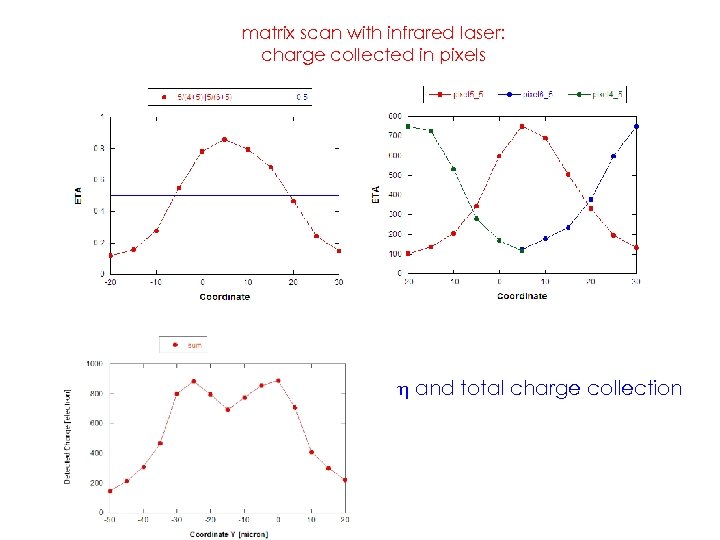

matrix scan with infrared laser: charge collected in pixels h and total charge collection

matrix scan with infrared laser: charge collected in pixels h and total charge collection

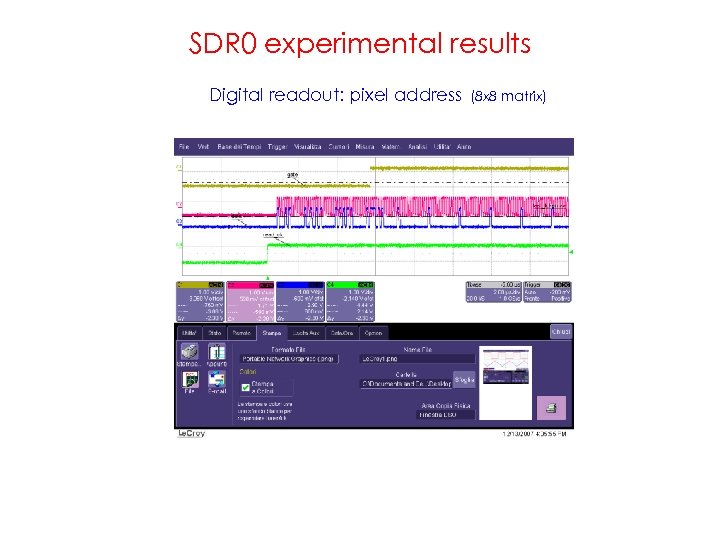

SDR 0 experimental results Digital readout: pixel address (8 x 8 matrix)

SDR 0 experimental results Digital readout: pixel address (8 x 8 matrix)

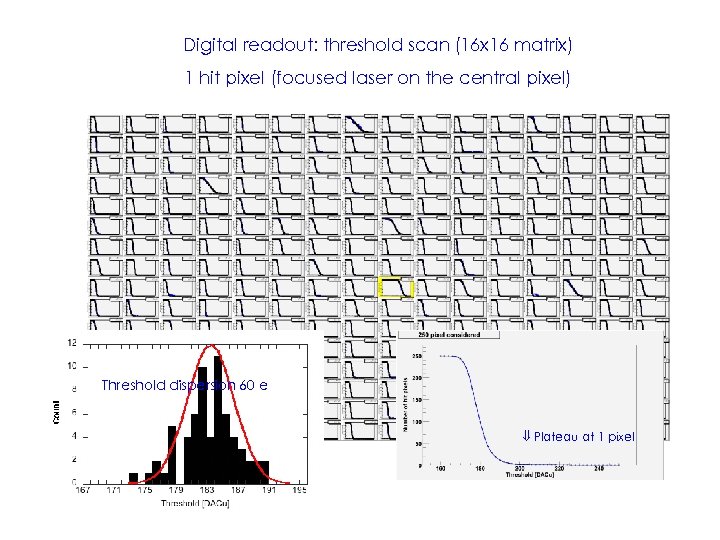

Digital readout: threshold scan (16 x 16 matrix) 1 hit pixel (focused laser on the central pixel) Threshold dispersion 60 e Plateau at 1 pixel

Digital readout: threshold scan (16 x 16 matrix) 1 hit pixel (focused laser on the central pixel) Threshold dispersion 60 e Plateau at 1 pixel

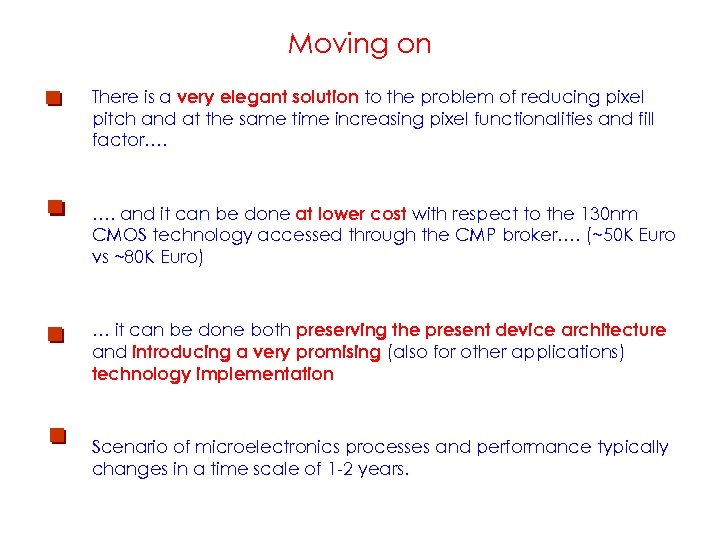

Moving on There is a very elegant solution to the problem of reducing pixel pitch and at the same time increasing pixel functionalities and fill factor…. …. and it can be done at lower cost with respect to the 130 nm CMOS technology accessed through the CMP broker…. (~50 K Euro vs ~80 K Euro) … it can be done both preserving the present device architecture and introducing a very promising (also for other applications) technology implementation Scenario of microelectronics processes and performance typically changes in a time scale of 1 -2 years.

Moving on There is a very elegant solution to the problem of reducing pixel pitch and at the same time increasing pixel functionalities and fill factor…. …. and it can be done at lower cost with respect to the 130 nm CMOS technology accessed through the CMP broker…. (~50 K Euro vs ~80 K Euro) … it can be done both preserving the present device architecture and introducing a very promising (also for other applications) technology implementation Scenario of microelectronics processes and performance typically changes in a time scale of 1 -2 years.

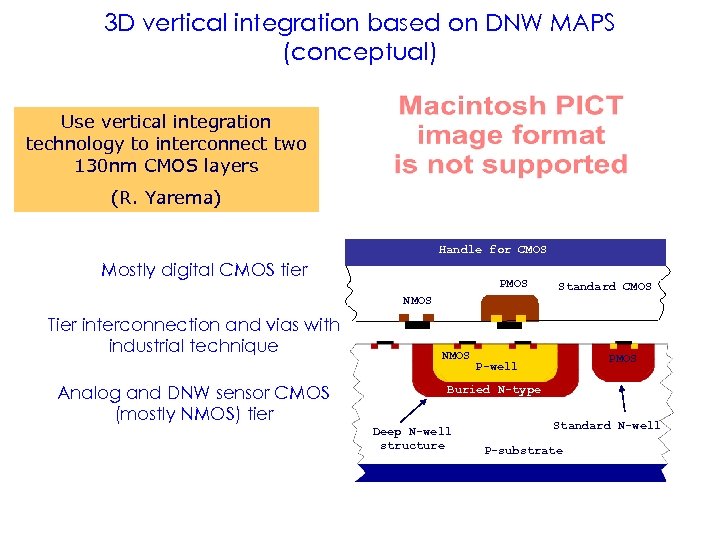

3 D vertical integration based on DNW MAPS (conceptual) Use vertical integration technology to interconnect two 130 nm CMOS layers (R. Yarema) Handle for CMOS Mostly digital CMOS tier PMOS Standard CMOS NMOS Tier interconnection and vias with industrial technique Analog and DNW sensor CMOS (mostly NMOS) tier NMOS P-well Buried N-type layer Deep N-well structure Standard N-well P-substrate

3 D vertical integration based on DNW MAPS (conceptual) Use vertical integration technology to interconnect two 130 nm CMOS layers (R. Yarema) Handle for CMOS Mostly digital CMOS tier PMOS Standard CMOS NMOS Tier interconnection and vias with industrial technique Analog and DNW sensor CMOS (mostly NMOS) tier NMOS P-well Buried N-type layer Deep N-well structure Standard N-well P-substrate

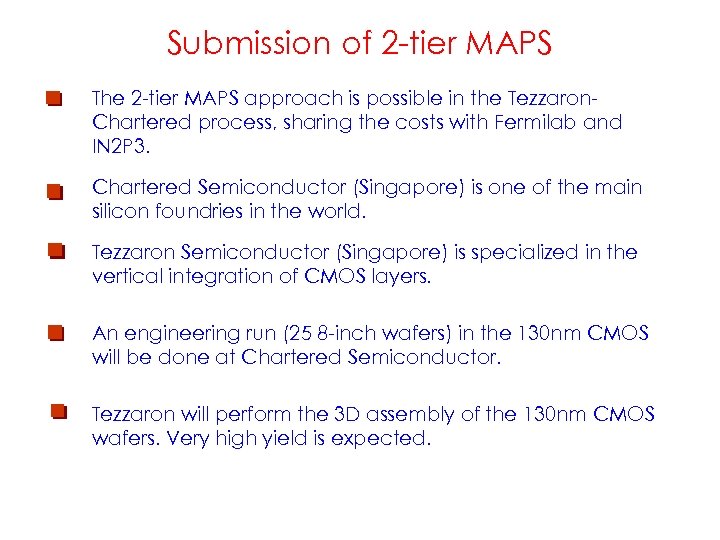

Submission of 2 -tier MAPS The 2 -tier MAPS approach is possible in the Tezzaron. Chartered process, sharing the costs with Fermilab and IN 2 P 3. Chartered Semiconductor (Singapore) is one of the main silicon foundries in the world. Tezzaron Semiconductor (Singapore) is specialized in the vertical integration of CMOS layers. An engineering run (25 8 -inch wafers) in the 130 nm CMOS will be done at Chartered Semiconductor. Tezzaron will perform the 3 D assembly of the 130 nm CMOS wafers. Very high yield is expected.

Submission of 2 -tier MAPS The 2 -tier MAPS approach is possible in the Tezzaron. Chartered process, sharing the costs with Fermilab and IN 2 P 3. Chartered Semiconductor (Singapore) is one of the main silicon foundries in the world. Tezzaron Semiconductor (Singapore) is specialized in the vertical integration of CMOS layers. An engineering run (25 8 -inch wafers) in the 130 nm CMOS will be done at Chartered Semiconductor. Tezzaron will perform the 3 D assembly of the 130 nm CMOS wafers. Very high yield is expected.

3 D Multi-Project Run • We have been invited by Fermilab (Ray Yarema) to join a 3 D multi project run using Tezzaron-Chartered. • The run is scheduled in December ’ 08 – (not later than) January ‘ 09 • There will be only 2 layers of electronics fabricated in the Chartered 130 nm process, using only one set of masks. This process has a very similar resistivity as the 130 nm STMicroelectronics process. It is very reasonable to expect very similar charge collection properties. • The wafers will be bonded face to face by Tezzaron. Face to Face Bonding

3 D Multi-Project Run • We have been invited by Fermilab (Ray Yarema) to join a 3 D multi project run using Tezzaron-Chartered. • The run is scheduled in December ’ 08 – (not later than) January ‘ 09 • There will be only 2 layers of electronics fabricated in the Chartered 130 nm process, using only one set of masks. This process has a very similar resistivity as the 130 nm STMicroelectronics process. It is very reasonable to expect very similar charge collection properties. • The wafers will be bonded face to face by Tezzaron. Face to Face Bonding

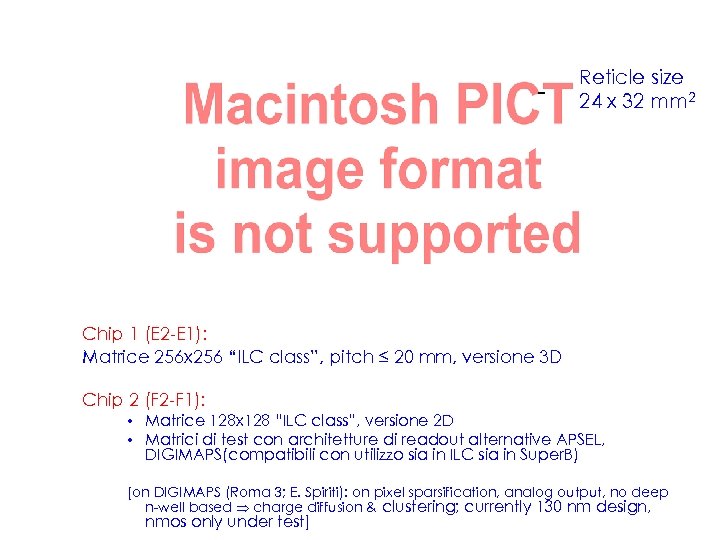

Reticle size 24 x 32 mm 2 Chip 1 (E 2 -E 1): Matrice 256 x 256 “ILC class”, pitch ≤ 20 mm, versione 3 D Chip 2 (F 2 -F 1): • Matrice 128 x 128 “ILC class”, versione 2 D • Matrici di test con architetture di readout alternative APSEL, DIGIMAPS(compatibili con utilizzo sia in ILC sia in Super. B) [on DIGIMAPS (Roma 3; E. Spiriti): on pixel sparsification, analog output, no deep n-well based charge diffusion & clustering; currently 130 nm design, nmos only under test]

Reticle size 24 x 32 mm 2 Chip 1 (E 2 -E 1): Matrice 256 x 256 “ILC class”, pitch ≤ 20 mm, versione 3 D Chip 2 (F 2 -F 1): • Matrice 128 x 128 “ILC class”, versione 2 D • Matrici di test con architetture di readout alternative APSEL, DIGIMAPS(compatibili con utilizzo sia in ILC sia in Super. B) [on DIGIMAPS (Roma 3; E. Spiriti): on pixel sparsification, analog output, no deep n-well based charge diffusion & clustering; currently 130 nm design, nmos only under test]

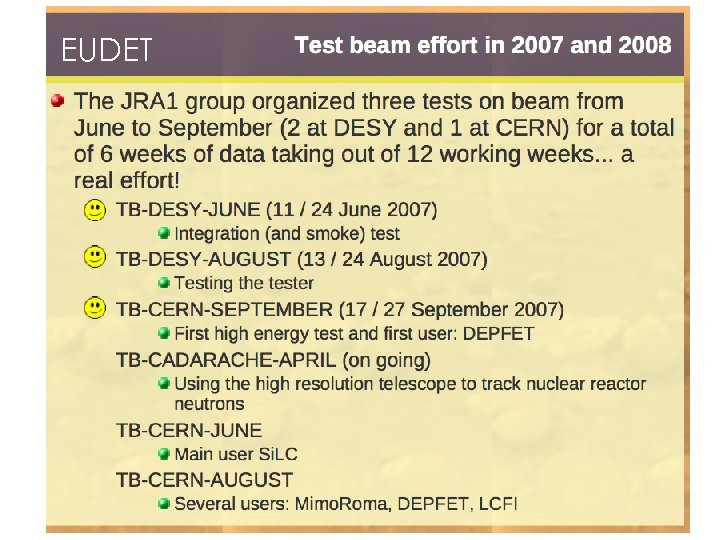

EUDET

EUDET

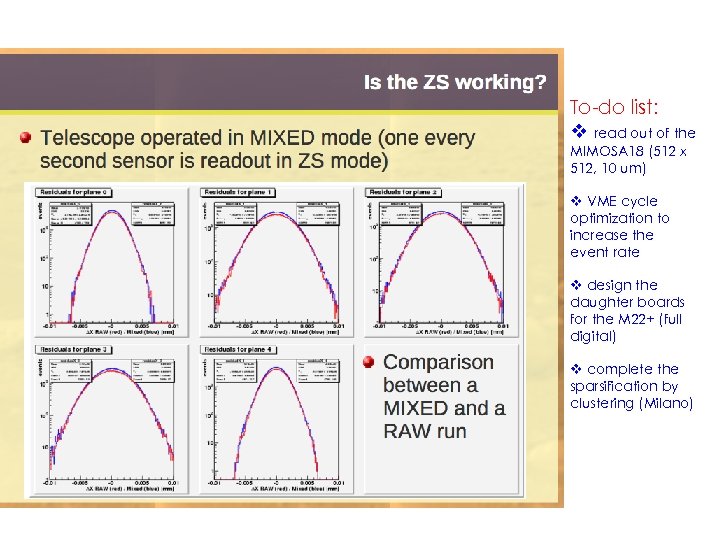

To-do list: v read out of the MIMOSA 18 (512 x 512, 10 um) v VME cycle optimization to increase the event rate v design the daughter boards for the M 22+ (full digital) v complete the sparsification by clustering (Milano)

To-do list: v read out of the MIMOSA 18 (512 x 512, 10 um) v VME cycle optimization to increase the event rate v design the daughter boards for the M 22+ (full digital) v complete the sparsification by clustering (Milano)

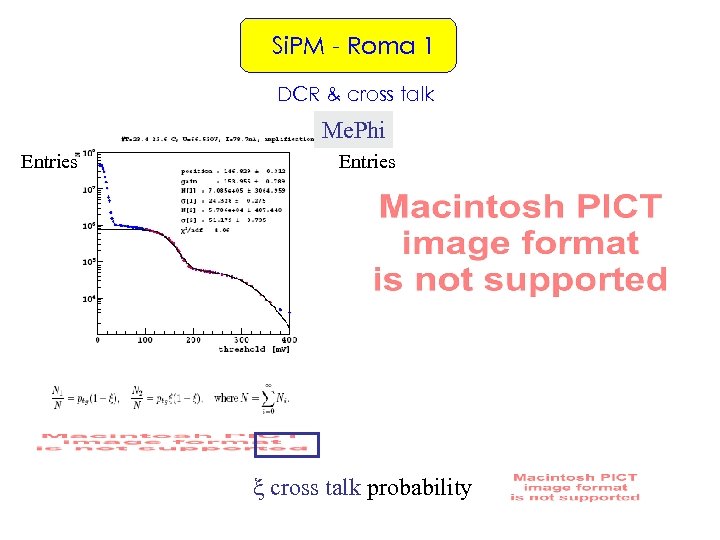

Si. PM - Roma 1 DCR & cross talk Me. Phi Entries ξ cross talk probability

Si. PM - Roma 1 DCR & cross talk Me. Phi Entries ξ cross talk probability

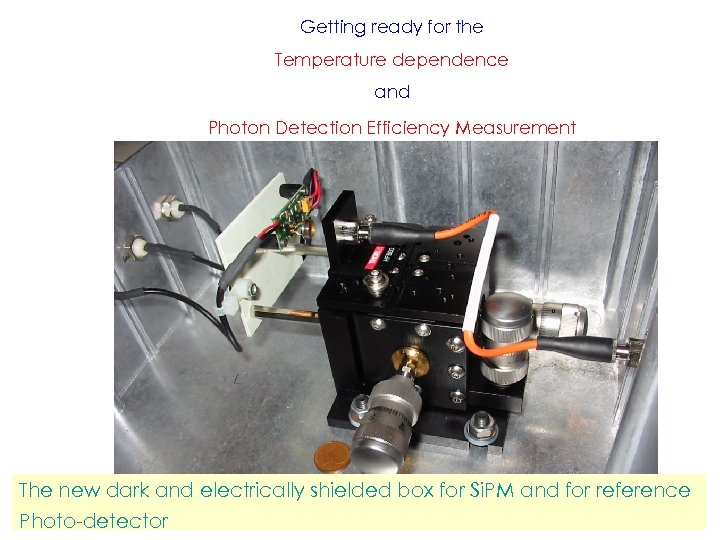

Getting ready for the Temperature dependence and Photon Detection Efficiency Measurement The new dark and electrically shielded box for Si. PM and for reference Photo-detector

Getting ready for the Temperature dependence and Photon Detection Efficiency Measurement The new dark and electrically shielded box for Si. PM and for reference Photo-detector

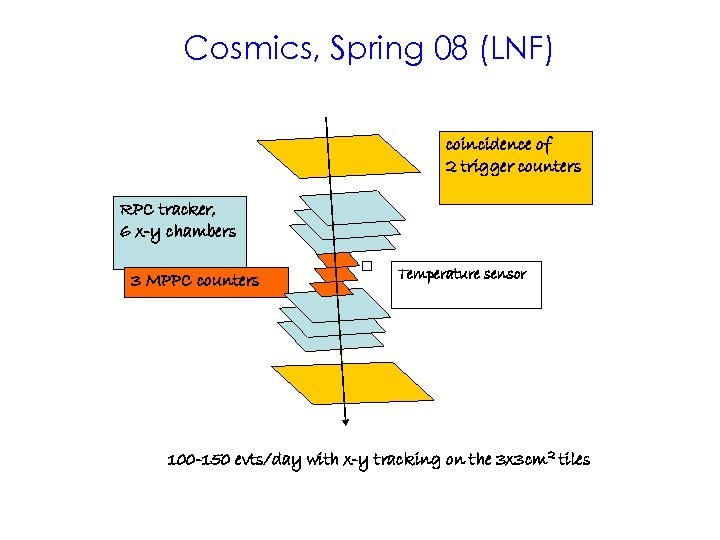

Cosmics, Spring 08 (LNF) coincidence of 2 trigger counters RPC tracker, 6 x-y chambers 3 MPPC counters Temperature sensor 100 -150 evts/day with x-y tracking on the 3 x 3 cm 2 tiles

Cosmics, Spring 08 (LNF) coincidence of 2 trigger counters RPC tracker, 6 x-y chambers 3 MPPC counters Temperature sensor 100 -150 evts/day with x-y tracking on the 3 x 3 cm 2 tiles

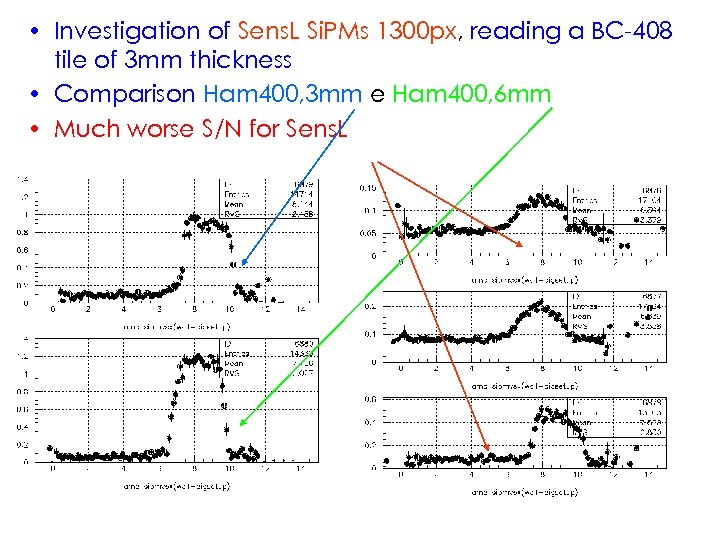

• Investigation of Sens. L Si. PMs 1300 px, reading a BC-408 tile of 3 mm thickness • Comparison Ham 400, 3 mm e Ham 400, 6 mm • Much worse S/N for Sens. L

• Investigation of Sens. L Si. PMs 1300 px, reading a BC-408 tile of 3 mm thickness • Comparison Ham 400, 3 mm e Ham 400, 6 mm • Much worse S/N for Sens. L

Next steps • Cosmic data taking ongoing • BTF test in June • Complete program by Dec. 2008

Next steps • Cosmic data taking ongoing • BTF test in June • Complete program by Dec. 2008

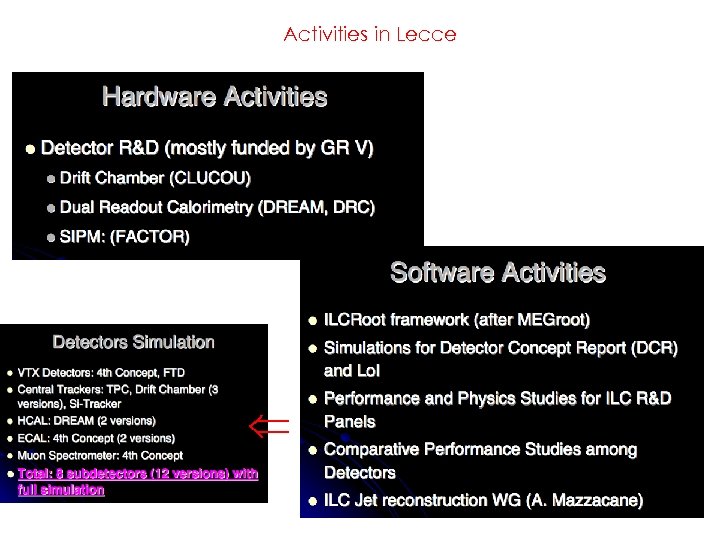

Activities in Lecce

Activities in Lecce