ОЗУ динамического типа DRAM

ОЗУ динамического типа DRAM

• Рассмотрим порядок адресации ячеек, количество адресных входов в два раза меньше чем разрядность адреса.

• Рассмотрим порядок адресации ячеек, количество адресных входов в два раза меньше чем разрядность адреса.

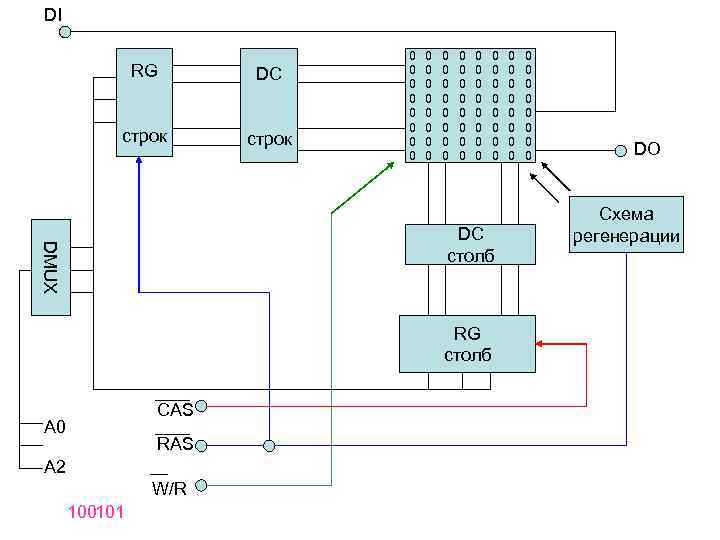

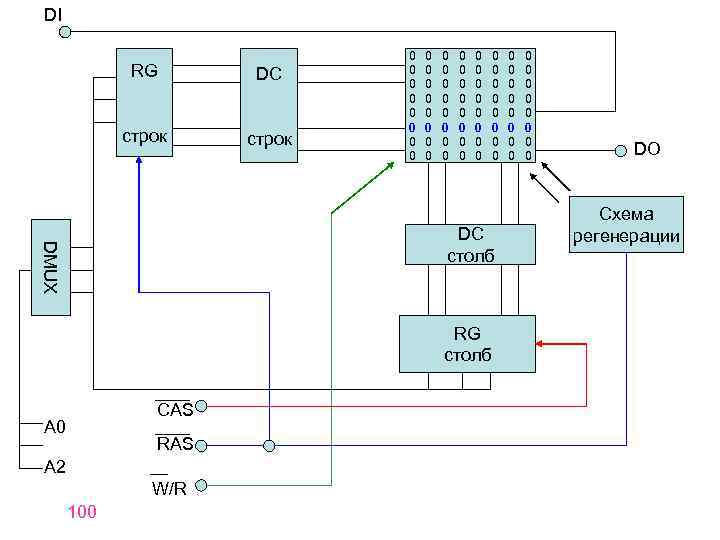

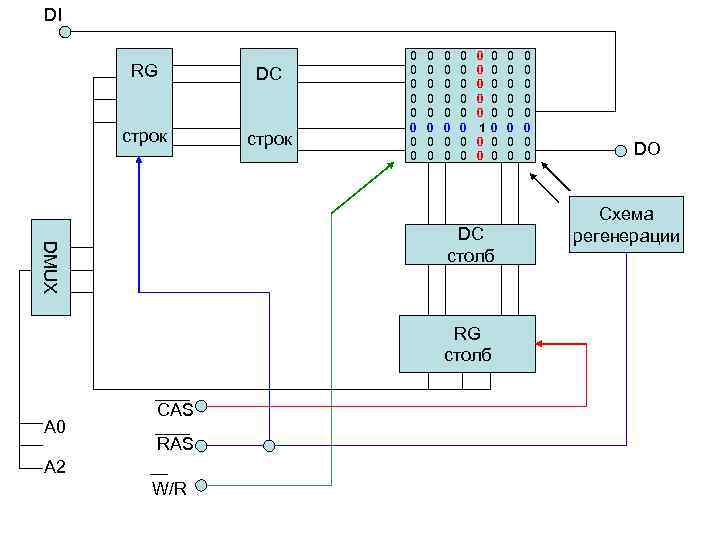

Предположим, что адрес ячейки 100101

Предположим, что адрес ячейки 100101

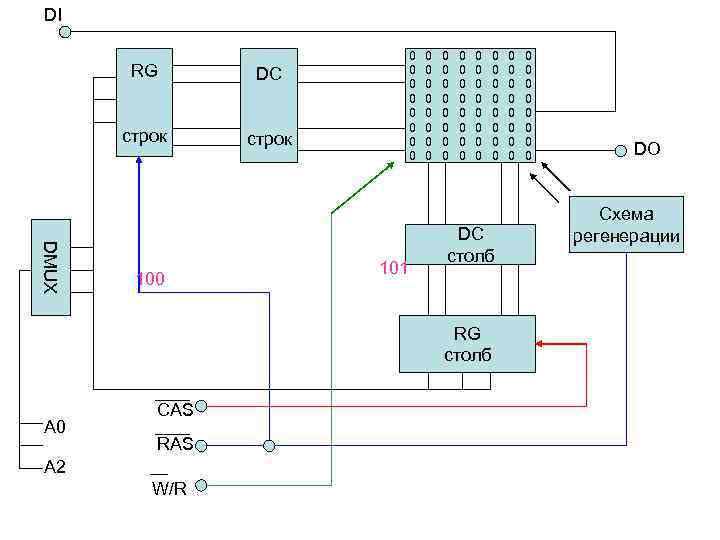

DI RG DC строк 0 0 0 0 строк DMUX 100 101 0 0 0 0 0 0 0 0 DC столб RG столб A 0 CAS RAS A 2 W/R 0 0 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 строк DMUX 100 101 0 0 0 0 0 0 0 0 DC столб RG столб A 0 CAS RAS A 2 W/R 0 0 0 0 0 0 DO Схема регенерации

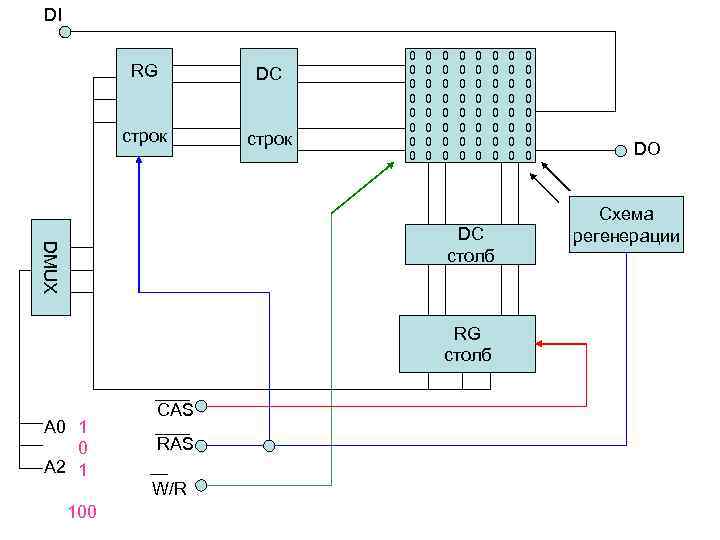

• На адресные входы подаются младшие разряды адреса и затем на стробирующий RAS подается 0.

• На адресные входы подаются младшие разряды адреса и затем на стробирующий RAS подается 0.

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб CAS A 0 RAS A 2 W/R 100101 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб CAS A 0 RAS A 2 W/R 100101 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб A 0 1 0 A 2 1 100 CAS RAS W/R 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб A 0 1 0 A 2 1 100 CAS RAS W/R 0 0 0 0 DO Схема регенерации

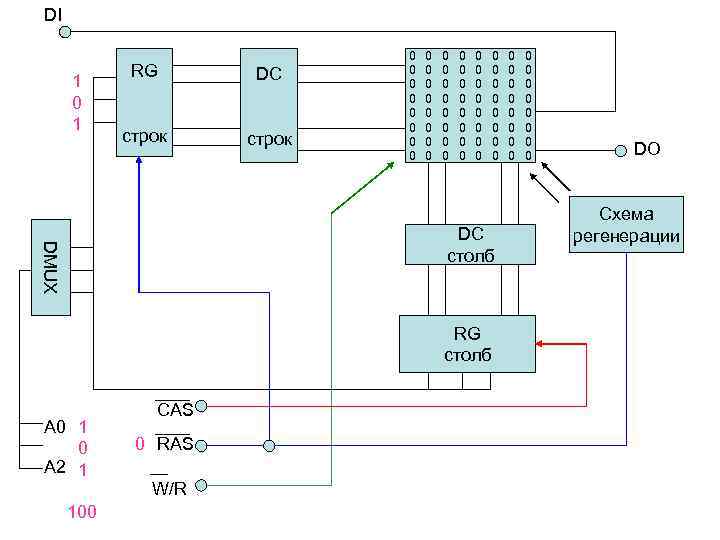

DI 1 0 1 RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб A 0 1 0 A 2 1 100 CAS 0 RAS W/R 0 0 0 0 DO Схема регенерации

DI 1 0 1 RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб A 0 1 0 A 2 1 100 CAS 0 RAS W/R 0 0 0 0 DO Схема регенерации

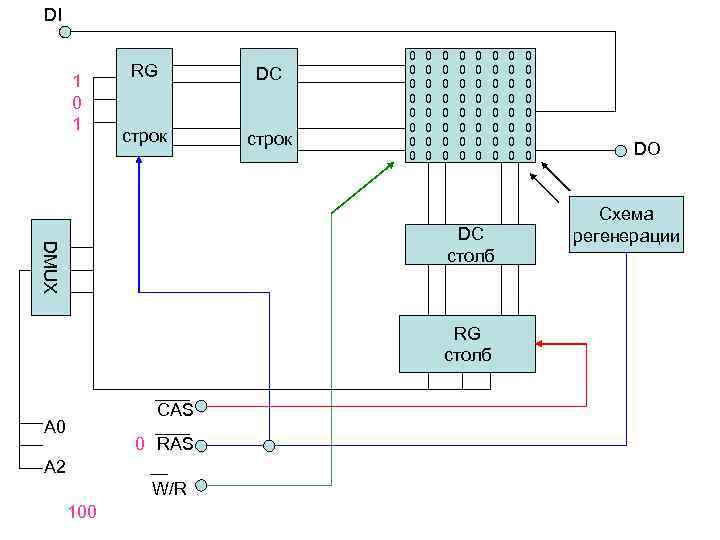

DI 1 0 1 RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб CAS A 0 0 RAS A 2 W/R 100 0 0 0 0 DO Схема регенерации

DI 1 0 1 RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб CAS A 0 0 RAS A 2 W/R 100 0 0 0 0 DO Схема регенерации

• Выбралась строчка где находится адресуемая ячейка.

• Выбралась строчка где находится адресуемая ячейка.

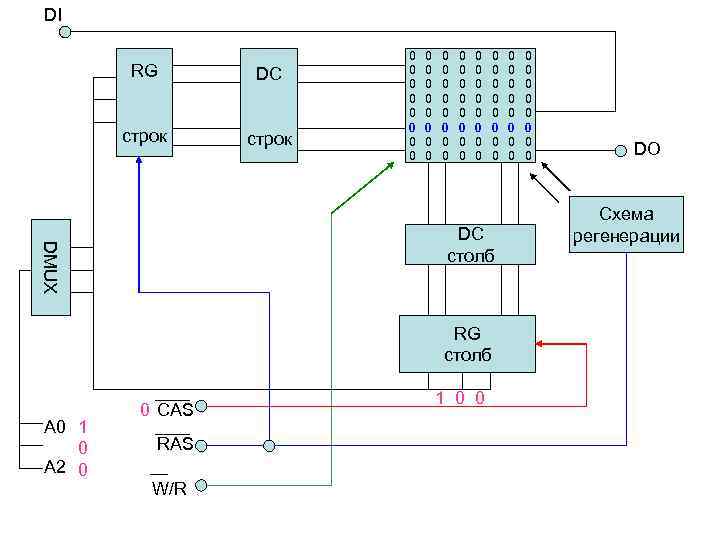

• На те же адресные входы подаются старшие разряды адреса (младшие снимаются) и стробирующий сигнал 0 на вход CAS

• На те же адресные входы подаются старшие разряды адреса (младшие снимаются) и стробирующий сигнал 0 на вход CAS

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб CAS A 0 RAS A 2 W/R 100 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб CAS A 0 RAS A 2 W/R 100 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб A 0 1 0 A 2 0 0 0 0 0 CAS RAS W/R 1 0 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб A 0 1 0 A 2 0 0 0 0 0 CAS RAS W/R 1 0 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб A 0 CAS RAS A 2 W/R 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб A 0 CAS RAS A 2 W/R 0 0 0 0 DO Схема регенерации

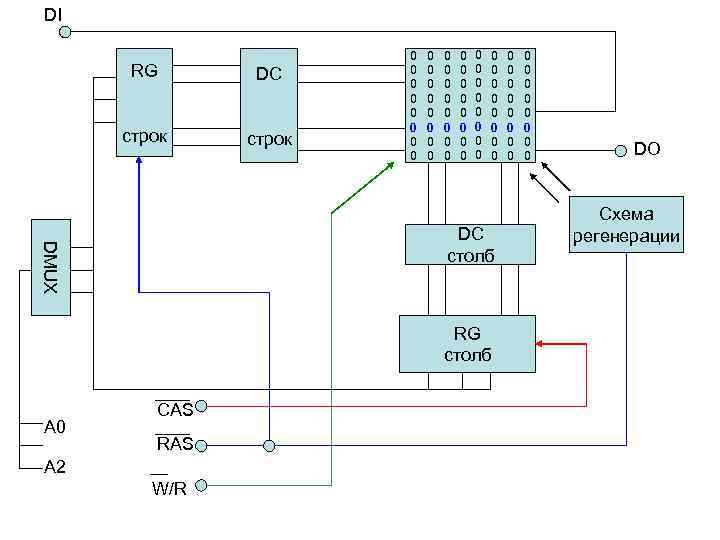

• Выбирается столбик, где находится адресуемая ячейка

• Выбирается столбик, где находится адресуемая ячейка

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб A 0 CAS RAS A 2 W/R 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 0 0 DMUX DC столб RG столб A 0 CAS RAS A 2 W/R 0 0 0 0 DO Схема регенерации

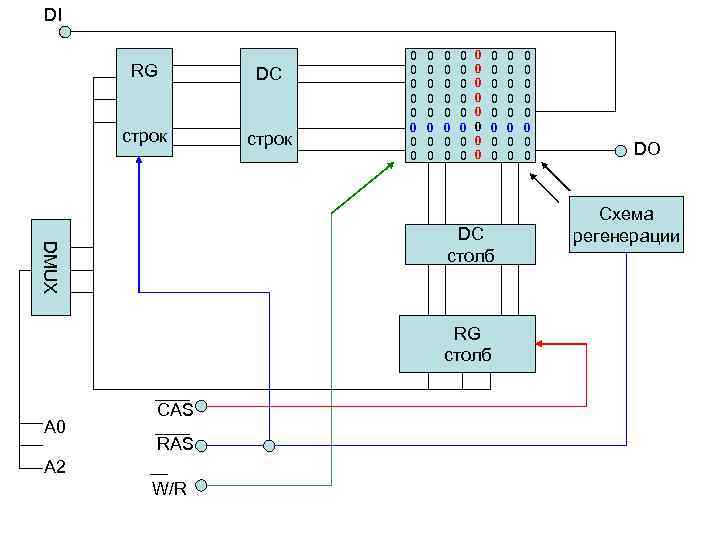

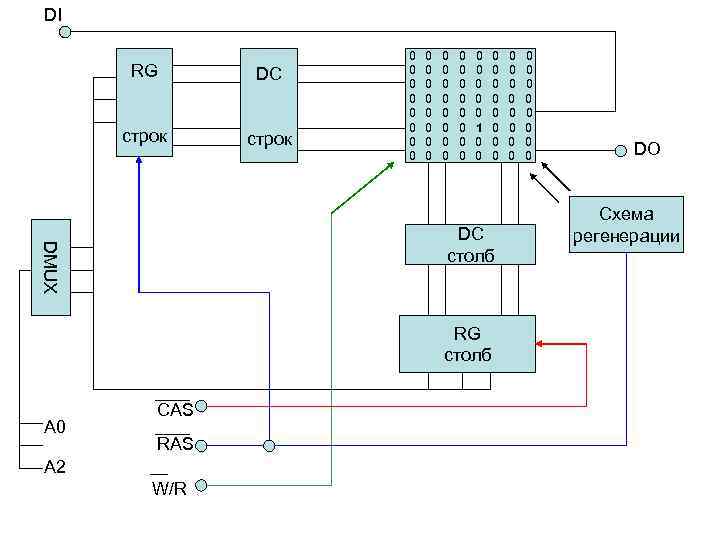

• Адресуемая ячейка лежит на пересечении выбранных строки и столбца

• Адресуемая ячейка лежит на пересечении выбранных строки и столбца

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 DMUX DC столб RG столб A 0 CAS RAS A 2 W/R 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 DMUX DC столб RG столб A 0 CAS RAS A 2 W/R 0 0 0 0 DO Схема регенерации

• При записи на DI подаётся бит информации и на W /R ноль. При чтении на W /R подается единица и на DO появляется считываемый бит информации.

• При записи на DI подаётся бит информации и на W /R ноль. При чтении на W /R подается единица и на DO появляется считываемый бит информации.

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 1 0 0 DMUX DC столб RG столб A 0 0 0 0 0 CAS RAS A 2 W/R 0 0 0 0 DO Схема регенерации

DI RG DC строк 0 0 0 0 0 0 0 0 0 0 1 0 0 DMUX DC столб RG столб A 0 0 0 0 0 CAS RAS A 2 W/R 0 0 0 0 DO Схема регенерации

УГО МИКРОСХЕМЫ DRAM А 0 А 1 А 2 А 3 А 4 А 5 А 6 DI RAS CAS W/R DRAM DO

УГО МИКРОСХЕМЫ DRAM А 0 А 1 А 2 А 3 А 4 А 5 А 6 DI RAS CAS W/R DRAM DO

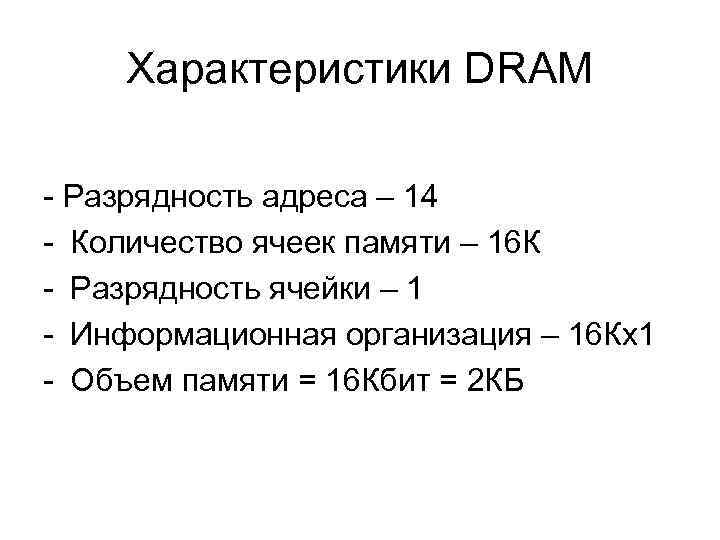

Характеристики DRAM - Разрядность адреса – 14 - Количество ячеек памяти – 16 К - Разрядность ячейки – 1 - Информационная организация – 16 Кх1 - Объем памяти = 16 Кбит = 2 КБ

Характеристики DRAM - Разрядность адреса – 14 - Количество ячеек памяти – 16 К - Разрядность ячейки – 1 - Информационная организация – 16 Кх1 - Объем памяти = 16 Кбит = 2 КБ