Основные устройства AVR

Основные устройства AVR

Основные устройства AVR

Порты ввода-вывода 1. Каждый порт микроконтроллеров состоит из определенного числа выводов, через которые микроконтроллер может осуществлять прием и передачу цифровых сигналов. 2. Задание направления передачи данных через любой контакт ввода/вывода может быть произведено программно в любой момент времени. 3. Выходные буферы всех портов, имея симметричные нагрузочные характеристики, обеспечивают высокую нагрузочную способность при любом уровне сигнала. Нагрузочной способности достаточно для непосредственного управления светодиодными индикаторами. 4. Входные буферы всех выводов построены по схеме триггера Шмитта. Для всех входов имеется возможность подключения внутреннего подтягивающего резистора между входом и шиной питания Vcc. 5. Отличительной особенностью портов микроконтроллеров AVR при использовании их в качестве цифровых портов ввода/вывода общего назначения является реализация истинной функциональности «чтение/модификация/запись» . Благодаря этому можно выполнять операции над любым выводом не влияя на другие выводы порта. Это относится к изменению режима работы контакта ввода/вывода, к изменению состояния выходного буфера (для выходов) и к изменению состояния внутреннего подтягивающего резистора (для входов).

Порты ввода-вывода 1. Каждый порт микроконтроллеров состоит из определенного числа выводов, через которые микроконтроллер может осуществлять прием и передачу цифровых сигналов. 2. Задание направления передачи данных через любой контакт ввода/вывода может быть произведено программно в любой момент времени. 3. Выходные буферы всех портов, имея симметричные нагрузочные характеристики, обеспечивают высокую нагрузочную способность при любом уровне сигнала. Нагрузочной способности достаточно для непосредственного управления светодиодными индикаторами. 4. Входные буферы всех выводов построены по схеме триггера Шмитта. Для всех входов имеется возможность подключения внутреннего подтягивающего резистора между входом и шиной питания Vcc. 5. Отличительной особенностью портов микроконтроллеров AVR при использовании их в качестве цифровых портов ввода/вывода общего назначения является реализация истинной функциональности «чтение/модификация/запись» . Благодаря этому можно выполнять операции над любым выводом не влияя на другие выводы порта. Это относится к изменению режима работы контакта ввода/вывода, к изменению состояния выходного буфера (для выходов) и к изменению состояния внутреннего подтягивающего резистора (для входов).

Регистры портов ввода/вывода Обращение к портам производится через регистры ввода/вывода. Под каждый порт в адресном пространстве ввода/вывода зарезервировано по 3 адреса, по которым размещены следующие регистры: • регистр данных порта PORTx, • регистр направления данных DDRх и • регистр выводов порта PINx. С помощью регистров PINx осуществляется доступ к физическим значениям сигналов на выводах порта, они доступны только для чтения. Регистры PORTx и DDRx доступны и для чтения, и для записи.

Регистры портов ввода/вывода Обращение к портам производится через регистры ввода/вывода. Под каждый порт в адресном пространстве ввода/вывода зарезервировано по 3 адреса, по которым размещены следующие регистры: • регистр данных порта PORTx, • регистр направления данных DDRх и • регистр выводов порта PINx. С помощью регистров PINx осуществляется доступ к физическим значениям сигналов на выводах порта, они доступны только для чтения. Регистры PORTx и DDRx доступны и для чтения, и для записи.

Состояние вывода микроконтроллера (независимо от установок бита DDxn) может быть получено путем чтения бита PINxn регистра PINx. При этом следует помнить , что между действительным изменением сигнала на выводе и изменением бита PINxn существует задержка. Эта задержка вносится узлом синхронизации, состоящим, из бита PINxn и дополнительного триггера-защелки. Значение сигнала на выводе микроконтроллера фиксируется триггером- защелкой при НИЗКОМ уровне тактового сигнала и переписывается затем в бит PINxn по нарастающему фронту тактового сигнала. Соответственно, величина задержки может составлять от 0. 5 до 1. 5 периодов системного тактового сигнала

Состояние вывода микроконтроллера (независимо от установок бита DDxn) может быть получено путем чтения бита PINxn регистра PINx. При этом следует помнить , что между действительным изменением сигнала на выводе и изменением бита PINxn существует задержка. Эта задержка вносится узлом синхронизации, состоящим, из бита PINxn и дополнительного триггера-защелки. Значение сигнала на выводе микроконтроллера фиксируется триггером- защелкой при НИЗКОМ уровне тактового сигнала и переписывается затем в бит PINxn по нарастающему фронту тактового сигнала. Соответственно, величина задержки может составлять от 0. 5 до 1. 5 периодов системного тактового сигнала

Регистры управления подтяжкой SFIOR (а) и MCUCR (б) Конфигурации выводов портов

Регистры управления подтяжкой SFIOR (а) и MCUCR (б) Конфигурации выводов портов

Таймеры/счётчики Микроконтроллеры семейства в зависимости от модели имеют в своем составе от двух до шести таймеров/счетчиков общего назначения. Таймеры используются для измерения временных интервалов, счётчики – для регистрации и подсчёта внешних событий. Во всех моделях микроконтроллеров семейства присутствуют как минимум два таймера/счетчика – Т 0 и Т 1. 8 -и и 16 -и разрядные соответственно Таймер/счетчик Т 0 имеет минимальный набор функций – отсчет и измерение временных интервалов, счетчик внешних событий, генерация сигналов с широтно-импульсной модуляцией (ШИМ) фиксированной разрядности (один или два канала), а также возможность работать в асинхронном режиме в качестве часов реального времени. Таймер/счетчик T 1 тоже может использоваться для отсчета временных интервалов и как счетчик внешних событий. Кроме того, он может осуществлять запоминание своего состояния по внешнему сигналу. Как и таймер/счетчик Т 0, он может работать в качестве 2 - или 3 -канального ШИМ модулятор а, но уже переменной разрядности. Количество каналов ШИМ зависит от модели. В составе всех микроконтроллеров семейства AVR имеется также сторожевой таймер. Сторожевой таймер позволяет избежать несанкционированного зацикливания программы, возникающего по тем или иным причинам.

Таймеры/счётчики Микроконтроллеры семейства в зависимости от модели имеют в своем составе от двух до шести таймеров/счетчиков общего назначения. Таймеры используются для измерения временных интервалов, счётчики – для регистрации и подсчёта внешних событий. Во всех моделях микроконтроллеров семейства присутствуют как минимум два таймера/счетчика – Т 0 и Т 1. 8 -и и 16 -и разрядные соответственно Таймер/счетчик Т 0 имеет минимальный набор функций – отсчет и измерение временных интервалов, счетчик внешних событий, генерация сигналов с широтно-импульсной модуляцией (ШИМ) фиксированной разрядности (один или два канала), а также возможность работать в асинхронном режиме в качестве часов реального времени. Таймер/счетчик T 1 тоже может использоваться для отсчета временных интервалов и как счетчик внешних событий. Кроме того, он может осуществлять запоминание своего состояния по внешнему сигналу. Как и таймер/счетчик Т 0, он может работать в качестве 2 - или 3 -канального ШИМ модулятор а, но уже переменной разрядности. Количество каналов ШИМ зависит от модели. В составе всех микроконтроллеров семейства AVR имеется также сторожевой таймер. Сторожевой таймер позволяет избежать несанкционированного зацикливания программы, возникающего по тем или иным причинам.

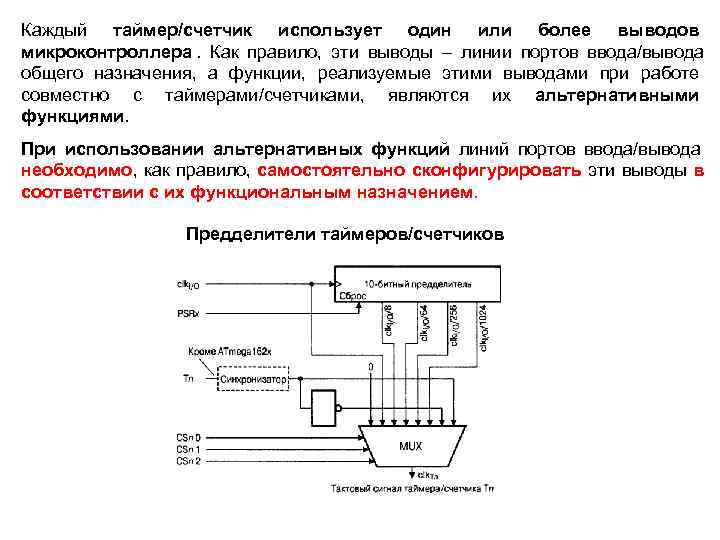

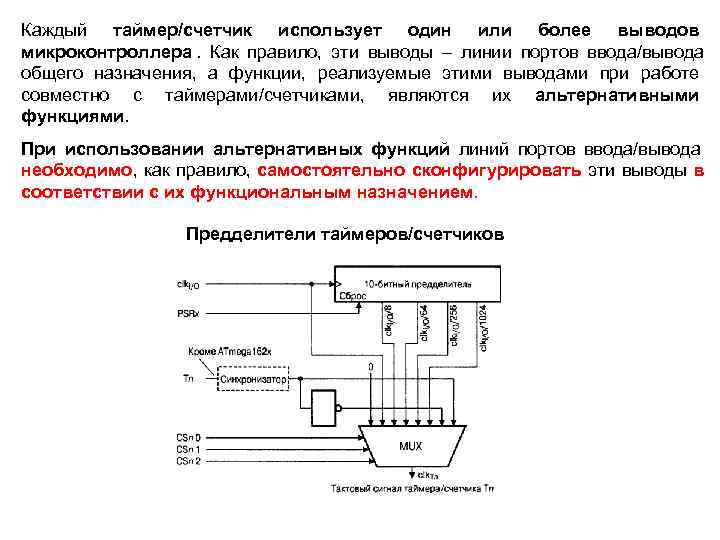

Каждый таймер/счетчик использует один или более выводов микроконтроллера. Как правило, эти выводы – линии портов ввода/вывода общего назначения, а функции, реализуемые этими выводами при работе совместно с таймерами/счетчиками, являются их альтернативными функциями. При использовании альтернативных функций линий портов ввода/вывода необходимо, как правило, самостоятельно сконфигурировать эти выводы в соответствии с их функциональным назначением. Предделители таймеров/счетчиков

Каждый таймер/счетчик использует один или более выводов микроконтроллера. Как правило, эти выводы – линии портов ввода/вывода общего назначения, а функции, реализуемые этими выводами при работе совместно с таймерами/счетчиками, являются их альтернативными функциями. При использовании альтернативных функций линий портов ввода/вывода необходимо, как правило, самостоятельно сконфигурировать эти выводы в соответствии с их функциональным назначением. Предделители таймеров/счетчиков

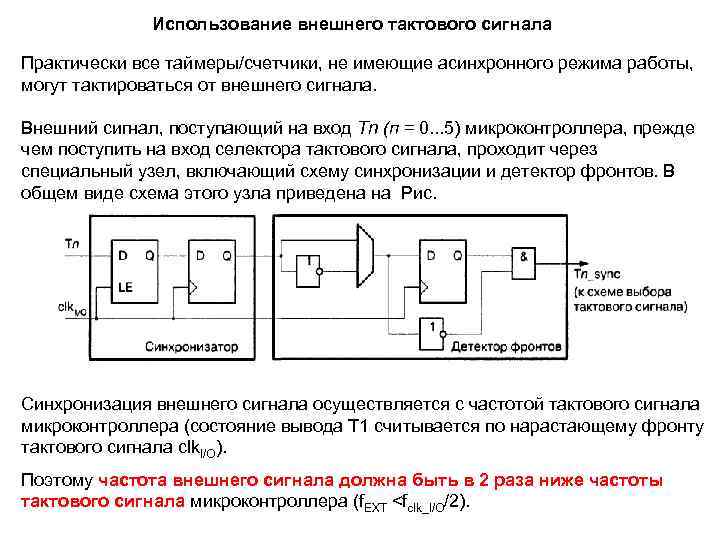

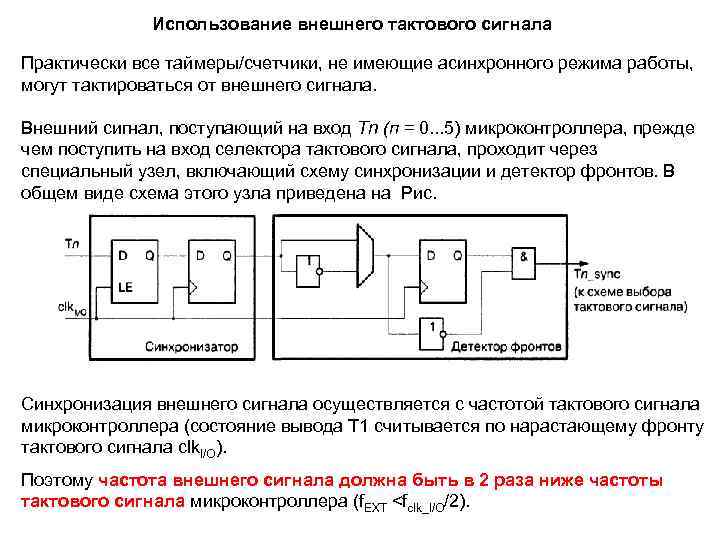

Использование внешнего тактового сигнала Практически все таймеры/счетчики, не имеющие асинхронного режима работы, могут тактироваться от внешнего сигнала. Внешний сигнал, поступающий на вход Тn (п = 0. . . 5) микроконтроллера, прежде чем поступить на вход селектора тактового сигнала, проходит через специальный узел, включающий схему синхронизации и детектор фронтов. В общем виде схема этого узла приведена на Рис. Синхронизация внешнего сигнала осуществляется с частотой тактового сигнала микроконтроллера (состояние вывода Т 1 считывается по нарастающему фронту тактового сигнала clk. I/O). Поэтому частота внешнего сигнала должна быть в 2 раза ниже частоты тактового сигнала микроконтроллера (f. EXT

Использование внешнего тактового сигнала Практически все таймеры/счетчики, не имеющие асинхронного режима работы, могут тактироваться от внешнего сигнала. Внешний сигнал, поступающий на вход Тn (п = 0. . . 5) микроконтроллера, прежде чем поступить на вход селектора тактового сигнала, проходит через специальный узел, включающий схему синхронизации и детектор фронтов. В общем виде схема этого узла приведена на Рис. Синхронизация внешнего сигнала осуществляется с частотой тактового сигнала микроконтроллера (состояние вывода Т 1 считывается по нарастающему фронту тактового сигнала clk. I/O). Поэтому частота внешнего сигнала должна быть в 2 раза ниже частоты тактового сигнала микроконтроллера (f. EXT

Структурная схема 8 -битных таймеров-счетчиков

Структурная схема 8 -битных таймеров-счетчиков

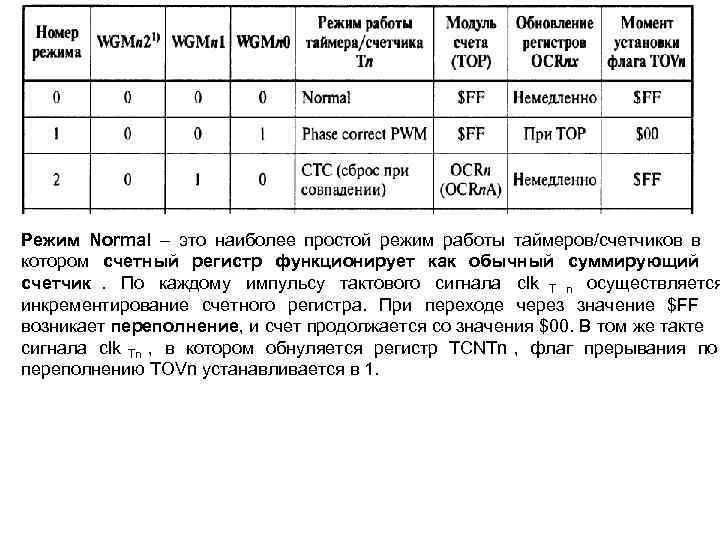

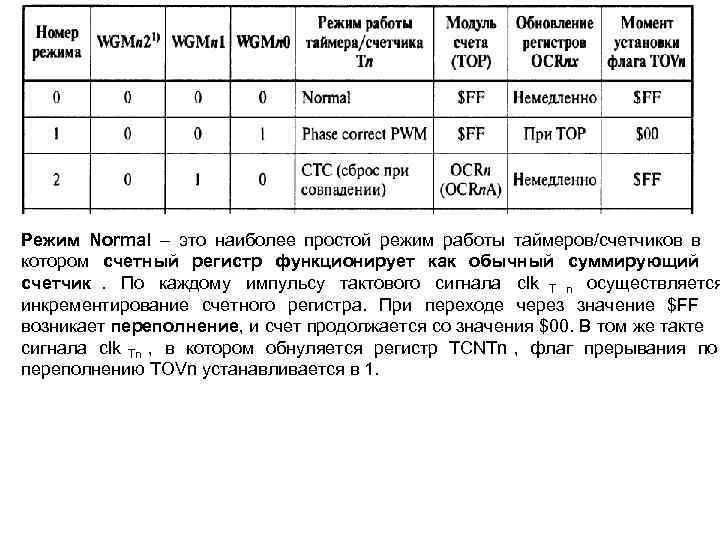

Режим Normal – это наиболее простой режим работы таймеров/счетчиков в котором счетный регистр функционирует как обычный суммирующий счетчик. По каждому импульсу тактового сигнала clk Т n осуществляется инкрементирование счетного регистра. При переходе через значение $FF возникает переполнение, и счет продолжается со значения $00. В том же такте сигнала clk Tn , в котором обнуляется регистр TCNTn , флаг прерывания по переполнению ТОVn устанавливается в 1.

Режим Normal – это наиболее простой режим работы таймеров/счетчиков в котором счетный регистр функционирует как обычный суммирующий счетчик. По каждому импульсу тактового сигнала clk Т n осуществляется инкрементирование счетного регистра. При переходе через значение $FF возникает переполнение, и счет продолжается со значения $00. В том же такте сигнала clk Tn , в котором обнуляется регистр TCNTn , флаг прерывания по переполнению ТОVn устанавливается в 1.

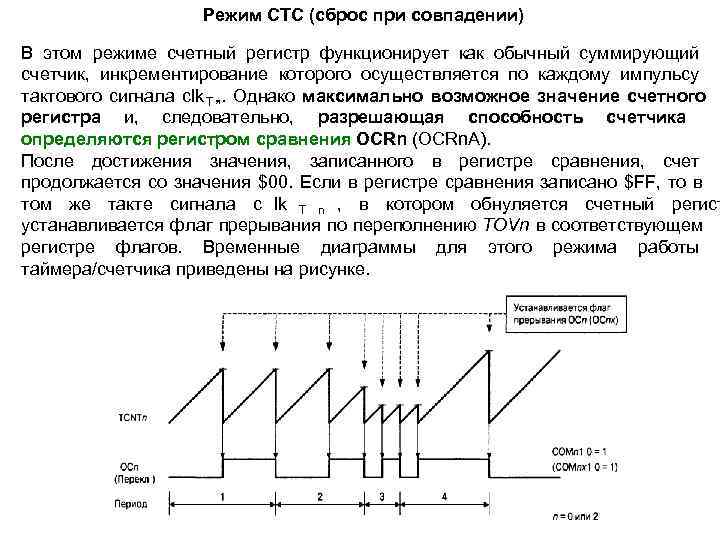

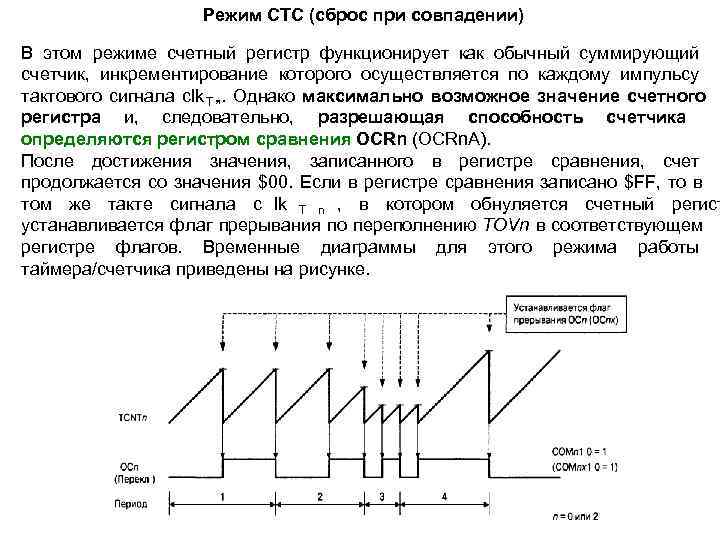

Режим СТС (сброс при совпадении) В этом режиме счетный регистр функционирует как обычный суммирующий счетчик, инкрементирование которого осуществляется по каждому импульсу тактового сигнала clk T „. Однако максимально возможное значение счетного регистра и, следовательно, разрешающая способность счетчика определяются регистром сравнения OCRn (OCRn. A). После достижения значения, записанного в регистре сравнения, счет продолжается со значения $00. Если в регистре сравнения записано $FF, то в том же такте сигнала с lk Т n , в котором обнуляется счетный регист устанавливается флаг прерывания по переполнению TOVn в соответствующем регистре флагов. Временные диаграммы для этого режима работы таймера/счетчика приведены на рисунке.

Режим СТС (сброс при совпадении) В этом режиме счетный регистр функционирует как обычный суммирующий счетчик, инкрементирование которого осуществляется по каждому импульсу тактового сигнала clk T „. Однако максимально возможное значение счетного регистра и, следовательно, разрешающая способность счетчика определяются регистром сравнения OCRn (OCRn. A). После достижения значения, записанного в регистре сравнения, счет продолжается со значения $00. Если в регистре сравнения записано $FF, то в том же такте сигнала с lk Т n , в котором обнуляется счетный регист устанавливается флаг прерывания по переполнению TOVn в соответствующем регистре флагов. Временные диаграммы для этого режима работы таймера/счетчика приведены на рисунке.

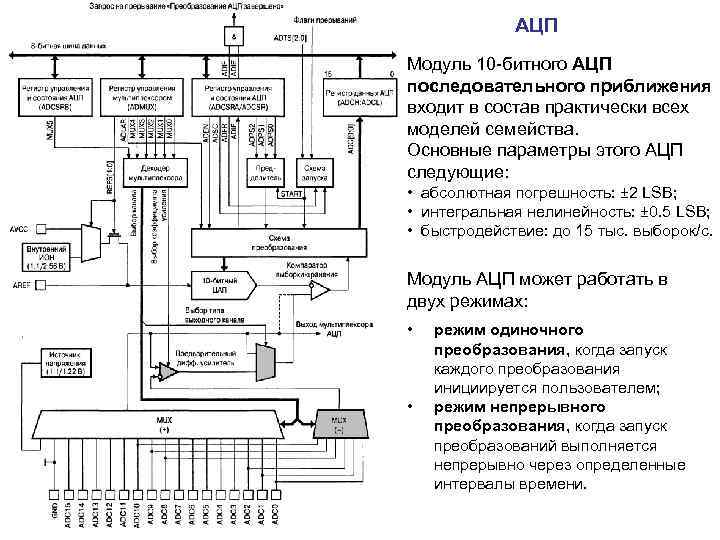

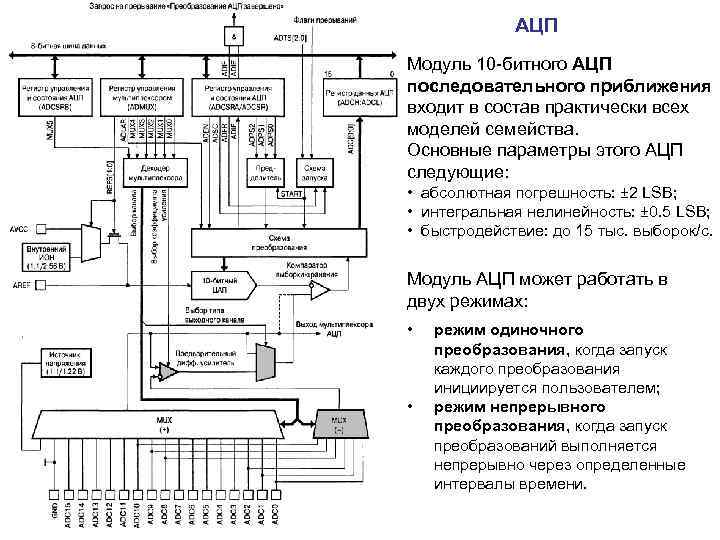

АЦП Модуль 10 -битного АЦП последовательного приближения входит в состав практически всех моделей семейства. Основные параметры этого АЦП следующие: • абсолютная погрешность: ± 2 LSB; • интегральная нелинейность: ± 0. 5 LSB; • быстродействие: до 15 тыс. выборок/с. Модуль АЦП может работать в двух режимах: • режим одиночного преобразования, когда запуск каждого преобразования инициируется пользователем; • режим непрерывного преобразования, когда запуск преобразований выполняется непрерывно через определенные интервалы времени.

АЦП Модуль 10 -битного АЦП последовательного приближения входит в состав практически всех моделей семейства. Основные параметры этого АЦП следующие: • абсолютная погрешность: ± 2 LSB; • интегральная нелинейность: ± 0. 5 LSB; • быстродействие: до 15 тыс. выборок/с. Модуль АЦП может работать в двух режимах: • режим одиночного преобразования, когда запуск каждого преобразования инициируется пользователем; • режим непрерывного преобразования, когда запуск преобразований выполняется непрерывно через определенные интервалы времени.

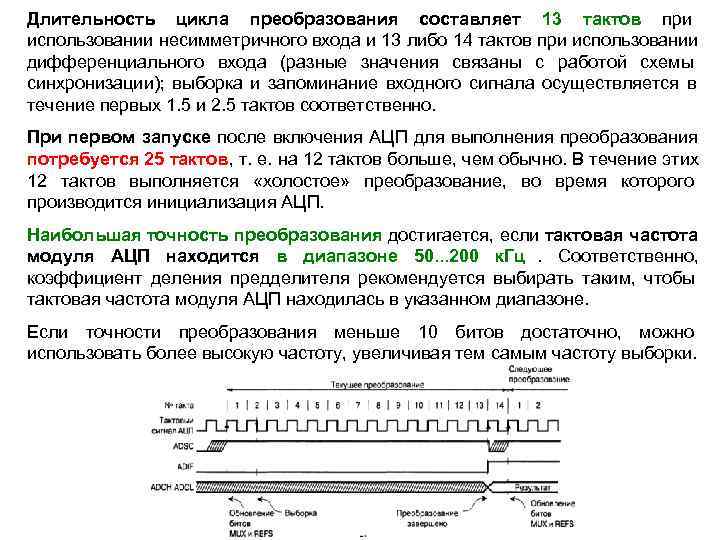

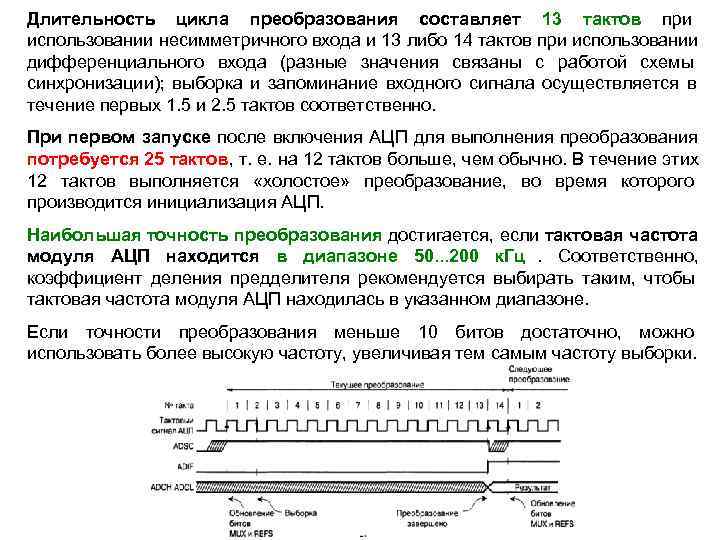

Длительность цикла преобразования составляет 13 тактов при использовании несимметричного входа и 13 либо 14 тактов при использовании дифференциального входа (разные значения связаны с работой схемы синхронизации); выборка и запоминание входного сигнала осуществляется в течение первых 1. 5 и 2. 5 тактов соответственно. При первом запуске после включения АЦП для выполнения преобразования потребуется 25 тактов, т. е. на 12 тактов больше, чем обычно. В течение этих 12 тактов выполняется «холостое» преобразование, во время которого производится инициализация АЦП. Наибольшая точность преобразования достигается, если тактовая частота модуля АЦП находится в диапазоне 50. . . 200 к. Гц. Соответственно, коэффициент деления предделителя рекомендуется выбирать таким, чтобы тактовая частота модуля АЦП находилась в указанном диапазоне. Если точности преобразования меньше 10 битов достаточно, можно использовать более высокую частоту, увеличивая тем самым частоту выборки.

Длительность цикла преобразования составляет 13 тактов при использовании несимметричного входа и 13 либо 14 тактов при использовании дифференциального входа (разные значения связаны с работой схемы синхронизации); выборка и запоминание входного сигнала осуществляется в течение первых 1. 5 и 2. 5 тактов соответственно. При первом запуске после включения АЦП для выполнения преобразования потребуется 25 тактов, т. е. на 12 тактов больше, чем обычно. В течение этих 12 тактов выполняется «холостое» преобразование, во время которого производится инициализация АЦП. Наибольшая точность преобразования достигается, если тактовая частота модуля АЦП находится в диапазоне 50. . . 200 к. Гц. Соответственно, коэффициент деления предделителя рекомендуется выбирать таким, чтобы тактовая частота модуля АЦП находилась в указанном диапазоне. Если точности преобразования меньше 10 битов достаточно, можно использовать более высокую частоту, увеличивая тем самым частоту выборки.

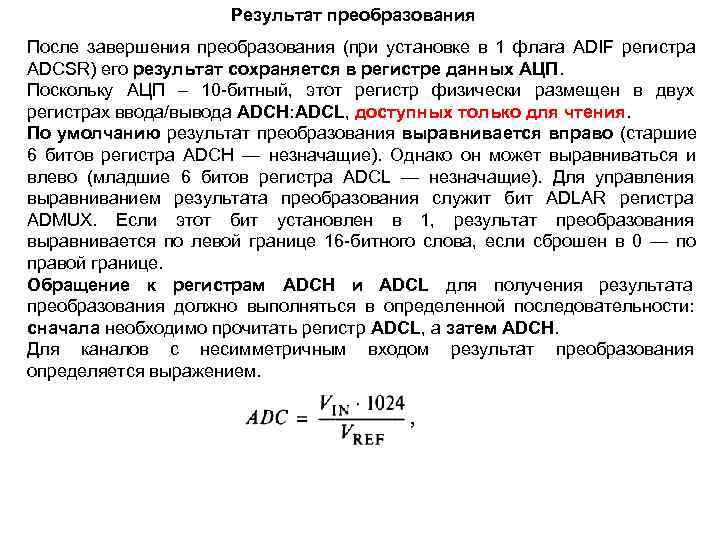

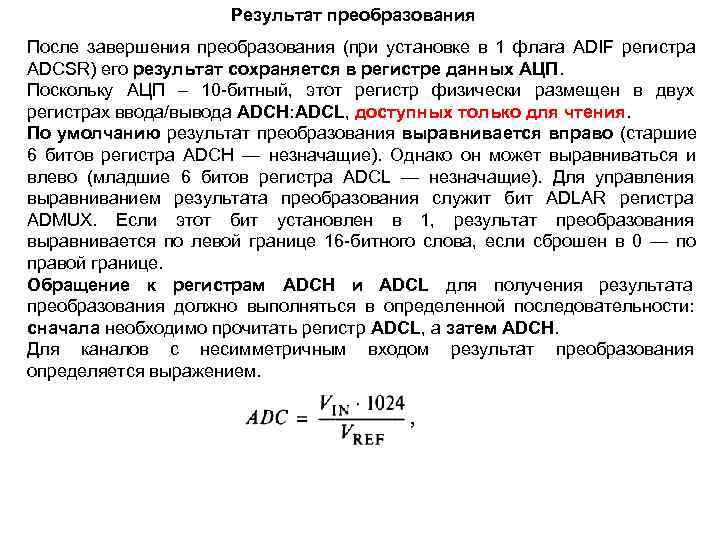

Результат преобразования После завершения преобразования (при установке в 1 флага ADIF регистра ADCSR) его результат сохраняется в регистре данных АЦП. Поскольку АЦП – 10 -битный, этот регистр физически размещен в двух регистрах ввода/вывода ADCH: ADCL, доступных только для чтения. По умолчанию результат преобразования выравнивается вправо (старшие 6 битов регистра ADCH — незначащие). Однако он может выравниваться и влево (младшие 6 битов регистра ADCL — незначащие). Для управления выравниванием результата преобразования служит бит ADLAR регистра ADMUX. Если этот бит установлен в 1, результат преобразования выравнивается по левой границе 16 -битного слова, если сброшен в 0 — по правой границе. Обращение к регистрам ADCH и ADCL для получения результата преобразования должно выполняться в определенной последовательности: сначала необходимо прочитать регистр ADCL, а затем ADCH. Для каналов с несимметричным входом результат преобразования определяется выражением.

Результат преобразования После завершения преобразования (при установке в 1 флага ADIF регистра ADCSR) его результат сохраняется в регистре данных АЦП. Поскольку АЦП – 10 -битный, этот регистр физически размещен в двух регистрах ввода/вывода ADCH: ADCL, доступных только для чтения. По умолчанию результат преобразования выравнивается вправо (старшие 6 битов регистра ADCH — незначащие). Однако он может выравниваться и влево (младшие 6 битов регистра ADCL — незначащие). Для управления выравниванием результата преобразования служит бит ADLAR регистра ADMUX. Если этот бит установлен в 1, результат преобразования выравнивается по левой границе 16 -битного слова, если сброшен в 0 — по правой границе. Обращение к регистрам ADCH и ADCL для получения результата преобразования должно выполняться в определенной последовательности: сначала необходимо прочитать регистр ADCL, а затем ADCH. Для каналов с несимметричным входом результат преобразования определяется выражением.