Основные структуры запоминающих устройств

Л6. Основные структуры запоминающих устройств.ppt

- Количество слайдов: 23

Основные структуры запоминающих устройств

Основные структуры запоминающих устройств

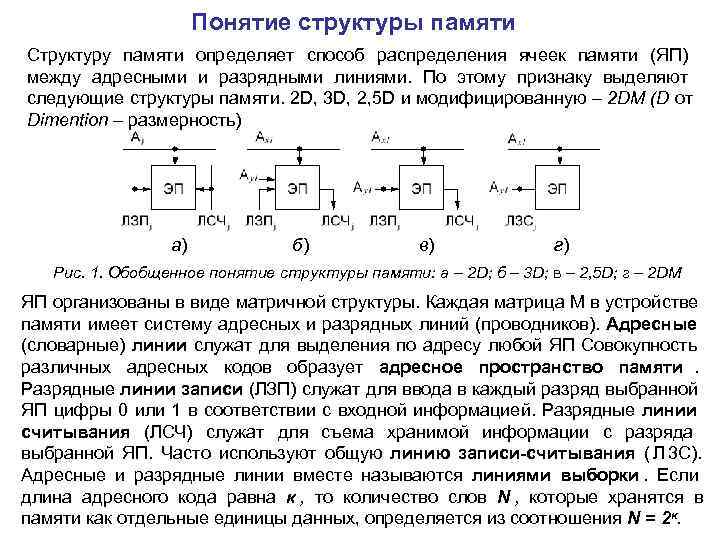

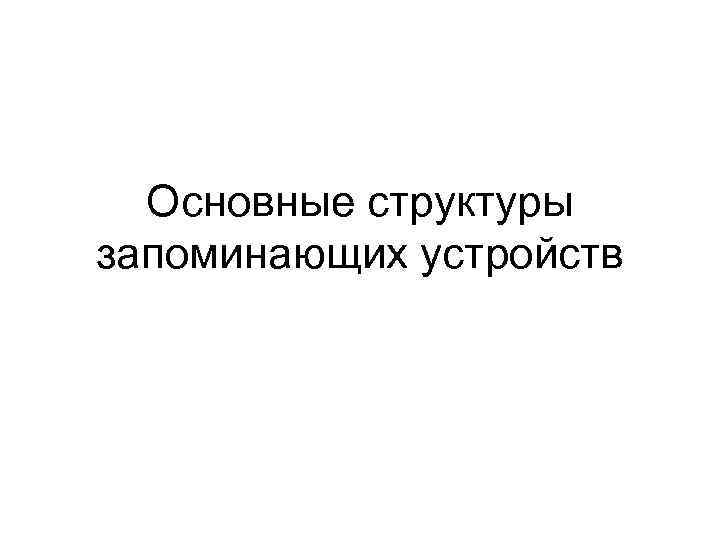

Понятие структуры памяти Структуру памяти определяет способ распределения ячеек памяти (ЯП) между адресными и разрядными линиями. По этому признаку выделяют следующие структуры памяти. 2 D, 3 D, 2, 5 D и модифицированную – 2 DM (D от Dimention – размерность) а) б) в) г) Рис. 1. Обобщенное понятие структуры памяти: а – 2 D; б – 3 D; в – 2, 5 D; г – 2 DM ЯП организованы в виде матричной структуры. Каждая матрица М в устройстве памяти имеет систему адресных и разрядных линий (проводников). Адресные (словарные) линии служат для выделения по адресу любой ЯП Совокупность различных адресных кодов образует адресное пространство памяти. Разрядные линии записи (ЛЗП) служат для ввода в каждый разряд выбранной ЯП цифры 0 или 1 в соответствии с входной информацией. Разрядные линии считывания (ЛСЧ) служат для съема хранимой информации с разряда выбранной ЯП. Часто используют общую линию записи-считывания ( Л 3 C). Адресные и разрядные линии вместе называются линиями выборки. Если длина адресного кода равна к , то количество слов N , которые хранятся в памяти как отдельные единицы данных, определяется из соотношения N = 2 к.

Понятие структуры памяти Структуру памяти определяет способ распределения ячеек памяти (ЯП) между адресными и разрядными линиями. По этому признаку выделяют следующие структуры памяти. 2 D, 3 D, 2, 5 D и модифицированную – 2 DM (D от Dimention – размерность) а) б) в) г) Рис. 1. Обобщенное понятие структуры памяти: а – 2 D; б – 3 D; в – 2, 5 D; г – 2 DM ЯП организованы в виде матричной структуры. Каждая матрица М в устройстве памяти имеет систему адресных и разрядных линий (проводников). Адресные (словарные) линии служат для выделения по адресу любой ЯП Совокупность различных адресных кодов образует адресное пространство памяти. Разрядные линии записи (ЛЗП) служат для ввода в каждый разряд выбранной ЯП цифры 0 или 1 в соответствии с входной информацией. Разрядные линии считывания (ЛСЧ) служат для съема хранимой информации с разряда выбранной ЯП. Часто используют общую линию записи-считывания ( Л 3 C). Адресные и разрядные линии вместе называются линиями выборки. Если длина адресного кода равна к , то количество слов N , которые хранятся в памяти как отдельные единицы данных, определяется из соотношения N = 2 к.

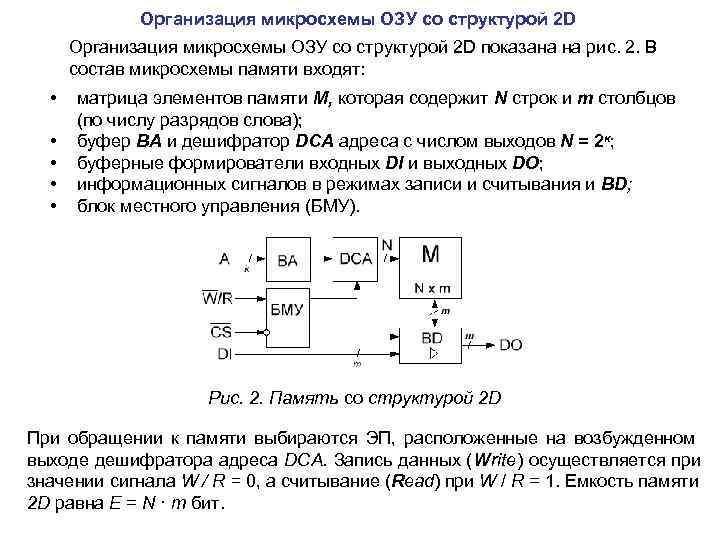

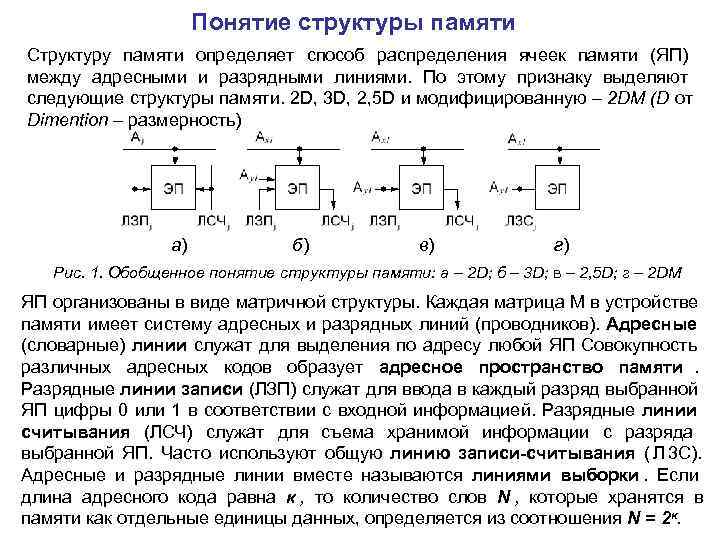

Организация микросхемы ОЗУ со структурой 2 D показана на рис. 2. В состав микросхемы памяти входят: • матрица элементов памяти М, которая содержит N строк и т столбцов (по числу разрядов слова); • буфер ВА и дешифратор DCА адреса с числом выходов N = 2 к; • буферные формирователи входных DI и выходных DO; • информационных сигналов в режимах записи и считывания и BD; • блок местного управления (БМУ). Рис. 2. Память со структурой 2 D При обращении к памяти выбираются ЭП, расположенные на возбужденном выходе дешифратора адреса DCА. Запись данных (Write) осуществляется при значении сигнала W / R = 0, а считывание (Read) при W / R = 1. Емкость памяти 2 D равна Е = N · m бит.

Организация микросхемы ОЗУ со структурой 2 D показана на рис. 2. В состав микросхемы памяти входят: • матрица элементов памяти М, которая содержит N строк и т столбцов (по числу разрядов слова); • буфер ВА и дешифратор DCА адреса с числом выходов N = 2 к; • буферные формирователи входных DI и выходных DO; • информационных сигналов в режимах записи и считывания и BD; • блок местного управления (БМУ). Рис. 2. Память со структурой 2 D При обращении к памяти выбираются ЭП, расположенные на возбужденном выходе дешифратора адреса DCА. Запись данных (Write) осуществляется при значении сигнала W / R = 0, а считывание (Read) при W / R = 1. Емкость памяти 2 D равна Е = N · m бит.

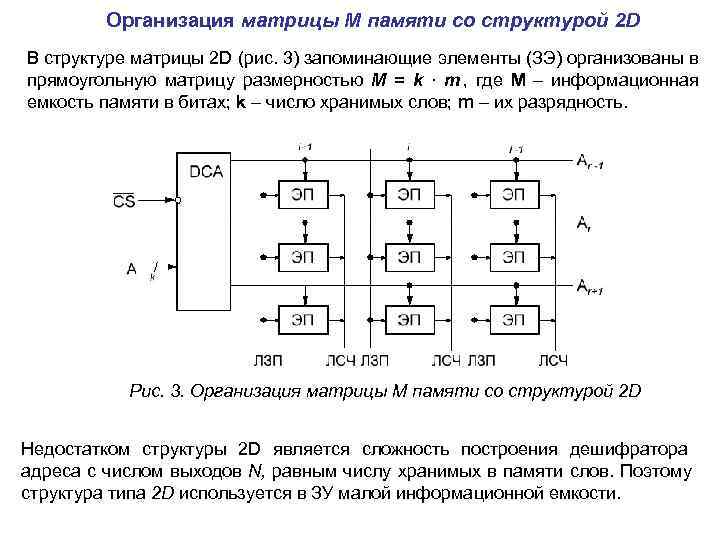

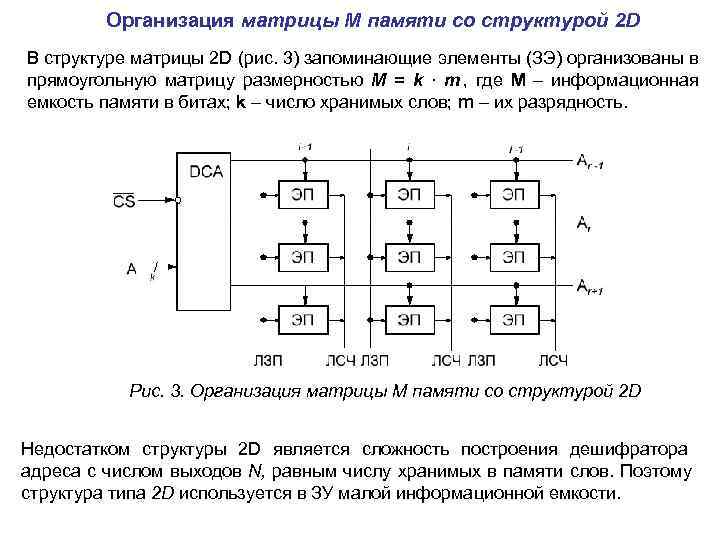

Организация матрицы М памяти со структурой 2 D В структуре матрицы 2 D (рис. 3) запоминающие элементы (ЗЭ) организованы в прямоугольную матрицу размерностью М = k ∙ m , где М – информационная емкость памяти в битах; k – число хранимых слов; m – их разрядность. Рис. 3. Организация матрицы М памяти со структурой 2 D Недостатком структуры 2 D является сложность построения дешифратора адреса с числом выходов N, равным числу хранимых в памяти слов. Поэтому структура типа 2 D используется в ЗУ малой информационной емкости.

Организация матрицы М памяти со структурой 2 D В структуре матрицы 2 D (рис. 3) запоминающие элементы (ЗЭ) организованы в прямоугольную матрицу размерностью М = k ∙ m , где М – информационная емкость памяти в битах; k – число хранимых слов; m – их разрядность. Рис. 3. Организация матрицы М памяти со структурой 2 D Недостатком структуры 2 D является сложность построения дешифратора адреса с числом выходов N, равным числу хранимых в памяти слов. Поэтому структура типа 2 D используется в ЗУ малой информационной емкости.

Память со структурой 3 D В памяти со структурой 3 D адресный код разделяется на две равные части Ах и Ау (для четного к ), каждая из которых декодируется отдельными дешифраторами соответственно DCX и DCY (рис. 4). Рис. 4. Память со структурой 3 D

Память со структурой 3 D В памяти со структурой 3 D адресный код разделяется на две равные части Ах и Ау (для четного к ), каждая из которых декодируется отдельными дешифраторами соответственно DCX и DCY (рис. 4). Рис. 4. Память со структурой 3 D

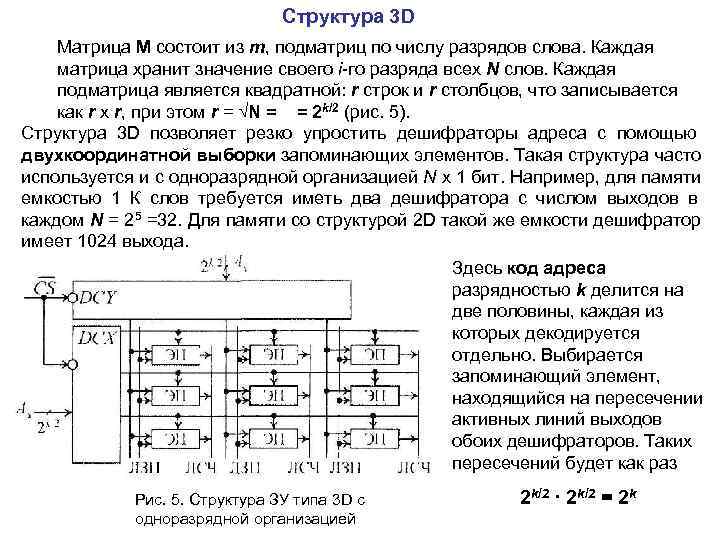

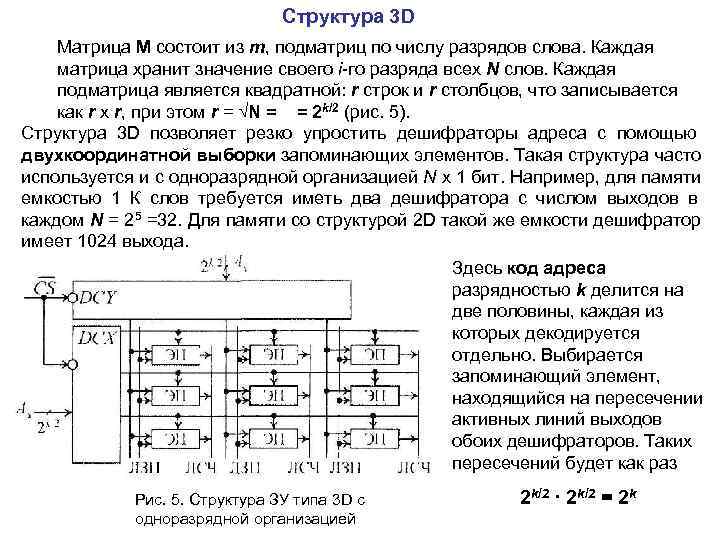

Структура 3 D Матрица М состоит из m, подматриц по числу разрядов слова. Каждая матрица хранит значение своего i-го разряда всех N слов. Каждая подматрица является квадратной: r строк и r столбцов, что записывается как r x r, при этом r = √N = = 2 k/2 (рис. 5). Структура 3 D позволяет резко упростить дешифраторы адреса с помощью двухкоординатной выборки запоминающих элементов. Такая структура часто используется и с одноразрядной организацией N x 1 бит. Например, для памяти емкостью 1 К слов требуется иметь два дешифратора с числом выходов в каждом N = 25 =32. Для памяти со структурой 2 D такой же емкости дешифратор имеет 1024 выхода. Здесь код адреса разрядностью k делится на две половины, каждая из которых декодируется отдельно. Выбирается запоминающий элемент, находящийся на пересечении активных линий выходов обоих дешифраторов. Таких пересечений будет как раз Рис. 5. Структура ЗУ типа 3 D с 2 k/2 ∙ 2 k/2 = 2 k одноразрядной организацией

Структура 3 D Матрица М состоит из m, подматриц по числу разрядов слова. Каждая матрица хранит значение своего i-го разряда всех N слов. Каждая подматрица является квадратной: r строк и r столбцов, что записывается как r x r, при этом r = √N = = 2 k/2 (рис. 5). Структура 3 D позволяет резко упростить дешифраторы адреса с помощью двухкоординатной выборки запоминающих элементов. Такая структура часто используется и с одноразрядной организацией N x 1 бит. Например, для памяти емкостью 1 К слов требуется иметь два дешифратора с числом выходов в каждом N = 25 =32. Для памяти со структурой 2 D такой же емкости дешифратор имеет 1024 выхода. Здесь код адреса разрядностью k делится на две половины, каждая из которых декодируется отдельно. Выбирается запоминающий элемент, находящийся на пересечении активных линий выходов обоих дешифраторов. Таких пересечений будет как раз Рис. 5. Структура ЗУ типа 3 D с 2 k/2 ∙ 2 k/2 = 2 k одноразрядной организацией

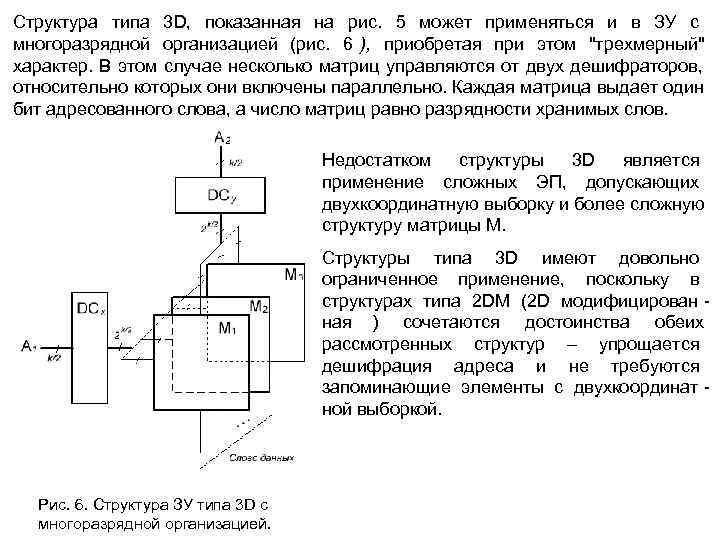

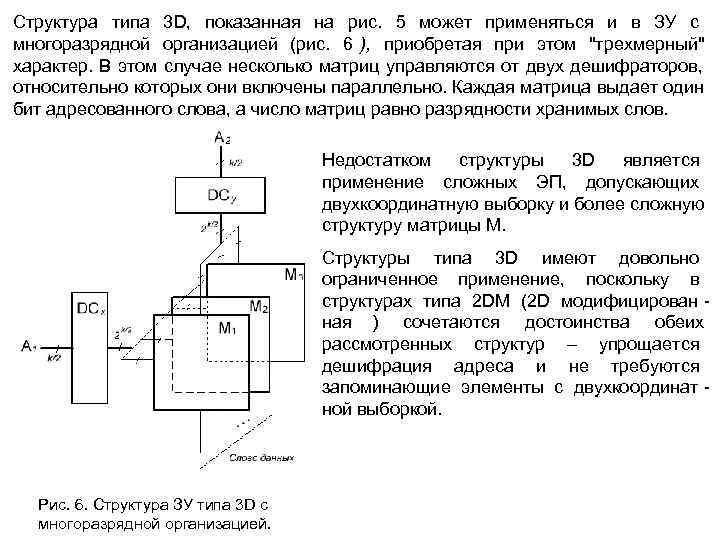

Структура типа 3 D, показанная на рис. 5 может применяться и в ЗУ с многоразрядной организацией (рис. 6 ), приобретая при этом "трехмерный" характер. В этом случае несколько матриц управляются от двух дешифраторов, относительно которых они включены параллельно. Каждая матрица выдает один бит адресованного слова, а число матриц равно разрядности хранимых слов. Недостатком структуры 3 D является применение сложных ЭП, допускающих двухкоординатную выборку и более сложную структуру матрицы М. Структуры типа 3 D имеют довольно ограниченное применение, поскольку в структурах типа 2 DM (2 D модифицирован - ная ) сочетаются достоинства обеих рассмотренных структур – упрощается дешифрация адреса и не требуются запоминающие элементы с двухкоординат - ной выборкой. Рис. 6. Cтpyктypa ЗУ типа 3 D с многоразрядной организацией.

Структура типа 3 D, показанная на рис. 5 может применяться и в ЗУ с многоразрядной организацией (рис. 6 ), приобретая при этом "трехмерный" характер. В этом случае несколько матриц управляются от двух дешифраторов, относительно которых они включены параллельно. Каждая матрица выдает один бит адресованного слова, а число матриц равно разрядности хранимых слов. Недостатком структуры 3 D является применение сложных ЭП, допускающих двухкоординатную выборку и более сложную структуру матрицы М. Структуры типа 3 D имеют довольно ограниченное применение, поскольку в структурах типа 2 DM (2 D модифицирован - ная ) сочетаются достоинства обеих рассмотренных структур – упрощается дешифрация адреса и не требуются запоминающие элементы с двухкоординат - ной выборкой. Рис. 6. Cтpyктypa ЗУ типа 3 D с многоразрядной организацией.

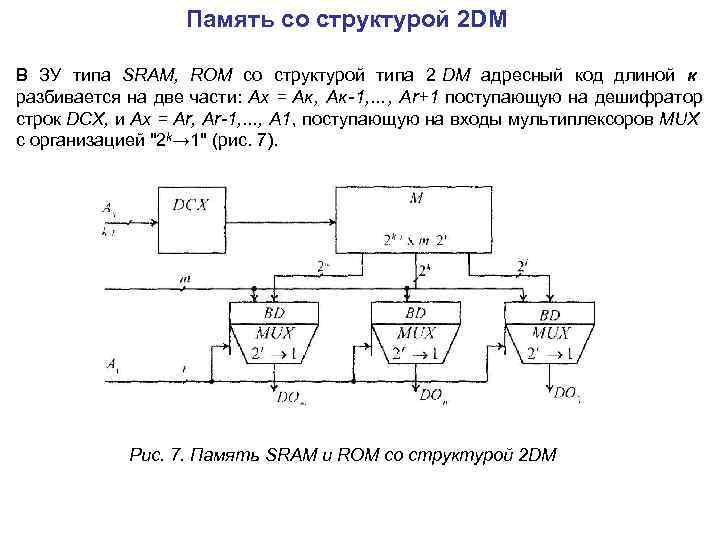

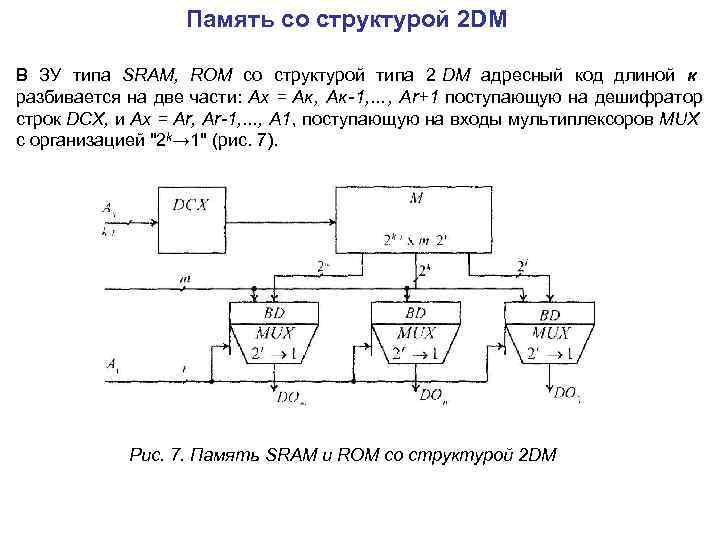

Память со структурой 2 DM В ЗУ типа SRAM, ROM со структурой типа 2 DM адресный код длиной к разбивается на две части: Ах = Ак, Ак-1, . . . , Аr+1 поступающую на дешифратор строк DCX, и Ах = Аr, Аr-1, . . . , А 1, поступающую на входы мультиплексоров MUX с организацией "2 k→ 1" (рис. 7). Рис. 7. Память SRAM и ROM со структурой 2 DM

Память со структурой 2 DM В ЗУ типа SRAM, ROM со структурой типа 2 DM адресный код длиной к разбивается на две части: Ах = Ак, Ак-1, . . . , Аr+1 поступающую на дешифратор строк DCX, и Ах = Аr, Аr-1, . . . , А 1, поступающую на входы мультиплексоров MUX с организацией "2 k→ 1" (рис. 7). Рис. 7. Память SRAM и ROM со структурой 2 DM

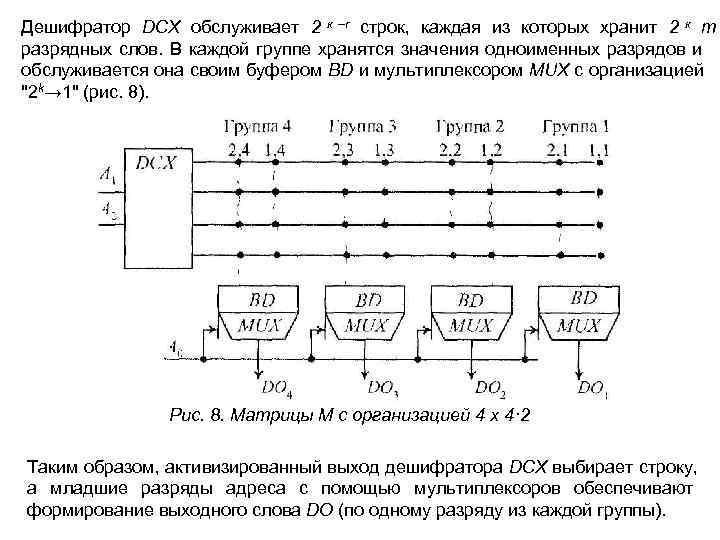

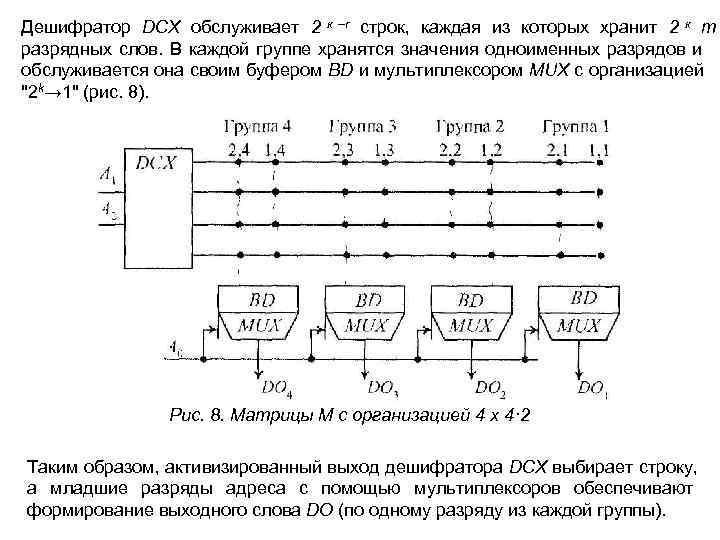

Дешифратор DCX обслуживает 2 к –r строк, каждая из которых хранит 2 к m разрядных слов. В каждой группе хранятся значения одноименных разрядов и обслуживается она своим буфером BD и мультиплексором MUX с организацией "2 k→ 1" (рис. 8). Рис. 8. Матрицы М с организацией 4 х 4· 2 Таким образом, активизированный выход дешифратора DCX выбирает строку, а младшие разряды адреса с помощью мультиплексоров обеспечивают формирование выходного слова DO (по одному разряду из каждой группы).

Дешифратор DCX обслуживает 2 к –r строк, каждая из которых хранит 2 к m разрядных слов. В каждой группе хранятся значения одноименных разрядов и обслуживается она своим буфером BD и мультиплексором MUX с организацией "2 k→ 1" (рис. 8). Рис. 8. Матрицы М с организацией 4 х 4· 2 Таким образом, активизированный выход дешифратора DCX выбирает строку, а младшие разряды адреса с помощью мультиплексоров обеспечивают формирование выходного слова DO (по одному разряду из каждой группы).

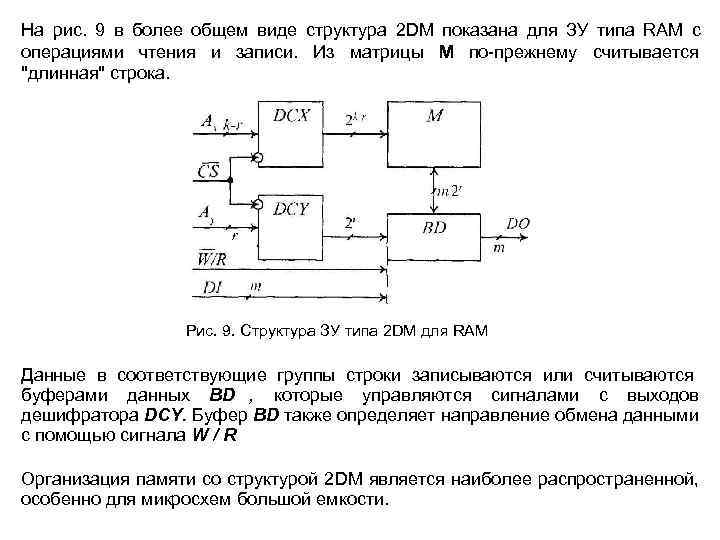

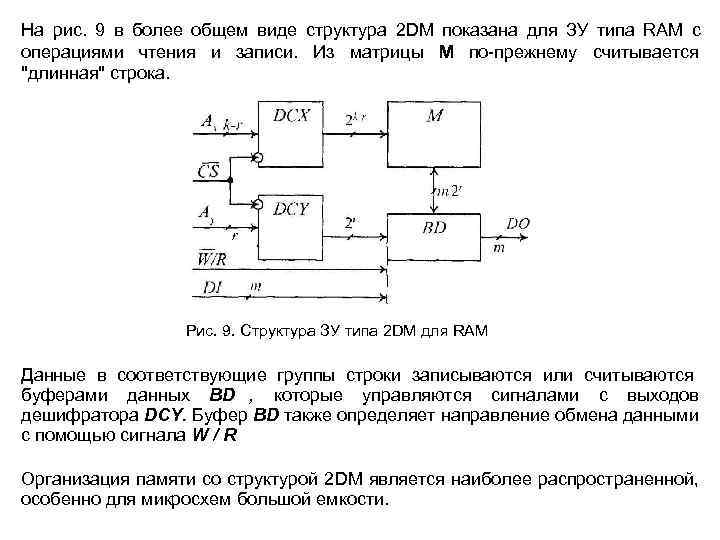

На рис. 9 в более общем виде структура 2 DM показана для ЗУ типа RAM с операциями чтения и записи. Из матрицы М по-прежнему считывается "длинная" строка. Рис. 9. Структура ЗУ типа 2 DM для RAM Данные в соответствующие группы строки записываются или считываются буферами данных BD , которые управляются сигналами с выходов дешифратора DCY. Буфер BD также определяет направление обмена данными с помощью сигнала W / R Организация памяти со структурой 2 DM является наиболее распространенной, особенно для микросхем большой емкости.

На рис. 9 в более общем виде структура 2 DM показана для ЗУ типа RAM с операциями чтения и записи. Из матрицы М по-прежнему считывается "длинная" строка. Рис. 9. Структура ЗУ типа 2 DM для RAM Данные в соответствующие группы строки записываются или считываются буферами данных BD , которые управляются сигналами с выходов дешифратора DCY. Буфер BD также определяет направление обмена данными с помощью сигнала W / R Организация памяти со структурой 2 DM является наиболее распространенной, особенно для микросхем большой емкости.

Память с последовательным доступом строится либо с использованием продвижения данных в цепочке элементов (по подобию с регистрами сдвига), либо с хранением данных в адресном ЗУ с необходимым управлением адресом доступа. Основными представителями этого вида памяти являются: • видеопамять, • буфер FIFO (очередь), • буфер LIFO (стек).

Память с последовательным доступом строится либо с использованием продвижения данных в цепочке элементов (по подобию с регистрами сдвига), либо с хранением данных в адресном ЗУ с необходимым управлением адресом доступа. Основными представителями этого вида памяти являются: • видеопамять, • буфер FIFO (очередь), • буфер LIFO (стек).

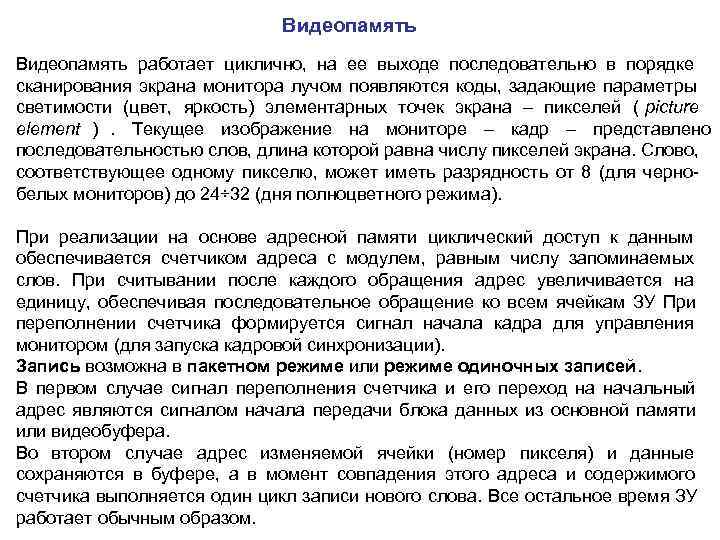

Видеопамять работает циклично, на ее выходе последовательно в порядке сканирования экрана монитора лучом появляются коды, задающие параметры светимости (цвет, яркость) элементарных точек экрана – пикселей ( picture element ). Текущее изображение на мониторе – кадр – представлено последовательностью слов, длина которой равна числу пикселей экрана. Слово, соответствующее одному пикселю, может иметь разрядность от 8 (для черно- белых мониторов) до 24÷ 32 (дня полноцветного режима). При реализации на основе адресной памяти циклический доступ к данным обеспечивается счетчиком адреса с модулем, равным числу запоминаемых слов. При считывании после каждого обращения адрес увеличивается на единицу, обеспечивая последовательное обращение ко всем ячейкам ЗУ При переполнении счетчика формируется сигнал начала кадра для управления монитором (для запуска кадровой синхронизации). Запись возможна в пакетном режиме или режиме одиночных записей. В первом случае сигнал переполнения счетчика и его переход на начальный адрес являются сигналом начала передачи блока данных из основной памяти или видеобуфера. Во втором случае адрес изменяемой ячейки (номер пикселя) и данные сохраняются в буфере, а в момент совпадения этого адреса и содержимого счетчика выполняется один цикл записи нового слова. Все остальное время ЗУ работает обычным образом.

Видеопамять работает циклично, на ее выходе последовательно в порядке сканирования экрана монитора лучом появляются коды, задающие параметры светимости (цвет, яркость) элементарных точек экрана – пикселей ( picture element ). Текущее изображение на мониторе – кадр – представлено последовательностью слов, длина которой равна числу пикселей экрана. Слово, соответствующее одному пикселю, может иметь разрядность от 8 (для черно- белых мониторов) до 24÷ 32 (дня полноцветного режима). При реализации на основе адресной памяти циклический доступ к данным обеспечивается счетчиком адреса с модулем, равным числу запоминаемых слов. При считывании после каждого обращения адрес увеличивается на единицу, обеспечивая последовательное обращение ко всем ячейкам ЗУ При переполнении счетчика формируется сигнал начала кадра для управления монитором (для запуска кадровой синхронизации). Запись возможна в пакетном режиме или режиме одиночных записей. В первом случае сигнал переполнения счетчика и его переход на начальный адрес являются сигналом начала передачи блока данных из основной памяти или видеобуфера. Во втором случае адрес изменяемой ячейки (номер пикселя) и данные сохраняются в буфере, а в момент совпадения этого адреса и содержимого счетчика выполняется один цикл записи нового слова. Все остальное время ЗУ работает обычным образом.

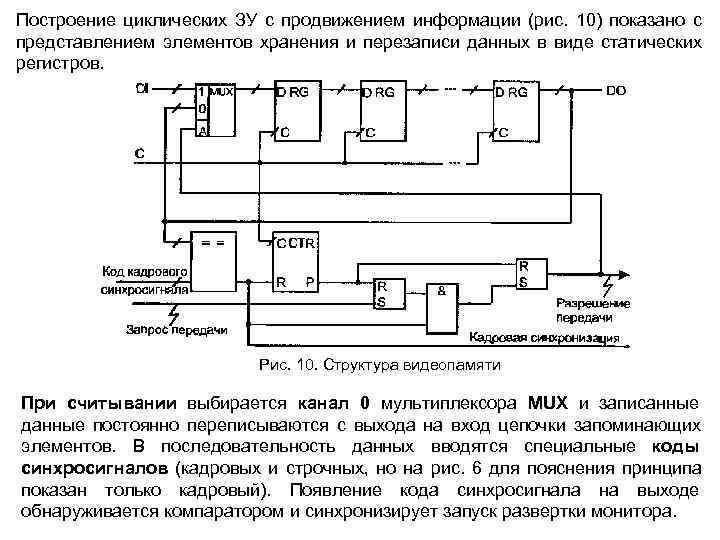

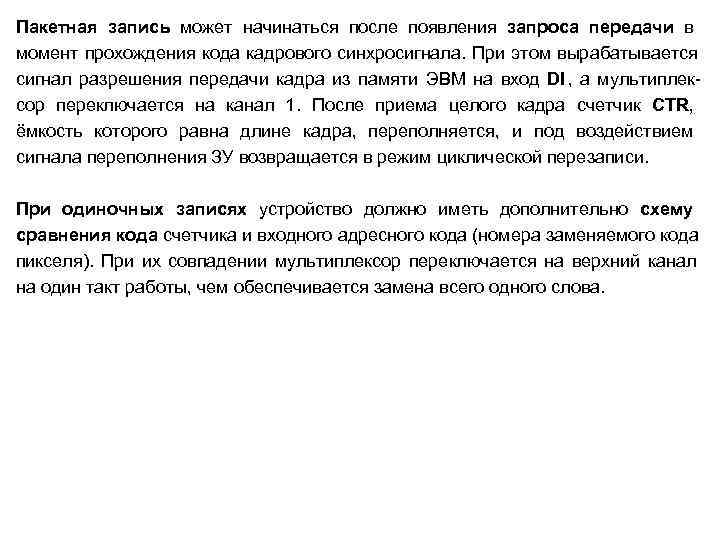

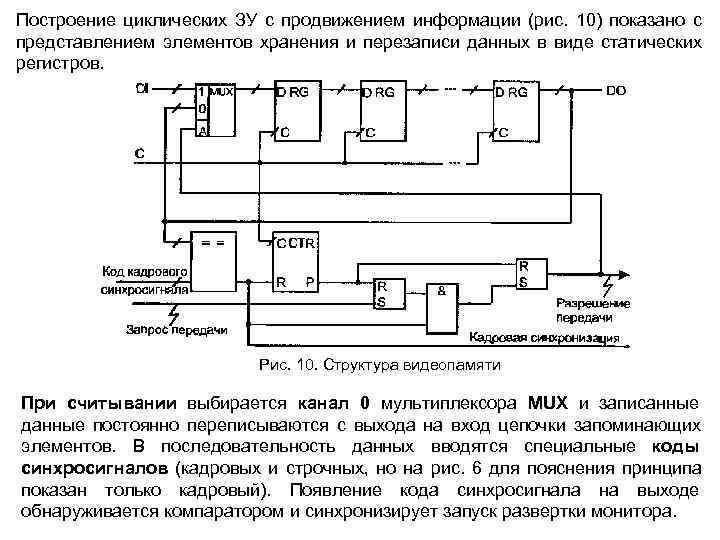

Построение циклических ЗУ с продвижением информации (рис. 10) показано с представлением элементов хранения и перезаписи данных в виде статических регистров. Рис. 10. Структура видеопамяти При считывании выбирается канал 0 мультиплексора MUX и записанные данные постоянно переписываются с выхода на вход цепочки запоминающих элементов. В последовательность данных вводятся специальные коды синхросигналов (кадровых и строчных, но на рис. 6 для пояснения принципа показан только кадровый). Появление кода синхросигнала на выходе обнаруживается компаратором и синхронизирует запуск развертки монитора.

Построение циклических ЗУ с продвижением информации (рис. 10) показано с представлением элементов хранения и перезаписи данных в виде статических регистров. Рис. 10. Структура видеопамяти При считывании выбирается канал 0 мультиплексора MUX и записанные данные постоянно переписываются с выхода на вход цепочки запоминающих элементов. В последовательность данных вводятся специальные коды синхросигналов (кадровых и строчных, но на рис. 6 для пояснения принципа показан только кадровый). Появление кода синхросигнала на выходе обнаруживается компаратором и синхронизирует запуск развертки монитора.

Пакетная запись может начинаться после появления запроса передачи в момент прохождения кода кадрового синхросигнала. При этом вырабатывается сигнал разрешения передачи кадра из памяти ЭВМ на вход DI , а мультиплек- сор переключается на канал 1. После приема целого кадра счетчик CTR, ёмкость которого равна длине кадра, переполняется, и под воздействием сигнала переполнения ЗУ возвращается в режим циклической перезаписи. При одиночных записях устройство должно иметь дополнительно схему сравнения кода счетчика и входного адресного кода (номера заменяемого кода пикселя). При их совпадении мультиплексор переключается на верхний канал на один такт работы, чем обеспечивается замена всего одного слова.

Пакетная запись может начинаться после появления запроса передачи в момент прохождения кода кадрового синхросигнала. При этом вырабатывается сигнал разрешения передачи кадра из памяти ЭВМ на вход DI , а мультиплек- сор переключается на канал 1. После приема целого кадра счетчик CTR, ёмкость которого равна длине кадра, переполняется, и под воздействием сигнала переполнения ЗУ возвращается в режим циклической перезаписи. При одиночных записях устройство должно иметь дополнительно схему сравнения кода счетчика и входного адресного кода (номера заменяемого кода пикселя). При их совпадении мультиплексор переключается на верхний канал на один такт работы, чем обеспечивается замена всего одного слова.

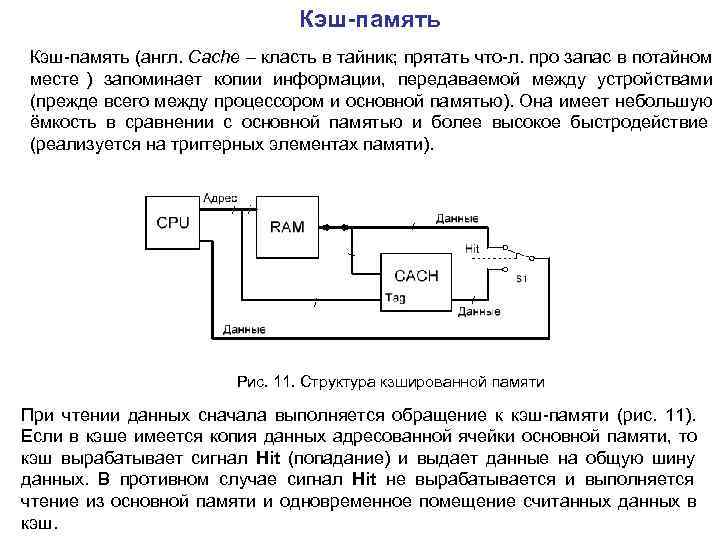

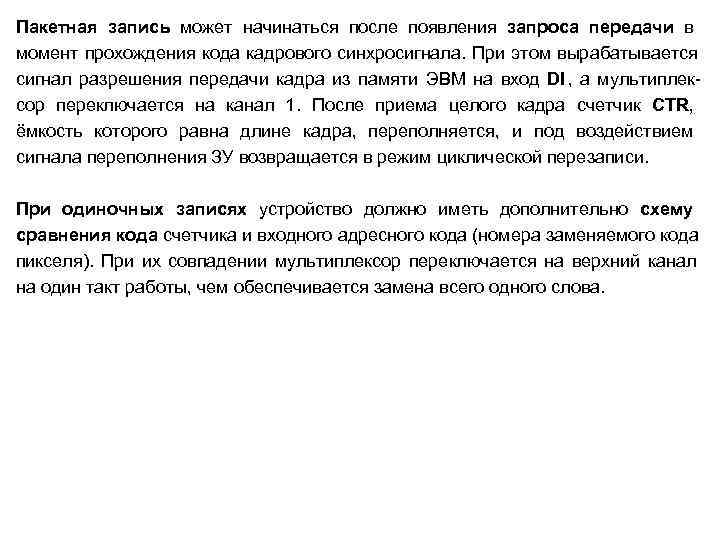

Кэш-память (англ. Cache – класть в тайник; прятать что-л. про запас в потайном месте ) запоминает копии информации, передаваемой между устройствами (прежде всего между процессором и основной памятью). Она имеет небольшую ёмкость в сравнении с основной памятью и более высокое быстродействие (реализуется на триггерных элементах памяти). Рис. 11. Структура кзшированной памяти При чтении данных сначала выполняется обращение к кэш-памяти (рис. 11). Если в кэше имеется копия данных адресованной ячейки основной памяти, то кэш вырабатывает сигнал Hit (попадание) и выдает данные на общую шину данных. В противном случае сигнал Hit не вырабатывается и выполняется чтение из основной памяти и одновременное помещение считанных данных в кэш.

Кэш-память (англ. Cache – класть в тайник; прятать что-л. про запас в потайном месте ) запоминает копии информации, передаваемой между устройствами (прежде всего между процессором и основной памятью). Она имеет небольшую ёмкость в сравнении с основной памятью и более высокое быстродействие (реализуется на триггерных элементах памяти). Рис. 11. Структура кзшированной памяти При чтении данных сначала выполняется обращение к кэш-памяти (рис. 11). Если в кэше имеется копия данных адресованной ячейки основной памяти, то кэш вырабатывает сигнал Hit (попадание) и выдает данные на общую шину данных. В противном случае сигнал Hit не вырабатывается и выполняется чтение из основной памяти и одновременное помещение считанных данных в кэш.

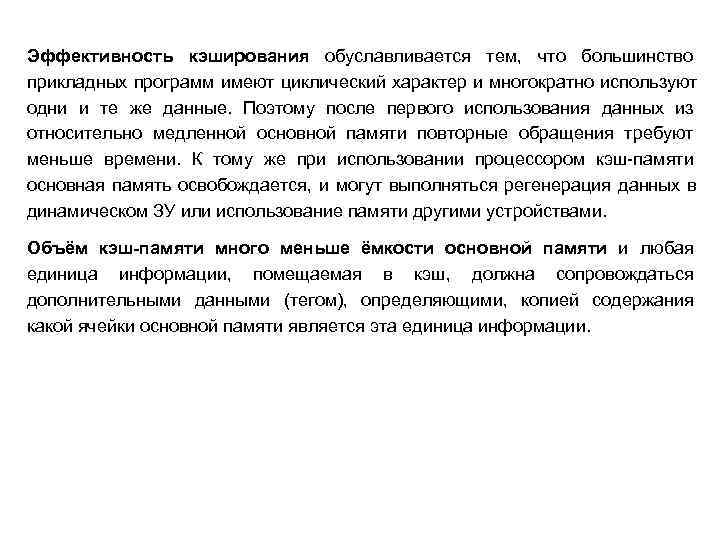

Эффективность кэширования обуславливается тем, что большинство прикладных программ имеют циклический характер и многократно используют одни и те же данные. Поэтому после первого использования данных из относительно медленной основной памяти повторные обращения требуют меньше времени. К тому же при использовании процессором кэш-памяти основная память освобождается, и могут выполняться регенерация данных в динамическом ЗУ или использование памяти другими устройствами. Объём кэш-памяти много меньше ёмкости основной памяти и любая единица информации, помещаемая в кэш, должна сопровождаться дополнительными данными (тегом), определяющими, копией содержания какой ячейки основной памяти является эта единица информации.

Эффективность кэширования обуславливается тем, что большинство прикладных программ имеют циклический характер и многократно используют одни и те же данные. Поэтому после первого использования данных из относительно медленной основной памяти повторные обращения требуют меньше времени. К тому же при использовании процессором кэш-памяти основная память освобождается, и могут выполняться регенерация данных в динамическом ЗУ или использование памяти другими устройствами. Объём кэш-памяти много меньше ёмкости основной памяти и любая единица информации, помещаемая в кэш, должна сопровождаться дополнительными данными (тегом), определяющими, копией содержания какой ячейки основной памяти является эта единица информации.

Организация доступа к данным в кэш-памяти 1. Полностью ассоциативная кэш-память (FACM, Fully Associated Cache Memory), структура которой показана на рис. 12, каждая ячейка хранит данные, и в поле "тег" – полный физический адрес информации, копия которой записана. При любых обменах физический адрес запрашиваемой информации сравнивается с полями "тег" всех ячеек и при совпадении их в любой ячейке устанавливается сигнал Hit. При чтении и значении сигнала Hit = 1 данные выдаются на шину данных, если же совпадений нет (Hit = 0), то при чтении из основной памяти данные вместе с адресом помешаются в свободную или наиболее давно не используемую ячейку кэш-памяти. При записи данные вместе с адресом сначала, как правило, размещаются в кэш-памяти (в обнаруженную ячейку при Hit = 1 и свободную при Hit = 0) Копирование данных в основную память выполняется под управлением специального Рис. 12. Структура полностью контроллера, когда нет обращений к ассоциативной кэш-памяти памяти.

Организация доступа к данным в кэш-памяти 1. Полностью ассоциативная кэш-память (FACM, Fully Associated Cache Memory), структура которой показана на рис. 12, каждая ячейка хранит данные, и в поле "тег" – полный физический адрес информации, копия которой записана. При любых обменах физический адрес запрашиваемой информации сравнивается с полями "тег" всех ячеек и при совпадении их в любой ячейке устанавливается сигнал Hit. При чтении и значении сигнала Hit = 1 данные выдаются на шину данных, если же совпадений нет (Hit = 0), то при чтении из основной памяти данные вместе с адресом помешаются в свободную или наиболее давно не используемую ячейку кэш-памяти. При записи данные вместе с адресом сначала, как правило, размещаются в кэш-памяти (в обнаруженную ячейку при Hit = 1 и свободную при Hit = 0) Копирование данных в основную память выполняется под управлением специального Рис. 12. Структура полностью контроллера, когда нет обращений к ассоциативной кэш-памяти памяти.

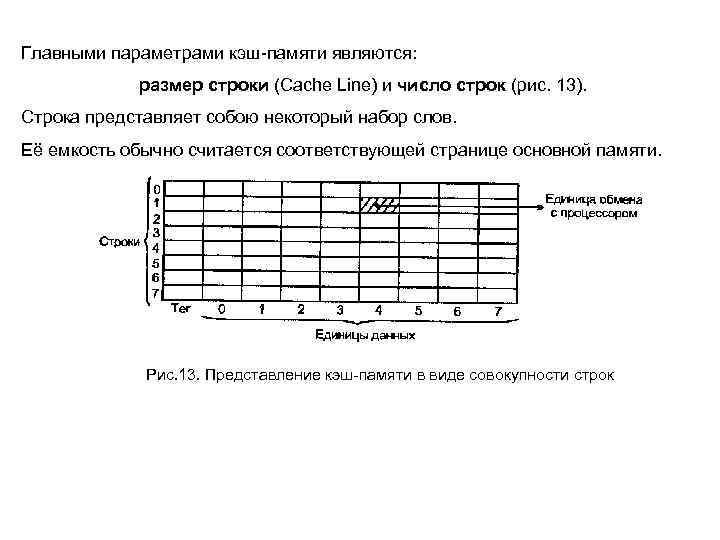

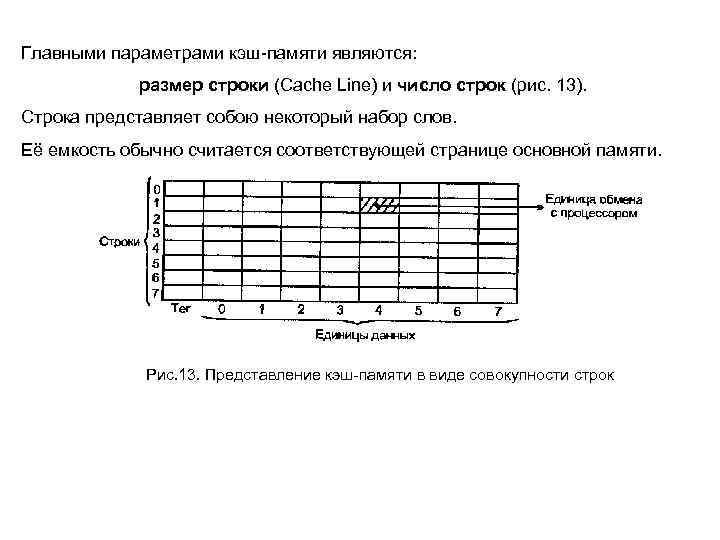

Главными параметрами кэш-памяти являются: размер строки (Cache Line) и число строк (рис. 13). Строка представляет собою некоторый набор слов. Её емкость обычно считается соответствующей странице основной памяти. Рис. 13. Представление кэш-памяти в виде совокупности строк

Главными параметрами кэш-памяти являются: размер строки (Cache Line) и число строк (рис. 13). Строка представляет собою некоторый набор слов. Её емкость обычно считается соответствующей странице основной памяти. Рис. 13. Представление кэш-памяти в виде совокупности строк

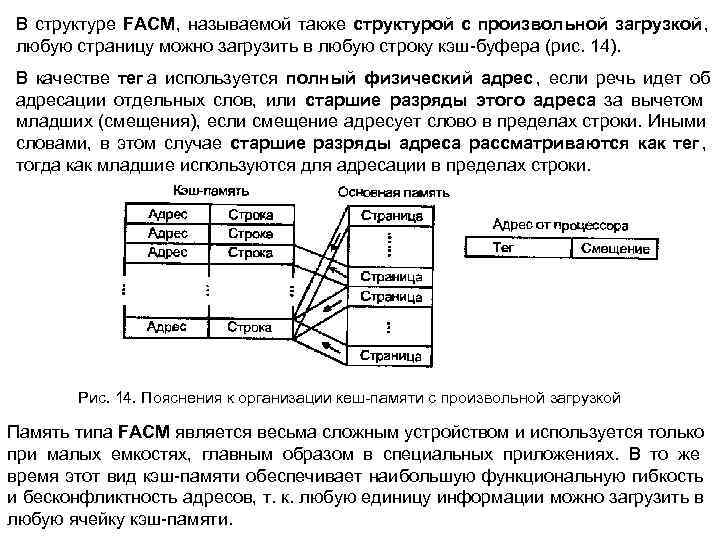

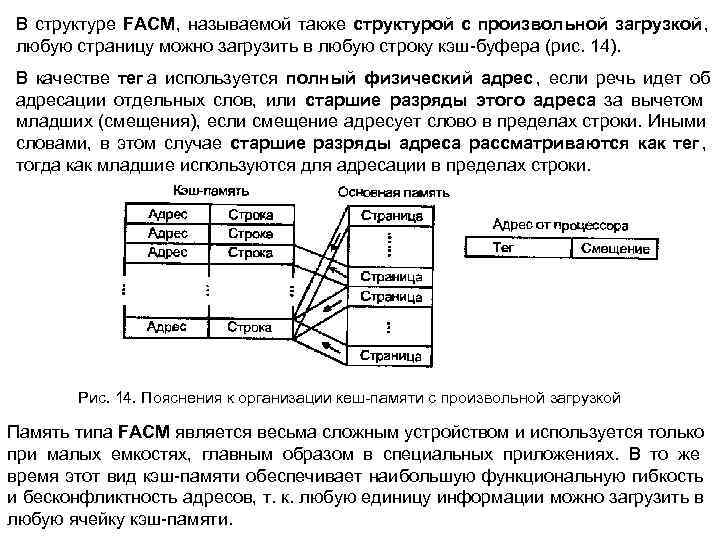

В структуре FACM , называемой также структурой с произвольной загрузкой , любую страницу можно загрузить в любую строку кэш-буфера (рис. 14). В качестве тег а используется полный физический адрес , если речь идет об адресации отдельных слов, или старшие разряды этого адреса за вычетом младших (смещения), если смещение адресует слово в пределах строки. Иными словами, в этом случае старшие разряды адреса рассматриваются как тег , тогда как младшие используются для адресации в пределах строки. Рис. 14. Пояснения к организации кеш-памяти с произвольной загрузкой Память типа FACM является весьма сложным устройством и используется только при малых емкостях, главным образом в специальных приложениях. В то же время этот вид кэш-памяти обеспечивает наибольшую функциональную гибкость и бесконфликтность адресов, т. к. любую единицу информации можно загрузить в любую ячейку кэш-памяти.

В структуре FACM , называемой также структурой с произвольной загрузкой , любую страницу можно загрузить в любую строку кэш-буфера (рис. 14). В качестве тег а используется полный физический адрес , если речь идет об адресации отдельных слов, или старшие разряды этого адреса за вычетом младших (смещения), если смещение адресует слово в пределах строки. Иными словами, в этом случае старшие разряды адреса рассматриваются как тег , тогда как младшие используются для адресации в пределах строки. Рис. 14. Пояснения к организации кеш-памяти с произвольной загрузкой Память типа FACM является весьма сложным устройством и используется только при малых емкостях, главным образом в специальных приложениях. В то же время этот вид кэш-памяти обеспечивает наибольшую функциональную гибкость и бесконфликтность адресов, т. к. любую единицу информации можно загрузить в любую ячейку кэш-памяти.

Сложность FACM заставляет искать иные структуры кэш-памяти, более экономичные по затратам аппаратных средств на их реализацию. К числу таких структур относятся: • кэш-память с прямым размещением и • кэш-память с наборно-ассоциативной архитектурой (с ассоциацией по нескольким направлениям).

Сложность FACM заставляет искать иные структуры кэш-памяти, более экономичные по затратам аппаратных средств на их реализацию. К числу таких структур относятся: • кэш-память с прямым размещением и • кэш-память с наборно-ассоциативной архитектурой (с ассоциацией по нескольким направлениям).

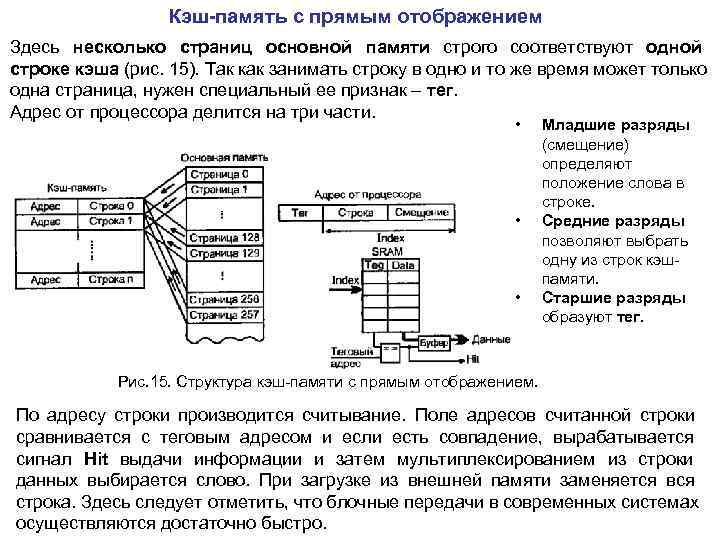

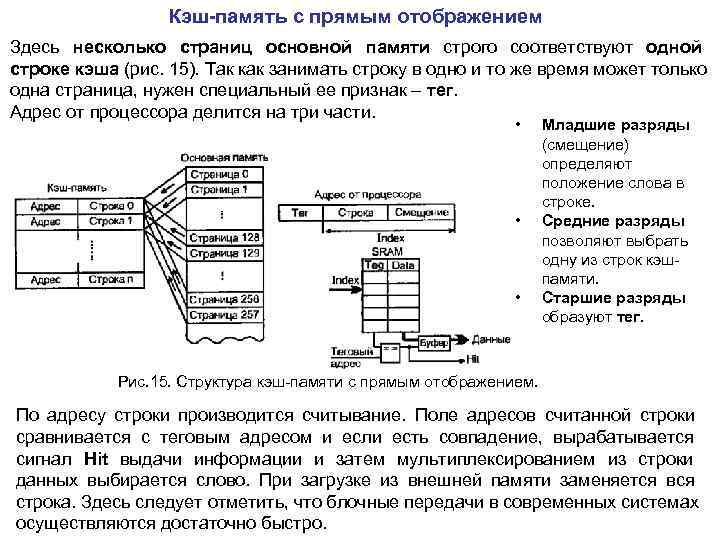

Кэш-память с прямым отображением Здесь несколько страниц основной памяти строго соответствуют одной строке кэша (рис. 15). Так как занимать строку в одно и то же время может только одна страница, нужен специальный ее признак – тег. Адрес от процессора делится на три части. • Младшие разряды (смещение) определяют положение слова в строке. • Средние разряды позволяют выбрать одну из строк кэш- памяти. • Старшие разряды образуют тег. Рис. 15. Структура кэш-памяти с прямым отображением. По адресу строки производится считывание. Поле адресов считанной строки сравнивается с теговым адресом и если есть совпадение, вырабатывается сигнал Hit выдачи информации и затем мультиплексированием из строки данных выбирается слово. При загрузке из внешней памяти заменяется вся строка. Здесь следует отметить, что блочные передачи в современных системах осуществляются достаточно быстро.

Кэш-память с прямым отображением Здесь несколько страниц основной памяти строго соответствуют одной строке кэша (рис. 15). Так как занимать строку в одно и то же время может только одна страница, нужен специальный ее признак – тег. Адрес от процессора делится на три части. • Младшие разряды (смещение) определяют положение слова в строке. • Средние разряды позволяют выбрать одну из строк кэш- памяти. • Старшие разряды образуют тег. Рис. 15. Структура кэш-памяти с прямым отображением. По адресу строки производится считывание. Поле адресов считанной строки сравнивается с теговым адресом и если есть совпадение, вырабатывается сигнал Hit выдачи информации и затем мультиплексированием из строки данных выбирается слово. При загрузке из внешней памяти заменяется вся строка. Здесь следует отметить, что блочные передачи в современных системах осуществляются достаточно быстро.

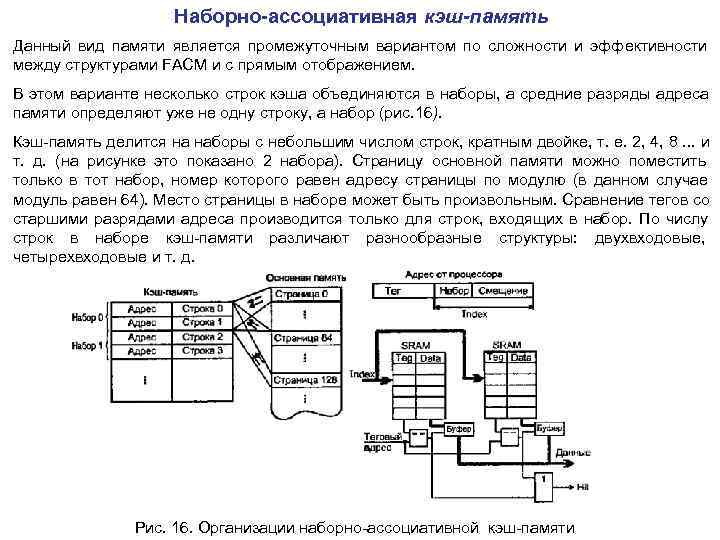

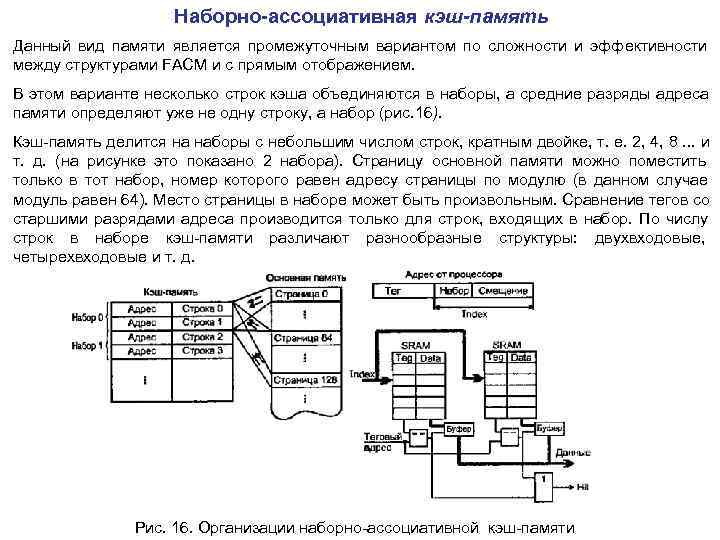

Наборно-ассоциативная кэш-память Данный вид памяти является промежуточным вариантом по сложности и эффективности между структурами FACM и с прямым отображением. В этом варианте несколько строк кэша объединяются в наборы, а средние разряды адреса памяти определяют уже не одну строку, а набор (рис. 16). Кэш-память делится на наборы с небольшим числом строк, кратным двойке, т. е. 2, 4, 8. . . и т. д. (на рисунке это показано 2 набора). Страницу основной памяти можно поместить только в тот набор, номер которого равен адресу страницы по модулю (в данном случае модуль равен 64). Место страницы в наборе может быть произвольным. Сравнение тегов со старшими разрядами адреса производится только для строк, входящих в набор. По числу строк в наборе кэш-памяти различают разнообразные структуры: двухвходовые, четырехвходовые и т. д. Рис. 16. Организации наборно-ассоциативной кэш-памяти

Наборно-ассоциативная кэш-память Данный вид памяти является промежуточным вариантом по сложности и эффективности между структурами FACM и с прямым отображением. В этом варианте несколько строк кэша объединяются в наборы, а средние разряды адреса памяти определяют уже не одну строку, а набор (рис. 16). Кэш-память делится на наборы с небольшим числом строк, кратным двойке, т. е. 2, 4, 8. . . и т. д. (на рисунке это показано 2 набора). Страницу основной памяти можно поместить только в тот набор, номер которого равен адресу страницы по модулю (в данном случае модуль равен 64). Место страницы в наборе может быть произвольным. Сравнение тегов со старшими разрядами адреса производится только для строк, входящих в набор. По числу строк в наборе кэш-памяти различают разнообразные структуры: двухвходовые, четырехвходовые и т. д. Рис. 16. Организации наборно-ассоциативной кэш-памяти

Для взятого примера используются два отдельных блока памяти для чётных строк и нечётных строк. Одновременно выбираются четные и нечетные строки (слова в них). Считывание идет от того блока, где имеется совпадение тега и тегового адреса. При этом из строки через смещение выбирается адресованное слово. При отсутствии совпадений происходит обращение к основной памяти и замещение строки в одном из блоков кэша. Наборно-ассоциативный кэш по сравнению с кэшем с прямым отображением имеет несколько удлиненный тег (в приведённом при мере на 1 разряд). Возможность свободного размещения страниц в наборе позволяет сформировать в кэше лучший состав страниц, т. к. имеется возможность выбрать ту или иную заменяемую страницу. В современных микропроцессорных системах кэш первого уровня ( внутрипроцессорный ), обозначаемый L 1 (от английского слова Level ), обычно имеет наборно-ассоциативную структуру, а кэш второго уровня L 2 (внешний) — структуру с прямым размещением. Ряд фирм выпускают микросхемы ассоциативной памяти. Например, одна из микросхем фирмы Cyrix имеет 4 К строк, 15 -разрядный теговый адрес и 16 -разрядный выход. Для построения кэш-памяти используют чаше всего обычные SRAM в сочетании с кэш- контроллерами. В высокопроизводительном микропроцессоре Power 3 фирмы IBM использован кэш наборно-ассоциативного типа емкостью 32 Кбайта для команд и 64 Кбайта для данных на 128 направлений. Для связей с кэшем второго уровня L 2 в системе Power 3 применена 256 -разрядная шина. Емкость кэша L 2 от 1 до 16 Мбайт. Кстати говоря, именно МП Power 3 использован в суперкомпьютере, который сумел обыграть чемпиона мира по шахматам Гарри Каспарова.

Для взятого примера используются два отдельных блока памяти для чётных строк и нечётных строк. Одновременно выбираются четные и нечетные строки (слова в них). Считывание идет от того блока, где имеется совпадение тега и тегового адреса. При этом из строки через смещение выбирается адресованное слово. При отсутствии совпадений происходит обращение к основной памяти и замещение строки в одном из блоков кэша. Наборно-ассоциативный кэш по сравнению с кэшем с прямым отображением имеет несколько удлиненный тег (в приведённом при мере на 1 разряд). Возможность свободного размещения страниц в наборе позволяет сформировать в кэше лучший состав страниц, т. к. имеется возможность выбрать ту или иную заменяемую страницу. В современных микропроцессорных системах кэш первого уровня ( внутрипроцессорный ), обозначаемый L 1 (от английского слова Level ), обычно имеет наборно-ассоциативную структуру, а кэш второго уровня L 2 (внешний) — структуру с прямым размещением. Ряд фирм выпускают микросхемы ассоциативной памяти. Например, одна из микросхем фирмы Cyrix имеет 4 К строк, 15 -разрядный теговый адрес и 16 -разрядный выход. Для построения кэш-памяти используют чаше всего обычные SRAM в сочетании с кэш- контроллерами. В высокопроизводительном микропроцессоре Power 3 фирмы IBM использован кэш наборно-ассоциативного типа емкостью 32 Кбайта для команд и 64 Кбайта для данных на 128 направлений. Для связей с кэшем второго уровня L 2 в системе Power 3 применена 256 -разрядная шина. Емкость кэша L 2 от 1 до 16 Мбайт. Кстати говоря, именно МП Power 3 использован в суперкомпьютере, который сумел обыграть чемпиона мира по шахматам Гарри Каспарова.