Основные определения Микропроцессор —устройство, отвечающее за

tmse_2012_lekcii_1_4.pptx

- Размер: 2.2 Мб

- Автор:

- Количество слайдов: 48

Описание презентации Основные определения Микропроцессор —устройство, отвечающее за по слайдам

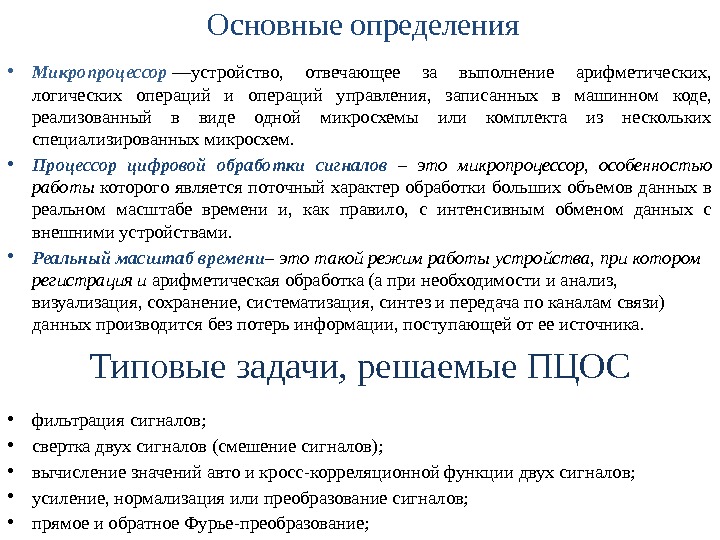

Основные определения • Микропроцессор —устройство, отвечающее за выполнение арифметических, логических операций и операций управления, записанных в машинном коде, реализованный в виде одной микросхемы или комплекта из нескольких специализированных микросхем. • Процессор цифровой обработки сигналов – это микропроцессор, особенностью работы которого является поточный характер обработки больших объемов данных в реальном масштабе времени и, как правило, с интенсивным обменом данных с внешними устройствами. • Реальный масштаб времени – это такой режим работы устройства, при котором регистрация и арифметическая обработка (а при необходимости и анализ, визуализация, сохранение, систематизация, синтез и передача по каналам связи) данных производится без потерь информации, поступающей от ее источника. Типовые задачи, решаемые ПЦОС • фильтрация сигналов; • свертка двух сигналов (смешение сигналов); • вычисление значений авто и кросс-корреляционной функции двух сигналов; • усиление, нормализация или преобразование сигналов; • прямое и обратное Фурье-преобразование;

Основные определения • Микропроцессор —устройство, отвечающее за выполнение арифметических, логических операций и операций управления, записанных в машинном коде, реализованный в виде одной микросхемы или комплекта из нескольких специализированных микросхем. • Процессор цифровой обработки сигналов – это микропроцессор, особенностью работы которого является поточный характер обработки больших объемов данных в реальном масштабе времени и, как правило, с интенсивным обменом данных с внешними устройствами. • Реальный масштаб времени – это такой режим работы устройства, при котором регистрация и арифметическая обработка (а при необходимости и анализ, визуализация, сохранение, систематизация, синтез и передача по каналам связи) данных производится без потерь информации, поступающей от ее источника. Типовые задачи, решаемые ПЦОС • фильтрация сигналов; • свертка двух сигналов (смешение сигналов); • вычисление значений авто и кросс-корреляционной функции двух сигналов; • усиление, нормализация или преобразование сигналов; • прямое и обратное Фурье-преобразование;

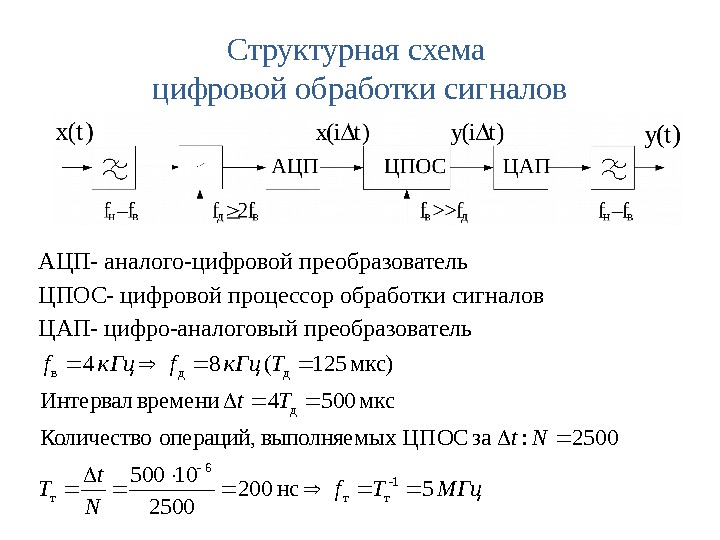

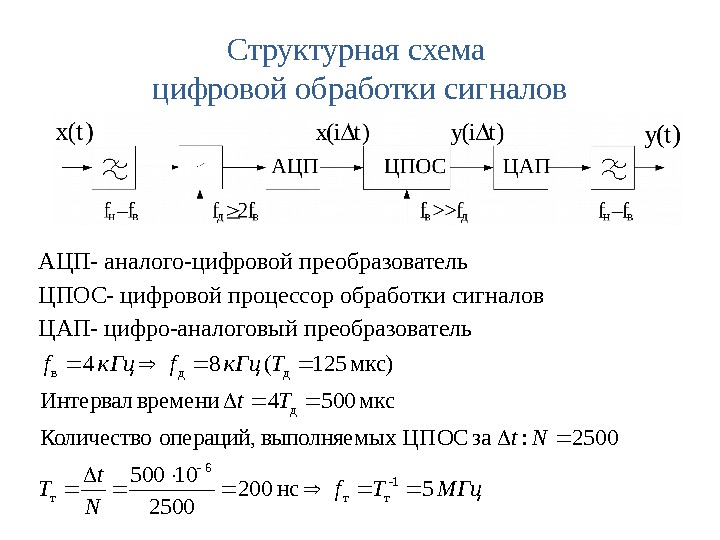

Структурная схема цифровой обработки сигналов АЦП- аналого-цифровой преобразователь ЦПОС- цифровой процессор обработки сигналов ЦАП- цифро-аналоговый преобразователь. МГц. Tf N t T Nt Tt Tк. Гцf 5 нс 200 2500 10500 2500 : за ЦПОСх выполняемы операций, Количество мкс 5004 времени Интервал мкс) 125( 8 4 1 — тт6 т дддв

Структурная схема цифровой обработки сигналов АЦП- аналого-цифровой преобразователь ЦПОС- цифровой процессор обработки сигналов ЦАП- цифро-аналоговый преобразователь. МГц. Tf N t T Nt Tt Tк. Гцf 5 нс 200 2500 10500 2500 : за ЦПОСх выполняемы операций, Количество мкс 5004 времени Интервал мкс) 125( 8 4 1 — тт6 т дддв

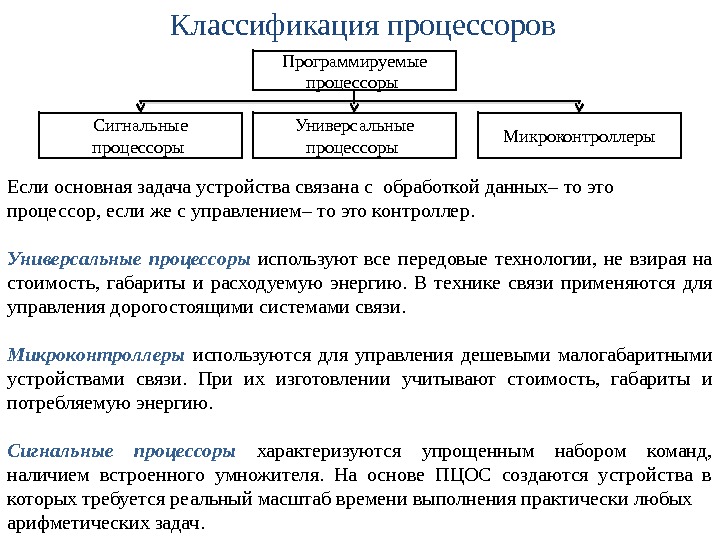

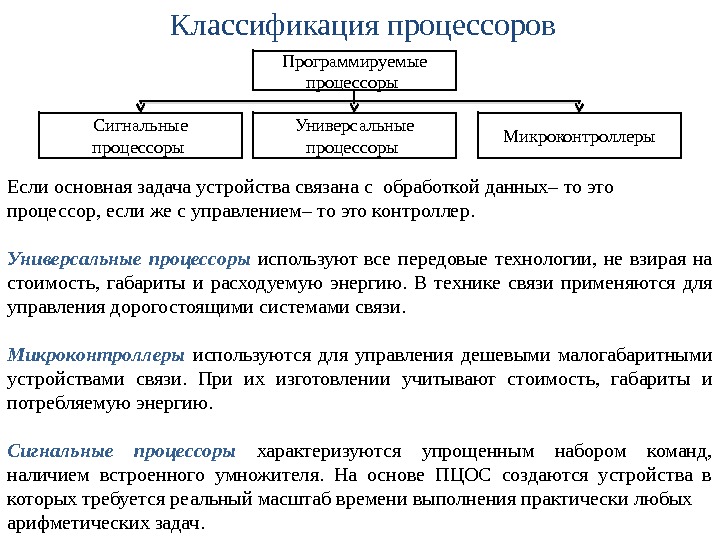

Если основная задача устройства связана с обработкой данных– то это процессор, если же с управлением– то это контроллер. Универсальные процессоры используют все передовые технологии, не взирая на стоимость, габариты и расходуемую энергию. В технике связи применяются для управления дорогостоящими системами связи. Микроконтроллеры используются для управления дешевыми малогабаритными устройствами связи. При их изготовлении учитывают стоимость, габариты и потребляемую энергию. Сигнальные процессоры характеризуются упрощенным набором команд, наличием встроенного умножителя. На основе ПЦОС создаются устройства в которых требуется реальный масштаб времени выполнения практически любых арифметических задач. Классификация процессоров Программируемые процессоры Сигнальные процессоры Универсальные процессоры Микроконтроллеры

Если основная задача устройства связана с обработкой данных– то это процессор, если же с управлением– то это контроллер. Универсальные процессоры используют все передовые технологии, не взирая на стоимость, габариты и расходуемую энергию. В технике связи применяются для управления дорогостоящими системами связи. Микроконтроллеры используются для управления дешевыми малогабаритными устройствами связи. При их изготовлении учитывают стоимость, габариты и потребляемую энергию. Сигнальные процессоры характеризуются упрощенным набором команд, наличием встроенного умножителя. На основе ПЦОС создаются устройства в которых требуется реальный масштаб времени выполнения практически любых арифметических задач. Классификация процессоров Программируемые процессоры Сигнальные процессоры Универсальные процессоры Микроконтроллеры

Архитектура процессоров Фон Неймана Гарвардская архитектура Модифицированная гарвардская архитектура

Архитектура процессоров Фон Неймана Гарвардская архитектура Модифицированная гарвардская архитектура

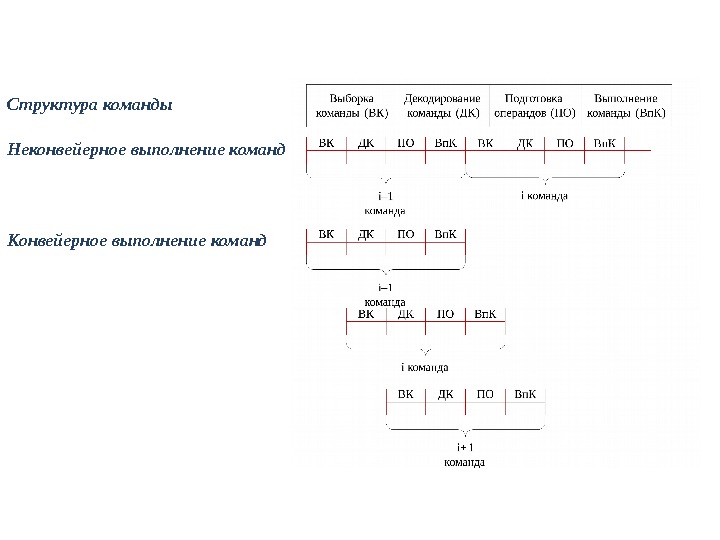

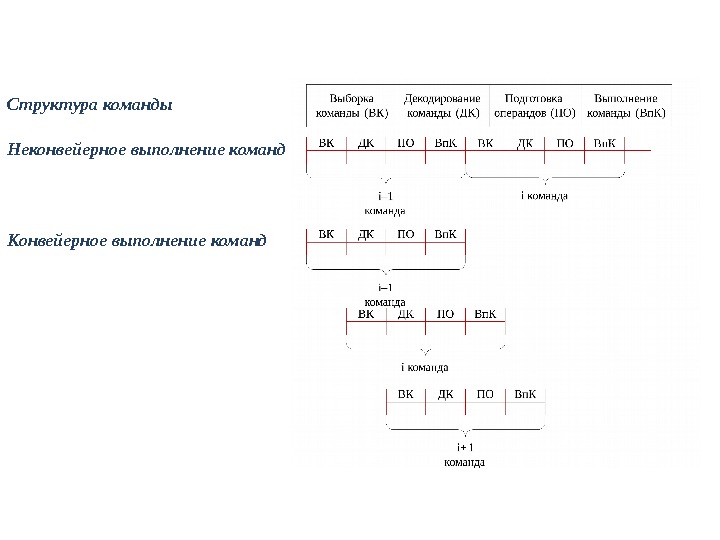

Неконвейерное выполнение команд. Структура команды Конвейерное выполнение команд

Неконвейерное выполнение команд. Структура команды Конвейерное выполнение команд

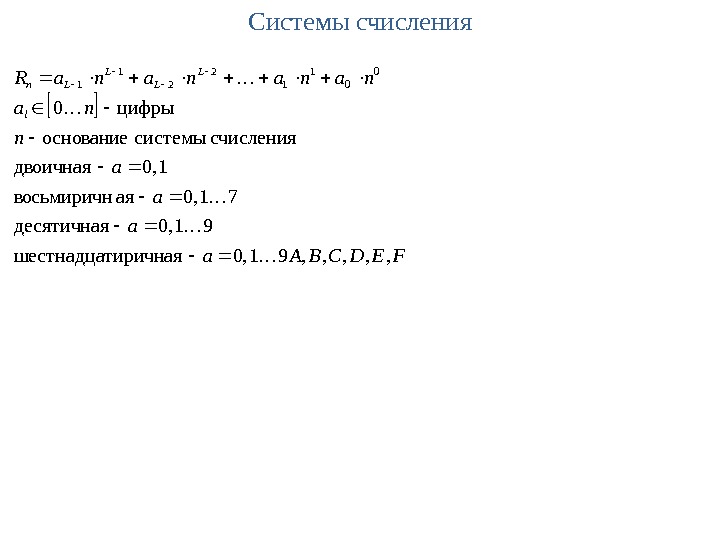

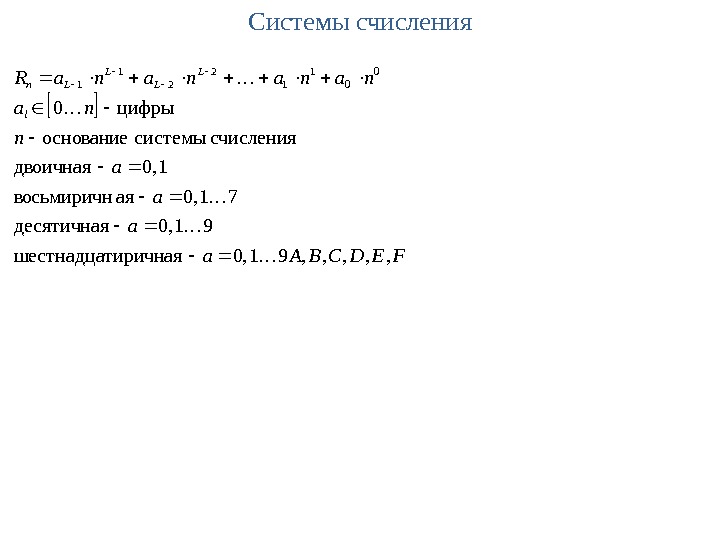

Системы счисления FEDCBAaa aan na nana. Rl L Ln , , , 91 , 0 иричнаяшестнадцат 91 , 0 десятичная 71 , 0 аявосьмиричн 1 , 0 двоичная счисления системы основание цифры

Системы счисления FEDCBAaa aan na nana. Rl L Ln , , , 91 , 0 иричнаяшестнадцат 91 , 0 десятичная 71 , 0 аявосьмиричн 1 , 0 двоичная счисления системы основание цифры

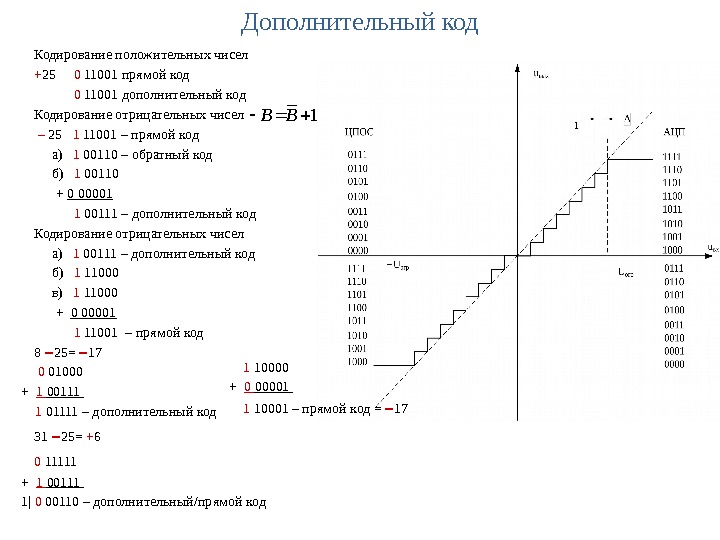

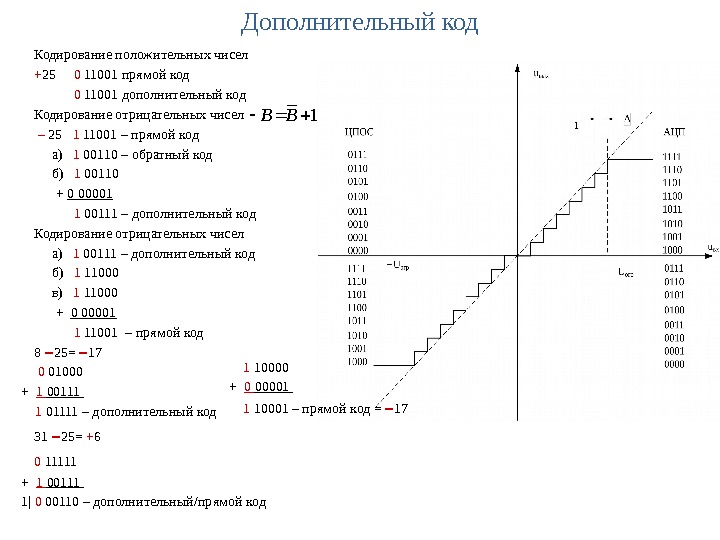

Дополнительный код Кодирование положительных чисел + 25 0 11001 прямой код 0 11001 дополнительный код Кодирование отрицательных чисел – 25 1 11001 – прямой код а) 1 00110 – обратный код б) 1 00110 + 0 00001 1 00111 – дополнительный код Кодирование отрицательных чисел а) 1 00111 – дополнительный код б) 1 11000 в) 1 11000 + 0 00001 1 11001 – прямой код 8 25= 17 0 01000 + 1 00111 1 01111 – дополнительный код 31 25= + 6 0 11111 + 1 00111 1| 0 00110 – дополнительный/прямой код 1 BB 1 10000 + 0 00001 1 10001 – прямой код =

Дополнительный код Кодирование положительных чисел + 25 0 11001 прямой код 0 11001 дополнительный код Кодирование отрицательных чисел – 25 1 11001 – прямой код а) 1 00110 – обратный код б) 1 00110 + 0 00001 1 00111 – дополнительный код Кодирование отрицательных чисел а) 1 00111 – дополнительный код б) 1 11000 в) 1 11000 + 0 00001 1 11001 – прямой код 8 25= 17 0 01000 + 1 00111 1 01111 – дополнительный код 31 25= + 6 0 11111 + 1 00111 1| 0 00110 – дополнительный/прямой код 1 BB 1 10000 + 0 00001 1 10001 – прямой код =

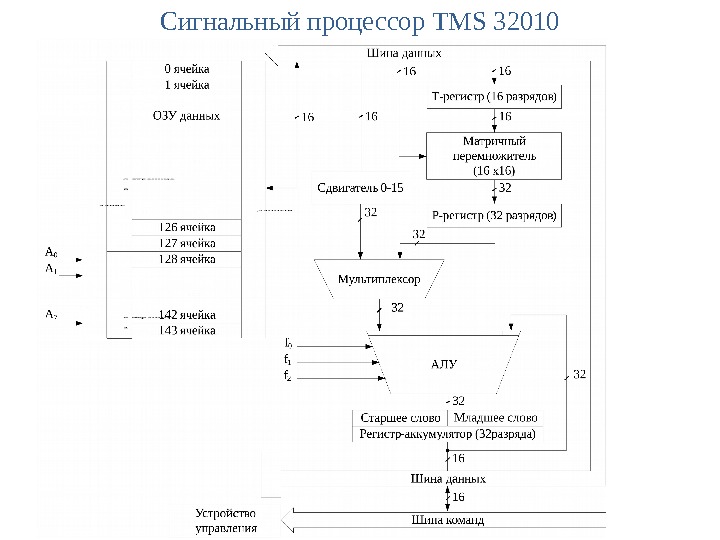

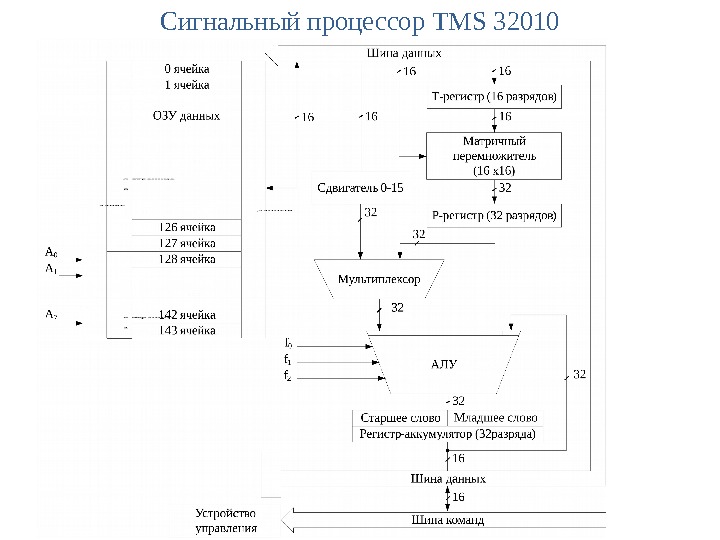

Сигнальный процессор TMS

Сигнальный процессор TMS

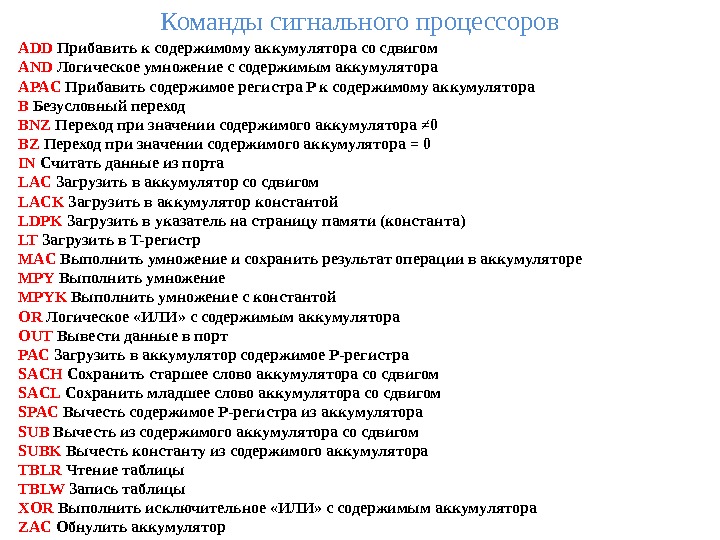

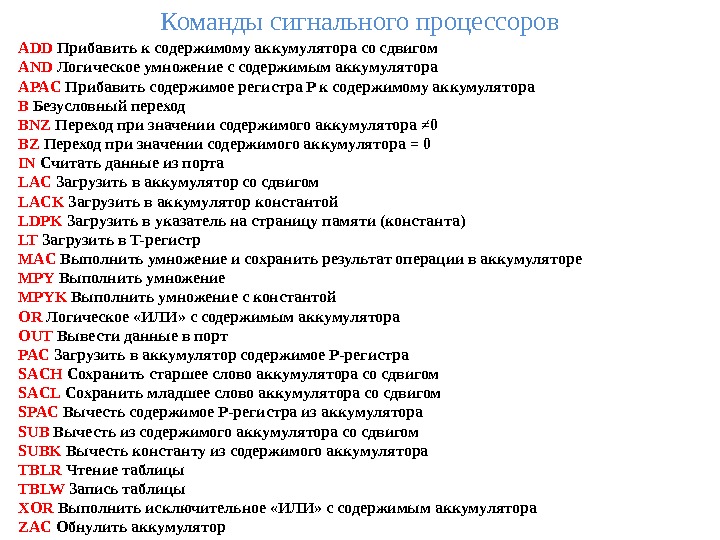

ADD Прибавить к содержимому аккумулятора со сдвигом AND Логическое умножение с содержимым аккумулятора APAC Прибавить содержимое регистра P к содержимому аккумулятора B Безусловный переход BNZ Переход при значении содержимого аккумулятора ≠ 0 BZ Переход при значении содержимого аккумулятора = 0 IN Считать данные из порта LAC Загрузить в аккумулятор со сдвигом LACK Загрузить в аккумулятор константой LDPK Загрузить в указатель на страницу памяти (константа) LT Загрузить в T-регистр MAC Выполнить умножение и сохранить результат операции в аккумуляторе MPY Выполнить умножение MPYK Выполнить умножение с константой OR Логическое «ИЛИ» с содержимым аккумулятора OUT Вывести данные в порт PAC Загрузить в аккумулятор содержимое Р-регистра SACH Сохранить старшее слово аккумулятора со сдвигом SACL Сохранить младшее слово аккумулятора со сдвигом SPAC Вычесть содержимое Р-регистра из аккумулятора SUB Вычесть из содержимого аккумулятора со сдвигом SUBK Вычесть константу из содержимого аккумулятора TBLR Чтение таблицы TBLW Запись таблицы XOR Выполнить исключительное «ИЛИ» с содержимым аккумулятора ZAC Обнулить аккумулятор Команды сигнального процессоров

ADD Прибавить к содержимому аккумулятора со сдвигом AND Логическое умножение с содержимым аккумулятора APAC Прибавить содержимое регистра P к содержимому аккумулятора B Безусловный переход BNZ Переход при значении содержимого аккумулятора ≠ 0 BZ Переход при значении содержимого аккумулятора = 0 IN Считать данные из порта LAC Загрузить в аккумулятор со сдвигом LACK Загрузить в аккумулятор константой LDPK Загрузить в указатель на страницу памяти (константа) LT Загрузить в T-регистр MAC Выполнить умножение и сохранить результат операции в аккумуляторе MPY Выполнить умножение MPYK Выполнить умножение с константой OR Логическое «ИЛИ» с содержимым аккумулятора OUT Вывести данные в порт PAC Загрузить в аккумулятор содержимое Р-регистра SACH Сохранить старшее слово аккумулятора со сдвигом SACL Сохранить младшее слово аккумулятора со сдвигом SPAC Вычесть содержимое Р-регистра из аккумулятора SUB Вычесть из содержимого аккумулятора со сдвигом SUBK Вычесть константу из содержимого аккумулятора TBLR Чтение таблицы TBLW Запись таблицы XOR Выполнить исключительное «ИЛИ» с содержимым аккумулятора ZAC Обнулить аккумулятор Команды сигнального процессоров

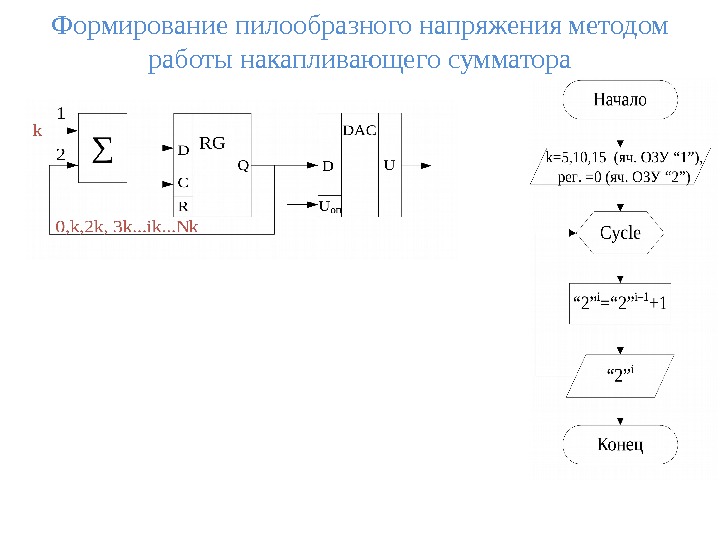

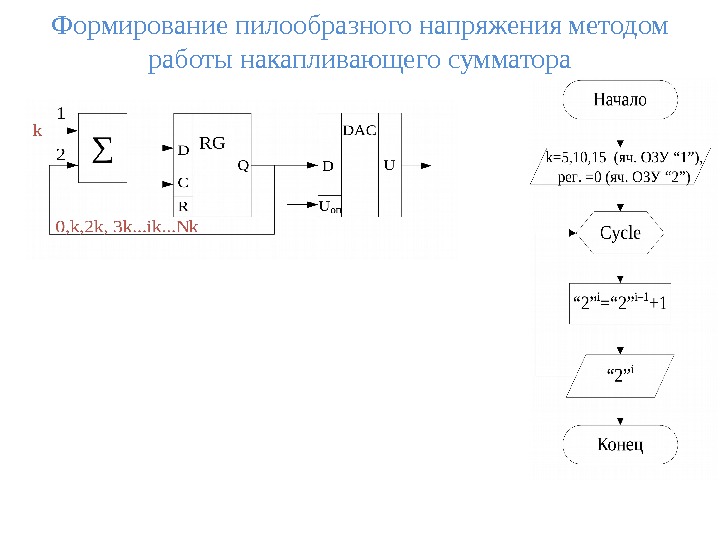

Формирование пилообразного напряжения методом работы накапливающего сумматора

Формирование пилообразного напряжения методом работы накапливающего сумматора

. text ldpk 0 lack 5 (10, 15) sacl 1 zac Cycle lac 2 add 1 sacl 2 out 2, pa 0 b Cycle . end

. text ldpk 0 lack 5 (10, 15) sacl 1 zac Cycle lac 2 add 1 sacl 2 out 2, pa 0 b Cycle . end

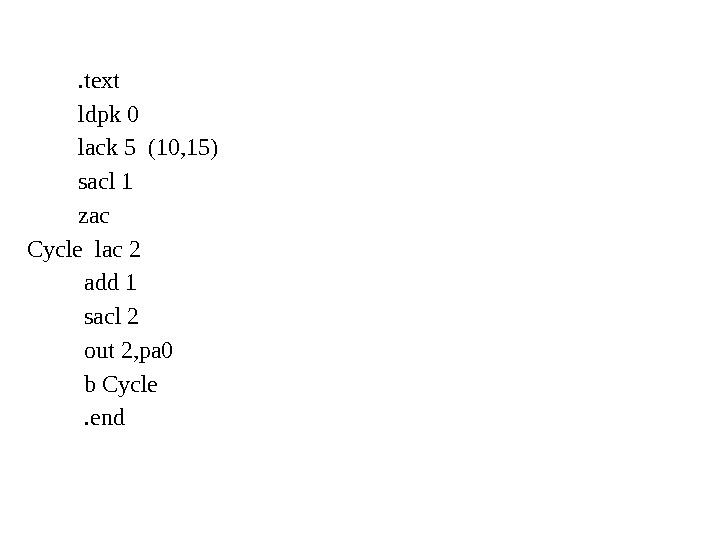

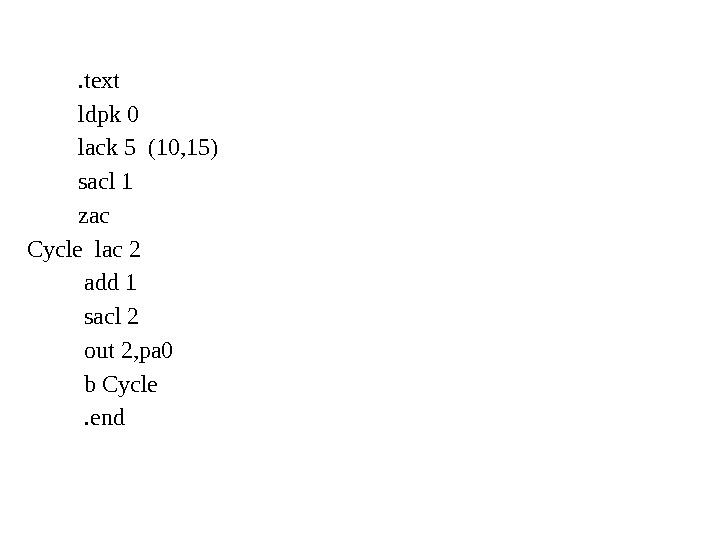

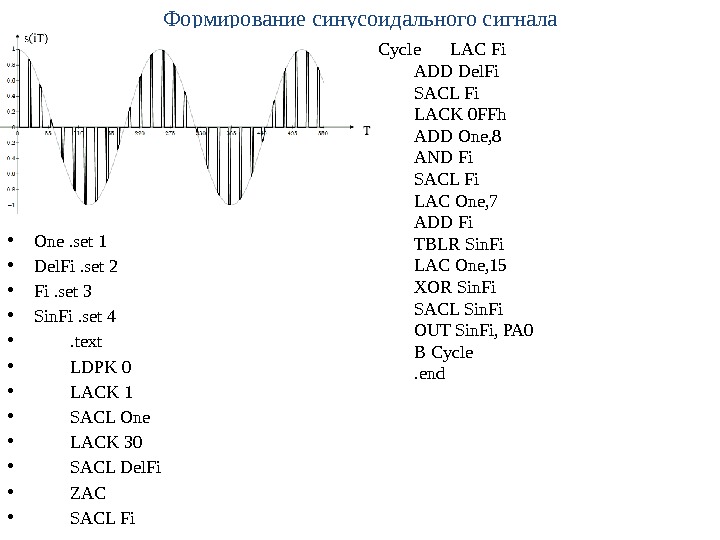

Формирование синусоидального сигнала • One. set 1 • Del. Fi. set 2 • Fi. set 3 • Sin. Fi. set 4 • . text • LDPK 0 • LACK 1 • SACL One • LACK 30 • SACL Del. Fi • ZAC • SACL Fi Cycle LAC Fi ADD Del. Fi SACL Fi LACK 0 FFh ADD One, 8 AND Fi SACL Fi LAC One, 7 ADD Fi TBLR Sin. Fi LAC One, 15 XOR Sin. Fi SACL Sin. Fi OUT Sin. Fi, PA 0 B Cycle. end

Формирование синусоидального сигнала • One. set 1 • Del. Fi. set 2 • Fi. set 3 • Sin. Fi. set 4 • . text • LDPK 0 • LACK 1 • SACL One • LACK 30 • SACL Del. Fi • ZAC • SACL Fi Cycle LAC Fi ADD Del. Fi SACL Fi LACK 0 FFh ADD One, 8 AND Fi SACL Fi LAC One, 7 ADD Fi TBLR Sin. Fi LAC One, 15 XOR Sin. Fi SACL Sin. Fi OUT Sin. Fi, PA 0 B Cycle. end

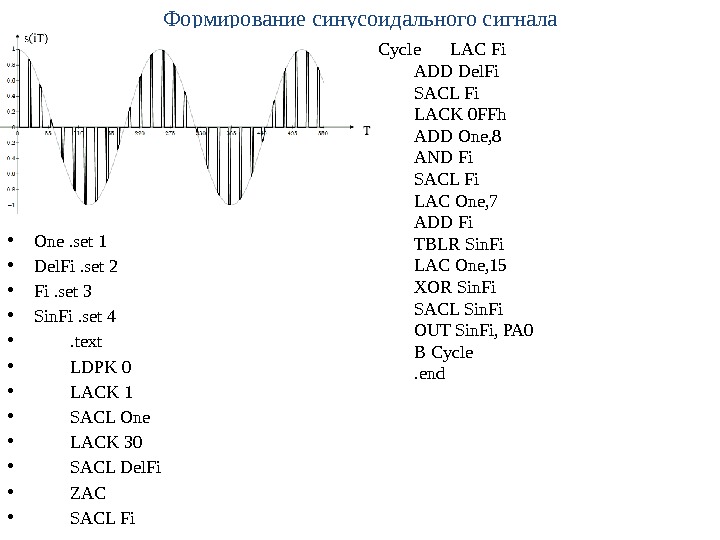

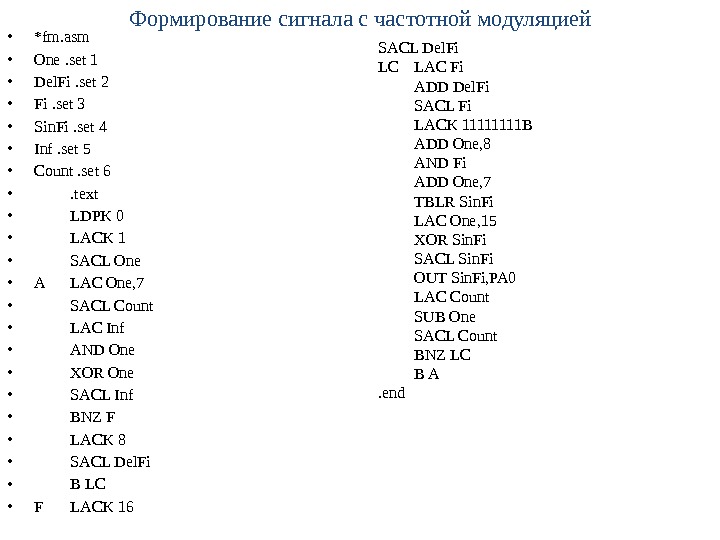

Формирование сигнала с частотной модуляцией • *fm. asm • One. set 1 • Del. Fi. set 2 • Fi. set 3 • Sin. Fi. set 4 • Inf. set 5 • Count. set 6 • . text • LDPK 0 • LACK 1 • SACL One • A LAC One, 7 • SACL Count • LAC Inf • AND One • XOR One • SACL Inf • BNZ F • LACK 8 • SACL Del. Fi • B LC • F LACK 16 SACL Del. Fi LC LAC Fi ADD Del. Fi SACL Fi LACK 1111 B ADD One, 8 AND Fi ADD One, 7 TBLR Sin. Fi LAC One, 15 XOR Sin. Fi SACL Sin. Fi OUT Sin. Fi, PA 0 LAC Count SUB One SACL Count BNZ LC B A. end

Формирование сигнала с частотной модуляцией • *fm. asm • One. set 1 • Del. Fi. set 2 • Fi. set 3 • Sin. Fi. set 4 • Inf. set 5 • Count. set 6 • . text • LDPK 0 • LACK 1 • SACL One • A LAC One, 7 • SACL Count • LAC Inf • AND One • XOR One • SACL Inf • BNZ F • LACK 8 • SACL Del. Fi • B LC • F LACK 16 SACL Del. Fi LC LAC Fi ADD Del. Fi SACL Fi LACK 1111 B ADD One, 8 AND Fi ADD One, 7 TBLR Sin. Fi LAC One, 15 XOR Sin. Fi SACL Sin. Fi OUT Sin. Fi, PA 0 LAC Count SUB One SACL Count BNZ LC B A. end

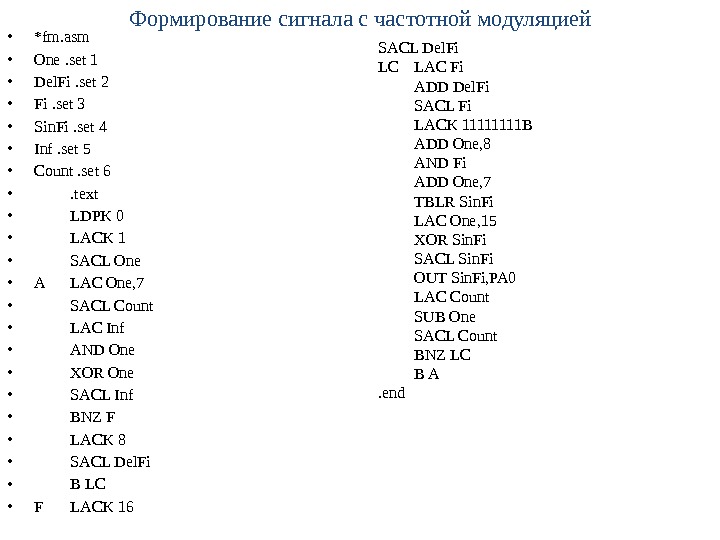

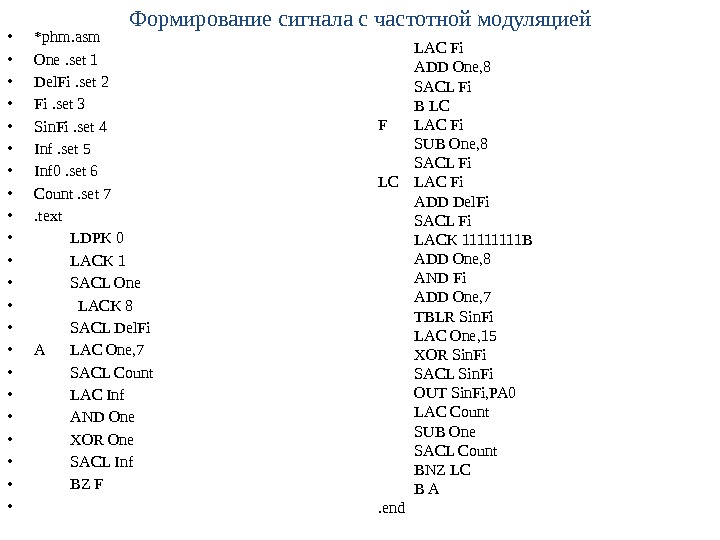

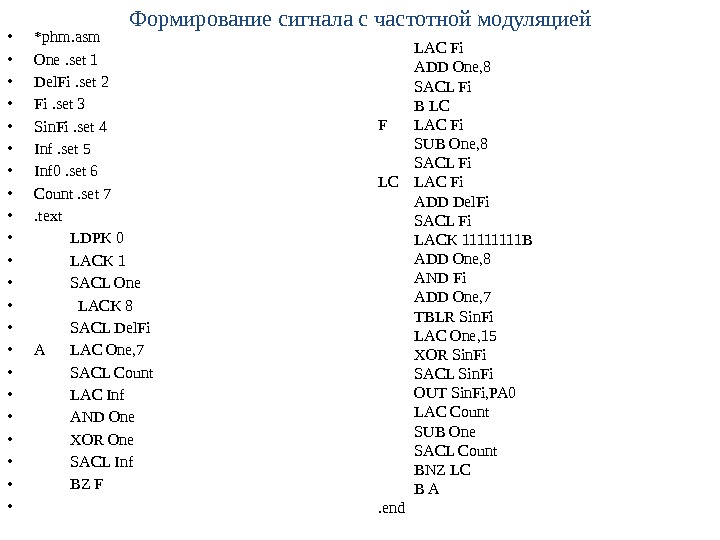

Формирование сигнала с частотной модуляцией • *phm. asm • One. set 1 • Del. Fi. set 2 • Fi. set 3 • Sin. Fi. set 4 • Inf. set 5 • Inf 0. set 6 • Count. set 7 • . text • LDPK 0 • LACK 1 • SACL One • LACK 8 • SACL Del. Fi • A LAC One, 7 • SACL Count • LAC Inf • AND One • XOR One • SACL Inf • BZ F • LAC Fi ADD One, 8 SACL Fi B LC F LAC Fi SUB One, 8 SACL Fi LC LAC Fi ADD Del. Fi SACL Fi LACK 1111 B ADD One, 8 AND Fi ADD One, 7 TBLR Sin. Fi LAC One, 15 XOR Sin. Fi SACL Sin. Fi OUT Sin. Fi, PA 0 LAC Count SUB One SACL Count BNZ LC B A. end

Формирование сигнала с частотной модуляцией • *phm. asm • One. set 1 • Del. Fi. set 2 • Fi. set 3 • Sin. Fi. set 4 • Inf. set 5 • Inf 0. set 6 • Count. set 7 • . text • LDPK 0 • LACK 1 • SACL One • LACK 8 • SACL Del. Fi • A LAC One, 7 • SACL Count • LAC Inf • AND One • XOR One • SACL Inf • BZ F • LAC Fi ADD One, 8 SACL Fi B LC F LAC Fi SUB One, 8 SACL Fi LC LAC Fi ADD Del. Fi SACL Fi LACK 1111 B ADD One, 8 AND Fi ADD One, 7 TBLR Sin. Fi LAC One, 15 XOR Sin. Fi SACL Sin. Fi OUT Sin. Fi, PA 0 LAC Count SUB One SACL Count BNZ LC B A. end

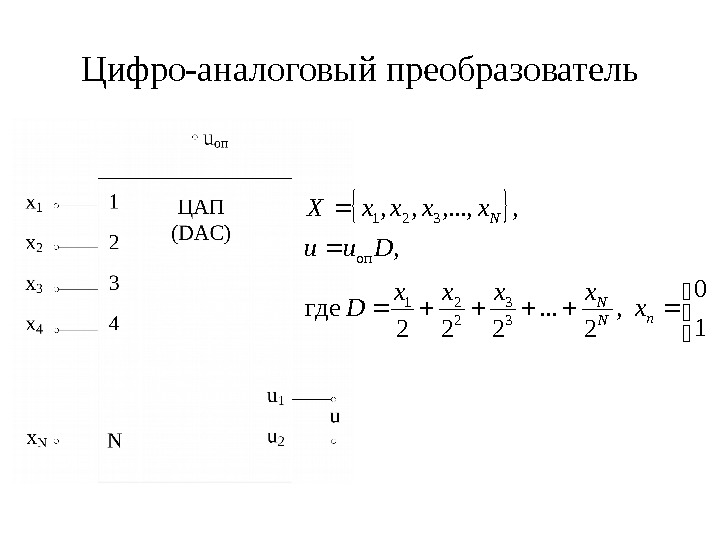

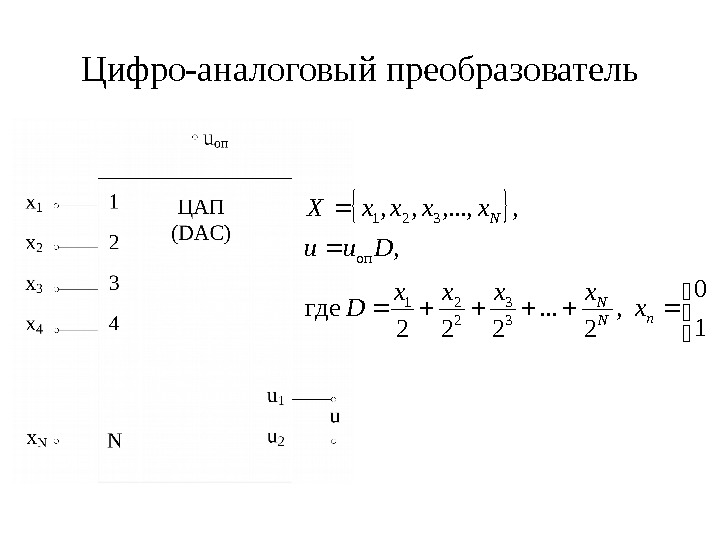

Цифро-аналоговый преобразователь 1 0 , 2. . . 222 где , , , . . . , , , 3 3 2 21 о п 321 n. N N N x xxxx D Duu xxxx. X

Цифро-аналоговый преобразователь 1 0 , 2. . . 222 где , , , . . . , , , 3 3 2 21 о п 321 n. N N N x xxxx D Duu xxxx. X

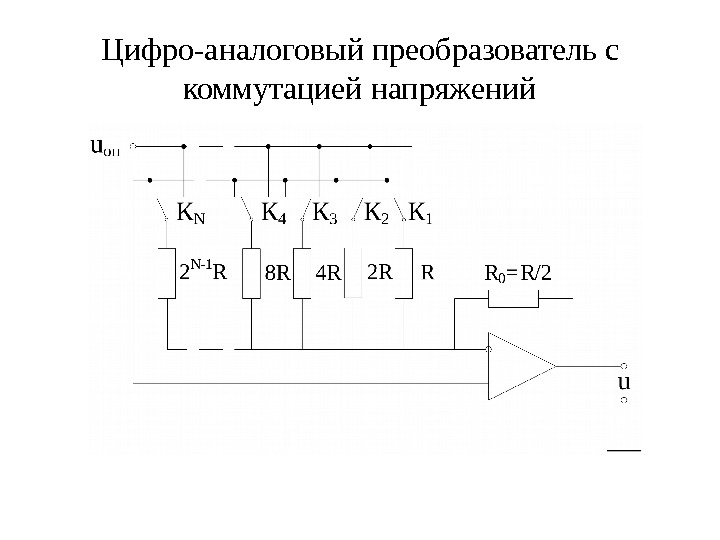

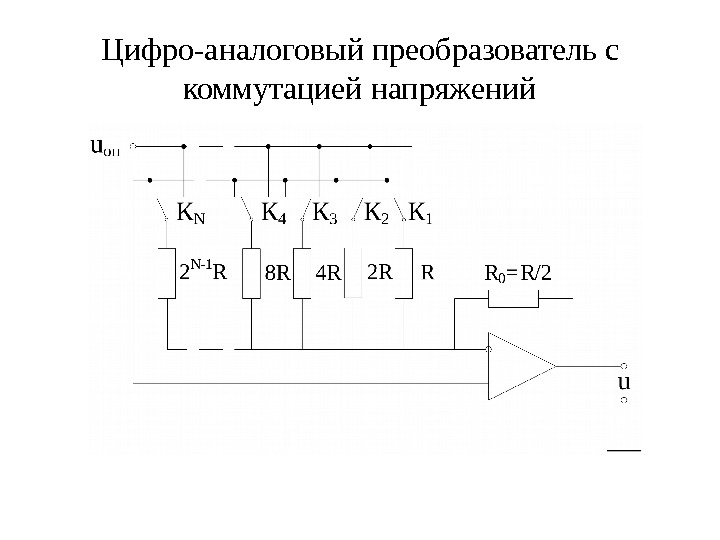

Цифро-аналоговый преобразователь с коммутацией напряжений

Цифро-аналоговый преобразователь с коммутацией напряжений

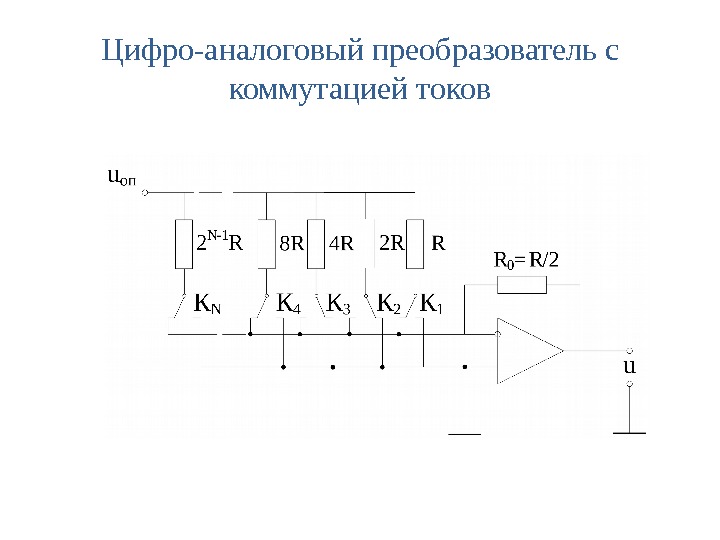

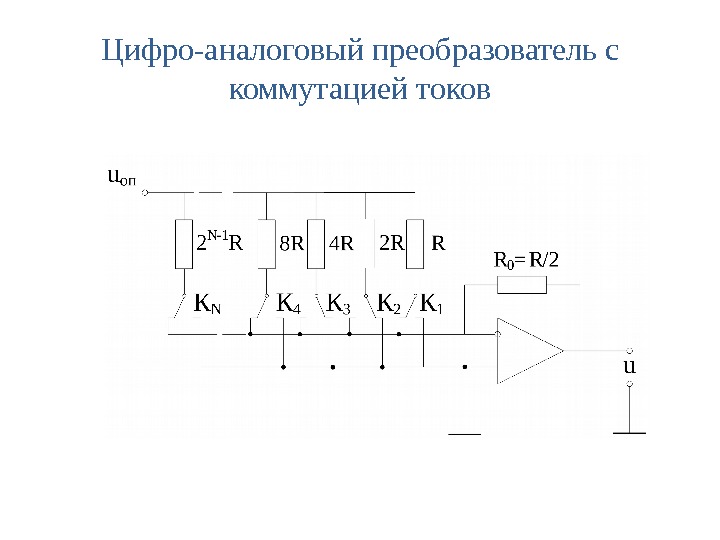

Цифро-аналоговый преобразователь с коммутацией токов

Цифро-аналоговый преобразователь с коммутацией токов

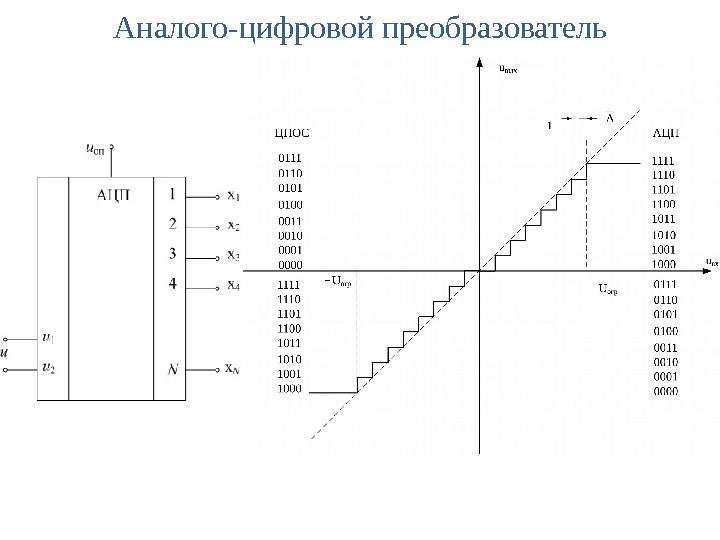

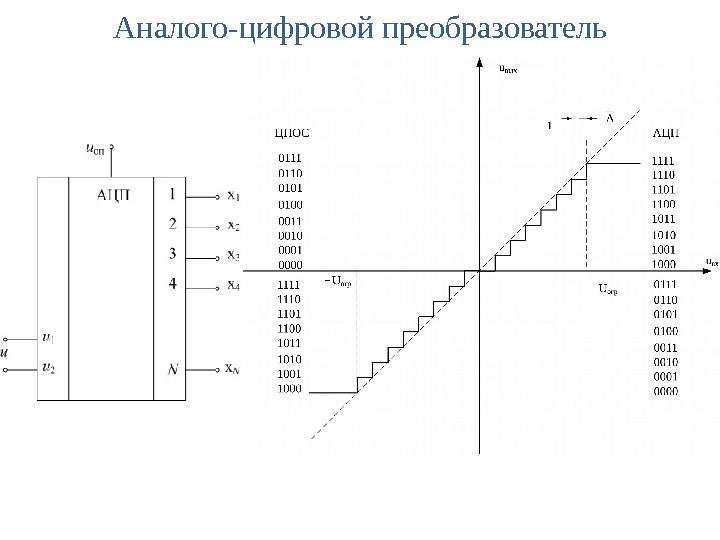

Аналого-цифровой преобразователь

Аналого-цифровой преобразователь

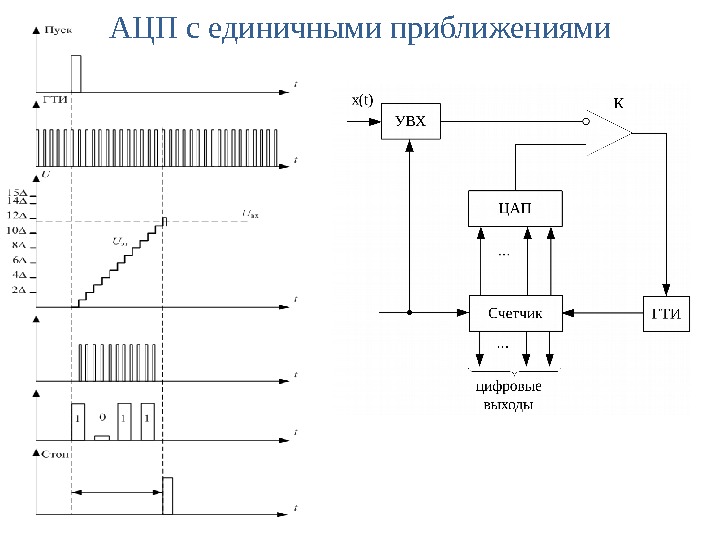

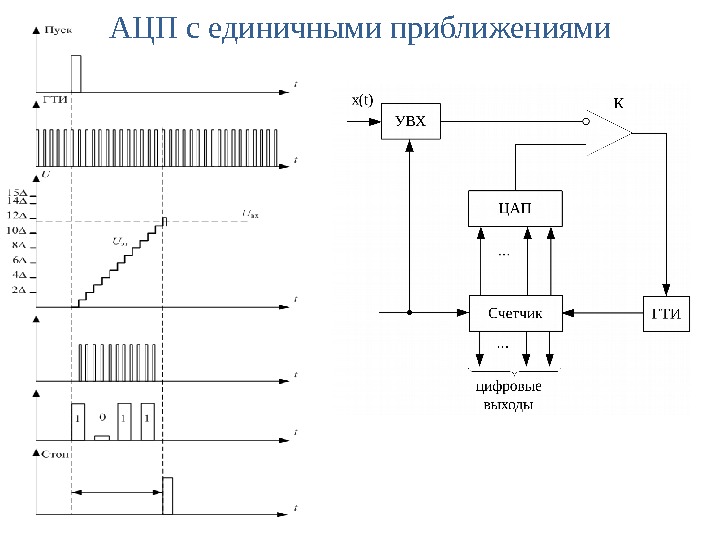

АЦП с единичными приближениями

АЦП с единичными приближениями

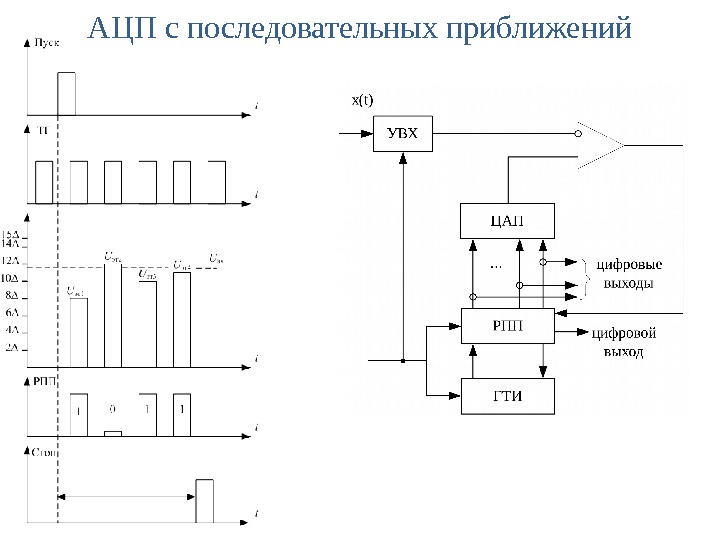

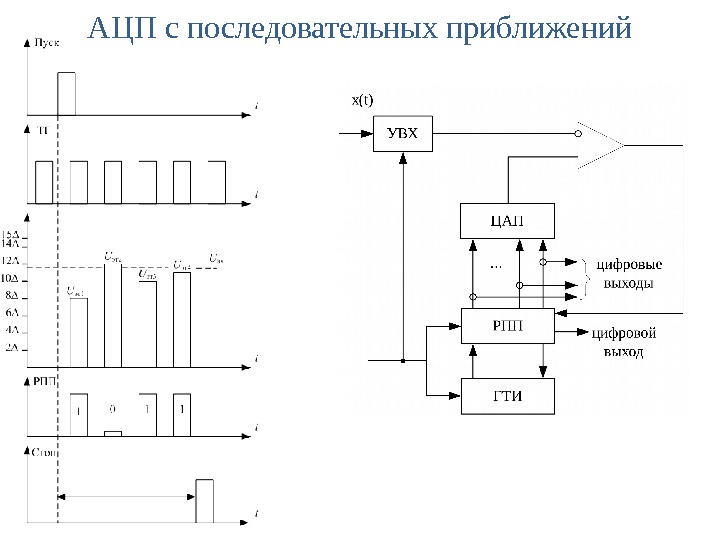

АЦП с последовательных приближений

АЦП с последовательных приближений

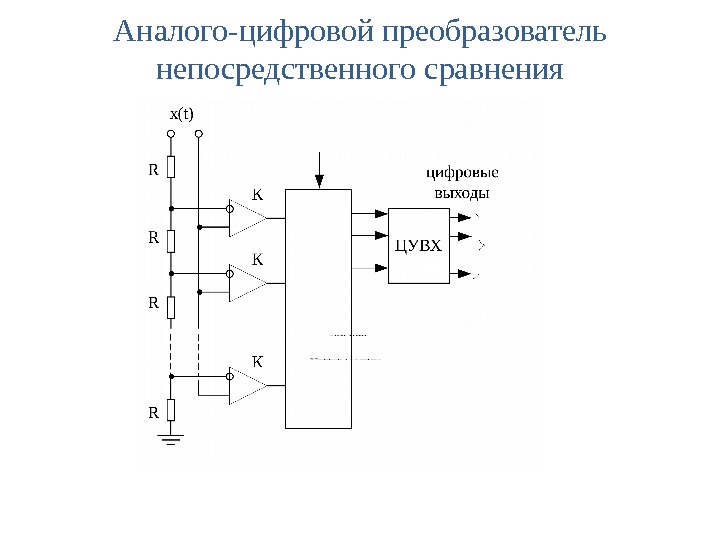

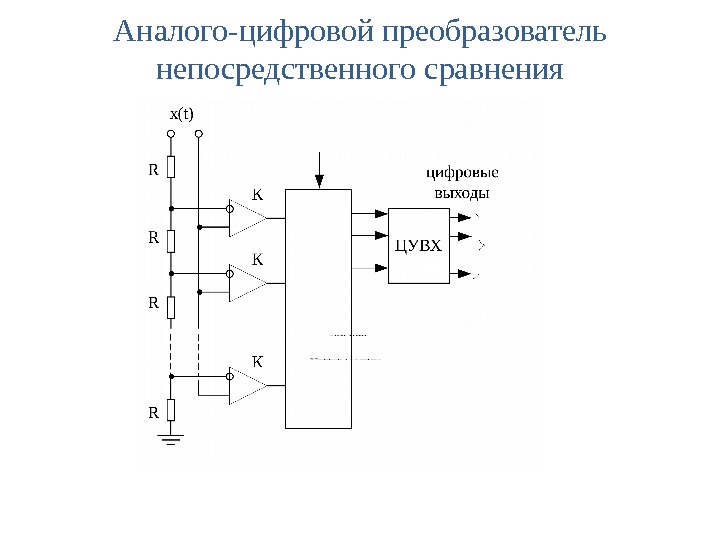

Аналого-цифровой преобразователь непосредственного сравнения

Аналого-цифровой преобразователь непосредственного сравнения

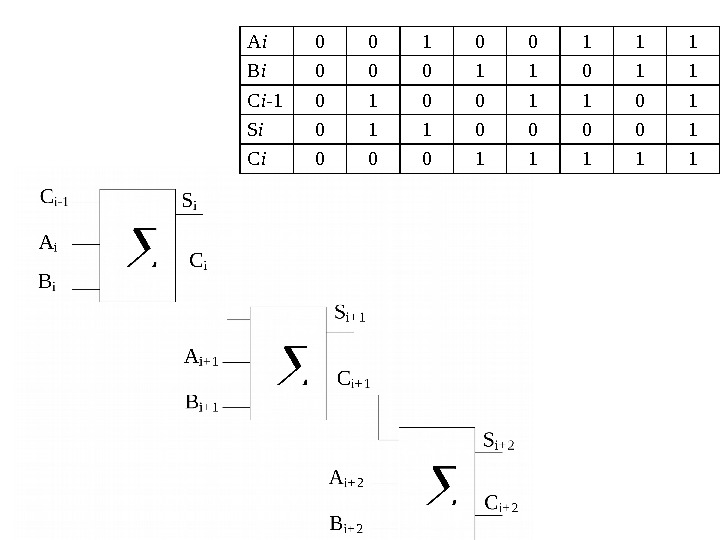

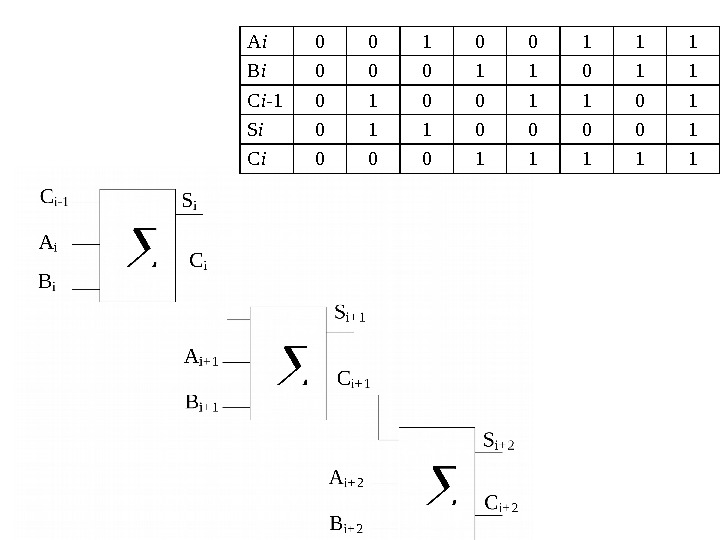

Устройства арифметического сложения

Устройства арифметического сложения

A i 0 0 1 1 1 B i 0 0 0 1 1 C i- 1 0 0 1 1 0 1 S i 0 1 1 0 0 1 C i

A i 0 0 1 1 1 B i 0 0 0 1 1 C i- 1 0 0 1 1 0 1 S i 0 1 1 0 0 1 C i

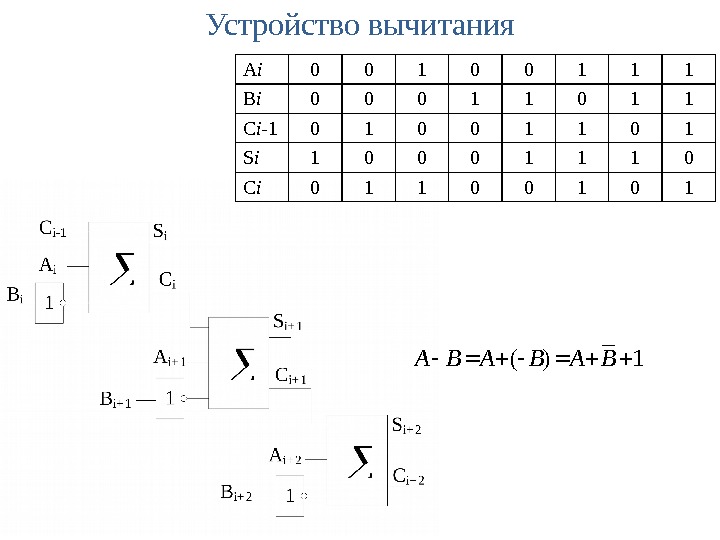

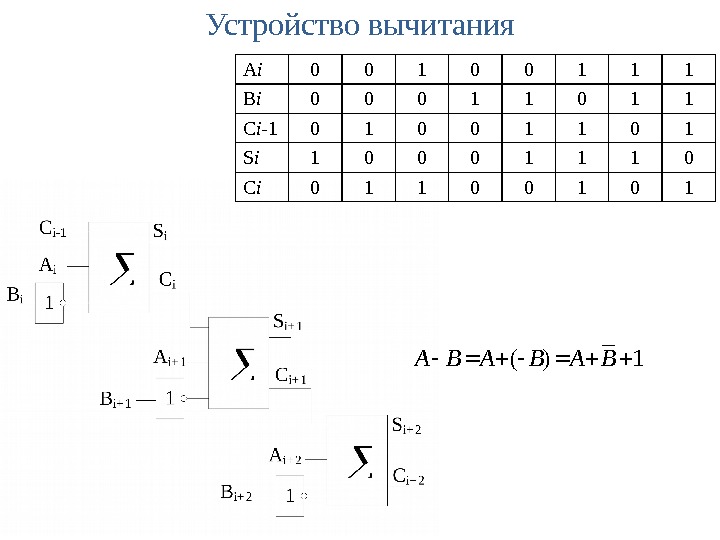

Устройство вычитания 1)(BABABA A i 0 0 1 1 1 B i 0 0 0 1 1 C i- 1 0 0 1 1 0 1 S i 1 0 0 0 1 1 1 0 C i

Устройство вычитания 1)(BABABA A i 0 0 1 1 1 B i 0 0 0 1 1 C i- 1 0 0 1 1 0 1 S i 1 0 0 0 1 1 1 0 C i

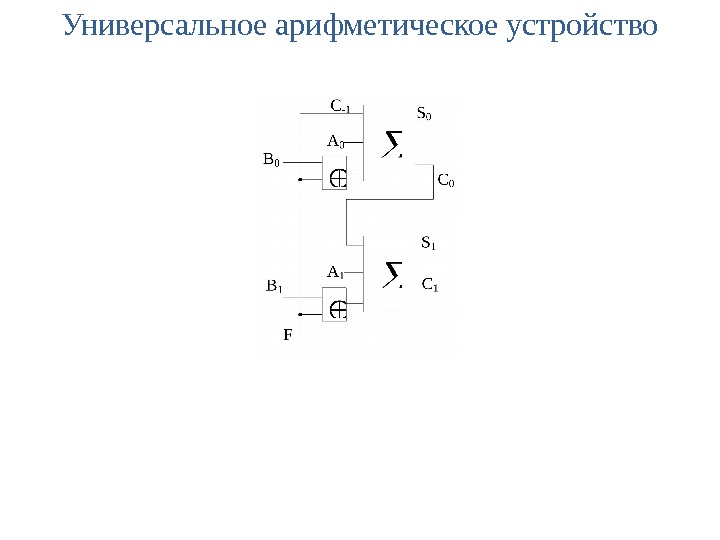

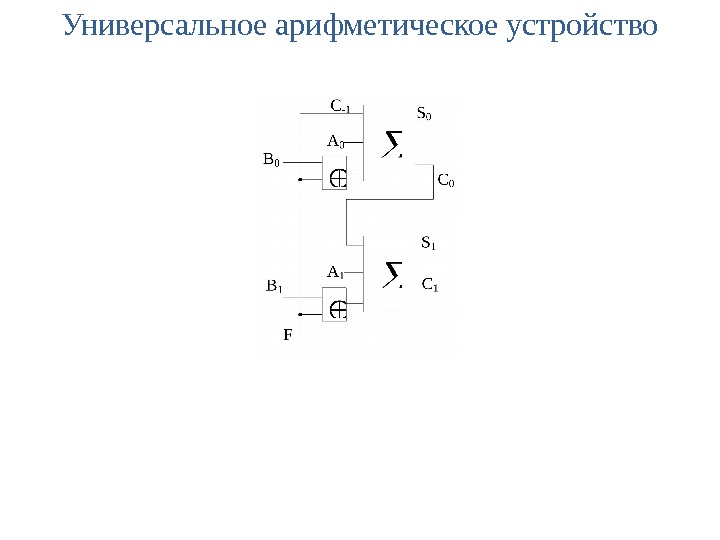

Универсальное арифметическое устройство

Универсальное арифметическое устройство

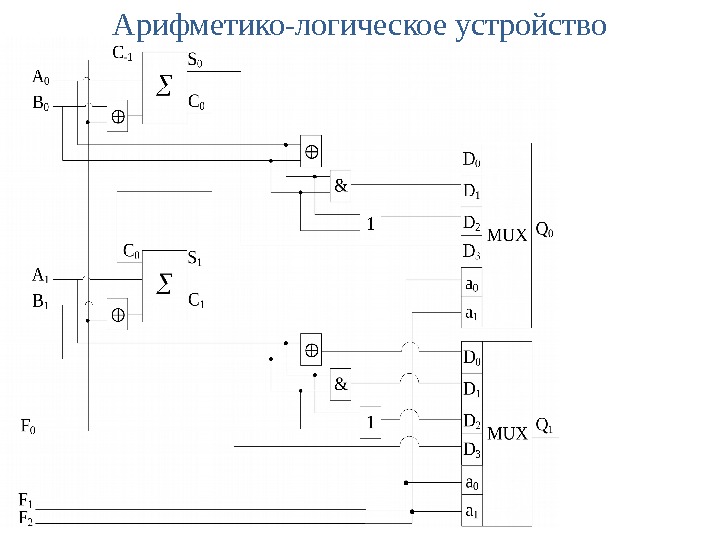

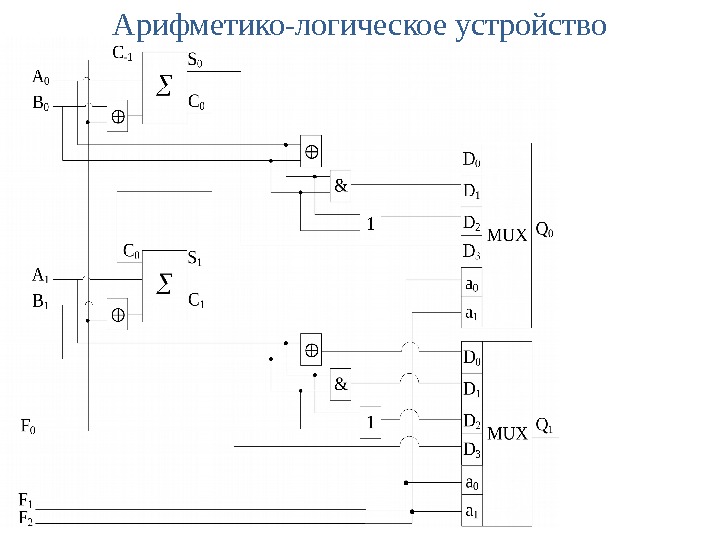

Арифметико-логическое устройство

Арифметико-логическое устройство

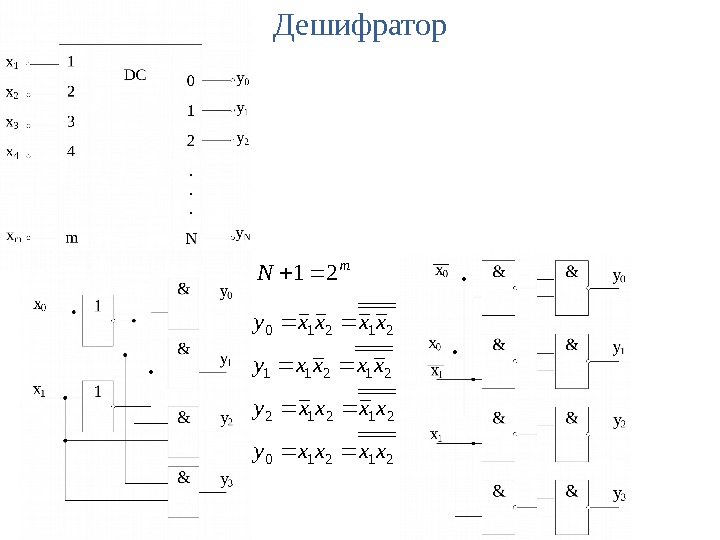

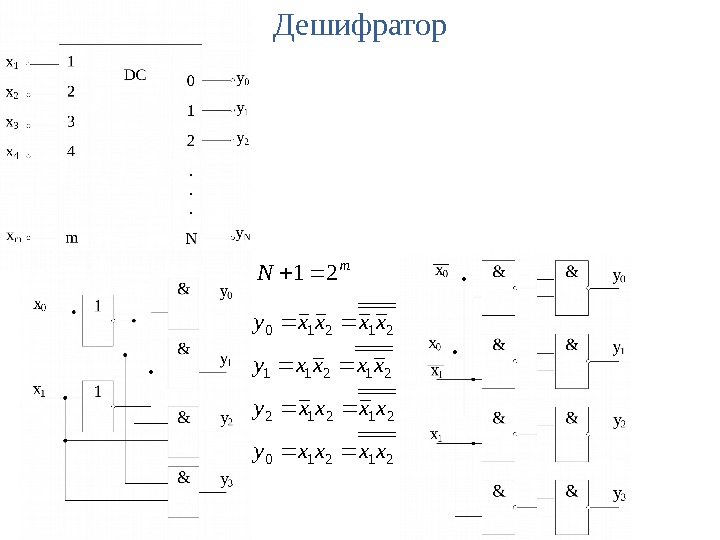

Дешифратор21210 21212 21211 21210 xxxxy m N

Дешифратор21210 21212 21211 21210 xxxxy m N

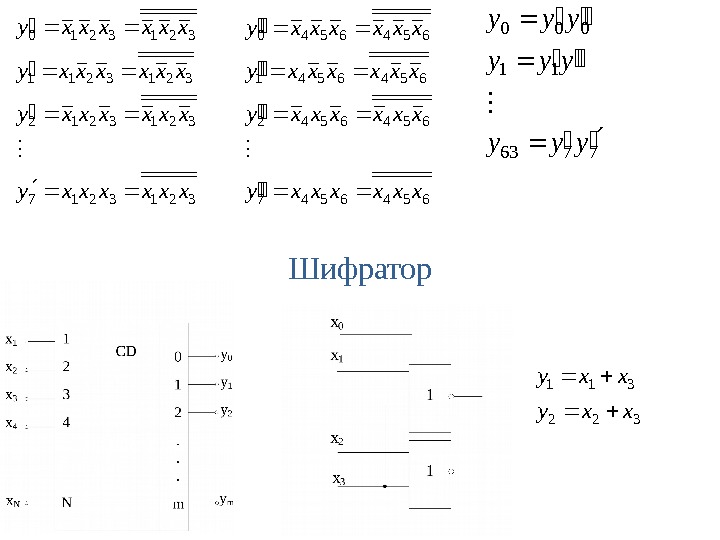

3213217 3213212 3213211 3213210 xxxxxxy 6546547 6546542 6546541 6546540 xxxxxxy 7763 11 000 yyy yyy 322 311 xxy Шифратор

3213217 3213212 3213211 3213210 xxxxxxy 6546547 6546542 6546541 6546540 xxxxxxy 7763 11 000 yyy yyy 322 311 xxy Шифратор

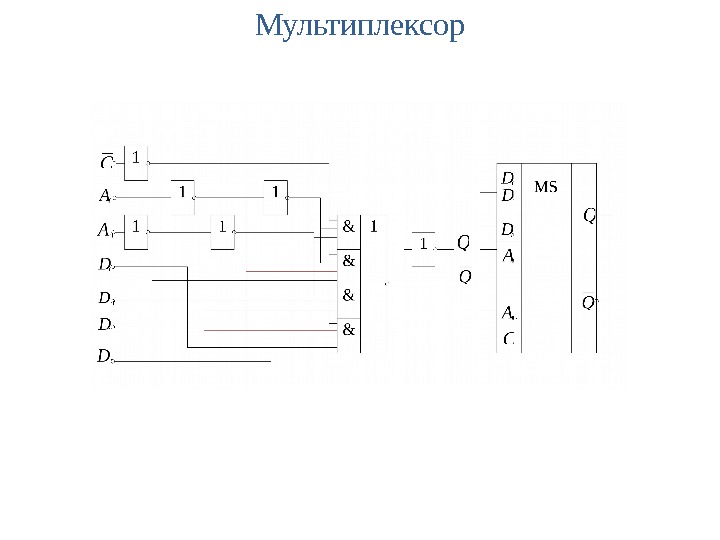

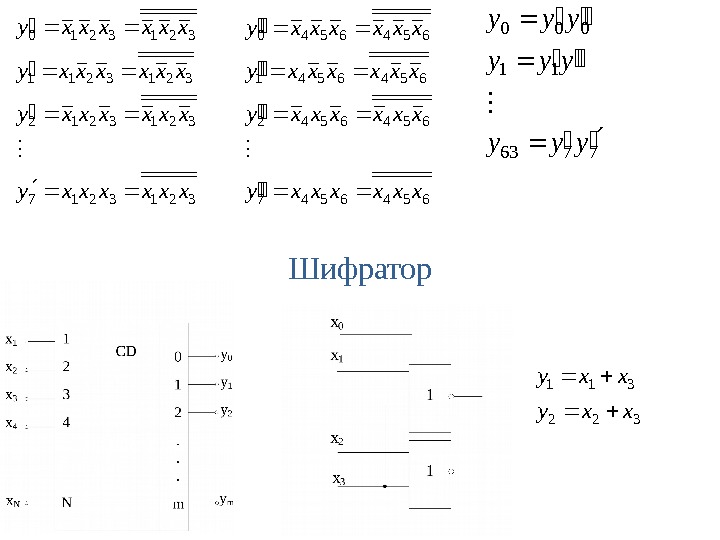

Мультиплексор

Мультиплексор

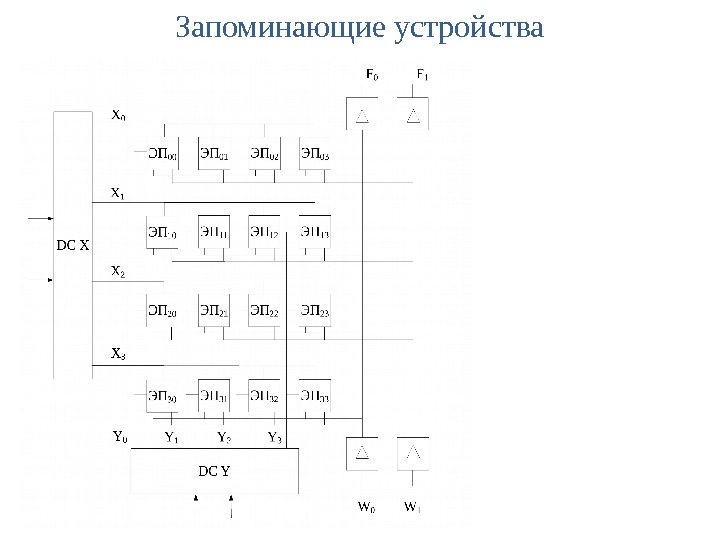

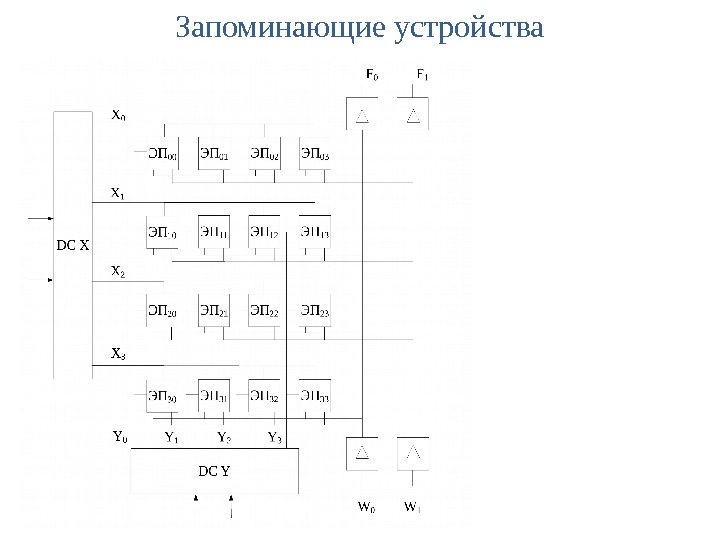

Запоминающие устройства

Запоминающие устройства

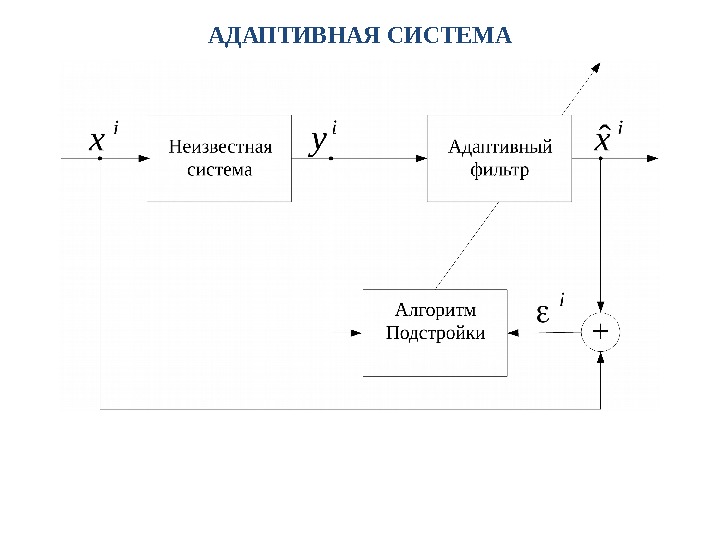

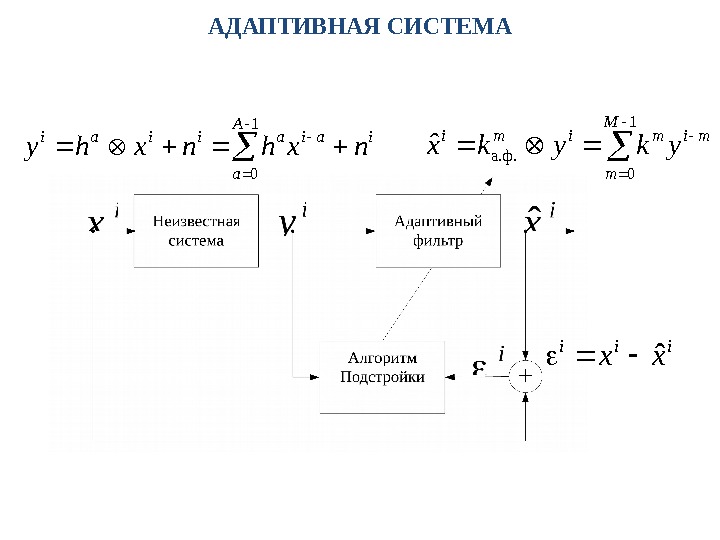

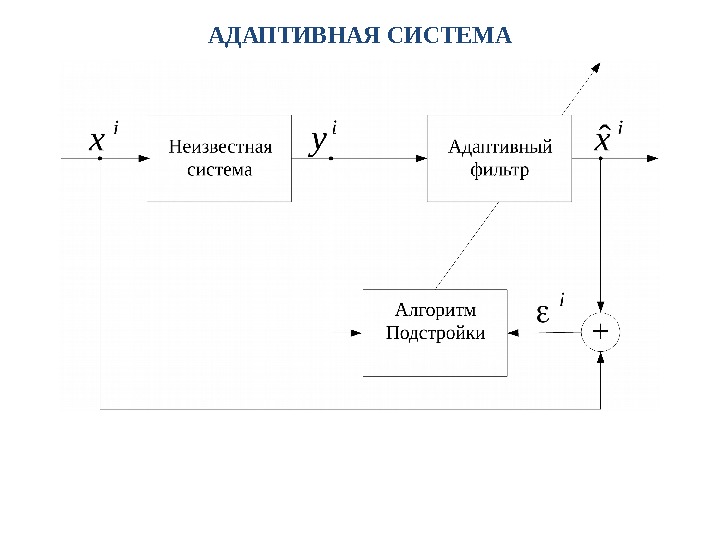

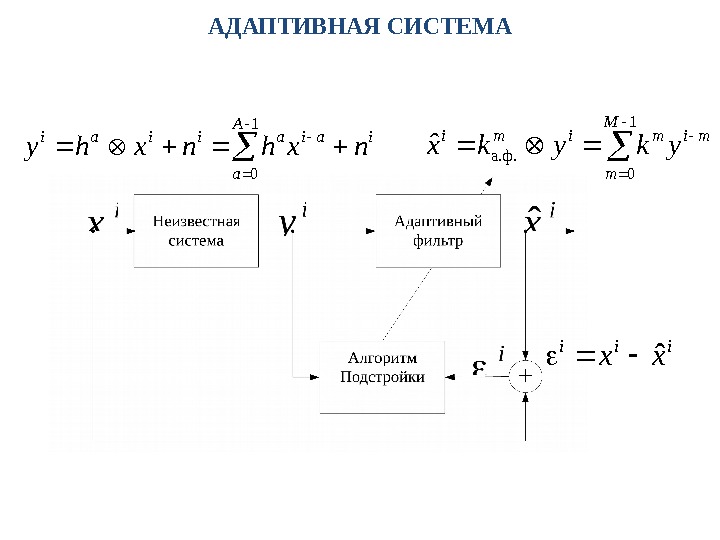

АДАПТИВНАЯ СИСТЕМА

АДАПТИВНАЯ СИСТЕМА

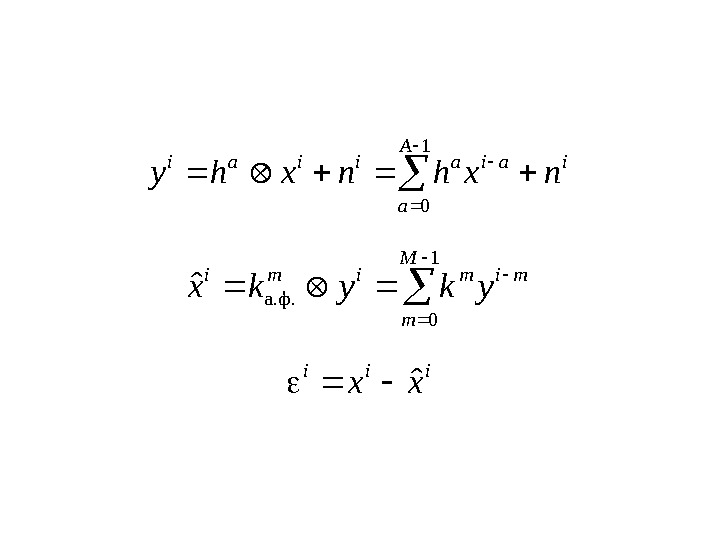

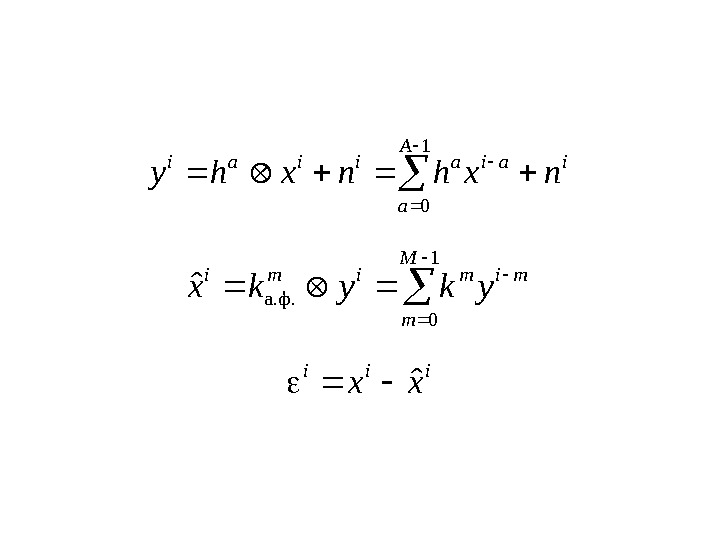

1 0 A a iaiaiiai nxhnxhy 1 0 а. ф. ˆ M m mimimi ykykx iii xxˆ

1 0 A a iaiaiiai nxhnxhy 1 0 а. ф. ˆ M m mimimi ykykx iii xxˆ

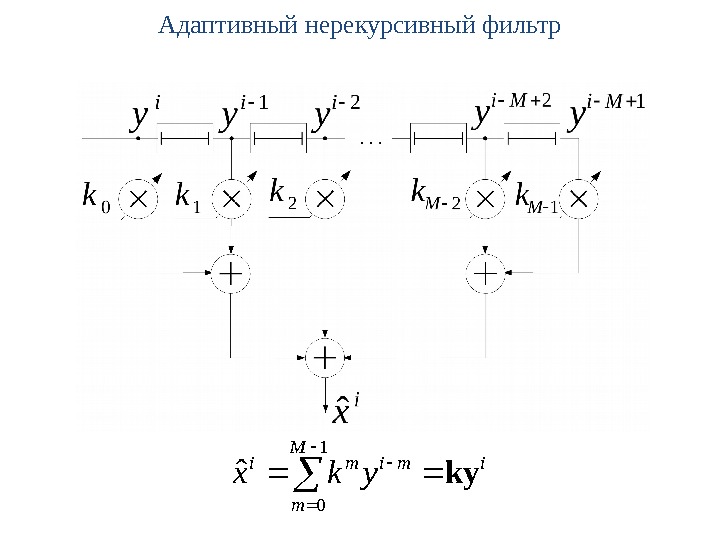

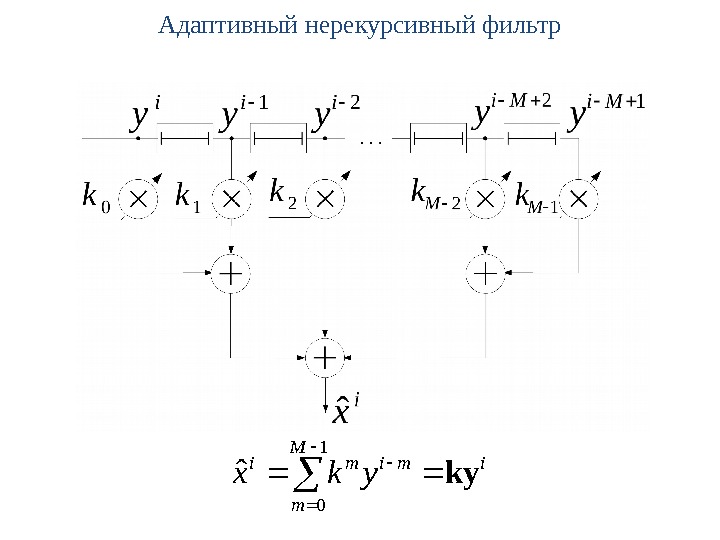

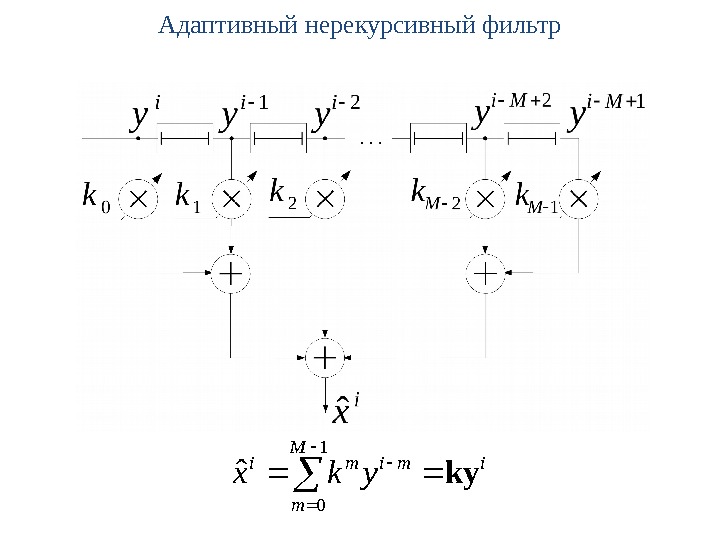

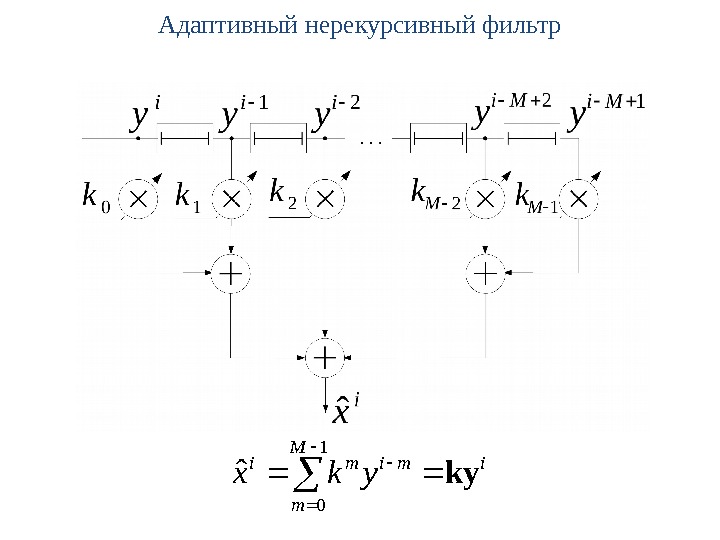

Адаптивный нерекурсивный фильтрi M m mimi ykxky 1 0 ˆ

Адаптивный нерекурсивный фильтрi M m mimi ykxky 1 0 ˆ

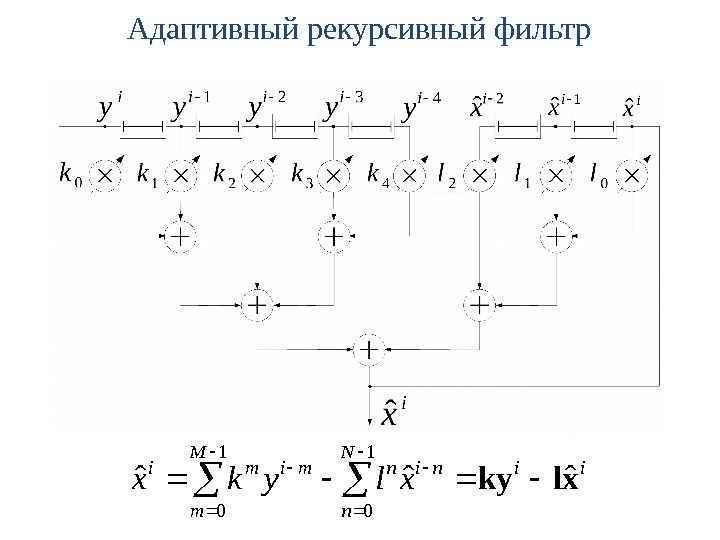

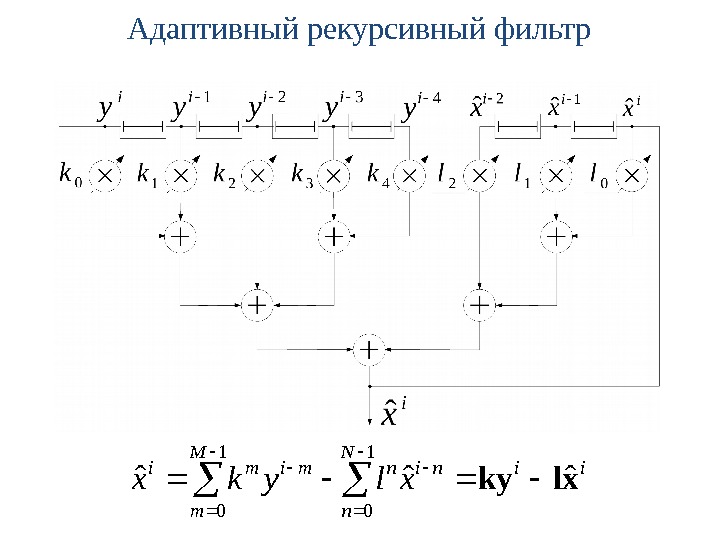

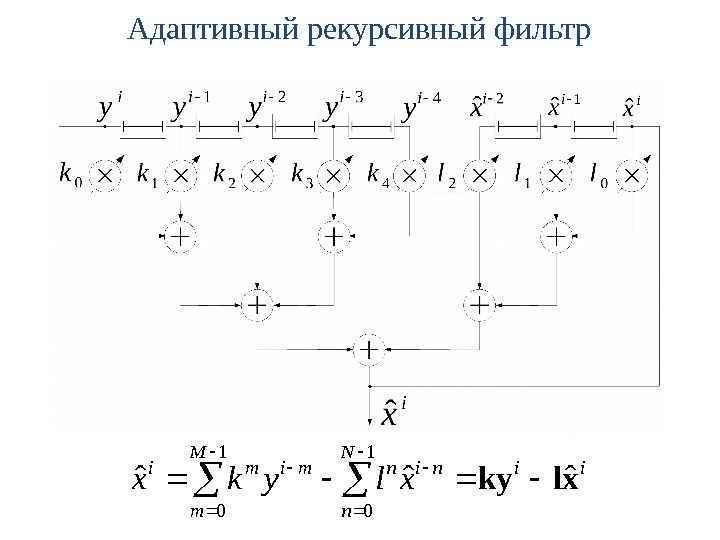

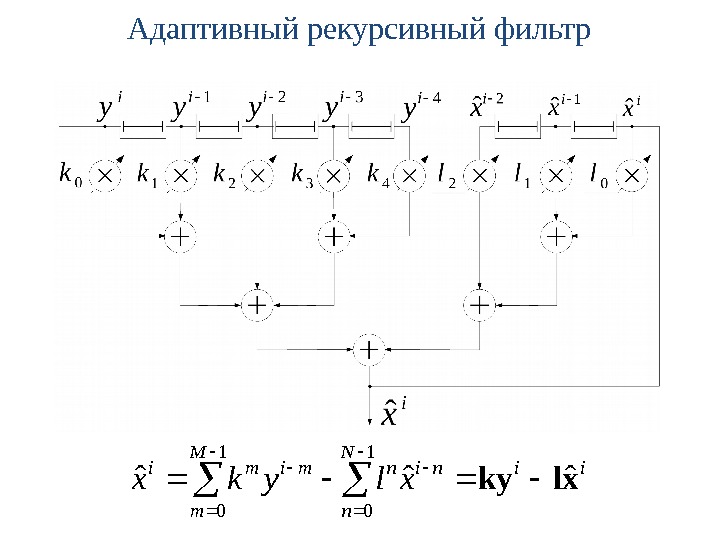

Адаптивный рекурсивный фильтр ii. N n nin. M m mimi xlykx xlky ˆˆˆ

Адаптивный рекурсивный фильтр ii. N n nin. M m mimi xlykx xlky ˆˆˆ

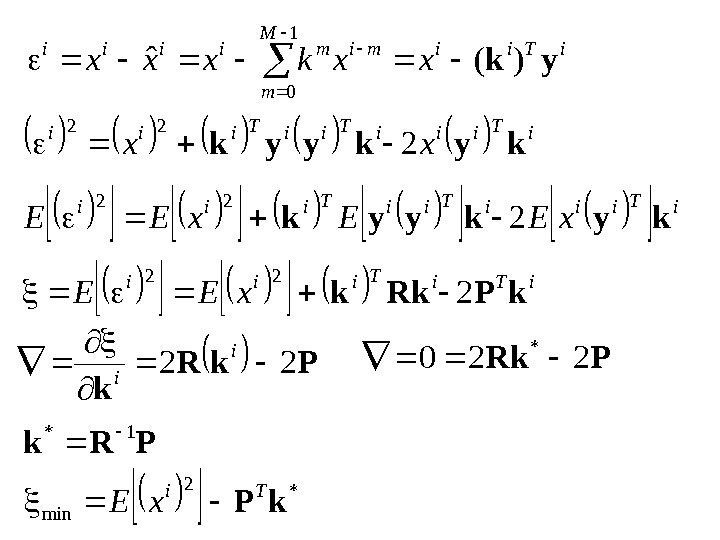

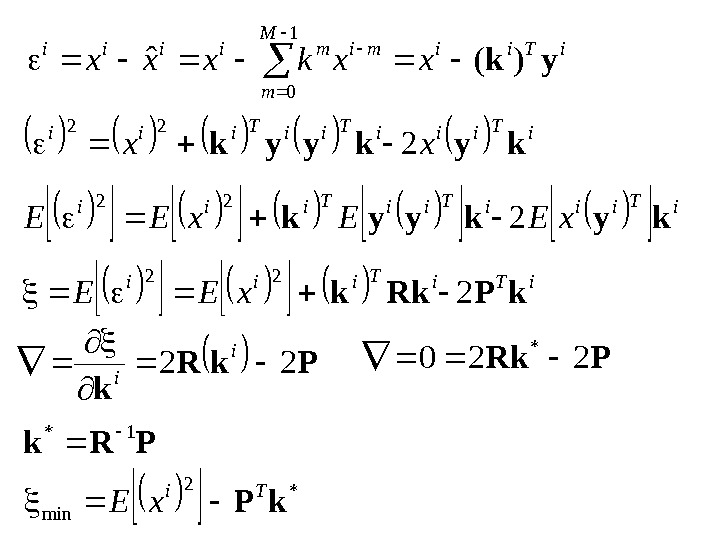

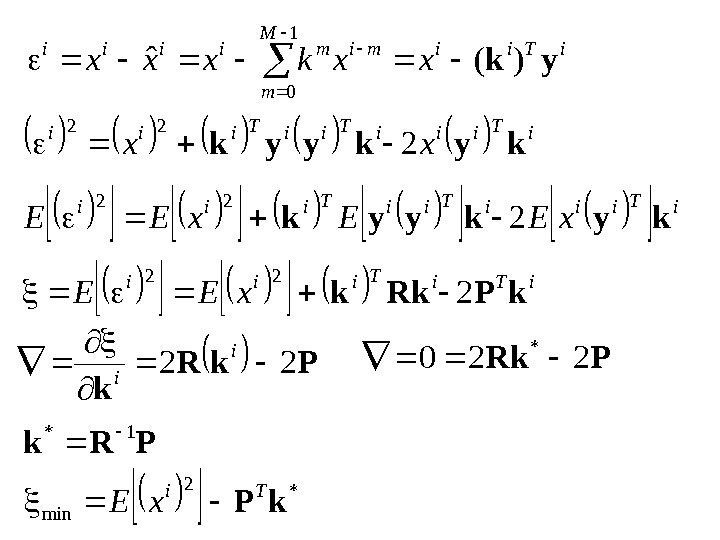

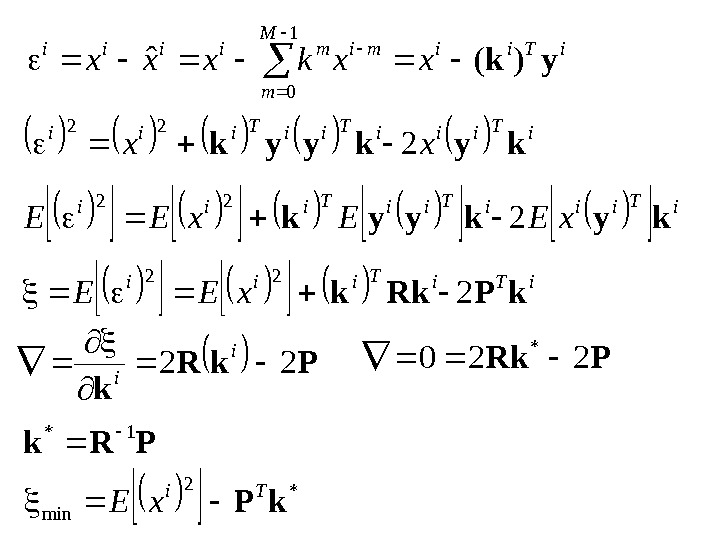

i. Tii M m mimiiii xxkxxxyk)(ˆ 1 0 i. Tiii xxkykyyk 2 22 i. Tiii x. EEkykyyk 2 22 Pk. R k 22 i i i. Tiii x. EEk. PRkk 2 22 PRk 220 * PRk 1* *2 mink. P Ti x.

i. Tii M m mimiiii xxkxxxyk)(ˆ 1 0 i. Tiii xxkykyyk 2 22 i. Tiii x. EEkykyyk 2 22 Pk. R k 22 i i i. Tiii x. EEk. PRkk 2 22 PRk 220 * PRk 1* *2 mink. P Ti x.

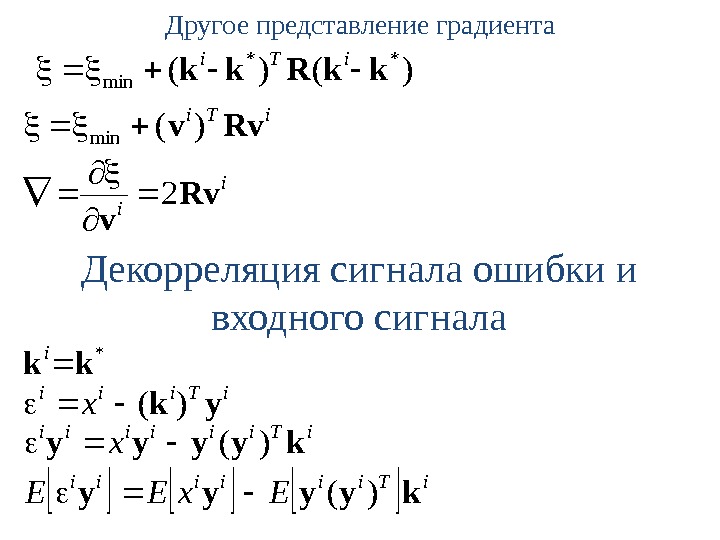

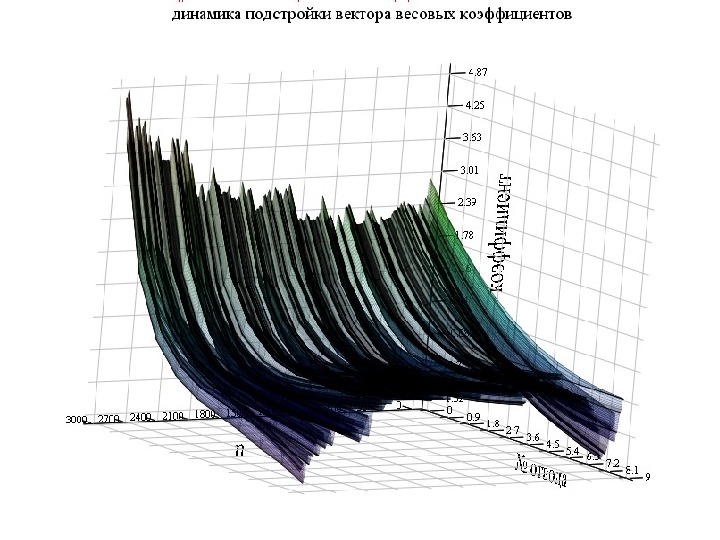

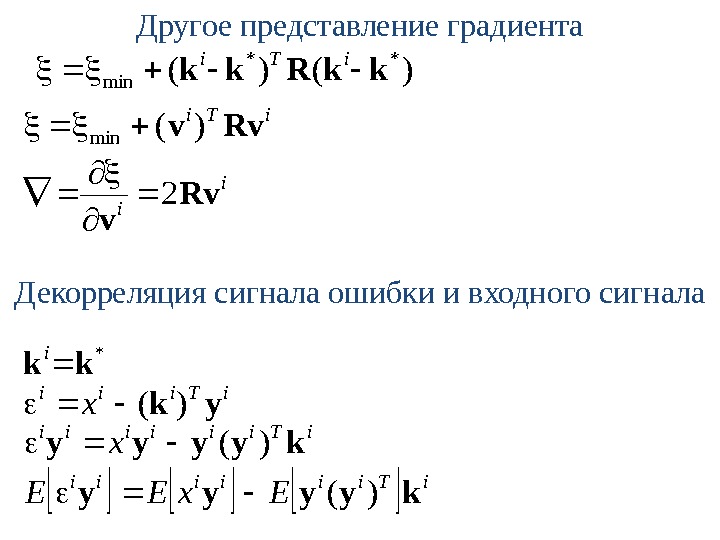

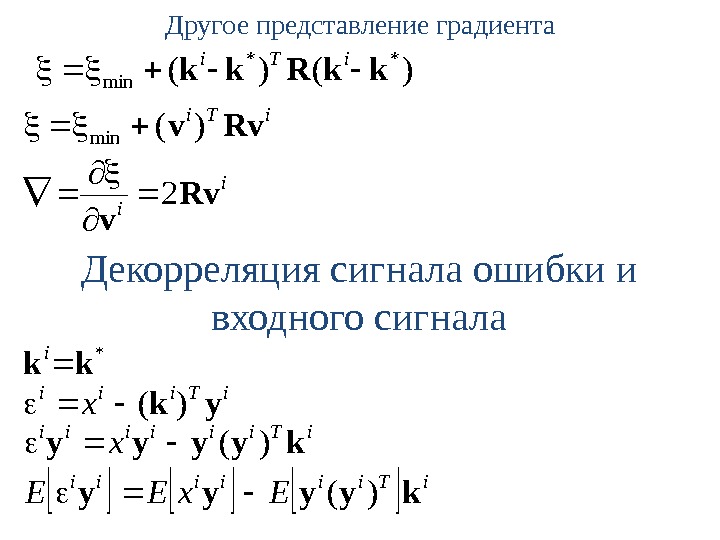

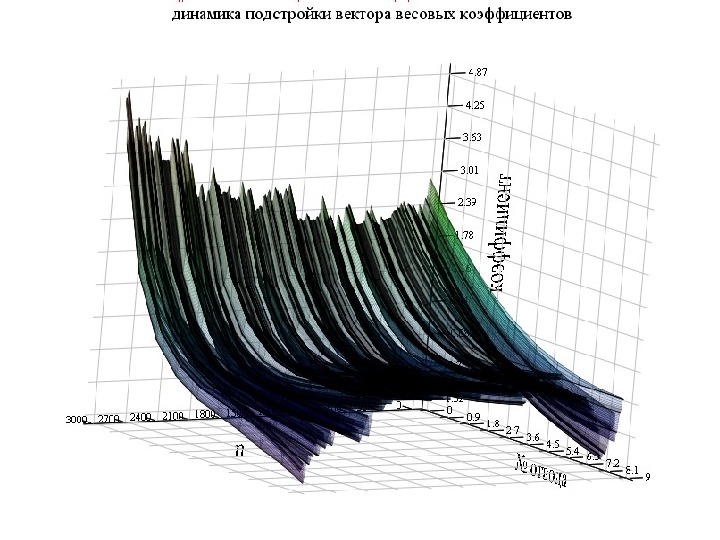

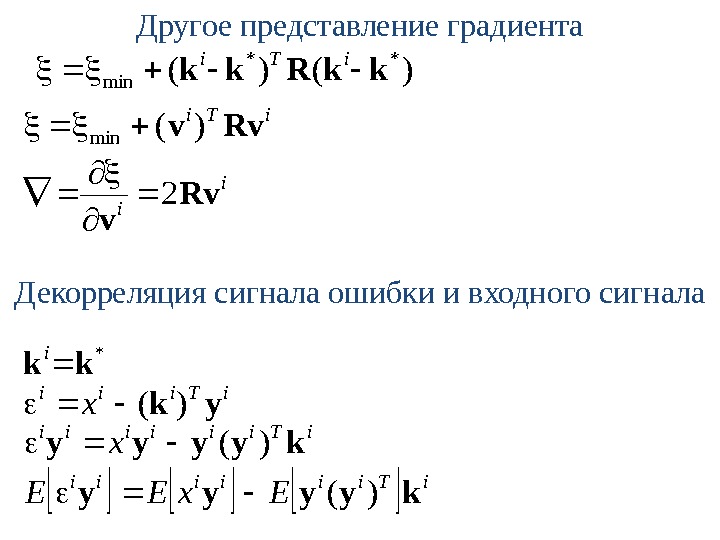

Другое представление градиента)()( ** minkk. Rkk i. Ti Rvv)(min i i Rv v 2 Декорреляция сигнала ошибки и входного сигнала * kk i i. Tiii xyk)( i. Tiiiiii xkyyyy)( i. Tiiiiii Ex. EEkyyyy)(

Другое представление градиента)()( ** minkk. Rkk i. Ti Rvv)(min i i Rv v 2 Декорреляция сигнала ошибки и входного сигнала * kk i i. Tiii xyk)( i. Tiiiiii xkyyyy)( i. Tiiiiii Ex. EEkyyyy)(

Запоминающие устройства

Запоминающие устройства

АДАПТИВНАЯ СИСТЕМА 1 0 A a iaiaiiai nxhnxhy 1 0 а. ф. ˆ M m mimimi ykykx iii xxˆ

АДАПТИВНАЯ СИСТЕМА 1 0 A a iaiaiiai nxhnxhy 1 0 а. ф. ˆ M m mimimi ykykx iii xxˆ

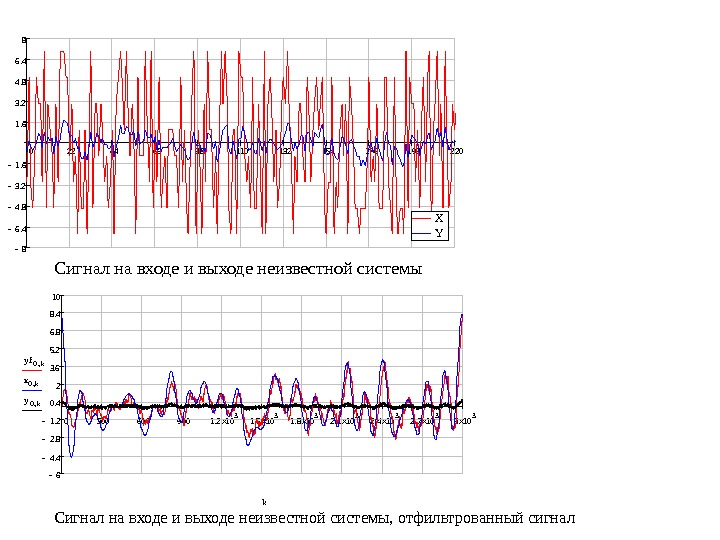

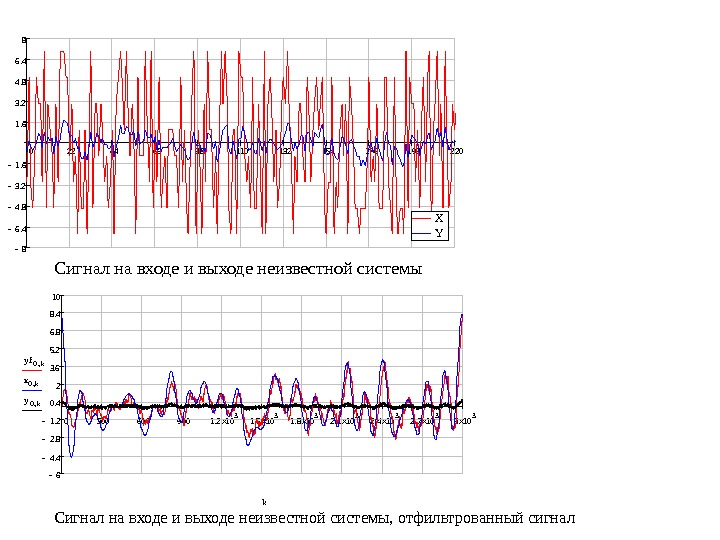

Сигнал на входе и выходе неизвестной системы0 22 44 66 88 110 132 154 17 6 198 220 8 6. 4 4. 8 3. 2 1. 63. 24. 86. 4 8 X Y Сигнал на входе и выходе неизвестной системы, отфильтрованный сигнал 0 300 600 900 1. 2 10 3 1. 5 10 3 1. 8 10 3 2. 1 10 3 2. 4 10 3 2. 7 10 3 3 10 3 6 4. 4 2. 8 1. 2 0. 4 23. 65. 26. 88. 4 10 yf 0 k x 0 k y 0 k k

Сигнал на входе и выходе неизвестной системы0 22 44 66 88 110 132 154 17 6 198 220 8 6. 4 4. 8 3. 2 1. 63. 24. 86. 4 8 X Y Сигнал на входе и выходе неизвестной системы, отфильтрованный сигнал 0 300 600 900 1. 2 10 3 1. 5 10 3 1. 8 10 3 2. 1 10 3 2. 4 10 3 2. 7 10 3 3 10 3 6 4. 4 2. 8 1. 2 0. 4 23. 65. 26. 88. 4 10 yf 0 k x 0 k y 0 k k

Адаптивный нерекурсивный фильтрi M m mimi ykxky 1 0 ˆ

Адаптивный нерекурсивный фильтрi M m mimi ykxky 1 0 ˆ

Адаптивный рекурсивный фильтр ii. N n nin. M m mimi xlykx xlky ˆˆˆ

Адаптивный рекурсивный фильтр ii. N n nin. M m mimi xlykx xlky ˆˆˆ

i. Tii M m mimiiii xxkxxxyk)(ˆ 1 0 i. Tiii xxkykyyk 2 22 i. Tiii x. EEkykyyk 2 22 Pk. R k 22 i i i. Tiii x. EEk. PRkk 2 22 PRk 220 * PRk 1* *2 mink. P Ti x.

i. Tii M m mimiiii xxkxxxyk)(ˆ 1 0 i. Tiii xxkykyyk 2 22 i. Tiii x. EEkykyyk 2 22 Pk. R k 22 i i i. Tiii x. EEk. PRkk 2 22 PRk 220 * PRk 1* *2 mink. P Ti x.

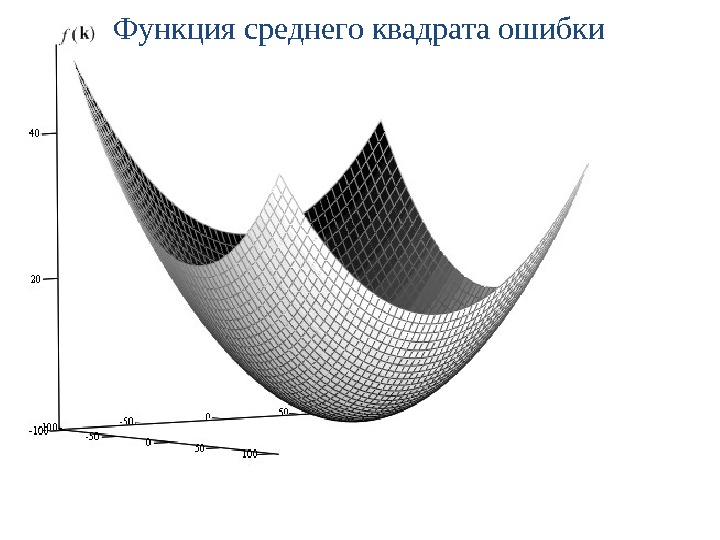

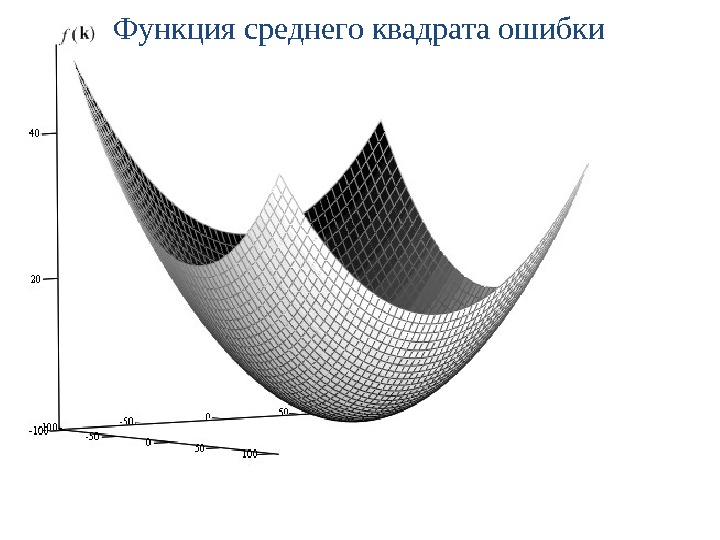

Функция среднего квадрата ошибки

Функция среднего квадрата ошибки

Другое представление градиента)()( ** minkk. Rkk i. Ti Rvv)(min i i Rv v 2 Декорреляция сигнала ошибки и входного сигнала * kk i i. Tiii xyk)( i. Tiiiiii xkyyyy)( i. Tiiiiii Ex. EEkyyyy)(

Другое представление градиента)()( ** minkk. Rkk i. Ti Rvv)(min i i Rv v 2 Декорреляция сигнала ошибки и входного сигнала * kk i i. Tiii xyk)( i. Tiiiiii xkyyyy)( i. Tiiiiii Ex. EEkyyyy)(

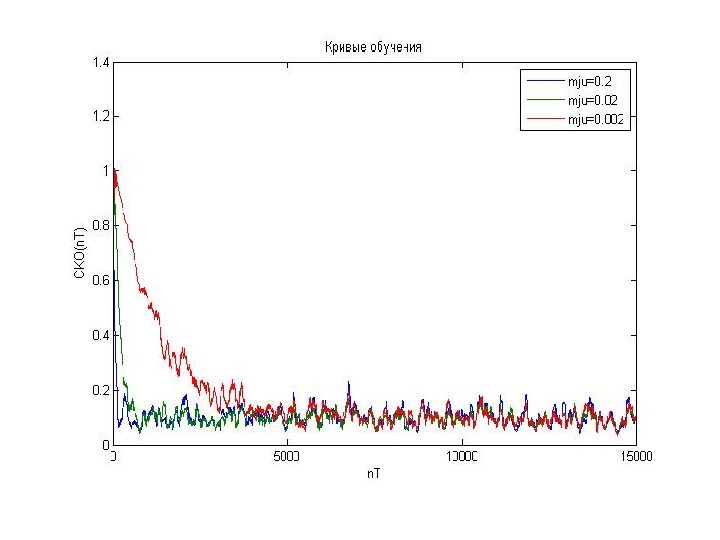

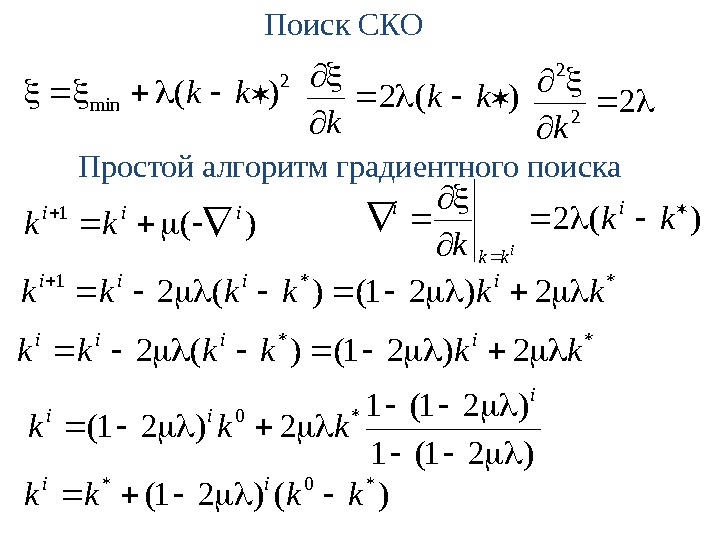

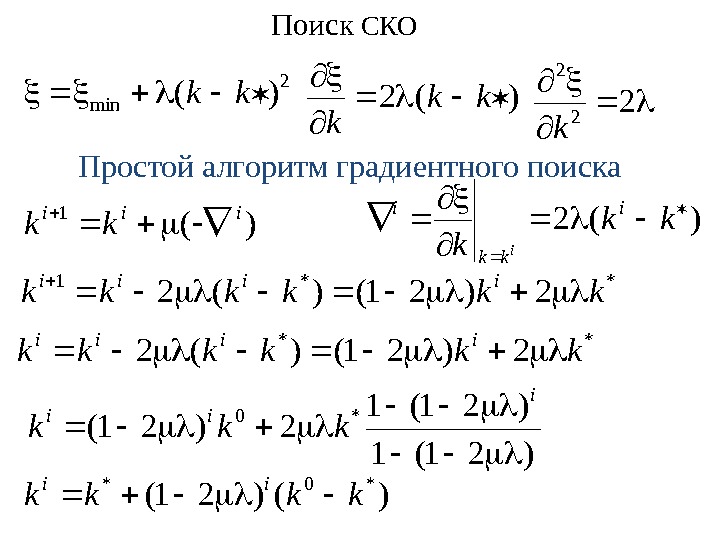

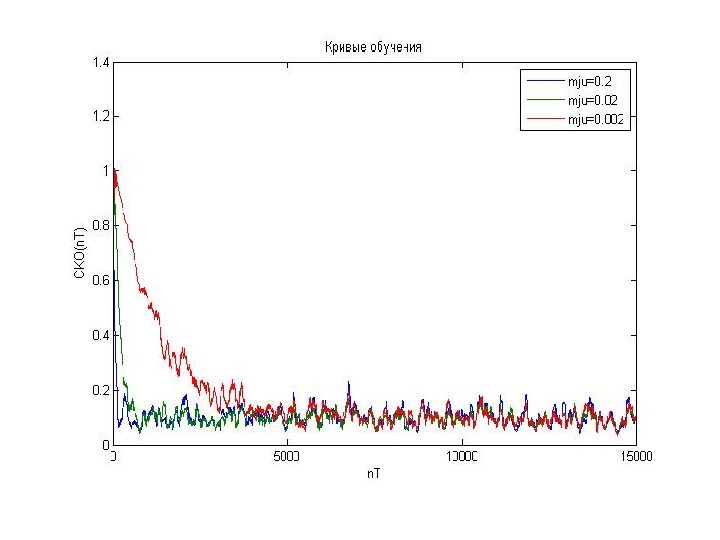

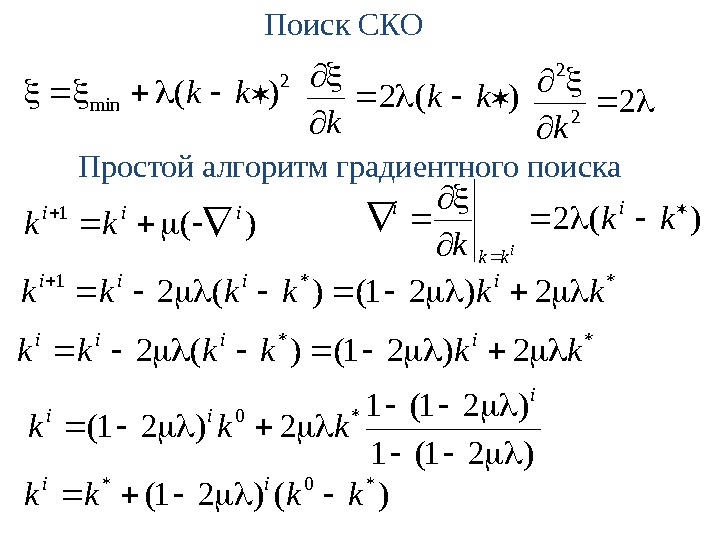

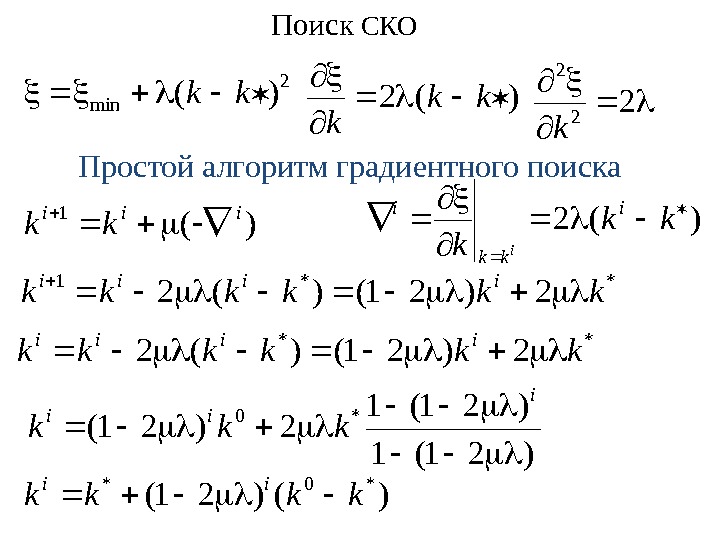

Поиск СКО 2 min)(kk)(2 kk k 2 2 2 k Простой алгоритм градиентного поиска )( 1 iii kk )(2 kk k i kk i i **1 2)21()(2 kkkkkk iiii ** 2)21()(2 kkkkkk iiii )21(1 2)21( *0 i iikkk )()21( *0* kkkk ii

Поиск СКО 2 min)(kk)(2 kk k 2 2 2 k Простой алгоритм градиентного поиска )( 1 iii kk )(2 kk k i kk i i **1 2)21()(2 kkkkkk iiii ** 2)21()(2 kkkkkk iiii )21(1 2)21( *0 i iikkk )()21( *0* kkkk ii

Поиск СКО 2 min)(kk)(2 kk k 2 2 2 k Простой алгоритм градиентного поиска )( 1 iii kk )(2 kk k i kk i i **1 2)21()(2 kkkkkk iiii ** 2)21()(2 kkkkkk iiii )21(1 2)21( *0 i iikkk )()21( *0* kkkk ii

Поиск СКО 2 min)(kk)(2 kk k 2 2 2 k Простой алгоритм градиентного поиска )( 1 iii kk )(2 kk k i kk i i **1 2)21()(2 kkkkkk iiii ** 2)21()(2 kkkkkk iiii )21(1 2)21( *0 i iikkk )()21( *0* kkkk ii