lecture3_4_pipeline.ppt

- Количество слайдов: 60

Организация конвейера #1 Lec # 1 Autumn 2006

Организация конвейера #1 Lec # 1 Autumn 2006

Конвейер команд • • • Конвейерная обработка инструкций – это метод реализации CPU, при котором множество операции над несколькими инструкциями перекрываются. Конвейер, исполняющий инструкцию, состоит из множества шагов, где на каждом - завершается этап обработки инструкции. Каждый шаг называется ступенью конвейера или стадией конвейера. Ступени или шаги соединены линейным образом: ступень за ступенью формирует конвейер-инструкций, которые входят с одного конца, проходят по ступеням и выходят на другом. Время на перемещение инструкции на один шаг дальше по конвейеру равно такту машины и определяется ступенью с наибольшим временем обработки. Конвейеризация увеличивает пропускную способность CPU - среднее число инструкций, завершенных за такт. – В идеальном случае (без тактов простоя), происходит завершение одной инструкции за машинный такт, то есть идеальное CPI = 1 – CPI - Cycles Per Instruction - среднее число тактов за которое исполняется одна инструкция. Конвейеризация не сокращает время выполнения отдельной инструкции: время, требуемое для завершения всех шагов по обработке инструкции (также называемое временем задержки завершения инструкции). – Минимальное время задержки завершения инструкции = n тактов, где n – число ступеней конвейера #2 Lec # 1 Autumn 2006

Конвейер команд • • • Конвейерная обработка инструкций – это метод реализации CPU, при котором множество операции над несколькими инструкциями перекрываются. Конвейер, исполняющий инструкцию, состоит из множества шагов, где на каждом - завершается этап обработки инструкции. Каждый шаг называется ступенью конвейера или стадией конвейера. Ступени или шаги соединены линейным образом: ступень за ступенью формирует конвейер-инструкций, которые входят с одного конца, проходят по ступеням и выходят на другом. Время на перемещение инструкции на один шаг дальше по конвейеру равно такту машины и определяется ступенью с наибольшим временем обработки. Конвейеризация увеличивает пропускную способность CPU - среднее число инструкций, завершенных за такт. – В идеальном случае (без тактов простоя), происходит завершение одной инструкции за машинный такт, то есть идеальное CPI = 1 – CPI - Cycles Per Instruction - среднее число тактов за которое исполняется одна инструкция. Конвейеризация не сокращает время выполнения отдельной инструкции: время, требуемое для завершения всех шагов по обработке инструкции (также называемое временем задержки завершения инструкции). – Минимальное время задержки завершения инструкции = n тактов, где n – число ступеней конвейера #2 Lec # 1 Autumn 2006

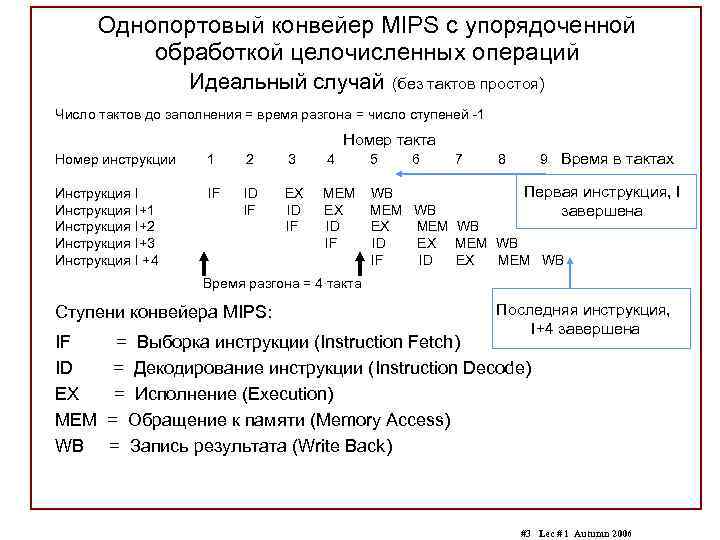

Однопортовый конвейер MIPS с упорядоченной обработкой целочисленных операций Идеальный случай (без тактов простоя) Число тактов до заполнения = время разгона = число ступеней -1 Номер такта 6 7 9 Время в тактах Номер инструкции 1 2 3 4 5 8 Инструкция I+1 Инструкция I+2 Инструкция I+3 Инструкция I +4 IF ID IF EX ID IF MEM EX ID IF Первая инструкция, I WB MEM WB завершена EX MEM WB ID EX MEM WB IF ID EX MEM WB Время разгона = 4 такта Ступени конвейера MIPS: IF ID EX MEM WB Последняя инструкция, I+4 завершена = Выборка инструкции (Instruction Fetch) = Декодирование инструкции (Instruction Decode) = Исполнение (Execution) = Обращение к памяти (Memory Access) = Запись результата (Write Back) #3 Lec # 1 Autumn 2006

Однопортовый конвейер MIPS с упорядоченной обработкой целочисленных операций Идеальный случай (без тактов простоя) Число тактов до заполнения = время разгона = число ступеней -1 Номер такта 6 7 9 Время в тактах Номер инструкции 1 2 3 4 5 8 Инструкция I+1 Инструкция I+2 Инструкция I+3 Инструкция I +4 IF ID IF EX ID IF MEM EX ID IF Первая инструкция, I WB MEM WB завершена EX MEM WB ID EX MEM WB IF ID EX MEM WB Время разгона = 4 такта Ступени конвейера MIPS: IF ID EX MEM WB Последняя инструкция, I+4 завершена = Выборка инструкции (Instruction Fetch) = Декодирование инструкции (Instruction Decode) = Исполнение (Execution) = Обращение к памяти (Memory Access) = Запись результата (Write Back) #3 Lec # 1 Autumn 2006

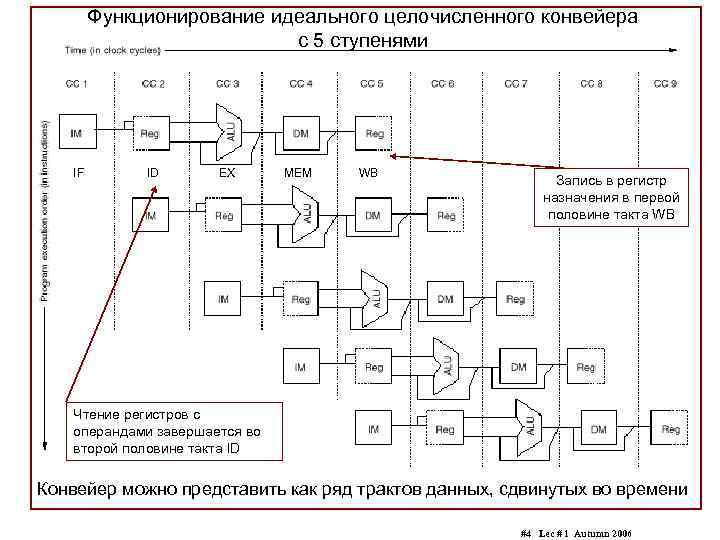

Функционирование идеального целочисленного конвейера с 5 ступенями IF ID EX MEM WB Запись в регистр назначения в первой половине такта WB Чтение регистров с операндами завершается во второй половине такта ID Конвейер можно представить как ряд трактов данных, сдвинутых во времени #4 Lec # 1 Autumn 2006

Функционирование идеального целочисленного конвейера с 5 ступенями IF ID EX MEM WB Запись в регистр назначения в первой половине такта WB Чтение регистров с операндами завершается во второй половине такта ID Конвейер можно представить как ряд трактов данных, сдвинутых во времени #4 Lec # 1 Autumn 2006

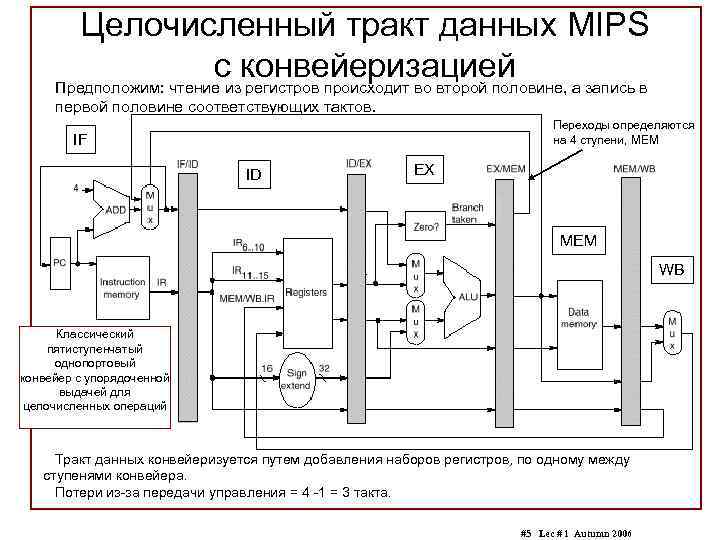

Целочисленный тракт данных MIPS сизконвейеризацией Предположим: чтение регистров происходит во второй половине, а запись в первой половине соответствующих тактов. Переходы определяются на 4 ступени, MEM IF ID EX MEM WB Классический пятиступенчатый однопортовый конвейер с упорядоченной выдачей для целочисленных операций Тракт данных конвейеризуется путем добавления наборов регистров, по одному между ступенями конвейера. Потери из-за передачи управления = 4 -1 = 3 такта. #5 Lec # 1 Autumn 2006

Целочисленный тракт данных MIPS сизконвейеризацией Предположим: чтение регистров происходит во второй половине, а запись в первой половине соответствующих тактов. Переходы определяются на 4 ступени, MEM IF ID EX MEM WB Классический пятиступенчатый однопортовый конвейер с упорядоченной выдачей для целочисленных операций Тракт данных конвейеризуется путем добавления наборов регистров, по одному между ступенями конвейера. Потери из-за передачи управления = 4 -1 = 3 такта. #5 Lec # 1 Autumn 2006

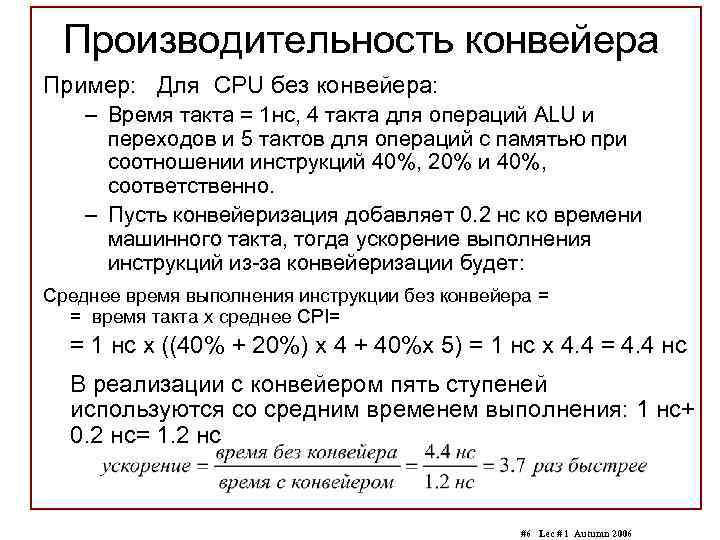

Производительность конвейера Пример: Для CPU без конвейера: – Время такта = 1 нс, 4 такта для операций ALU и переходов и 5 тактов для операций с памятью при соотношении инструкций 40%, 20% и 40%, соответственно. – Пусть конвейеризация добавляет 0. 2 нс ко времени машинного такта, тогда ускорение выполнения инструкций из-за конвейеризации будет: Среднее время выполнения инструкции без конвейера = = время такта x среднее CPI= = 1 нс x ((40% + 20%) x 4 + 40%x 5) = 1 нс x 4. 4 = 4. 4 нс В реализации с конвейером пять ступеней используются со средним временем выполнения: 1 нс+ 0. 2 нс= 1. 2 нс #6 Lec # 1 Autumn 2006

Производительность конвейера Пример: Для CPU без конвейера: – Время такта = 1 нс, 4 такта для операций ALU и переходов и 5 тактов для операций с памятью при соотношении инструкций 40%, 20% и 40%, соответственно. – Пусть конвейеризация добавляет 0. 2 нс ко времени машинного такта, тогда ускорение выполнения инструкций из-за конвейеризации будет: Среднее время выполнения инструкции без конвейера = = время такта x среднее CPI= = 1 нс x ((40% + 20%) x 4 + 40%x 5) = 1 нс x 4. 4 = 4. 4 нс В реализации с конвейером пять ступеней используются со средним временем выполнения: 1 нс+ 0. 2 нс= 1. 2 нс #6 Lec # 1 Autumn 2006

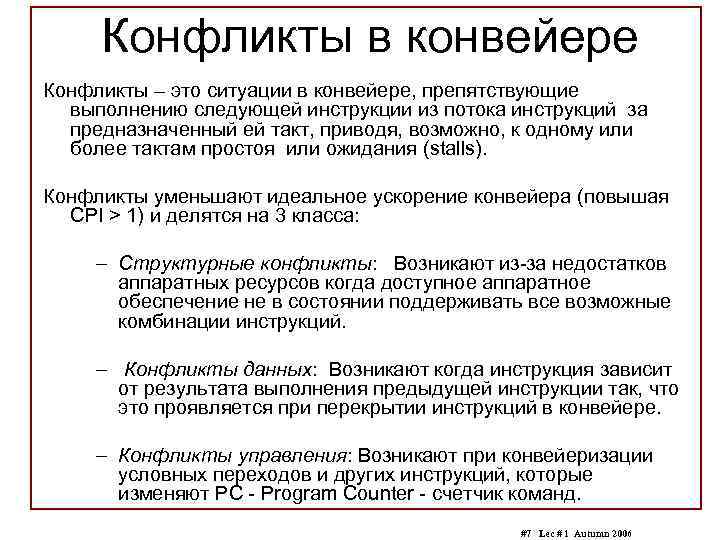

Конфликты в конвейере Конфликты – это ситуации в конвейере, препятствующие выполнению следующей инструкции из потока инструкций за предназначенный ей такт, приводя, возможно, к одному или более тактам простоя или ожидания (stalls). Конфликты уменьшают идеальное ускорение конвейера (повышая CPI > 1) и делятся на 3 класса: – Структурные конфликты: Возникают из-за недостатков аппаратных ресурсов когда доступное аппаратное обеспечение не в состоянии поддерживать все возможные комбинации инструкций. – Конфликты данных: Возникают когда инструкция зависит от результата выполнения предыдущей инструкции так, что это проявляется при перекрытии инструкций в конвейере. – Конфликты управления: Возникают при конвейеризации условных переходов и других инструкций, которые изменяют PC - Program Counter - счетчик команд. #7 Lec # 1 Autumn 2006

Конфликты в конвейере Конфликты – это ситуации в конвейере, препятствующие выполнению следующей инструкции из потока инструкций за предназначенный ей такт, приводя, возможно, к одному или более тактам простоя или ожидания (stalls). Конфликты уменьшают идеальное ускорение конвейера (повышая CPI > 1) и делятся на 3 класса: – Структурные конфликты: Возникают из-за недостатков аппаратных ресурсов когда доступное аппаратное обеспечение не в состоянии поддерживать все возможные комбинации инструкций. – Конфликты данных: Возникают когда инструкция зависит от результата выполнения предыдущей инструкции так, что это проявляется при перекрытии инструкций в конвейере. – Конфликты управления: Возникают при конвейеризации условных переходов и других инструкций, которые изменяют PC - Program Counter - счетчик команд. #7 Lec # 1 Autumn 2006

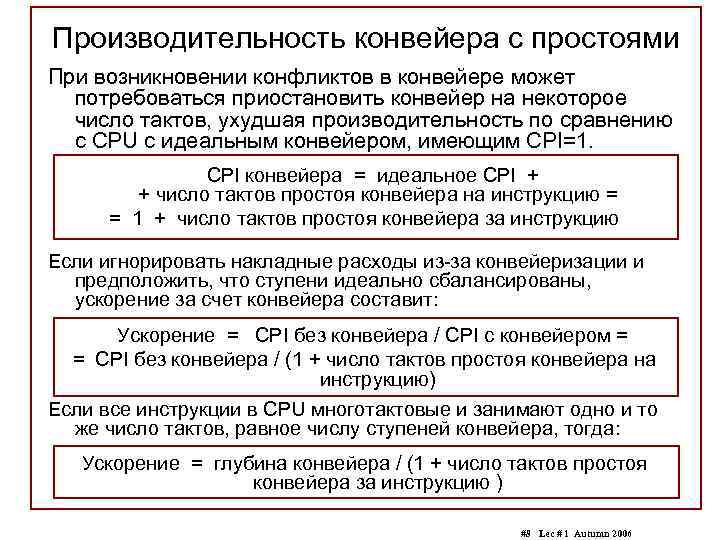

Производительность конвейера с простоями При возникновении конфликтов в конвейере может потребоваться приостановить конвейер на некоторое число тактов, ухудшая производительность по сравнению с CPU с идеальным конвейером, имеющим CPI=1. CPI конвейера = идеальное CPI + + число тактов простоя конвейера на инструкцию = = 1 + число тактов простоя конвейера за инструкцию Если игнорировать накладные расходы из-за конвейеризации и предположить, что ступени идеально сбалансированы, ускорение за счет конвейера составит: Ускорение = CPI без конвейера / CPI с конвейером = = CPI без конвейера / (1 + число тактов простоя конвейера на инструкцию) Если все инструкции в CPU многотактовые и занимают одно и то же число тактов, равное числу ступеней конвейера, тогда: Ускорение = глубина конвейера / (1 + число тактов простоя конвейера за инструкцию ) #8 Lec # 1 Autumn 2006

Производительность конвейера с простоями При возникновении конфликтов в конвейере может потребоваться приостановить конвейер на некоторое число тактов, ухудшая производительность по сравнению с CPU с идеальным конвейером, имеющим CPI=1. CPI конвейера = идеальное CPI + + число тактов простоя конвейера на инструкцию = = 1 + число тактов простоя конвейера за инструкцию Если игнорировать накладные расходы из-за конвейеризации и предположить, что ступени идеально сбалансированы, ускорение за счет конвейера составит: Ускорение = CPI без конвейера / CPI с конвейером = = CPI без конвейера / (1 + число тактов простоя конвейера на инструкцию) Если все инструкции в CPU многотактовые и занимают одно и то же число тактов, равное числу ступеней конвейера, тогда: Ускорение = глубина конвейера / (1 + число тактов простоя конвейера за инструкцию ) #8 Lec # 1 Autumn 2006

Структурные (или аппаратные) конфликты В машинах с конвейером исполнение перекрывающихся инструкций требует конвейеризации функциональных устройств и дублирования ресурсов, чтобы допустить все возможные комбинации инструкций в конвейере. Если возникает конфликт ресурсов из-за того, что аппаратный ресурс требуется более чем одной инструкции в одном и том же такте, и одна или более таких инструкций не могут быть совмещены, возникает структурный конфликт. Например: Когда конвейерной машине с общей памятью команд и данных требуется одновременно извлекать из памяти данные и инструкции происходит остановка конвейера на такт для поочередного доступа к памяти. #9 Lec # 1 Autumn 2006

Структурные (или аппаратные) конфликты В машинах с конвейером исполнение перекрывающихся инструкций требует конвейеризации функциональных устройств и дублирования ресурсов, чтобы допустить все возможные комбинации инструкций в конвейере. Если возникает конфликт ресурсов из-за того, что аппаратный ресурс требуется более чем одной инструкции в одном и том же такте, и одна или более таких инструкций не могут быть совмещены, возникает структурный конфликт. Например: Когда конвейерной машине с общей памятью команд и данных требуется одновременно извлекать из памяти данные и инструкции происходит остановка конвейера на такт для поочередного доступа к памяти. #9 Lec # 1 Autumn 2006

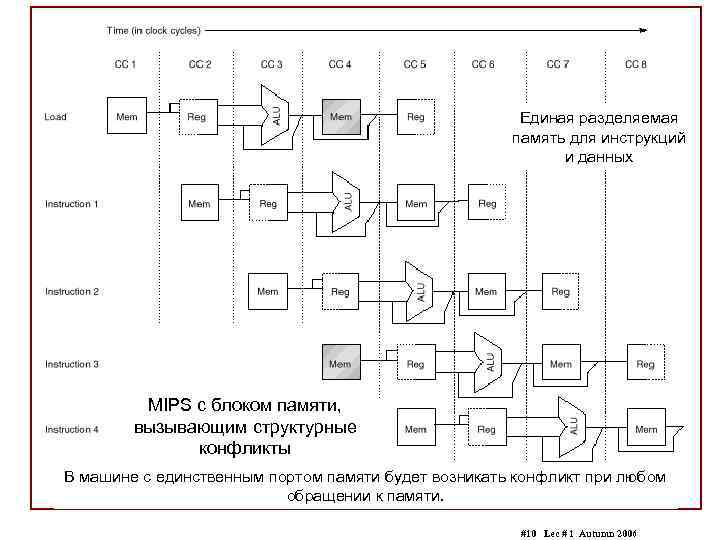

Единая разделяемая память для инструкций и данных MIPS с блоком памяти, вызывающим структурные конфликты В машине с единственным портом памяти будет возникать конфликт при любом обращении к памяти. #10 Lec # 1 Autumn 2006

Единая разделяемая память для инструкций и данных MIPS с блоком памяти, вызывающим структурные конфликты В машине с единственным портом памяти будет возникать конфликт при любом обращении к памяти. #10 Lec # 1 Autumn 2006

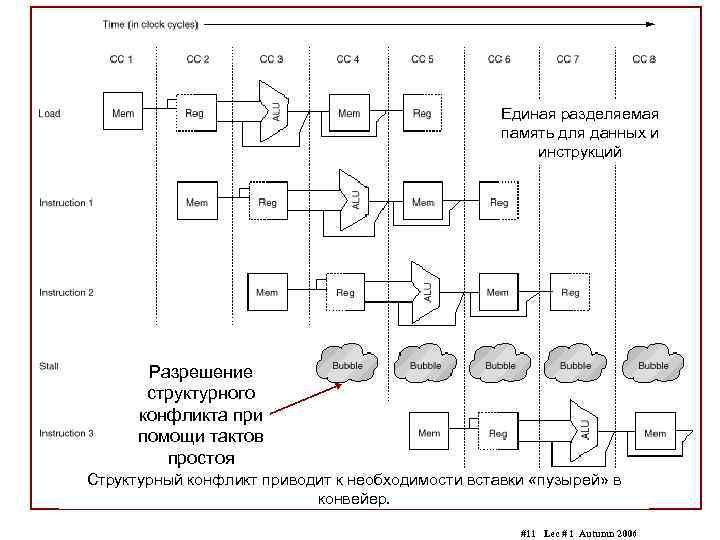

Единая разделяемая память для данных и инструкций Разрешение структурного конфликта при помощи тактов простоя Структурный конфликт приводит к необходимости вставки «пузырей» в конвейер. #11 Lec # 1 Autumn 2006

Единая разделяемая память для данных и инструкций Разрешение структурного конфликта при помощи тактов простоя Структурный конфликт приводит к необходимости вставки «пузырей» в конвейер. #11 Lec # 1 Autumn 2006

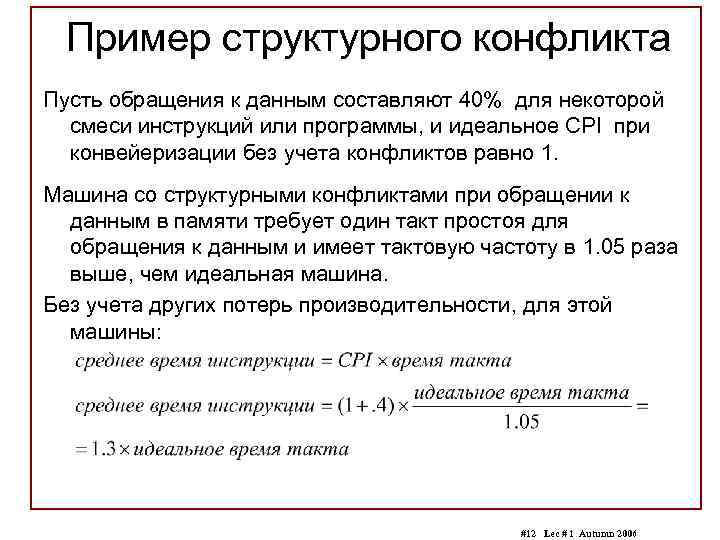

Пример структурного конфликта Пусть обращения к данным составляют 40% для некоторой смеси инструкций или программы, и идеальное CPI при конвейеризации без учета конфликтов равно 1. Машина со структурными конфликтами при обращении к данным в памяти требует один такт простоя для обращения к данным и имеет тактовую частоту в 1. 05 раза выше, чем идеальная машина. Без учета других потерь производительности, для этой машины: #12 Lec # 1 Autumn 2006

Пример структурного конфликта Пусть обращения к данным составляют 40% для некоторой смеси инструкций или программы, и идеальное CPI при конвейеризации без учета конфликтов равно 1. Машина со структурными конфликтами при обращении к данным в памяти требует один такт простоя для обращения к данным и имеет тактовую частоту в 1. 05 раза выше, чем идеальная машина. Без учета других потерь производительности, для этой машины: #12 Lec # 1 Autumn 2006

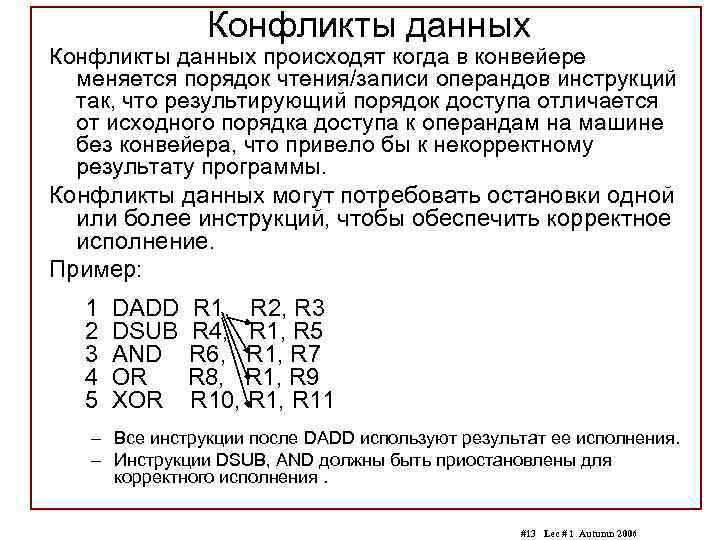

Конфликты данных происходят когда в конвейере меняется порядок чтения/записи операндов инструкций так, что результирующий порядок доступа отличается от исходного порядка доступа к операндам на машине без конвейера, что привело бы к некорректному результату программы. Конфликты данных могут потребовать остановки одной или более инструкций, чтобы обеспечить корректное исполнение. Пример: 1 2 3 4 5 DADD DSUB AND OR XOR R 1, R 2, R 3 R 4, R 1, R 5 R 6, R 1, R 7 R 8, R 1, R 9 R 10, R 11 – Все инструкции после DADD используют результат ее исполнения. – Инструкции DSUB, AND должны быть приостановлены для корректного исполнения. #13 Lec # 1 Autumn 2006

Конфликты данных происходят когда в конвейере меняется порядок чтения/записи операндов инструкций так, что результирующий порядок доступа отличается от исходного порядка доступа к операндам на машине без конвейера, что привело бы к некорректному результату программы. Конфликты данных могут потребовать остановки одной или более инструкций, чтобы обеспечить корректное исполнение. Пример: 1 2 3 4 5 DADD DSUB AND OR XOR R 1, R 2, R 3 R 4, R 1, R 5 R 6, R 1, R 7 R 8, R 1, R 9 R 10, R 11 – Все инструкции после DADD используют результат ее исполнения. – Инструкции DSUB, AND должны быть приостановлены для корректного исполнения. #13 Lec # 1 Autumn 2006

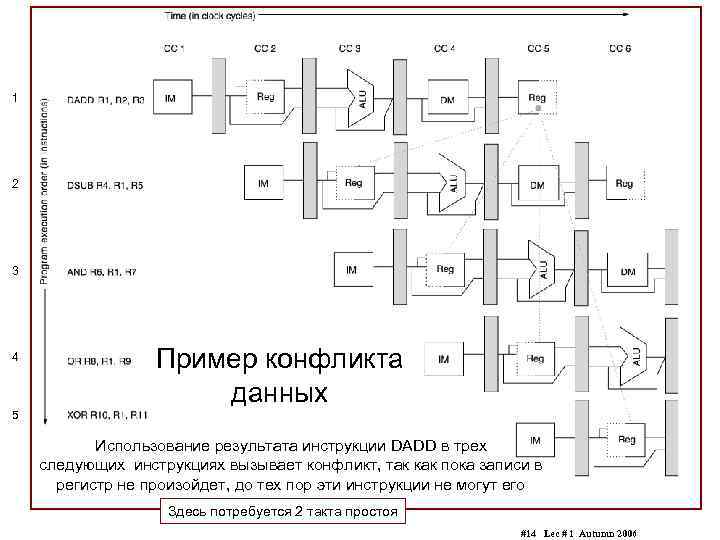

1 2 3 4 Пример конфликта данных 5 Использование результата инструкции DADD в трех следующих инструкциях вызывает конфликт, так как пока записи в регистр не произойдет, до тех пор эти инструкции не могут его прочитать. Здесь потребуется 2 такта простоя #14 Lec # 1 Autumn 2006

1 2 3 4 Пример конфликта данных 5 Использование результата инструкции DADD в трех следующих инструкциях вызывает конфликт, так как пока записи в регистр не произойдет, до тех пор эти инструкции не могут его прочитать. Здесь потребуется 2 такта простоя #14 Lec # 1 Autumn 2006

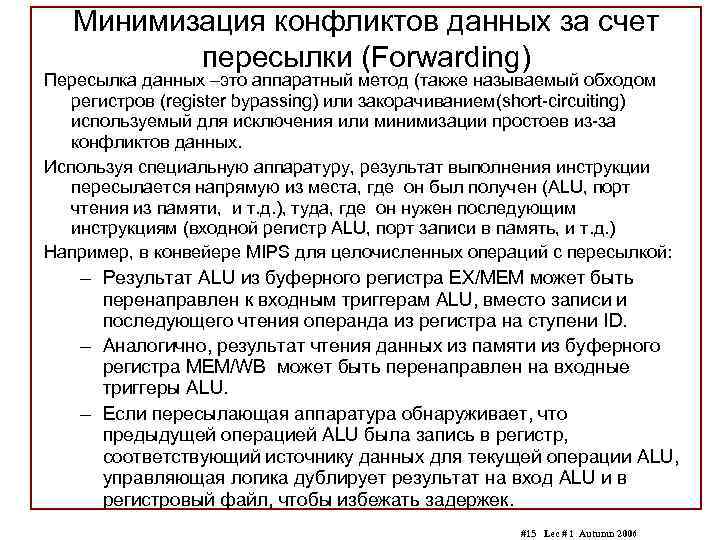

Минимизация конфликтов данных за счет пересылки (Forwarding) Пересылка данных –это аппаратный метод (также называемый обходом регистров (register bypassing) или закорачиванием(short-circuiting) используемый для исключения или минимизации простоев из-за конфликтов данных. Используя специальную аппаратуру, результат выполнения инструкции пересылается напрямую из места, где он был получен (ALU, порт чтения из памяти, и т. д. ), туда, где он нужен последующим инструкциям (входной регистр ALU, порт записи в память, и т. д. ) Например, в конвейере MIPS для целочисленных операций с пересылкой: – Результат ALU из буферного регистра EX/MEM может быть перенаправлен к входным триггерам ALU, вместо записи и последующего чтения операнда из регистра на ступени ID. – Аналогично, результат чтения данных из памяти из буферного регистра MEM/WB может быть перенаправлен на входные триггеры ALU. – Если пересылающая аппаратура обнаруживает, что предыдущей операцией ALU была запись в регистр, соответствующий источнику данных для текущей операции ALU, управляющая логика дублирует результат на вход ALU и в регистровый файл, чтобы избежать задержек. #15 Lec # 1 Autumn 2006

Минимизация конфликтов данных за счет пересылки (Forwarding) Пересылка данных –это аппаратный метод (также называемый обходом регистров (register bypassing) или закорачиванием(short-circuiting) используемый для исключения или минимизации простоев из-за конфликтов данных. Используя специальную аппаратуру, результат выполнения инструкции пересылается напрямую из места, где он был получен (ALU, порт чтения из памяти, и т. д. ), туда, где он нужен последующим инструкциям (входной регистр ALU, порт записи в память, и т. д. ) Например, в конвейере MIPS для целочисленных операций с пересылкой: – Результат ALU из буферного регистра EX/MEM может быть перенаправлен к входным триггерам ALU, вместо записи и последующего чтения операнда из регистра на ступени ID. – Аналогично, результат чтения данных из памяти из буферного регистра MEM/WB может быть перенаправлен на входные триггеры ALU. – Если пересылающая аппаратура обнаруживает, что предыдущей операцией ALU была запись в регистр, соответствующий источнику данных для текущей операции ALU, управляющая логика дублирует результат на вход ALU и в регистровый файл, чтобы избежать задержек. #15 Lec # 1 Autumn 2006

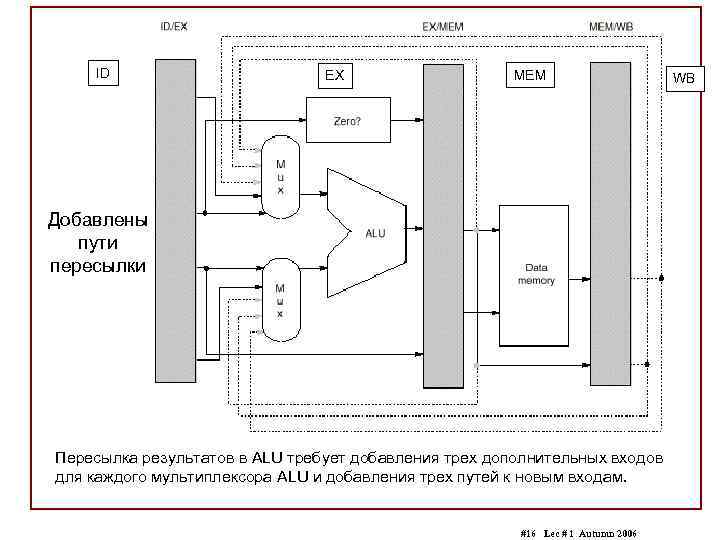

ID EX MEM Добавлены пути пересылки Пересылка результатов в ALU требует добавления трех дополнительных входов для каждого мультиплексора ALU и добавления трех путей к новым входам. #16 Lec # 1 Autumn 2006 WB

ID EX MEM Добавлены пути пересылки Пересылка результатов в ALU требует добавления трех дополнительных входов для каждого мультиплексора ALU и добавления трех путей к новым входам. #16 Lec # 1 Autumn 2006 WB

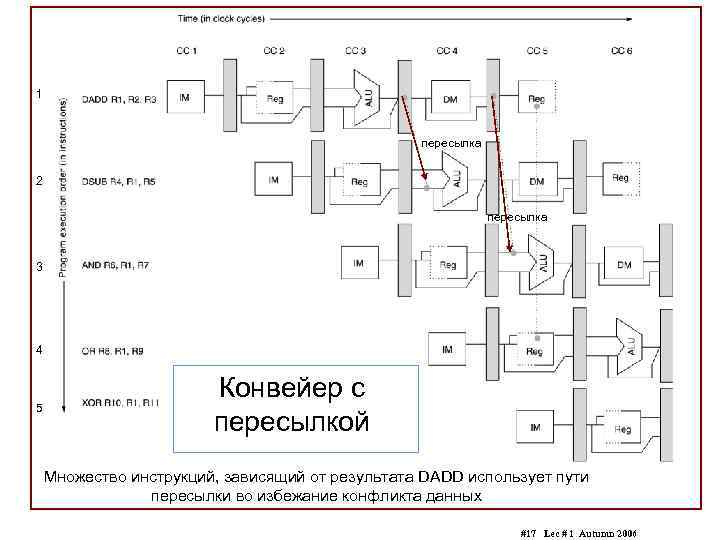

1 пересылка 2 пересылка 3 4 5 Конвейер с пересылкой Множество инструкций, зависящий от результата DADD использует пути пересылки во избежание конфликта данных #17 Lec # 1 Autumn 2006

1 пересылка 2 пересылка 3 4 5 Конвейер с пересылкой Множество инструкций, зависящий от результата DADD использует пути пересылки во избежание конфликта данных #17 Lec # 1 Autumn 2006

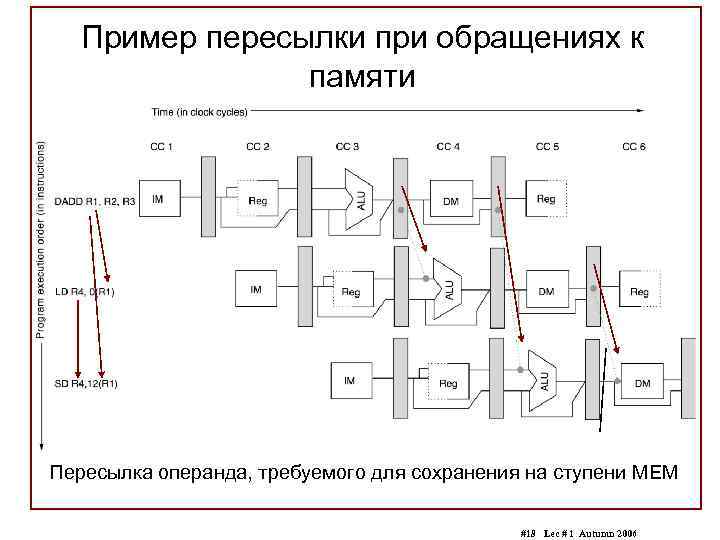

Пример пересылки при обращениях к памяти Пересылка операнда, требуемого для сохранения на ступени MEM #18 Lec # 1 Autumn 2006

Пример пересылки при обращениях к памяти Пересылка операнда, требуемого для сохранения на ступени MEM #18 Lec # 1 Autumn 2006

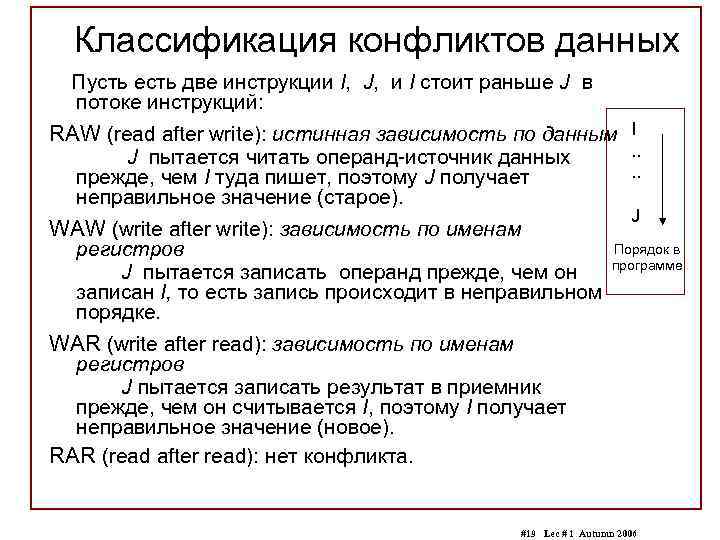

Классификация конфликтов данных Пусть есть две инструкции I, J, и I стоит раньше J в потоке инструкций: RAW (read after write): истинная зависимость по данным I. . J пытается читать операнд-источник данных. . прежде, чем I туда пишет, поэтому J получает неправильное значение (старое). J WAW (write after write): зависимость по именам Порядок в регистров программе J пытается записать операнд прежде, чем он записан I, то есть запись происходит в неправильном порядке. WAR (write after read): зависимость по именам регистров J пытается записать результат в приемник прежде, чем он считывается I, поэтому I получает неправильное значение (новое). RAR (read after read): нет конфликта. #19 Lec # 1 Autumn 2006

Классификация конфликтов данных Пусть есть две инструкции I, J, и I стоит раньше J в потоке инструкций: RAW (read after write): истинная зависимость по данным I. . J пытается читать операнд-источник данных. . прежде, чем I туда пишет, поэтому J получает неправильное значение (старое). J WAW (write after write): зависимость по именам Порядок в регистров программе J пытается записать операнд прежде, чем он записан I, то есть запись происходит в неправильном порядке. WAR (write after read): зависимость по именам регистров J пытается записать результат в приемник прежде, чем он считывается I, поэтому I получает неправильное значение (новое). RAR (read after read): нет конфликта. #19 Lec # 1 Autumn 2006

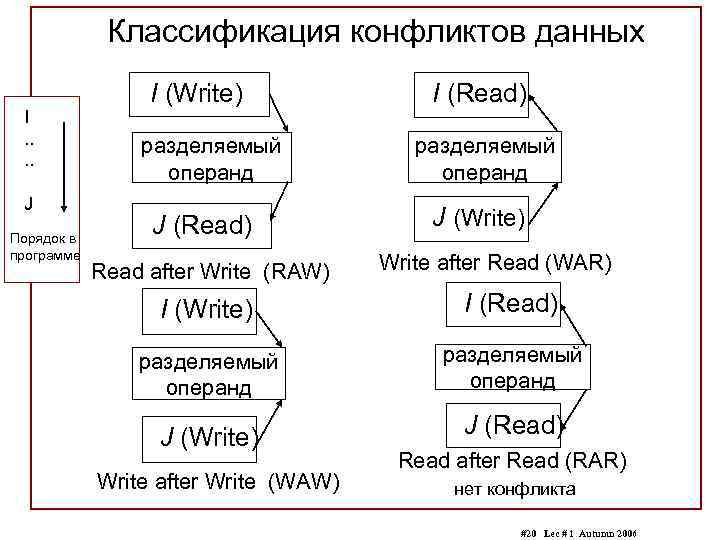

Классификация конфликтов данных I. . J Порядок в программе I (Write) разделяемый операнд J (Read) Read after Write (RAW) I (Read) разделяемый операнд J (Write) Write after Read (WAR) I (Write) I (Read) разделяемый операнд J (Write) Write after Write (WAW) J (Read) Read after Read (RAR) нет конфликта #20 Lec # 1 Autumn 2006

Классификация конфликтов данных I. . J Порядок в программе I (Write) разделяемый операнд J (Read) Read after Write (RAW) I (Read) разделяемый операнд J (Write) Write after Read (WAR) I (Write) I (Read) разделяемый операнд J (Write) Write after Write (WAW) J (Read) Read after Read (RAR) нет конфликта #20 Lec # 1 Autumn 2006

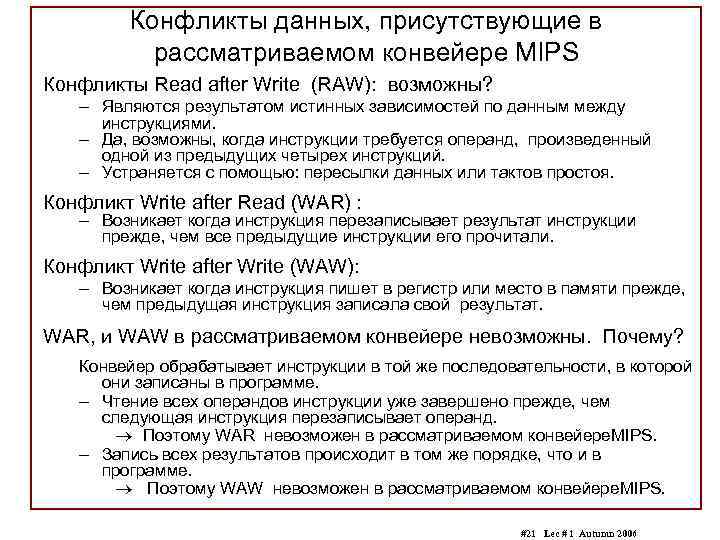

Конфликты данных, присутствующие в рассматриваемом конвейере MIPS Конфликты Read after Write (RAW): возможны? – Являются результатом истинных зависимостей по данным между инструкциями. – Да, возможны, когда инструкции требуется операнд, произведенный одной из предыдущих четырех инструкций. – Устраняется с помощью: пересылки данных или тактов простоя. Конфликт Write after Read (WAR) : – Возникает когда инструкция перезаписывает результат инструкции прежде, чем все предыдущие инструкции его прочитали. Конфликт Write after Write (WAW): – Возникает когда инструкция пишет в регистр или место в памяти прежде, чем предыдущая инструкция записала свой результат. WAR, и WAW в рассматриваемом конвейере невозможны. Почему? Конвейер обрабатывает инструкции в той же последовательности, в которой они записаны в программе. – Чтение всех операндов инструкции уже завершено прежде, чем следующая инструкция перезаписывает операнд. ® Поэтому WAR невозможен в рассматриваемом конвейере. MIPS. – Запись всех результатов происходит в том же порядке, что и в программе. ® Поэтому WAW невозможен в рассматриваемом конвейере. MIPS. #21 Lec # 1 Autumn 2006

Конфликты данных, присутствующие в рассматриваемом конвейере MIPS Конфликты Read after Write (RAW): возможны? – Являются результатом истинных зависимостей по данным между инструкциями. – Да, возможны, когда инструкции требуется операнд, произведенный одной из предыдущих четырех инструкций. – Устраняется с помощью: пересылки данных или тактов простоя. Конфликт Write after Read (WAR) : – Возникает когда инструкция перезаписывает результат инструкции прежде, чем все предыдущие инструкции его прочитали. Конфликт Write after Write (WAW): – Возникает когда инструкция пишет в регистр или место в памяти прежде, чем предыдущая инструкция записала свой результат. WAR, и WAW в рассматриваемом конвейере невозможны. Почему? Конвейер обрабатывает инструкции в той же последовательности, в которой они записаны в программе. – Чтение всех операндов инструкции уже завершено прежде, чем следующая инструкция перезаписывает операнд. ® Поэтому WAR невозможен в рассматриваемом конвейере. MIPS. – Запись всех результатов происходит в том же порядке, что и в программе. ® Поэтому WAW невозможен в рассматриваемом конвейере. MIPS. #21 Lec # 1 Autumn 2006

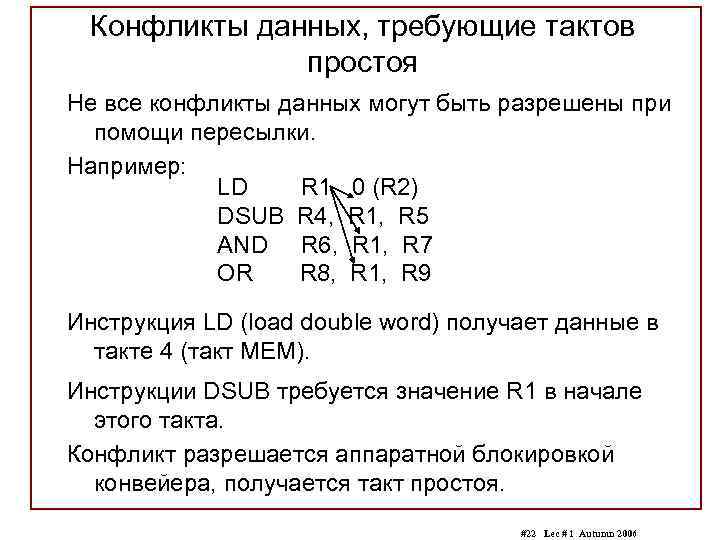

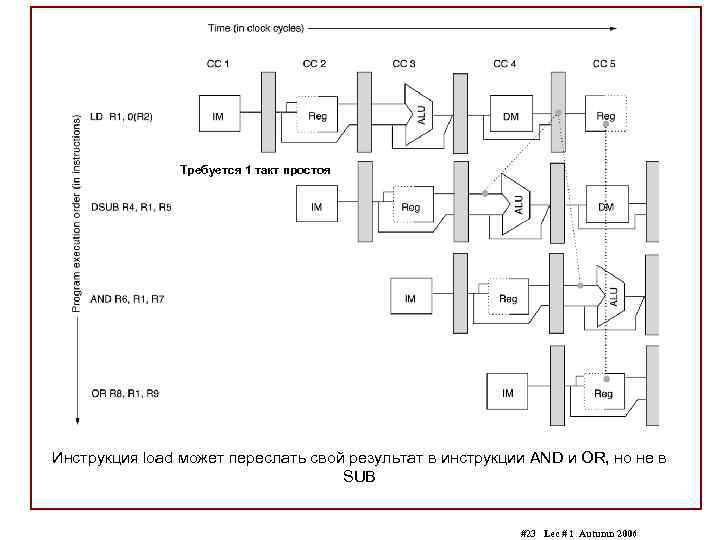

Конфликты данных, требующие тактов простоя Не все конфликты данных могут быть разрешены при помощи пересылки. Например: LD R 1, 0 (R 2) DSUB R 4, R 1, R 5 AND R 6, R 1, R 7 OR R 8, R 1, R 9 Инструкция LD (load double word) получает данные в такте 4 (такт MEM). Инструкции DSUB требуется значение R 1 в начале этого такта. Конфликт разрешается аппаратной блокировкой конвейера, получается такт простоя. #22 Lec # 1 Autumn 2006

Конфликты данных, требующие тактов простоя Не все конфликты данных могут быть разрешены при помощи пересылки. Например: LD R 1, 0 (R 2) DSUB R 4, R 1, R 5 AND R 6, R 1, R 7 OR R 8, R 1, R 9 Инструкция LD (load double word) получает данные в такте 4 (такт MEM). Инструкции DSUB требуется значение R 1 в начале этого такта. Конфликт разрешается аппаратной блокировкой конвейера, получается такт простоя. #22 Lec # 1 Autumn 2006

Требуется 1 такт простоя Инструкция load может переслать свой результат в инструкции AND и OR, но не в SUB #23 Lec # 1 Autumn 2006

Требуется 1 такт простоя Инструкция load может переслать свой результат в инструкции AND и OR, но не в SUB #23 Lec # 1 Autumn 2006

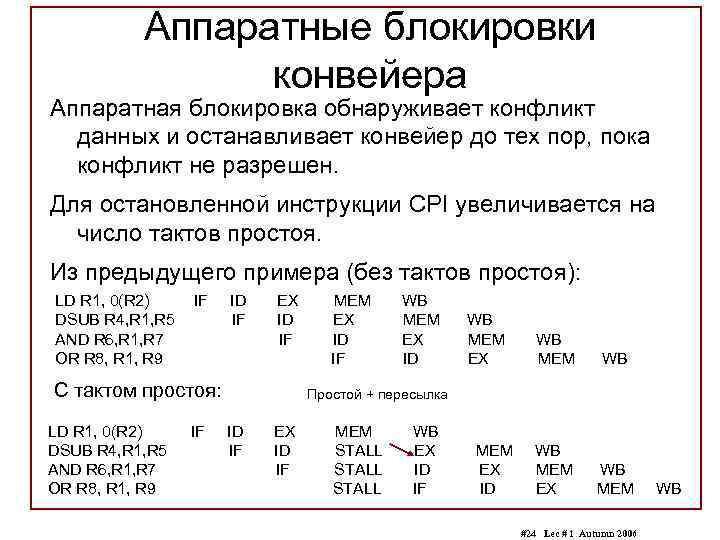

Аппаратные блокировки конвейера Аппаратная блокировка обнаруживает конфликт данных и останавливает конвейер до тех пор, пока конфликт не разрешен. Для остановленной инструкции CPI увеличивается на число тактов простоя. Из предыдущего примера (без тактов простоя): LD R 1, 0(R 2) DSUB R 4, R 1, R 5 AND R 6, R 1, R 7 OR R 8, R 1, R 9 IF ID IF EX ID IF С тактом простоя: LD R 1, 0(R 2) DSUB R 4, R 1, R 5 AND R 6, R 1, R 7 OR R 8, R 1, R 9 IF MEM EX ID IF WB MEM EX ID WB MEM EX WB MEM WB WB MEM EX WB MEM Простой + пересылка ID IF EX ID IF MEM STALL WB EX ID IF MEM EX ID #24 Lec # 1 Autumn 2006 WB

Аппаратные блокировки конвейера Аппаратная блокировка обнаруживает конфликт данных и останавливает конвейер до тех пор, пока конфликт не разрешен. Для остановленной инструкции CPI увеличивается на число тактов простоя. Из предыдущего примера (без тактов простоя): LD R 1, 0(R 2) DSUB R 4, R 1, R 5 AND R 6, R 1, R 7 OR R 8, R 1, R 9 IF ID IF EX ID IF С тактом простоя: LD R 1, 0(R 2) DSUB R 4, R 1, R 5 AND R 6, R 1, R 7 OR R 8, R 1, R 9 IF MEM EX ID IF WB MEM EX ID WB MEM EX WB MEM WB WB MEM EX WB MEM Простой + пересылка ID IF EX ID IF MEM STALL WB EX ID IF MEM EX ID #24 Lec # 1 Autumn 2006 WB

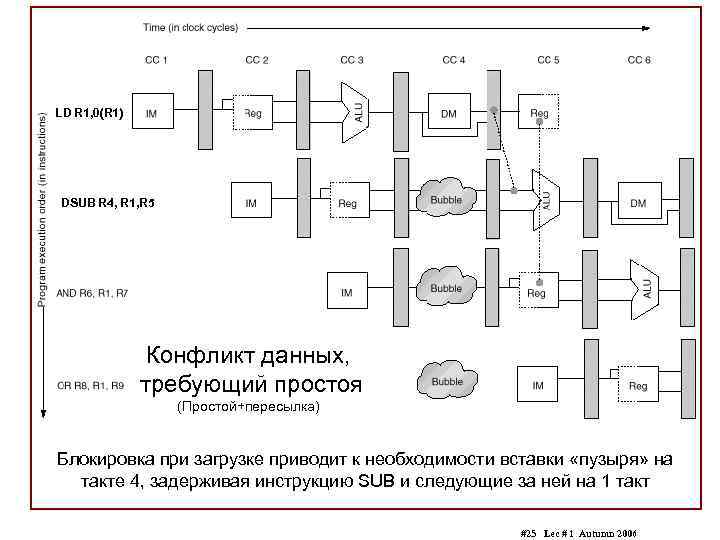

LD R 1, 0(R 1) DSUB R 4, R 1, R 5 Конфликт данных, требующий простоя (Простой+пересылка) Блокировка при загрузке приводит к необходимости вставки «пузыря» на такте 4, задерживая инструкцию SUB и следующие за ней на 1 такт #25 Lec # 1 Autumn 2006

LD R 1, 0(R 1) DSUB R 4, R 1, R 5 Конфликт данных, требующий простоя (Простой+пересылка) Блокировка при загрузке приводит к необходимости вставки «пузыря» на такте 4, задерживая инструкцию SUB и следующие за ней на 1 такт #25 Lec # 1 Autumn 2006

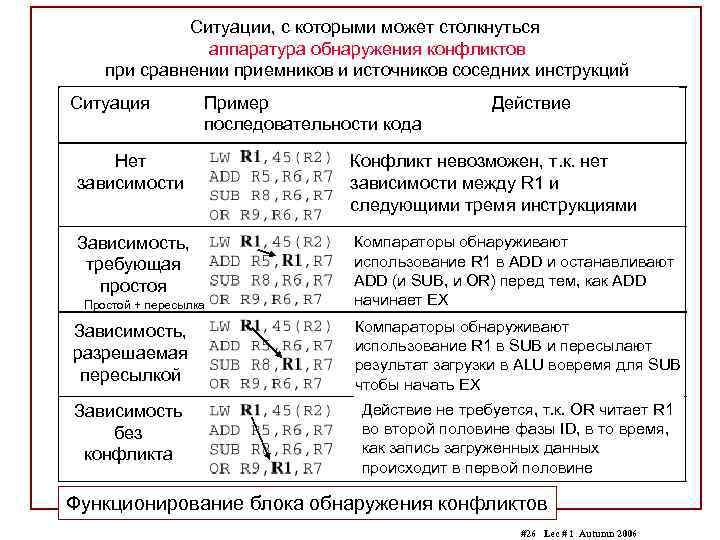

Ситуации, с которыми может столкнуться аппаратура обнаружения конфликтов при сравнении приемников и источников соседних инструкций Ситуация Пример последовательности кода Действие Нет зависимости Конфликт невозможен, т. к. нет зависимости между R 1 и следующими тремя инструкциями Зависимость, требующая простоя Компараторы обнаруживают использование R 1 в ADD и останавливают ADD (и SUB, и OR) перед тем, как ADD начинает EX Простой + пересылка Зависимость, разрешаемая пересылкой Компараторы обнаруживают использование R 1 в SUB и пересылают результат загрузки в ALU вовремя для SUB чтобы начать EX Зависимость без конфликта Действие не требуется, т. к. OR читает R 1 во второй половине фазы ID, в то время, как запись загруженных данных происходит в первой половине Функционирование блока обнаружения конфликтов #26 Lec # 1 Autumn 2006

Ситуации, с которыми может столкнуться аппаратура обнаружения конфликтов при сравнении приемников и источников соседних инструкций Ситуация Пример последовательности кода Действие Нет зависимости Конфликт невозможен, т. к. нет зависимости между R 1 и следующими тремя инструкциями Зависимость, требующая простоя Компараторы обнаруживают использование R 1 в ADD и останавливают ADD (и SUB, и OR) перед тем, как ADD начинает EX Простой + пересылка Зависимость, разрешаемая пересылкой Компараторы обнаруживают использование R 1 в SUB и пересылают результат загрузки в ALU вовремя для SUB чтобы начать EX Зависимость без конфликта Действие не требуется, т. к. OR читает R 1 во второй половине фазы ID, в то время, как запись загруженных данных происходит в первой половине Функционирование блока обнаружения конфликтов #26 Lec # 1 Autumn 2006

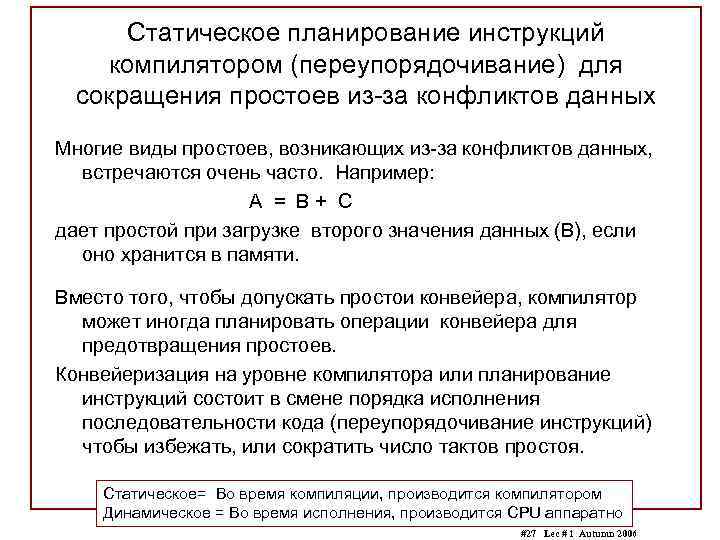

Статическое планирование инструкций компилятором (переупорядочивание) для сокращения простоев из-за конфликтов данных Многие виды простоев, возникающих из-за конфликтов данных, встречаются очень часто. Например: A = B+ C дает простой при загрузке второго значения данных (B), если оно хранится в памяти. Вместо того, чтобы допускать простои конвейера, компилятор может иногда планировать операции конвейера для предотвращения простоев. Конвейеризация на уровне компилятора или планирование инструкций состоит в смене порядка исполнения последовательности кода (переупорядочивание инструкций) чтобы избежать, или сократить число тактов простоя. Статическое= Во время компиляции, производится компилятором Динамическое = Во время исполнения, производится CPU аппаратно #27 Lec # 1 Autumn 2006

Статическое планирование инструкций компилятором (переупорядочивание) для сокращения простоев из-за конфликтов данных Многие виды простоев, возникающих из-за конфликтов данных, встречаются очень часто. Например: A = B+ C дает простой при загрузке второго значения данных (B), если оно хранится в памяти. Вместо того, чтобы допускать простои конвейера, компилятор может иногда планировать операции конвейера для предотвращения простоев. Конвейеризация на уровне компилятора или планирование инструкций состоит в смене порядка исполнения последовательности кода (переупорядочивание инструкций) чтобы избежать, или сократить число тактов простоя. Статическое= Во время компиляции, производится компилятором Динамическое = Во время исполнения, производится CPU аппаратно #27 Lec # 1 Autumn 2006

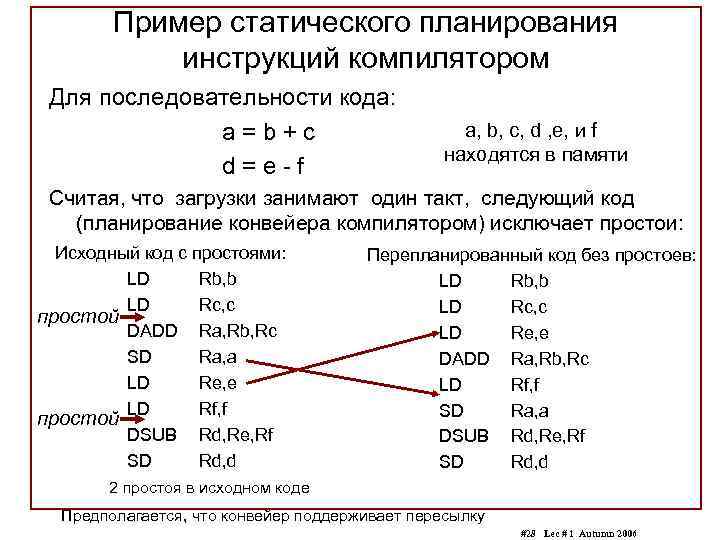

Пример статического планирования инструкций компилятором Для последовательности кода: a=b+c d=e-f a, b, c, d , e, и f находятся в памяти Считая, что загрузки занимают один такт, следующий код (планирование конвейера компилятором) исключает простои: Исходный код с простоями: LD Rb, b LD Rc, c простой DADD Ra, Rb, Rc SD Ra, a LD Re, e LD Rf, f простой DSUB Rd, Re, Rf SD Rd, d Перепланированный код без простоев: LD Rb, b LD Rc, c LD Re, e DADD Ra, Rb, Rc LD Rf, f SD Ra, a DSUB Rd, Re, Rf SD Rd, d 2 простоя в исходном коде Предполагается, что конвейер поддерживает пересылку #28 Lec # 1 Autumn 2006

Пример статического планирования инструкций компилятором Для последовательности кода: a=b+c d=e-f a, b, c, d , e, и f находятся в памяти Считая, что загрузки занимают один такт, следующий код (планирование конвейера компилятором) исключает простои: Исходный код с простоями: LD Rb, b LD Rc, c простой DADD Ra, Rb, Rc SD Ra, a LD Re, e LD Rf, f простой DSUB Rd, Re, Rf SD Rd, d Перепланированный код без простоев: LD Rb, b LD Rc, c LD Re, e DADD Ra, Rb, Rc LD Rf, f SD Ra, a DSUB Rd, Re, Rf SD Rd, d 2 простоя в исходном коде Предполагается, что конвейер поддерживает пересылку #28 Lec # 1 Autumn 2006

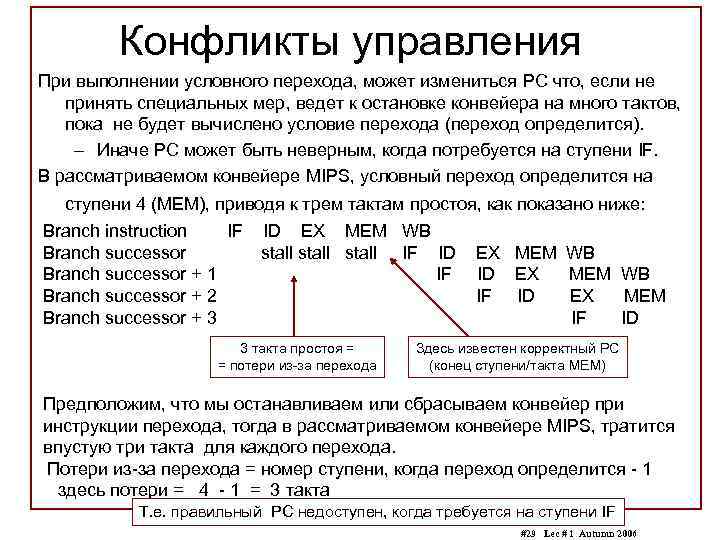

Конфликты управления При выполнении условного перехода, может измениться PC что, если не принять специальных мер, ведет к остановке конвейера на много тактов, пока не будет вычислено условие перехода (переход определится). – Иначе PC может быть неверным, когда потребуется на ступени IF. В рассматриваемом конвейере MIPS, условный переход определится на ступени 4 (MEM), приводя к трем тактам простоя, как показано ниже: Branch instruction IF ID EX MEM WB Branch successor stall IF ID Branch successor + 1 IF Branch successor + 2 Branch successor + 3 3 такта простоя = = потери из-за перехода EX MEM WB ID EX MEM WB IF ID EX MEM IF ID Здесь известен корректный PC (конец ступени/такта MEM) Предположим, что мы останавливаем или сбрасываем конвейер при инструкции перехода, тогда в рассматриваемом конвейере MIPS, тратится впустую три такта для каждого перехода. Потери из-за перехода = номер ступени, когда переход определится - 1 здесь потери = 4 - 1 = 3 такта Т. е. правильный PC недоступен, когда требуется на ступени IF #29 Lec # 1 Autumn 2006

Конфликты управления При выполнении условного перехода, может измениться PC что, если не принять специальных мер, ведет к остановке конвейера на много тактов, пока не будет вычислено условие перехода (переход определится). – Иначе PC может быть неверным, когда потребуется на ступени IF. В рассматриваемом конвейере MIPS, условный переход определится на ступени 4 (MEM), приводя к трем тактам простоя, как показано ниже: Branch instruction IF ID EX MEM WB Branch successor stall IF ID Branch successor + 1 IF Branch successor + 2 Branch successor + 3 3 такта простоя = = потери из-за перехода EX MEM WB ID EX MEM WB IF ID EX MEM IF ID Здесь известен корректный PC (конец ступени/такта MEM) Предположим, что мы останавливаем или сбрасываем конвейер при инструкции перехода, тогда в рассматриваемом конвейере MIPS, тратится впустую три такта для каждого перехода. Потери из-за перехода = номер ступени, когда переход определится - 1 здесь потери = 4 - 1 = 3 такта Т. е. правильный PC недоступен, когда требуется на ступени IF #29 Lec # 1 Autumn 2006

Сокращение числа тактов простоя из-за переходов Аппаратные способы сокращения числа тактов простоя: 1 - Как можно раньше в конвейере выяснить, выполняем ли переход. 2 - Как можно раньше в конвейере вычислить результирующий PC. В MIPS: – инструкции условного перехода BEQZ, BNE, проверяют значение регистра на равенство нулю. – это действие можно завершить в такте ID, перемещая тест на 0 в этот такт. – оба PC (выбранный и невыбранный) должны быть вычислены заранее. – требуется дополнительный сумматор так как имеющееся ALU не может быть использовано до такта EX. – в таком случае будет только один такт простоя при переходах. #30 Lec # 1 Autumn 2006

Сокращение числа тактов простоя из-за переходов Аппаратные способы сокращения числа тактов простоя: 1 - Как можно раньше в конвейере выяснить, выполняем ли переход. 2 - Как можно раньше в конвейере вычислить результирующий PC. В MIPS: – инструкции условного перехода BEQZ, BNE, проверяют значение регистра на равенство нулю. – это действие можно завершить в такте ID, перемещая тест на 0 в этот такт. – оба PC (выбранный и невыбранный) должны быть вычислены заранее. – требуется дополнительный сумматор так как имеющееся ALU не может быть использовано до такта EX. – в таком случае будет только один такт простоя при переходах. #30 Lec # 1 Autumn 2006

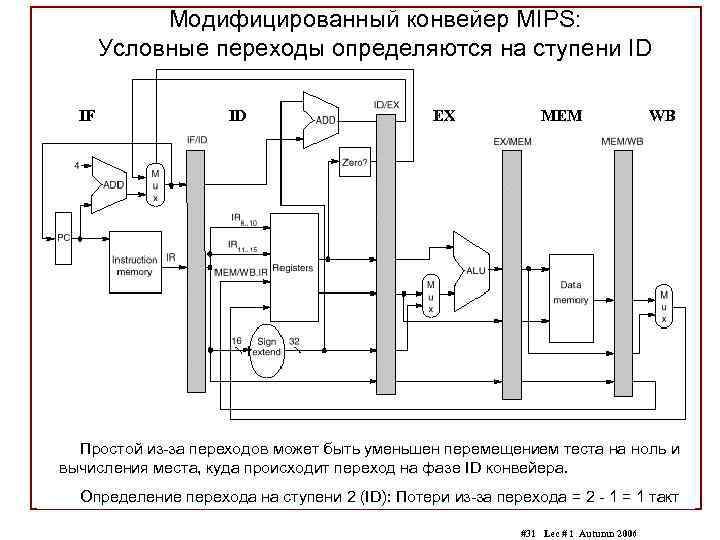

Модифицированный конвейер MIPS: Условные переходы определяются на ступени ID IF ID EX MEM WB Простой из-за переходов может быть уменьшен перемещением теста на ноль и вычисления места, куда происходит переход на фазе ID конвейера. Определение перехода на ступени 2 (ID): Потери из-за перехода = 2 - 1 = 1 такт #31 Lec # 1 Autumn 2006

Модифицированный конвейер MIPS: Условные переходы определяются на ступени ID IF ID EX MEM WB Простой из-за переходов может быть уменьшен перемещением теста на ноль и вычисления места, куда происходит переход на фазе ID конвейера. Определение перехода на ступени 2 (ID): Потери из-за перехода = 2 - 1 = 1 такт #31 Lec # 1 Autumn 2006

Статические методы обработки переходов Как обрабатывать переходы в CPU с конвейером? 1 Схема, обсужденная раньше состоит в сбросе или остановке конвейера при каждом обнаружении условного перехода путем задерживания или удаления всех инструкций в конвейере, до тех пор, пока место назначения перехода не будет известно (не нужны дополнительные регистры, шины управления). 2 Другой метод заключается в предсказании того, что данный переход не произойдет и состояние машины не меняется до Наиболее тех пор, пока результат перехода точно не определен. При распро- этом исполнение продолжается со следующей инструкции; странено простой случается, когда данный переход происходит. 3 Еще в одном методе предсказывают, что переход произойдет и начинают выборку и исполнение из места перехода; простой случается, когда переход не происходит. 4 Задержанный переход: Инструкция, следующая после перехода из слота задержки перехода исполняется независимо от того, произошел переход или нет (такая инструкция должна быть обозначена программистом). #32 Lec # 1 Autumn 2006

Статические методы обработки переходов Как обрабатывать переходы в CPU с конвейером? 1 Схема, обсужденная раньше состоит в сбросе или остановке конвейера при каждом обнаружении условного перехода путем задерживания или удаления всех инструкций в конвейере, до тех пор, пока место назначения перехода не будет известно (не нужны дополнительные регистры, шины управления). 2 Другой метод заключается в предсказании того, что данный переход не произойдет и состояние машины не меняется до Наиболее тех пор, пока результат перехода точно не определен. При распро- этом исполнение продолжается со следующей инструкции; странено простой случается, когда данный переход происходит. 3 Еще в одном методе предсказывают, что переход произойдет и начинают выборку и исполнение из места перехода; простой случается, когда переход не происходит. 4 Задержанный переход: Инструкция, следующая после перехода из слота задержки перехода исполняется независимо от того, произошел переход или нет (такая инструкция должна быть обозначена программистом). #32 Lec # 1 Autumn 2006

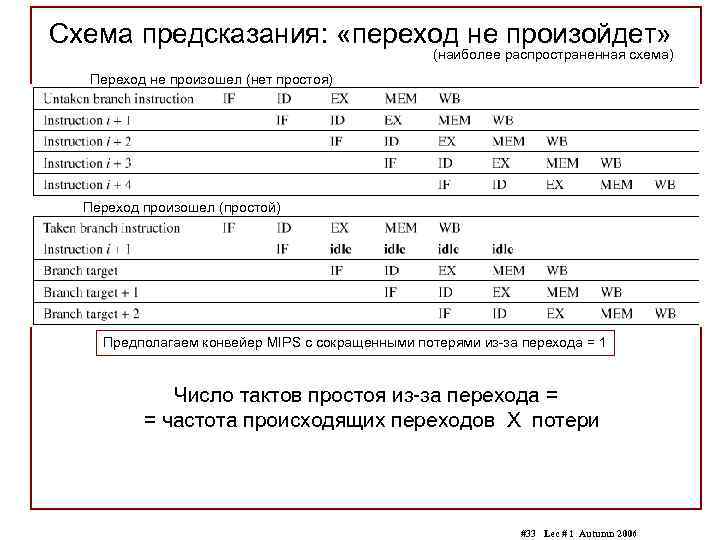

Схема предсказания: «переход не произойдет» (наиболее распространенная схема) Переход не произошел (нет простоя) Переход произошел (простой) Предполагаем конвейер MIPS с сокращенными потерями из-за перехода = 1 Число тактов простоя из-за перехода = = частота происходящих переходов X потери #33 Lec # 1 Autumn 2006

Схема предсказания: «переход не произойдет» (наиболее распространенная схема) Переход не произошел (нет простоя) Переход произошел (простой) Предполагаем конвейер MIPS с сокращенными потерями из-за перехода = 1 Число тактов простоя из-за перехода = = частота происходящих переходов X потери #33 Lec # 1 Autumn 2006

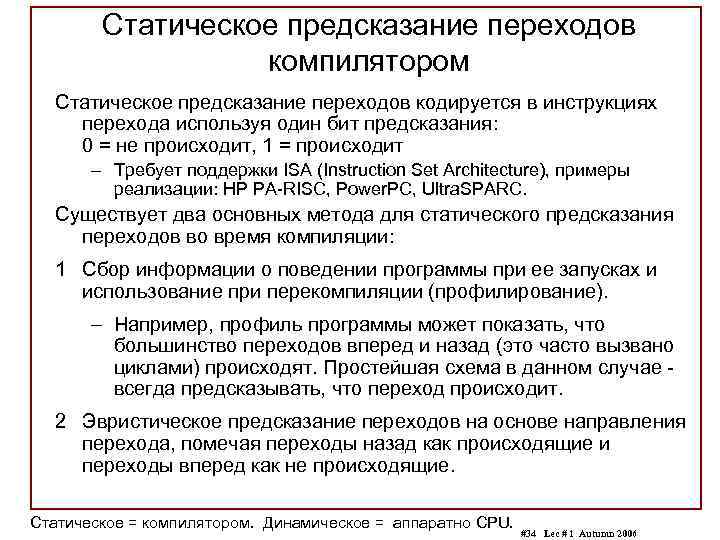

Статическое предсказание переходов компилятором Статическое предсказание переходов кодируется в инструкциях перехода используя один бит предсказания: 0 = не происходит, 1 = происходит – Требует поддержки ISA (Instruction Set Architecture), примеры реализации: HP PA-RISC, Power. PC, Ultra. SPARC. Существует два основных метода для статического предсказания переходов во время компиляции: 1 Сбор информации о поведении программы при ее запусках и использование при перекомпиляции (профилирование). – Например, профиль программы может показать, что большинство переходов вперед и назад (это часто вызвано циклами) происходят. Простейшая схема в данном случае всегда предсказывать, что переход происходит. 2 Эвристическое предсказание переходов на основе направления перехода, помечая переходы назад как происходящие и переходы вперед как не происходящие. Статическое = компилятором. Динамическое = аппаратно CPU. #34 Lec # 1 Autumn 2006

Статическое предсказание переходов компилятором Статическое предсказание переходов кодируется в инструкциях перехода используя один бит предсказания: 0 = не происходит, 1 = происходит – Требует поддержки ISA (Instruction Set Architecture), примеры реализации: HP PA-RISC, Power. PC, Ultra. SPARC. Существует два основных метода для статического предсказания переходов во время компиляции: 1 Сбор информации о поведении программы при ее запусках и использование при перекомпиляции (профилирование). – Например, профиль программы может показать, что большинство переходов вперед и назад (это часто вызвано циклами) происходят. Простейшая схема в данном случае всегда предсказывать, что переход происходит. 2 Эвристическое предсказание переходов на основе направления перехода, помечая переходы назад как происходящие и переходы вперед как не происходящие. Статическое = компилятором. Динамическое = аппаратно CPU. #34 Lec # 1 Autumn 2006

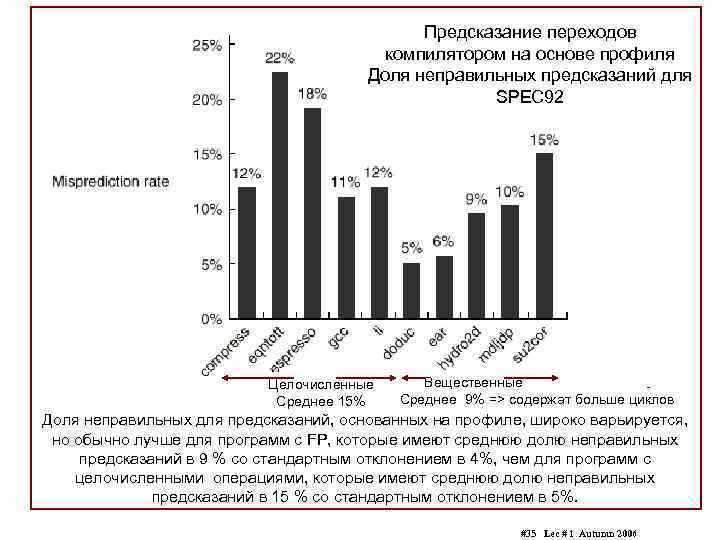

Предсказание переходов компилятором на основе профиля Доля неправильных предсказаний для SPEC 92 Целочисленные Среднее 15% Вещественные Среднее 9% => содержат больше циклов _ Доля неправильных для предсказаний, основанных на профиле, широко варьируется, но обычно лучше для программ с FP, которые имеют среднюю долю неправильных предсказаний в 9 % со стандартным отклонением в 4%, чем для программ с целочисленными операциями, которые имеют среднюю долю неправильных предсказаний в 15 % со стандартным отклонением в 5%. #35 Lec # 1 Autumn 2006

Предсказание переходов компилятором на основе профиля Доля неправильных предсказаний для SPEC 92 Целочисленные Среднее 15% Вещественные Среднее 9% => содержат больше циклов _ Доля неправильных для предсказаний, основанных на профиле, широко варьируется, но обычно лучше для программ с FP, которые имеют среднюю долю неправильных предсказаний в 9 % со стандартным отклонением в 4%, чем для программ с целочисленными операциями, которые имеют среднюю долю неправильных предсказаний в 15 % со стандартным отклонением в 5%. #35 Lec # 1 Autumn 2006

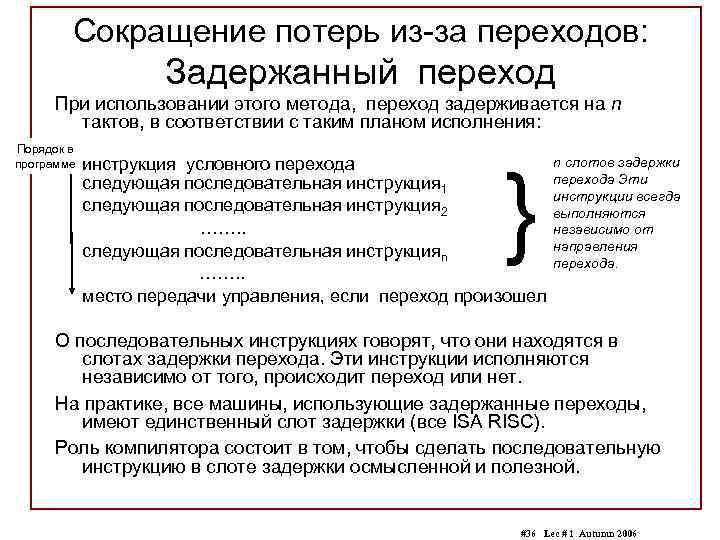

Сокращение потерь из-за переходов: Задержанный переход При использовании этого метода, переход задерживается на n тактов, в соответствии с таким планом исполнения: Порядок в программе инструкция условного перехода следующая последовательная инструкция 1 следующая последовательная инструкция 2 ……. . следующая последовательная инструкцияn ……. . место передачи управления, если переход произошел } n слотов задержки перехода Эти инструкции всегда выполняются независимо от направления перехода. О последовательных инструкциях говорят, что они находятся в слотах задержки перехода. Эти инструкции исполняются независимо от того, происходит переход или нет. На практике, все машины, использующие задержанные переходы, имеют единственный слот задержки (все ISA RISC). Роль компилятора состоит в том, чтобы сделать последовательную инструкцию в слоте задержки осмысленной и полезной. #36 Lec # 1 Autumn 2006

Сокращение потерь из-за переходов: Задержанный переход При использовании этого метода, переход задерживается на n тактов, в соответствии с таким планом исполнения: Порядок в программе инструкция условного перехода следующая последовательная инструкция 1 следующая последовательная инструкция 2 ……. . следующая последовательная инструкцияn ……. . место передачи управления, если переход произошел } n слотов задержки перехода Эти инструкции всегда выполняются независимо от направления перехода. О последовательных инструкциях говорят, что они находятся в слотах задержки перехода. Эти инструкции исполняются независимо от того, происходит переход или нет. На практике, все машины, использующие задержанные переходы, имеют единственный слот задержки (все ISA RISC). Роль компилятора состоит в том, чтобы сделать последовательную инструкцию в слоте задержки осмысленной и полезной. #36 Lec # 1 Autumn 2006

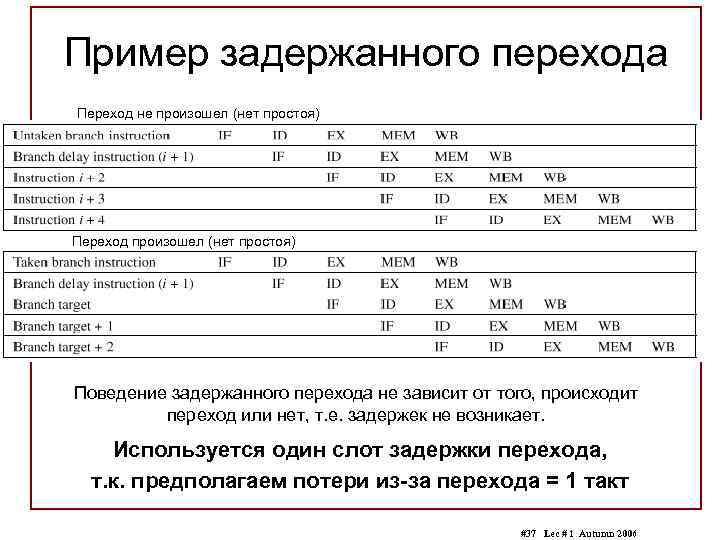

Пример задержанного перехода Переход не произошел (нет простоя) Переход произошел (нет простоя) Поведение задержанного перехода не зависит от того, происходит переход или нет, т. е. задержек не возникает. Используется один слот задержки перехода, т. к. предполагаем потери из-за перехода = 1 такт #37 Lec # 1 Autumn 2006

Пример задержанного перехода Переход не произошел (нет простоя) Переход произошел (нет простоя) Поведение задержанного перехода не зависит от того, происходит переход или нет, т. е. задержек не возникает. Используется один слот задержки перехода, т. к. предполагаем потери из-за перехода = 1 такт #37 Lec # 1 Autumn 2006

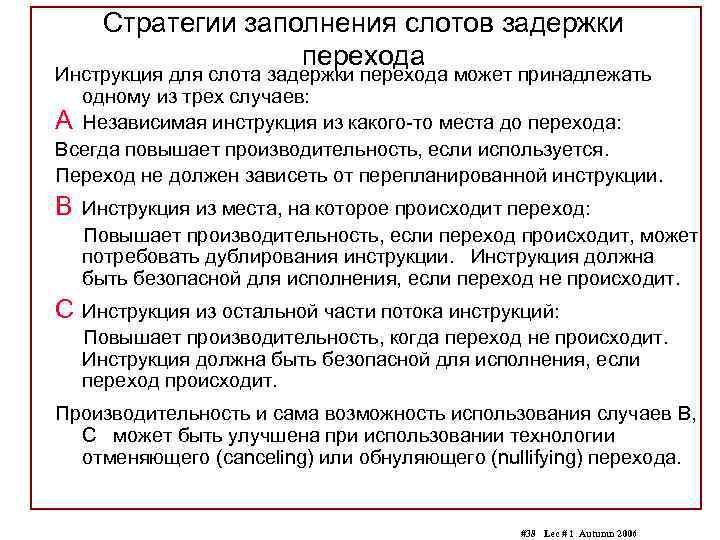

Стратегии заполнения слотов задержки перехода Инструкция для слота задержки перехода может принадлежать одному из трех случаев: A Независимая инструкция из какого-то места до перехода: Всегда повышает производительность, если используется. Переход не должен зависеть от перепланированной инструкции. B Инструкция из места, на которое происходит переход: Повышает производительность, если переход происходит, может потребовать дублирования инструкции. Инструкция должна быть безопасной для исполнения, если переход не происходит. C Инструкция из остальной части потока инструкций: Повышает производительность, когда переход не происходит. Инструкция должна быть безопасной для исполнения, если переход происходит. Производительность и сама возможность использования случаев B, C может быть улучшена при использовании технологии отменяющего (canceling) или обнуляющего (nullifying) перехода. #38 Lec # 1 Autumn 2006

Стратегии заполнения слотов задержки перехода Инструкция для слота задержки перехода может принадлежать одному из трех случаев: A Независимая инструкция из какого-то места до перехода: Всегда повышает производительность, если используется. Переход не должен зависеть от перепланированной инструкции. B Инструкция из места, на которое происходит переход: Повышает производительность, если переход происходит, может потребовать дублирования инструкции. Инструкция должна быть безопасной для исполнения, если переход не происходит. C Инструкция из остальной части потока инструкций: Повышает производительность, когда переход не происходит. Инструкция должна быть безопасной для исполнения, если переход происходит. Производительность и сама возможность использования случаев B, C может быть улучшена при использовании технологии отменяющего (canceling) или обнуляющего (nullifying) перехода. #38 Lec # 1 Autumn 2006

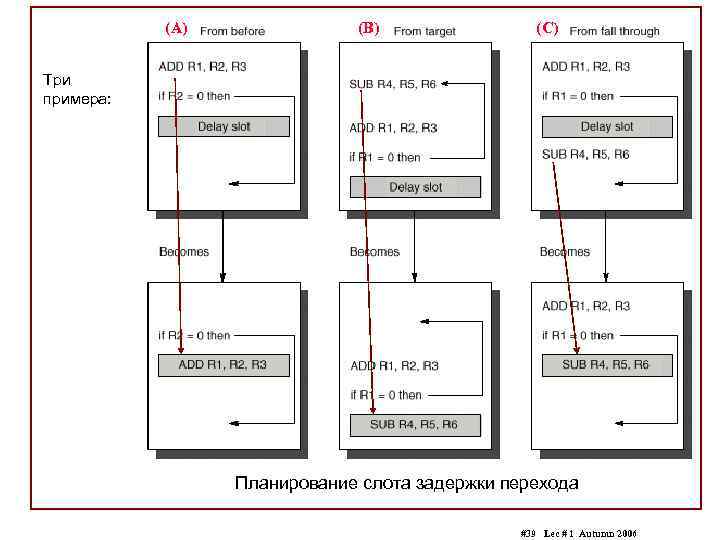

(A) (B) (C) Три примера: Планирование слота задержки перехода #39 Lec # 1 Autumn 2006

(A) (B) (C) Три примера: Планирование слота задержки перехода #39 Lec # 1 Autumn 2006

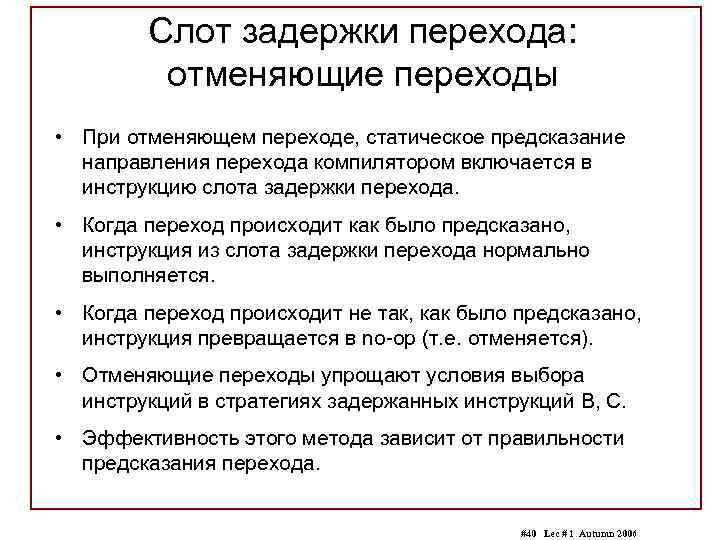

Слот задержки перехода: отменяющие переходы • При отменяющем переходе, статическое предсказание направления перехода компилятором включается в инструкцию слота задержки перехода. • Когда переход происходит как было предсказано, инструкция из слота задержки перехода нормально выполняется. • Когда переход происходит не так, как было предсказано, инструкция превращается в no-op (т. е. отменяется). • Отменяющие переходы упрощают условия выбора инструкций в стратегиях задержанных инструкций B, C. • Эффективность этого метода зависит от правильности предсказания перехода. #40 Lec # 1 Autumn 2006

Слот задержки перехода: отменяющие переходы • При отменяющем переходе, статическое предсказание направления перехода компилятором включается в инструкцию слота задержки перехода. • Когда переход происходит как было предсказано, инструкция из слота задержки перехода нормально выполняется. • Когда переход происходит не так, как было предсказано, инструкция превращается в no-op (т. е. отменяется). • Отменяющие переходы упрощают условия выбора инструкций в стратегиях задержанных инструкций B, C. • Эффективность этого метода зависит от правильности предсказания перехода. #40 Lec # 1 Autumn 2006

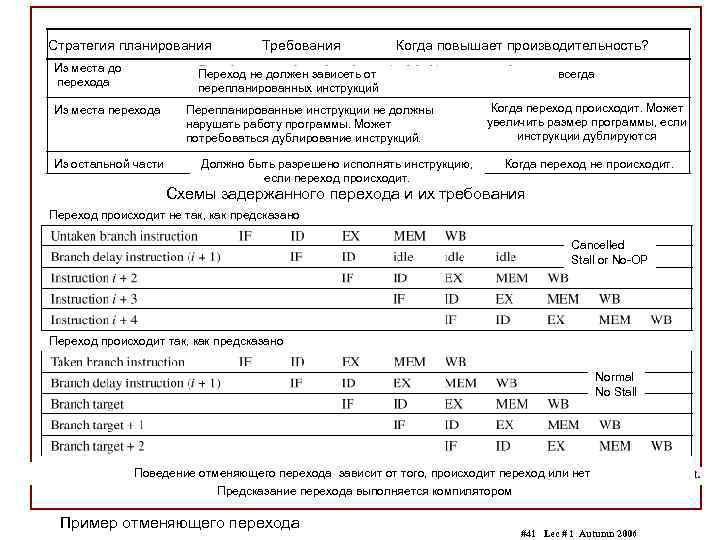

Стратегия планирования Из места до перехода Требования Когда повышает производительность? Переход не должен зависеть от перепланированных инструкций Из места перехода Из остальной части Перепланированные инструкции не должны нарушать работу программы. Может потребоваться дублирование инструкций. Должно быть разрешено исполнять инструкцию, если переход происходит. всегда Когда переход происходит. Может увеличить размер программы, если инструкции дублируются Когда переход не происходит. Схемы задержанного перехода и их требования Переход происходит не так, как предсказано Cancelled Stall or No-OP Переход происходит так, как предсказано Normal No Stall Поведение отменяющего перехода зависит от того, происходит переход или нет Предсказание перехода выполняется компилятором Пример отменяющего перехода #41 Lec # 1 Autumn 2006

Стратегия планирования Из места до перехода Требования Когда повышает производительность? Переход не должен зависеть от перепланированных инструкций Из места перехода Из остальной части Перепланированные инструкции не должны нарушать работу программы. Может потребоваться дублирование инструкций. Должно быть разрешено исполнять инструкцию, если переход происходит. всегда Когда переход происходит. Может увеличить размер программы, если инструкции дублируются Когда переход не происходит. Схемы задержанного перехода и их требования Переход происходит не так, как предсказано Cancelled Stall or No-OP Переход происходит так, как предсказано Normal No Stall Поведение отменяющего перехода зависит от того, происходит переход или нет Предсказание перехода выполняется компилятором Пример отменяющего перехода #41 Lec # 1 Autumn 2006

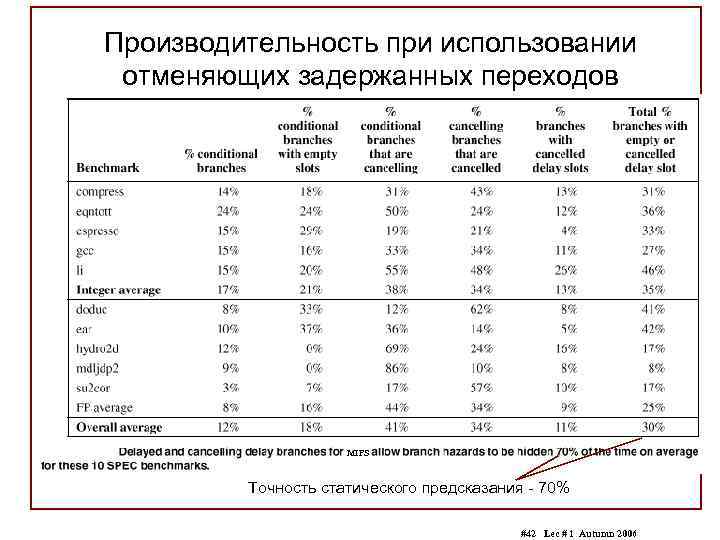

Производительность при использовании отменяющих задержанных переходов MIPS Точность статического предсказания - 70% #42 Lec # 1 Autumn 2006

Производительность при использовании отменяющих задержанных переходов MIPS Точность статического предсказания - 70% #42 Lec # 1 Autumn 2006

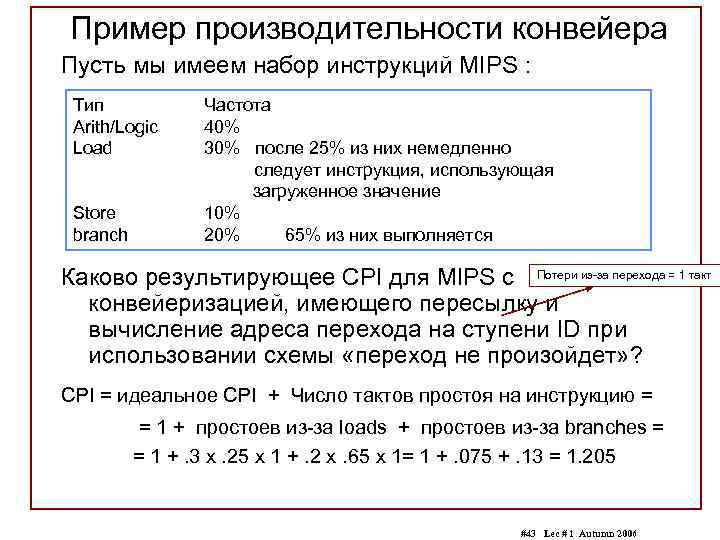

Пример производительности конвейера Пусть мы имеем набор инструкций MIPS : Тип Arith/Logic Load Store branch Частота 40% 30% после 25% из них немедленно следует инструкция, использующая загруженное значение 10% 20% 65% из них выполняется Каково результирующее CPI для MIPS с Потери из-за перехода = 1 такт конвейеризацией, имеющего пересылку и вычисление адреса перехода на ступени ID при использовании схемы «переход не произойдет» ? CPI = идеальное CPI + Число тактов простоя на инструкцию = = 1 + простоев из-за loads + простоев из-за branches = = 1 +. 3 x. 25 x 1 +. 2 x. 65 x 1= 1 +. 075 +. 13 = 1. 205 #43 Lec # 1 Autumn 2006

Пример производительности конвейера Пусть мы имеем набор инструкций MIPS : Тип Arith/Logic Load Store branch Частота 40% 30% после 25% из них немедленно следует инструкция, использующая загруженное значение 10% 20% 65% из них выполняется Каково результирующее CPI для MIPS с Потери из-за перехода = 1 такт конвейеризацией, имеющего пересылку и вычисление адреса перехода на ступени ID при использовании схемы «переход не произойдет» ? CPI = идеальное CPI + Число тактов простоя на инструкцию = = 1 + простоев из-за loads + простоев из-за branches = = 1 +. 3 x. 25 x 1 +. 2 x. 65 x 1= 1 +. 075 +. 13 = 1. 205 #43 Lec # 1 Autumn 2006

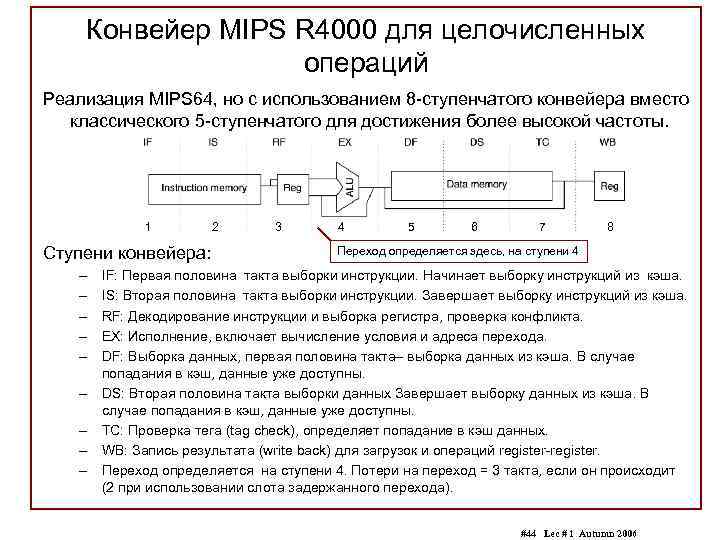

Конвейер MIPS R 4000 для целочисленных операций Реализация MIPS 64, но с использованием 8 -ступенчатого конвейера вместо классического 5 -ступенчатого для достижения более высокой частоты. 1 Ступени конвейера: – – – – – 2 3 4 5 6 7 8 Переход определяется здесь, на ступени 4 IF: Первая половина такта выборки инструкции. Начинает выборку инструкций из кэша. IS: Вторая половина такта выборки инструкции. Завершает выборку инструкций из кэша. RF: Декодирование инструкции и выборка регистра, проверка конфликта. EX: Исполнение, включает вычисление условия и адреса перехода. DF: Выборка данных, первая половина такта– выборка данных из кэша. В случае попадания в кэш, данные уже доступны. DS: Вторая половина такта выборки данных Завершает выборку данных из кэша. В случае попадания в кэш, данные уже доступны. TC: Проверка тега (tag check), определяет попадание в кэш данных. WB: Запись результата (write back) для загрузок и операций register-register. Переход определяется на ступени 4. Потери на переход = 3 такта, если он происходит (2 при использовании слота задержанного перехода). #44 Lec # 1 Autumn 2006

Конвейер MIPS R 4000 для целочисленных операций Реализация MIPS 64, но с использованием 8 -ступенчатого конвейера вместо классического 5 -ступенчатого для достижения более высокой частоты. 1 Ступени конвейера: – – – – – 2 3 4 5 6 7 8 Переход определяется здесь, на ступени 4 IF: Первая половина такта выборки инструкции. Начинает выборку инструкций из кэша. IS: Вторая половина такта выборки инструкции. Завершает выборку инструкций из кэша. RF: Декодирование инструкции и выборка регистра, проверка конфликта. EX: Исполнение, включает вычисление условия и адреса перехода. DF: Выборка данных, первая половина такта– выборка данных из кэша. В случае попадания в кэш, данные уже доступны. DS: Вторая половина такта выборки данных Завершает выборку данных из кэша. В случае попадания в кэш, данные уже доступны. TC: Проверка тега (tag check), определяет попадание в кэш данных. WB: Запись результата (write back) для загрузок и операций register-register. Переход определяется на ступени 4. Потери на переход = 3 такта, если он происходит (2 при использовании слота задержанного перехода). #44 Lec # 1 Autumn 2006

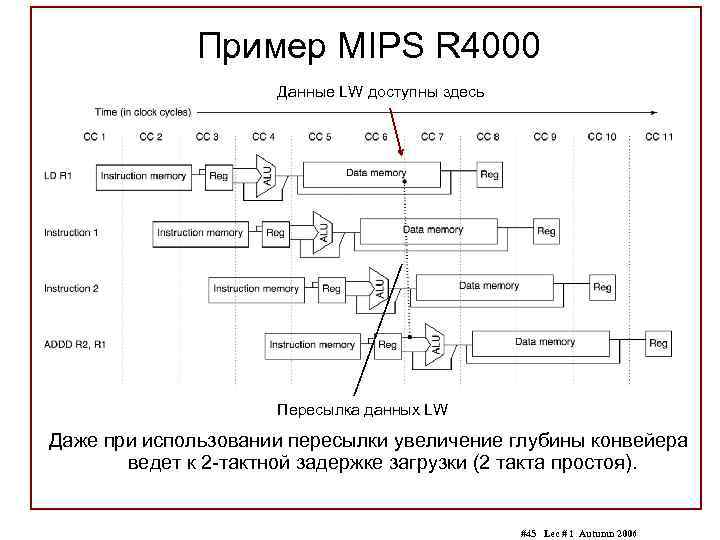

Пример MIPS R 4000 Данные LW доступны здесь Пересылка данных LW Даже при использовании пересылки увеличение глубины конвейера ведет к 2 -тактной задержке загрузки (2 такта простоя). #45 Lec # 1 Autumn 2006

Пример MIPS R 4000 Данные LW доступны здесь Пересылка данных LW Даже при использовании пересылки увеличение глубины конвейера ведет к 2 -тактной задержке загрузки (2 такта простоя). #45 Lec # 1 Autumn 2006

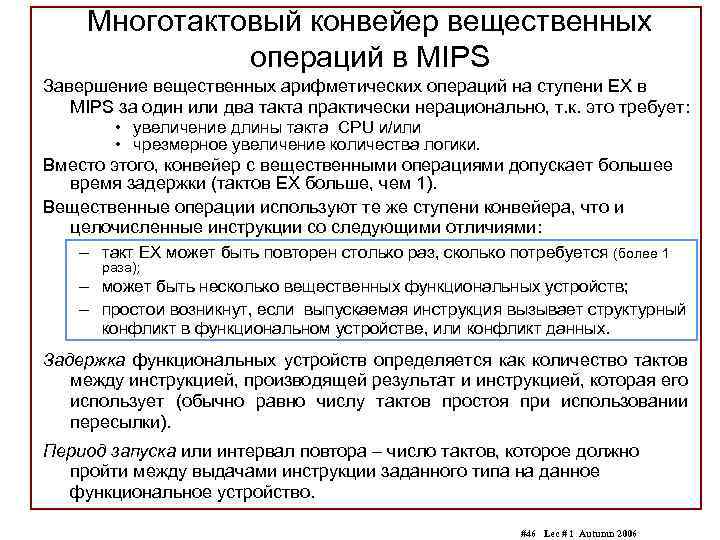

Многотактовый конвейер вещественных операций в MIPS Завершение вещественных арифметических операций на ступени EX в MIPS за один или два такта практически нерационально, т. к. это требует: • увеличение длины такта CPU и/или • чрезмерное увеличение количества логики. Вместо этого, конвейер с вещественными операциями допускает большее время задержки (тактов EX больше, чем 1). Вещественные операции используют те же ступени конвейера, что и целочисленные инструкции со следующими отличиями: – такт EX может быть повторен столько раз, сколько потребуется (более 1 раза); – может быть несколько вещественных функциональных устройств; – простои возникнут, если выпускаемая инструкция вызывает структурный конфликт в функциональном устройстве, или конфликт данных. Задержка функциональных устройств определяется как количество тактов между инструкцией, производящей результат и инструкцией, которая его использует (обычно равно числу тактов простоя при использовании пересылки). Период запуска или интервал повтора – число тактов, которое должно пройти между выдачами инструкции заданного типа на данное функциональное устройство. #46 Lec # 1 Autumn 2006

Многотактовый конвейер вещественных операций в MIPS Завершение вещественных арифметических операций на ступени EX в MIPS за один или два такта практически нерационально, т. к. это требует: • увеличение длины такта CPU и/или • чрезмерное увеличение количества логики. Вместо этого, конвейер с вещественными операциями допускает большее время задержки (тактов EX больше, чем 1). Вещественные операции используют те же ступени конвейера, что и целочисленные инструкции со следующими отличиями: – такт EX может быть повторен столько раз, сколько потребуется (более 1 раза); – может быть несколько вещественных функциональных устройств; – простои возникнут, если выпускаемая инструкция вызывает структурный конфликт в функциональном устройстве, или конфликт данных. Задержка функциональных устройств определяется как количество тактов между инструкцией, производящей результат и инструкцией, которая его использует (обычно равно числу тактов простоя при использовании пересылки). Период запуска или интервал повтора – число тактов, которое должно пройти между выдачами инструкции заданного типа на данное функциональное устройство. #46 Lec # 1 Autumn 2006

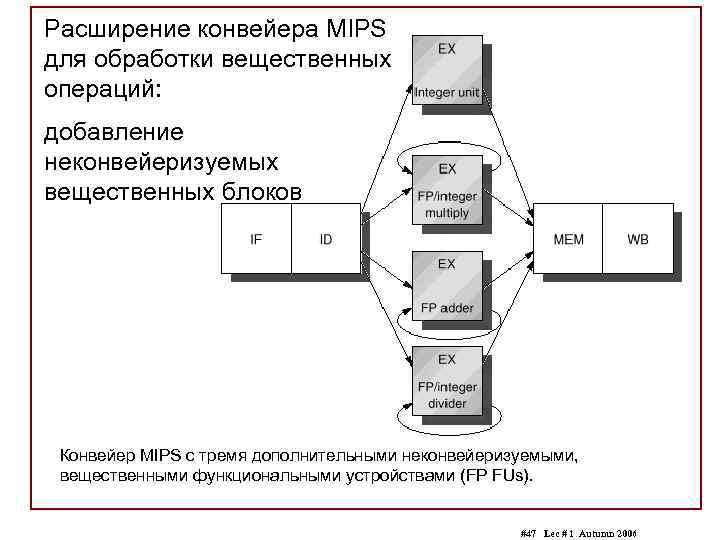

Расширение конвейера MIPS для обработки вещественных операций: добавление неконвейеризуемых вещественных блоков Конвейер MIPS с тремя дополнительными неконвейеризуемыми, вещественными функциональными устройствами (FP FUs). #47 Lec # 1 Autumn 2006

Расширение конвейера MIPS для обработки вещественных операций: добавление неконвейеризуемых вещественных блоков Конвейер MIPS с тремя дополнительными неконвейеризуемыми, вещественными функциональными устройствами (FP FUs). #47 Lec # 1 Autumn 2006

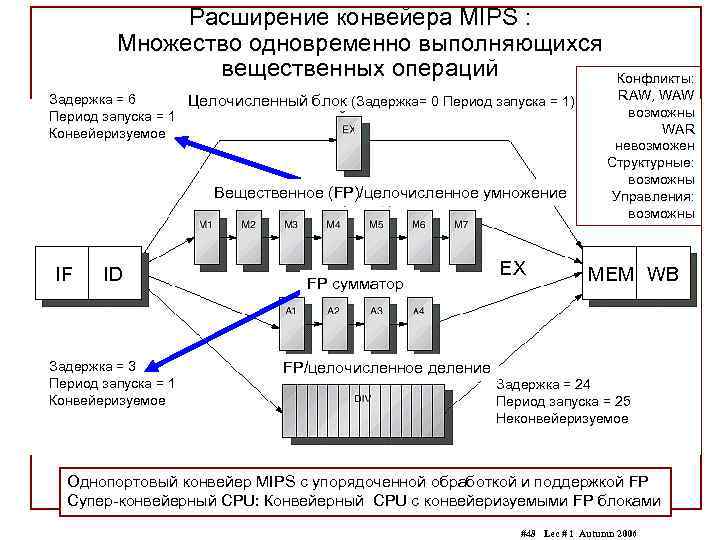

Расширение конвейера MIPS : Множество одновременно выполняющихся вещественных операций Задержка = 6 Целочисленный блок (Задержка= 0 Период запуска = 1) Период запуска = 1 Конвейеризуемое Вещественное (FP)/целочисленное умножение IF ID Задержка = 3 Период запуска = 1 Конвейеризуемое FP сумматор EX Конфликты: RAW, WAW возможны WAR невозможен Структурные: возможны Управления: возможны MEM WB FP/целочисленное деление Задержка = 24 Период запуска = 25 Неконвейеризуемое Однопортовый конвейер MIPS с упорядоченной обработкой и поддержкой FP Супер-конвейерный CPU: Конвейерный CPU с конвейеризуемыми FP блоками #48 Lec # 1 Autumn 2006

Расширение конвейера MIPS : Множество одновременно выполняющихся вещественных операций Задержка = 6 Целочисленный блок (Задержка= 0 Период запуска = 1) Период запуска = 1 Конвейеризуемое Вещественное (FP)/целочисленное умножение IF ID Задержка = 3 Период запуска = 1 Конвейеризуемое FP сумматор EX Конфликты: RAW, WAW возможны WAR невозможен Структурные: возможны Управления: возможны MEM WB FP/целочисленное деление Задержка = 24 Период запуска = 25 Неконвейеризуемое Однопортовый конвейер MIPS с упорядоченной обработкой и поддержкой FP Супер-конвейерный CPU: Конвейерный CPU с конвейеризуемыми FP блоками #48 Lec # 1 Autumn 2006

Задержки и периоды запуска для функциональных устройств (FUs) FU Задержка Период запуска Целочисленное ALU 0 1 Память данных 1 1 (загрузка целочисленных и FP значений) FP сложение 3 1 FP умножение 6 1 24 25 (и целочисленное умножение) FP деление (и целочисленное деление) #49 Lec # 1 Autumn 2006

Задержки и периоды запуска для функциональных устройств (FUs) FU Задержка Период запуска Целочисленное ALU 0 1 Память данных 1 1 (загрузка целочисленных и FP значений) FP сложение 3 1 FP умножение 6 1 24 25 (и целочисленное умножение) FP деление (и целочисленное деление) #49 Lec # 1 Autumn 2006

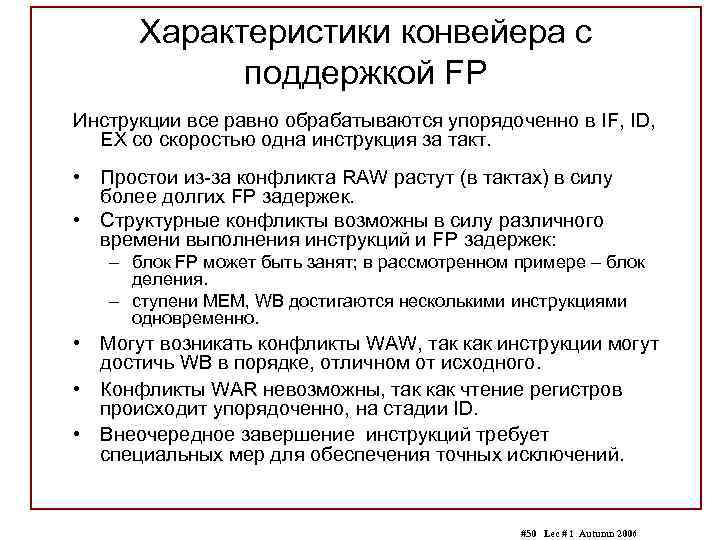

Характеристики конвейера с поддержкой FP Инструкции все равно обрабатываются упорядоченно в IF, ID, EX со скоростью одна инструкция за такт. • Простои из-за конфликта RAW растут (в тактах) в силу более долгих FP задержек. • Структурные конфликты возможны в силу различного времени выполнения инструкций и FP задержек: – блок FP может быть занят; в рассмотренном примере – блок деления. – ступени MEM, WB достигаются несколькими инструкциями одновременно. • Могут возникать конфликты WAW, так как инструкции могут достичь WB в порядке, отличном от исходного. • Конфликты WAR невозможны, так как чтение регистров происходит упорядоченно, на стадии ID. • Внеочередное завершение инструкций требует специальных мер для обеспечения точных исключений. #50 Lec # 1 Autumn 2006

Характеристики конвейера с поддержкой FP Инструкции все равно обрабатываются упорядоченно в IF, ID, EX со скоростью одна инструкция за такт. • Простои из-за конфликта RAW растут (в тактах) в силу более долгих FP задержек. • Структурные конфликты возможны в силу различного времени выполнения инструкций и FP задержек: – блок FP может быть занят; в рассмотренном примере – блок деления. – ступени MEM, WB достигаются несколькими инструкциями одновременно. • Могут возникать конфликты WAW, так как инструкции могут достичь WB в порядке, отличном от исходного. • Конфликты WAR невозможны, так как чтение регистров происходит упорядоченно, на стадии ID. • Внеочередное завершение инструкций требует специальных мер для обеспечения точных исключений. #50 Lec # 1 Autumn 2006

Пример работы FP конвейера CC 1 MUL. D ADD. D L. D S. D CC 2 CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 CC 9 CC 10 CC 11 IF ID M 1 M 2 M 3 M 4 M 5 M 6 M 7 MEM WB IF ID A 2 A 3 A 4 MEM IF A 1 ID EX MEM WB IF ID EX MEM Все инструкции выше считаются независимыми WB WB Пример показывает, что инструкции могут достигать ступени WB и внеочередно завершаться (т. е. в ином порядке, чем в программе). Поэтому конфликты Write-After-Write (WAW) могут возникать в этом конвейере. #51 Lec # 1 Autumn 2006

Пример работы FP конвейера CC 1 MUL. D ADD. D L. D S. D CC 2 CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 CC 9 CC 10 CC 11 IF ID M 1 M 2 M 3 M 4 M 5 M 6 M 7 MEM WB IF ID A 2 A 3 A 4 MEM IF A 1 ID EX MEM WB IF ID EX MEM Все инструкции выше считаются независимыми WB WB Пример показывает, что инструкции могут достигать ступени WB и внеочередно завершаться (т. е. в ином порядке, чем в программе). Поэтому конфликты Write-After-Write (WAW) могут возникать в этом конвейере. #51 Lec # 1 Autumn 2006

Пример простоев из-за конфликта RAW в коде с вещественными операциями (при использовании пересылки данных) CC 1 CC 2 IF L. D F 4, 0(R 2) ID EX MEM IF ID STALL M 1 M 2 IF STALL MUL. D F 0, F 4, F 6 ADD. D F 2, F 0, F 8 S. D F 2, 0(R 2) CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 M 3 M 4 CC 9 CC 10 CC 11 CC 12 CC 13 CC 14 CC 15 CC 16 CC 17 CC 18 WB M 5 M 6 M 7 MEM WB ID STALL STALL A 1 A 2 IF STALL STALL ID EX A 3 A 4 MEM WB STALL MEM WB Третий простой - из-за 6 тактов простоя равны задержке функционального блока FP сложения структурного конфликта на ступени MEM #52 Lec # 1 Autumn 2006

Пример простоев из-за конфликта RAW в коде с вещественными операциями (при использовании пересылки данных) CC 1 CC 2 IF L. D F 4, 0(R 2) ID EX MEM IF ID STALL M 1 M 2 IF STALL MUL. D F 0, F 4, F 6 ADD. D F 2, F 0, F 8 S. D F 2, 0(R 2) CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 M 3 M 4 CC 9 CC 10 CC 11 CC 12 CC 13 CC 14 CC 15 CC 16 CC 17 CC 18 WB M 5 M 6 M 7 MEM WB ID STALL STALL A 1 A 2 IF STALL STALL ID EX A 3 A 4 MEM WB STALL MEM WB Третий простой - из-за 6 тактов простоя равны задержке функционального блока FP сложения структурного конфликта на ступени MEM #52 Lec # 1 Autumn 2006

Пример структурных конфликтов в коде с вещественными операциями CC 1 MULTD F 0, F 4, F 6 . . . (integer) ADDD F 2, F 4, F 6 . . . (integer) LD F 8, 0(R 2) CC 2 CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 CC 9 CC 10 CC 11 IF ID M 1 M 2 M 3 M 4 M 5 M 6 M 7 MEM WB IF ID EX MEM WB IF ID A 1 A 2 A 3 A 4 MEM WB IF ID EX MEM WB #53 Lec # 1 Autumn 2006

Пример структурных конфликтов в коде с вещественными операциями CC 1 MULTD F 0, F 4, F 6 . . . (integer) ADDD F 2, F 4, F 6 . . . (integer) LD F 8, 0(R 2) CC 2 CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 CC 9 CC 10 CC 11 IF ID M 1 M 2 M 3 M 4 M 5 M 6 M 7 MEM WB IF ID EX MEM WB IF ID A 1 A 2 A 3 A 4 MEM WB IF ID EX MEM WB #53 Lec # 1 Autumn 2006

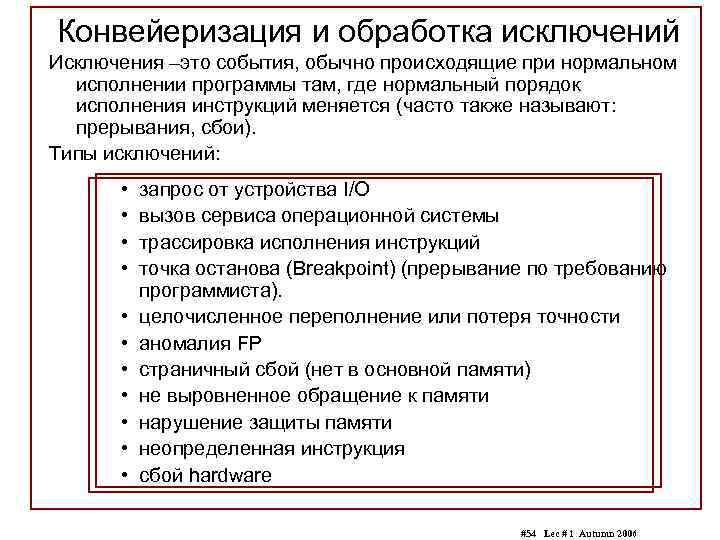

Конвейеризация и обработка исключений Исключения –это события, обычно происходящие при нормальном исполнении программы там, где нормальный порядок исполнения инструкций меняется (часто также называют: прерывания, сбои). Типы исключений: • • • запрос от устройства I/O вызов сервиса операционной системы трассировка исполнения инструкций точка останова (Breakpoint) (прерывание по требованию программиста). целочисленное переполнение или потеря точности аномалия FP страничный сбой (нет в основной памяти) не выровненное обращение к памяти нарушение защиты памяти неопределенная инструкция сбой hardware #54 Lec # 1 Autumn 2006

Конвейеризация и обработка исключений Исключения –это события, обычно происходящие при нормальном исполнении программы там, где нормальный порядок исполнения инструкций меняется (часто также называют: прерывания, сбои). Типы исключений: • • • запрос от устройства I/O вызов сервиса операционной системы трассировка исполнения инструкций точка останова (Breakpoint) (прерывание по требованию программиста). целочисленное переполнение или потеря точности аномалия FP страничный сбой (нет в основной памяти) не выровненное обращение к памяти нарушение защиты памяти неопределенная инструкция сбой hardware #54 Lec # 1 Autumn 2006

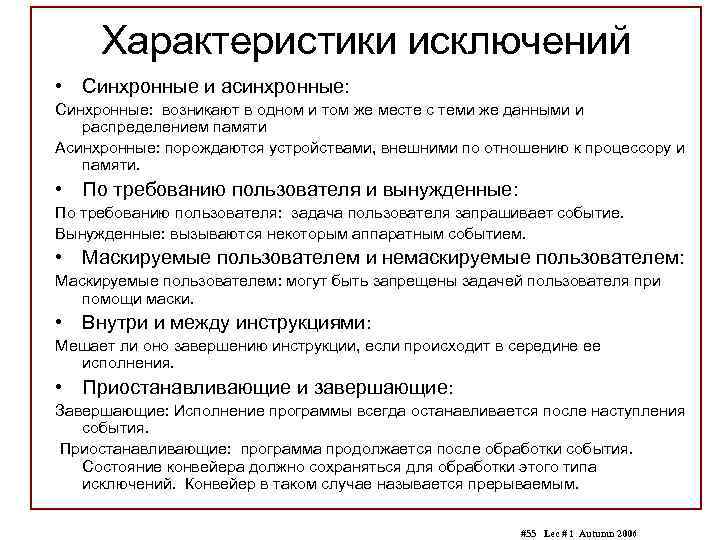

Характеристики исключений • Синхронные и асинхронные: Синхронные: возникают в одном и том же месте с теми же данными и распределением памяти Асинхронные: порождаются устройствами, внешними по отношению к процессору и памяти. • По требованию пользователя и вынужденные: По требованию пользователя: задача пользователя запрашивает событие. Вынужденные: вызываются некоторым аппаратным событием. • Маскируемые пользователем и немаскируемые пользователем: Маскируемые пользователем: могут быть запрещены задачей пользователя при помощи маски. • Внутри и между инструкциями: Мешает ли оно завершению инструкции, если происходит в середине ее исполнения. • Приостанавливающие и завершающие: Завершающие: Исполнение программы всегда останавливается после наступления события. Приостанавливающие: программа продолжается после обработки события. Состояние конвейера должно сохраняться для обработки этого типа исключений. Конвейер в таком случае называется прерываемым. #55 Lec # 1 Autumn 2006

Характеристики исключений • Синхронные и асинхронные: Синхронные: возникают в одном и том же месте с теми же данными и распределением памяти Асинхронные: порождаются устройствами, внешними по отношению к процессору и памяти. • По требованию пользователя и вынужденные: По требованию пользователя: задача пользователя запрашивает событие. Вынужденные: вызываются некоторым аппаратным событием. • Маскируемые пользователем и немаскируемые пользователем: Маскируемые пользователем: могут быть запрещены задачей пользователя при помощи маски. • Внутри и между инструкциями: Мешает ли оно завершению инструкции, если происходит в середине ее исполнения. • Приостанавливающие и завершающие: Завершающие: Исполнение программы всегда останавливается после наступления события. Приостанавливающие: программа продолжается после обработки события. Состояние конвейера должно сохраняться для обработки этого типа исключений. Конвейер в таком случае называется прерываемым. #55 Lec # 1 Autumn 2006

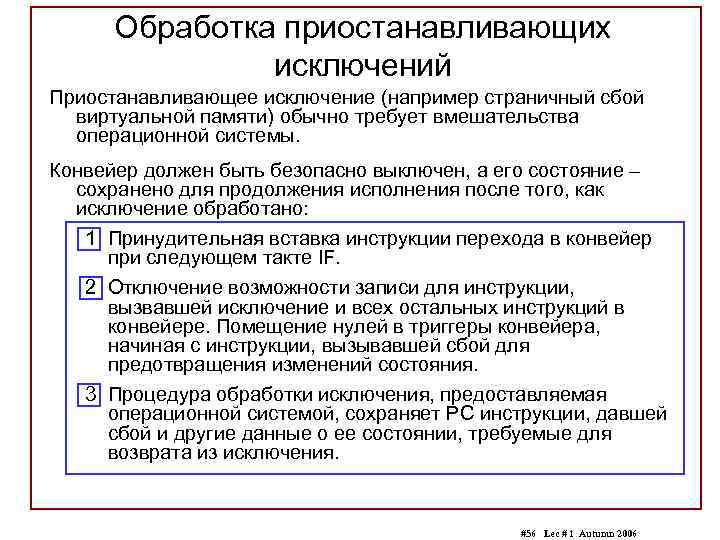

Обработка приостанавливающих исключений Приостанавливающее исключение (например страничный сбой виртуальной памяти) обычно требует вмешательства операционной системы. Конвейер должен быть безопасно выключен, а его состояние – сохранено для продолжения исполнения после того, как исключение обработано: 1 Принудительная вставка инструкции перехода в конвейер при следующем такте IF. 2 Отключение возможности записи для инструкции, вызвавшей исключение и всех остальных инструкций в конвейере. Помещение нулей в триггеры конвейера, начиная с инструкции, вызывавшей сбой для предотвращения изменений состояния. 3 Процедура обработки исключения, предоставляемая операционной системой, сохраняет PC инструкции, давшей сбой и другие данные о ее состоянии, требуемые для возврата из исключения. #56 Lec # 1 Autumn 2006

Обработка приостанавливающих исключений Приостанавливающее исключение (например страничный сбой виртуальной памяти) обычно требует вмешательства операционной системы. Конвейер должен быть безопасно выключен, а его состояние – сохранено для продолжения исполнения после того, как исключение обработано: 1 Принудительная вставка инструкции перехода в конвейер при следующем такте IF. 2 Отключение возможности записи для инструкции, вызвавшей исключение и всех остальных инструкций в конвейере. Помещение нулей в триггеры конвейера, начиная с инструкции, вызывавшей сбой для предотвращения изменений состояния. 3 Процедура обработки исключения, предоставляемая операционной системой, сохраняет PC инструкции, давшей сбой и другие данные о ее состоянии, требуемые для возврата из исключения. #56 Lec # 1 Autumn 2006

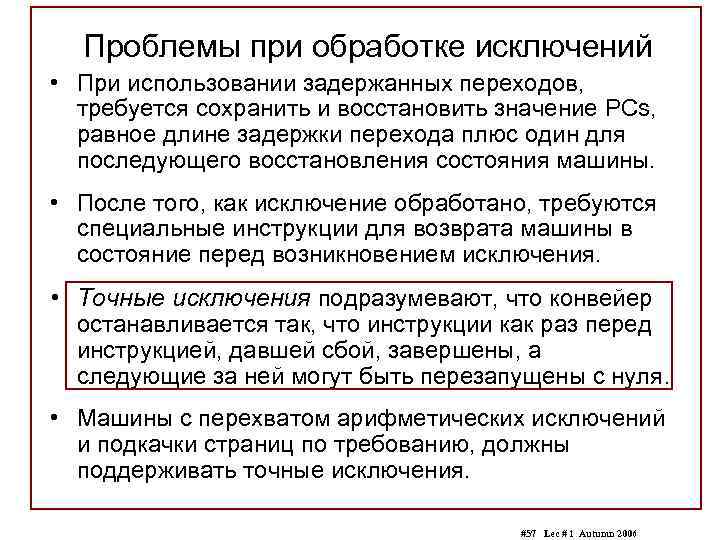

Проблемы при обработке исключений • При использовании задержанных переходов, требуется сохранить и восстановить значение PCs, равное длине задержки перехода плюс один для последующего восстановления состояния машины. • После того, как исключение обработано, требуются специальные инструкции для возврата машины в состояние перед возникновением исключения. • Точные исключения подразумевают, что конвейер останавливается так, что инструкции как раз перед инструкцией, давшей сбой, завершены, а следующие за ней могут быть перезапущены с нуля. • Машины с перехватом арифметических исключений и подкачки страниц по требованию, должны поддерживать точные исключения. #57 Lec # 1 Autumn 2006

Проблемы при обработке исключений • При использовании задержанных переходов, требуется сохранить и восстановить значение PCs, равное длине задержки перехода плюс один для последующего восстановления состояния машины. • После того, как исключение обработано, требуются специальные инструкции для возврата машины в состояние перед возникновением исключения. • Точные исключения подразумевают, что конвейер останавливается так, что инструкции как раз перед инструкцией, давшей сбой, завершены, а следующие за ней могут быть перезапущены с нуля. • Машины с перехватом арифметических исключений и подкачки страниц по требованию, должны поддерживать точные исключения. #57 Lec # 1 Autumn 2006

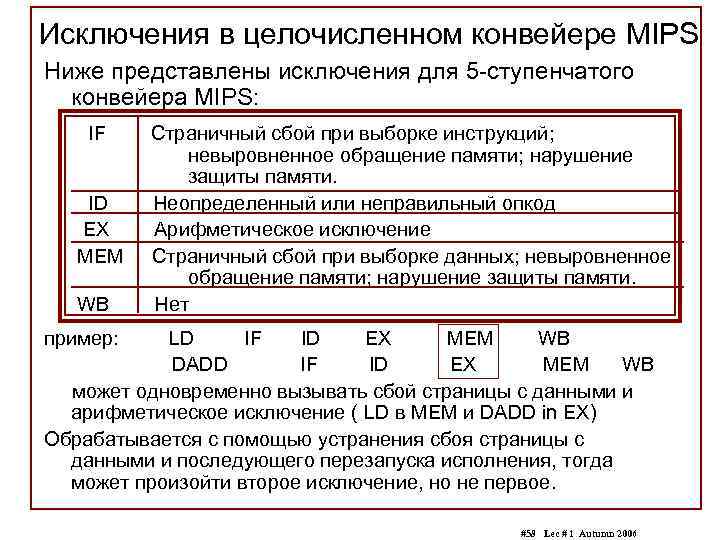

Исключения в целочисленном конвейере MIPS Ниже представлены исключения для 5 -ступенчатого конвейера MIPS: IF ID EX MEM WB Страничный сбой при выборке инструкций; невыровненное обращение памяти; нарушение защиты памяти. Неопределенный или неправильный опкод Арифметическое исключение Страничный сбой при выборке данных; невыровненное обращение памяти; нарушение защиты памяти. Нет пример: LD IF ID EX MEM WB DADD IF ID EX MEM WB может одновременно вызывать сбой страницы с данными и арифметическое исключение ( LD в MEM и DADD in EX) Обрабатывается с помощью устранения сбоя страницы с данными и последующего перезапуска исполнения, тогда может произойти второе исключение, но не первое. #58 Lec # 1 Autumn 2006

Исключения в целочисленном конвейере MIPS Ниже представлены исключения для 5 -ступенчатого конвейера MIPS: IF ID EX MEM WB Страничный сбой при выборке инструкций; невыровненное обращение памяти; нарушение защиты памяти. Неопределенный или неправильный опкод Арифметическое исключение Страничный сбой при выборке данных; невыровненное обращение памяти; нарушение защиты памяти. Нет пример: LD IF ID EX MEM WB DADD IF ID EX MEM WB может одновременно вызывать сбой страницы с данными и арифметическое исключение ( LD в MEM и DADD in EX) Обрабатывается с помощью устранения сбоя страницы с данными и последующего перезапуска исполнения, тогда может произойти второе исключение, но не первое. #58 Lec # 1 Autumn 2006

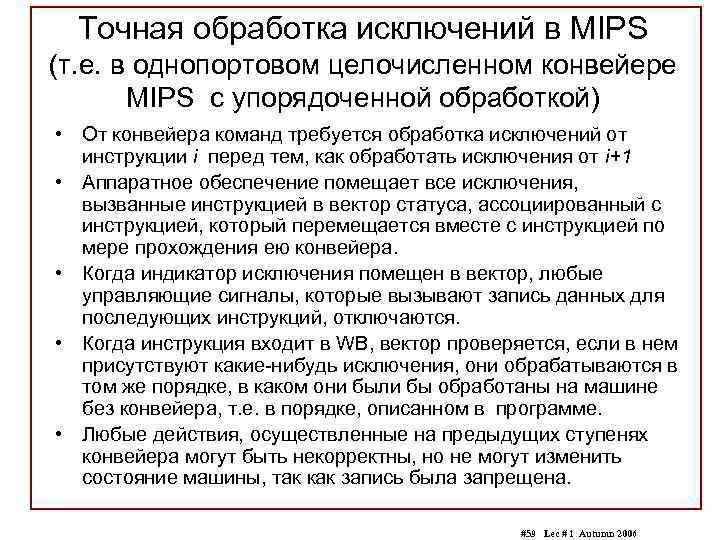

Точная обработка исключений в MIPS (т. е. в однопортовом целочисленном конвейере MIPS с упорядоченной обработкой) • От конвейера команд требуется обработка исключений от инструкции i перед тем, как обработать исключения от i+1 • Аппаратное обеспечение помещает все исключения, вызванные инструкцией в вектор статуса, ассоциированный с инструкцией, который перемещается вместе с инструкцией по мере прохождения ею конвейера. • Когда индикатор исключения помещен в вектор, любые управляющие сигналы, которые вызывают запись данных для последующих инструкций, отключаются. • Когда инструкция входит в WB, вектор проверяется, если в нем присутствуют какие-нибудь исключения, они обрабатываются в том же порядке, в каком они были бы обработаны на машине без конвейера, т. е. в порядке, описанном в программе. • Любые действия, осуществленные на предыдущих ступенях конвейера могут быть некорректны, но не могут изменить состояние машины, так как запись была запрещена. #59 Lec # 1 Autumn 2006

Точная обработка исключений в MIPS (т. е. в однопортовом целочисленном конвейере MIPS с упорядоченной обработкой) • От конвейера команд требуется обработка исключений от инструкции i перед тем, как обработать исключения от i+1 • Аппаратное обеспечение помещает все исключения, вызванные инструкцией в вектор статуса, ассоциированный с инструкцией, который перемещается вместе с инструкцией по мере прохождения ею конвейера. • Когда индикатор исключения помещен в вектор, любые управляющие сигналы, которые вызывают запись данных для последующих инструкций, отключаются. • Когда инструкция входит в WB, вектор проверяется, если в нем присутствуют какие-нибудь исключения, они обрабатываются в том же порядке, в каком они были бы обработаны на машине без конвейера, т. е. в порядке, описанном в программе. • Любые действия, осуществленные на предыдущих ступенях конвейера могут быть некорректны, но не могут изменить состояние машины, так как запись была запрещена. #59 Lec # 1 Autumn 2006

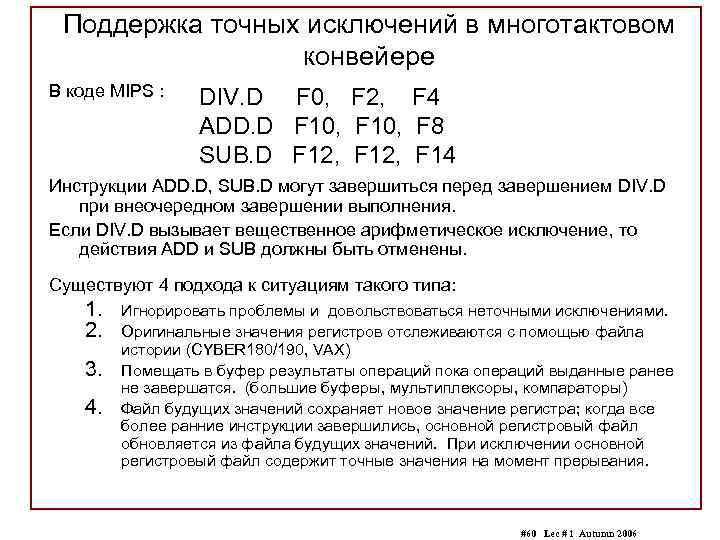

Поддержка точных исключений в многотактовом конвейере В коде MIPS : DIV. D F 0, F 2, F 4 ADD. D F 10, F 8 SUB. D F 12, F 14 Инструкции ADD. D, SUB. D могут завершиться перед завершением DIV. D при внеочередном завершении выполнения. Если DIV. D вызывает вещественное арифметическое исключение, то действия ADD и SUB должны быть отменены. Существуют 4 подхода к ситуациям такого типа: 1. 2. 3. 4. Игнорировать проблемы и довольствоваться неточными исключениями. Оригинальные значения регистров отслеживаются с помощью файла истории (CYBER 180/190, VAX) Помещать в буфер результаты операций пока операций выданные ранее не завершатся. (большие буферы, мультиплексоры, компараторы) Файл будущих значений сохраняет новое значение регистра; когда все более ранние инструкции завершились, основной регистровый файл обновляется из файла будущих значений. При исключении основной регистровый файл содержит точные значения на момент прерывания. #60 Lec # 1 Autumn 2006

Поддержка точных исключений в многотактовом конвейере В коде MIPS : DIV. D F 0, F 2, F 4 ADD. D F 10, F 8 SUB. D F 12, F 14 Инструкции ADD. D, SUB. D могут завершиться перед завершением DIV. D при внеочередном завершении выполнения. Если DIV. D вызывает вещественное арифметическое исключение, то действия ADD и SUB должны быть отменены. Существуют 4 подхода к ситуациям такого типа: 1. 2. 3. 4. Игнорировать проблемы и довольствоваться неточными исключениями. Оригинальные значения регистров отслеживаются с помощью файла истории (CYBER 180/190, VAX) Помещать в буфер результаты операций пока операций выданные ранее не завершатся. (большие буферы, мультиплексоры, компараторы) Файл будущих значений сохраняет новое значение регистра; когда все более ранние инструкции завершились, основной регистровый файл обновляется из файла будущих значений. При исключении основной регистровый файл содержит точные значения на момент прерывания. #60 Lec # 1 Autumn 2006