Организация кэш-памяти Рис. 7. 1. Однотранзисторный вариант элемента динамической памяти с хранением информации в виде заряда на емкости в цепи стока транзистора

Организация кэш-памяти Рис. 7. 1. Однотранзисторный вариант элемента динамической памяти с хранением информации в виде заряда на емкости в цепи стока транзистора

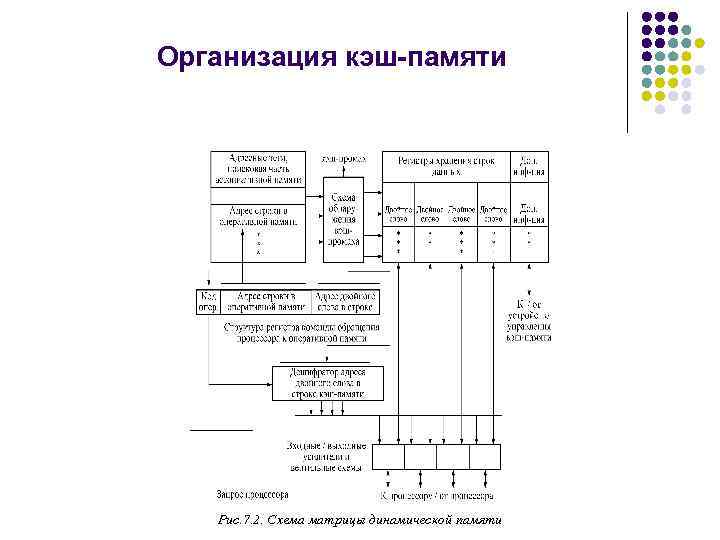

Организация кэш-памяти Рис. 7. 2. Схема матрицы динамической памяти

Организация кэш-памяти Рис. 7. 2. Схема матрицы динамической памяти

Организация кэш-памяти Рис. 7. 3. Оперативная память с расслоением адресов

Организация кэш-памяти Рис. 7. 3. Оперативная память с расслоением адресов

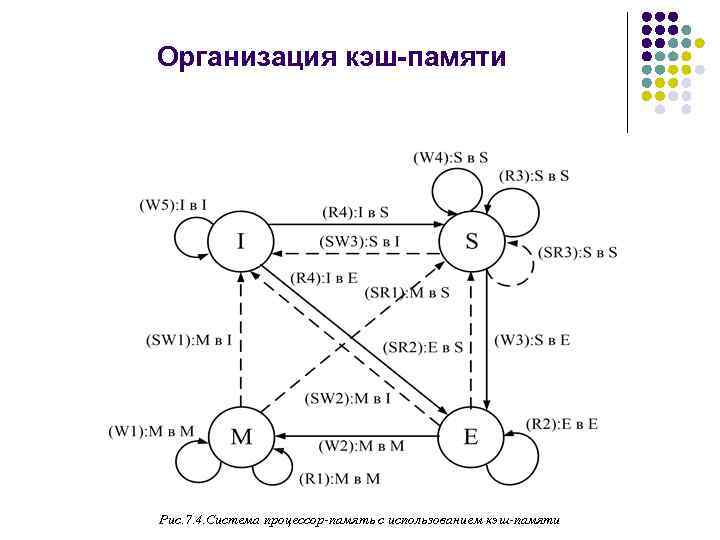

Организация кэш-памяти Рис. 7. 4. Система процессор-память с использованием кэш-памяти

Организация кэш-памяти Рис. 7. 4. Система процессор-память с использованием кэш-памяти

Организация кэш-памяти Рис. 7. 5. Схема матрицы однобитовой динамической памяти с внутренним регистром строки кэш-памяти на статических элементах памяти

Организация кэш-памяти Рис. 7. 5. Схема матрицы однобитовой динамической памяти с внутренним регистром строки кэш-памяти на статических элементах памяти

Организация кэш-памяти Рис. 7. 6. Упрощенная схема работы кэш-памяти на основе ассоциативной памяти

Организация кэш-памяти Рис. 7. 6. Упрощенная схема работы кэш-памяти на основе ассоциативной памяти

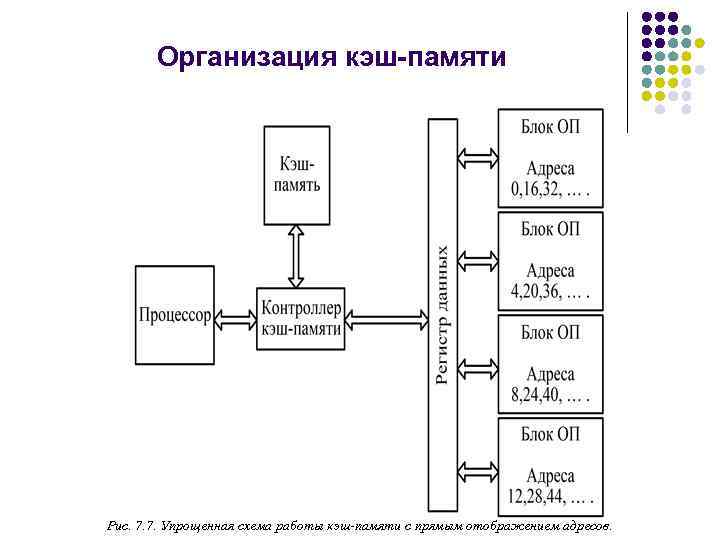

Организация кэш-памяти Рис. 7. 7. Упрощенная схема работы кэш-памяти с прямым отображением адресов.

Организация кэш-памяти Рис. 7. 7. Упрощенная схема работы кэш-памяти с прямым отображением адресов.

Организация кэш-памяти Рис. 7. 8. Упрощенная схема работы кэш-памяти на основе множественно ассоциативной памяти

Организация кэш-памяти Рис. 7. 8. Упрощенная схема работы кэш-памяти на основе множественно ассоциативной памяти

Организация кэш-памяти Обозначения: R№ – Изменение состояния строк при операциях чтения. W№ – Изменение состояния строк при операциях записи. SR№ – Изменение состояния строк кэшей других процессоров при чтении (Операции просмотров при чтении). SW№ – Изменение состояния строк кэшей других процессоров при записи (Операции просмотров при записи). Рис. 7. 9. Протокол MESI – диаграмма состояний.

Организация кэш-памяти Обозначения: R№ – Изменение состояния строк при операциях чтения. W№ – Изменение состояния строк при операциях записи. SR№ – Изменение состояния строк кэшей других процессоров при чтении (Операции просмотров при чтении). SW№ – Изменение состояния строк кэшей других процессоров при записи (Операции просмотров при записи). Рис. 7. 9. Протокол MESI – диаграмма состояний.