Org-EVM-1.ppt

- Количество слайдов: 11

Организация ЭВМ и систем Шишаев Максим Геннадьевич Тел. (81555) 79248 shishaev@iimm. kolasc. net. ru Фомин Дмитрий Евгеньевич

Организация ЭВМ и систем Шишаев Максим Геннадьевич Тел. (81555) 79248 shishaev@iimm. kolasc. net. ru Фомин Дмитрий Евгеньевич

Организация (архитектура) ЭВМ Объем курса – 32 час. лекций + 32 час. лабораторный практикум Отчетность - экзамен Допуск к экзамену – посещение занятий (лекций и практик) + выполнение лабораторных и самостоятельных заданий Литература: 1. Хамахер и др. Организация ЭВМ 2. Цилькер и др. Организация ЭВМ. Учебник 3. 4. 5. Гук. Архитектура IBM PC Ассемблер – любые книги Материалы Интернета

Организация (архитектура) ЭВМ Объем курса – 32 час. лекций + 32 час. лабораторный практикум Отчетность - экзамен Допуск к экзамену – посещение занятий (лекций и практик) + выполнение лабораторных и самостоятельных заданий Литература: 1. Хамахер и др. Организация ЭВМ 2. Цилькер и др. Организация ЭВМ. Учебник 3. 4. 5. Гук. Архитектура IBM PC Ассемблер – любые книги Материалы Интернета

Структура курса 1. Введение. Структура и основные принципы работы ЭВМ 2. Архитектура и принципы работы процессора 3. Организация системы ввода-вывода 4. Организация памяти 5. Архитектура высокопроизводительных вычислительных систем 6. Пример архитектуры процессора. Intel IA-32. 7. Внешние устройства.

Структура курса 1. Введение. Структура и основные принципы работы ЭВМ 2. Архитектура и принципы работы процессора 3. Организация системы ввода-вывода 4. Организация памяти 5. Архитектура высокопроизводительных вычислительных систем 6. Пример архитектуры процессора. Intel IA-32. 7. Внешние устройства.

Часть 1. Введение Структура и основные принципы работы ЭВМ

Часть 1. Введение Структура и основные принципы работы ЭВМ

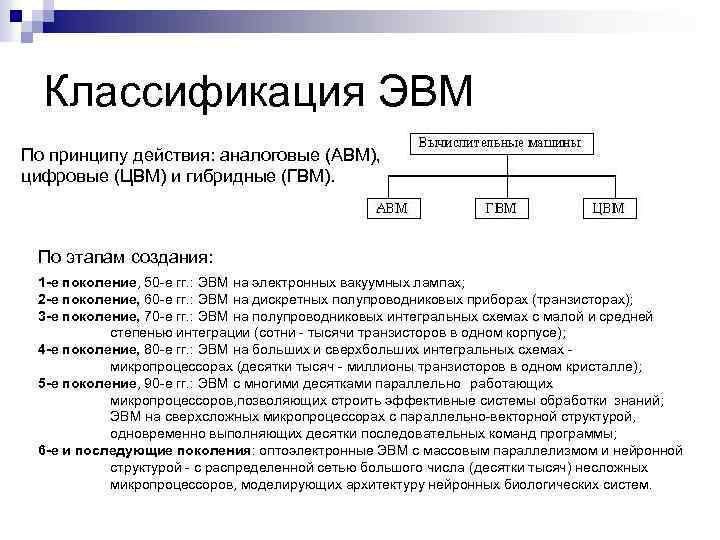

Классификация ЭВМ По принципу действия: аналоговые (АВМ), цифровые (ЦВМ) и гибридные (ГВМ). По этапам создания: 1 -е поколение, 50 -е гг. : ЭВМ на электронных вакуумных лампах; 2 -е поколение, 60 -е гг. : ЭВМ на дискретных полупроводниковых приборах (транзисторах); 3 -е поколение, 70 -е гг. : ЭВМ на полупроводниковых интегральных схемах с малой и средней степенью интеграции (сотни - тысячи транзисторов в одном корпусе); 4 -е поколение, 80 -е гг. : ЭВМ на больших и сверхбольших интегральных схемах микропроцессорах (десятки тысяч - миллионы транзисторов в одном кристалле); 5 -е поколение, 90 -е гг. : ЭВМ с многими десятками параллельно работающих микропроцессоров, позволяющих строить эффективные системы обработки знаний; ЭВМ на сверхсложных микропроцессорах с параллельно-векторной структурой, одновременно выполняющих десятки последовательных команд программы; 6 -е и последующие поколения: оптоэлектронные ЭВМ с массовым параллелизмом и нейронной структурой - с распределенной сетью большого числа (десятки тысяч) несложных микропроцессоров, моделирующих архитектуру нейронных биологических систем.

Классификация ЭВМ По принципу действия: аналоговые (АВМ), цифровые (ЦВМ) и гибридные (ГВМ). По этапам создания: 1 -е поколение, 50 -е гг. : ЭВМ на электронных вакуумных лампах; 2 -е поколение, 60 -е гг. : ЭВМ на дискретных полупроводниковых приборах (транзисторах); 3 -е поколение, 70 -е гг. : ЭВМ на полупроводниковых интегральных схемах с малой и средней степенью интеграции (сотни - тысячи транзисторов в одном корпусе); 4 -е поколение, 80 -е гг. : ЭВМ на больших и сверхбольших интегральных схемах микропроцессорах (десятки тысяч - миллионы транзисторов в одном кристалле); 5 -е поколение, 90 -е гг. : ЭВМ с многими десятками параллельно работающих микропроцессоров, позволяющих строить эффективные системы обработки знаний; ЭВМ на сверхсложных микропроцессорах с параллельно-векторной структурой, одновременно выполняющих десятки последовательных команд программы; 6 -е и последующие поколения: оптоэлектронные ЭВМ с массовым параллелизмом и нейронной структурой - с распределенной сетью большого числа (десятки тысяч) несложных микропроцессоров, моделирующих архитектуру нейронных биологических систем.

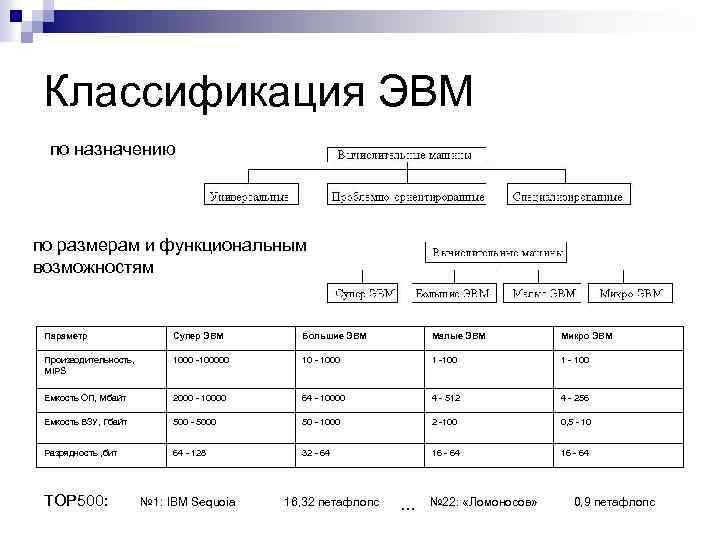

Классификация ЭВМ по назначению по размерам и функциональным возможностям Параметр Супер ЭВМ Большие ЭВМ Малые ЭВМ Микро ЭВМ Производительность, MIPS 1000 -100000 10 - 1000 1 -100 1 - 100 Емкость ОП, Мбайт 2000 - 10000 64 - 10000 4 - 512 4 - 256 Емкость ВЗУ, Гбайт 500 - 5000 50 - 1000 2 -100 0, 5 - 10 Разрядность , бит 64 - 128 32 - 64 16 - 64 TOP 500: № 1: IBM Sequoia 16, 32 петафлопс … № 22: «Ломоносов» 0, 9 петафлопс

Классификация ЭВМ по назначению по размерам и функциональным возможностям Параметр Супер ЭВМ Большие ЭВМ Малые ЭВМ Микро ЭВМ Производительность, MIPS 1000 -100000 10 - 1000 1 -100 1 - 100 Емкость ОП, Мбайт 2000 - 10000 64 - 10000 4 - 512 4 - 256 Емкость ВЗУ, Гбайт 500 - 5000 50 - 1000 2 -100 0, 5 - 10 Разрядность , бит 64 - 128 32 - 64 16 - 64 TOP 500: № 1: IBM Sequoia 16, 32 петафлопс … № 22: «Ломоносов» 0, 9 петафлопс

Функциональная структура ЭВМ АЛУ Устр. ввода Память Устр. вывода Устройство управления Процессор Кодированная информация (scan-коды нажатых клавиш и т. п. ) Выполняет арифметические и логические операции. 1. Берет из Памяти исх. данные 2. Кладет в регистры 3. Выполняет действие 4. (Отправляет результат в Память) Управляет «физикой» вычислений: выдает разл. cинхронизирующие сигналы для обмена данными с памятью, регистрами, и т. п.

Функциональная структура ЭВМ АЛУ Устр. ввода Память Устр. вывода Устройство управления Процессор Кодированная информация (scan-коды нажатых клавиш и т. п. ) Выполняет арифметические и логические операции. 1. Берет из Памяти исх. данные 2. Кладет в регистры 3. Выполняет действие 4. (Отправляет результат в Память) Управляет «физикой» вычислений: выдает разл. cинхронизирующие сигналы для обмена данными с памятью, регистрами, и т. п.

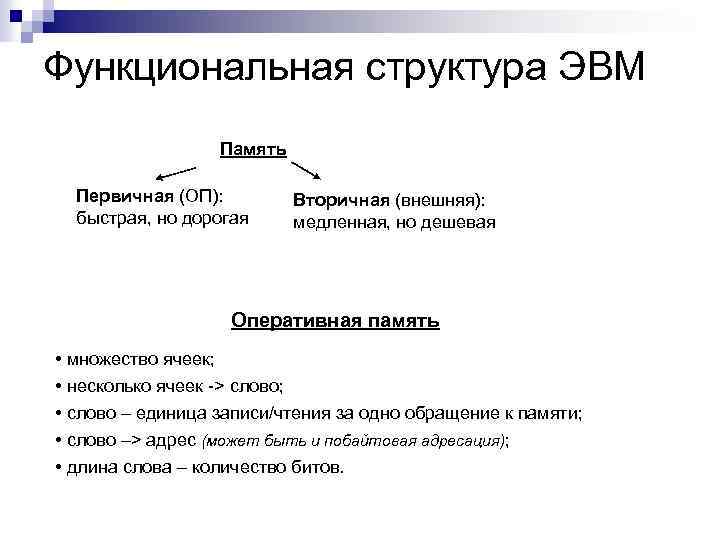

Функциональная структура ЭВМ Память Первичная (ОП): быстрая, но дорогая Вторичная (внешняя): медленная, но дешевая Оперативная память • множество ячеек; • несколько ячеек -> слово; • слово – единица записи/чтения за одно обращение к памяти; • слово –> адрес (может быть и побайтовая адресация); • длина слова – количество битов.

Функциональная структура ЭВМ Память Первичная (ОП): быстрая, но дорогая Вторичная (внешняя): медленная, но дешевая Оперативная память • множество ячеек; • несколько ячеек -> слово; • слово – единица записи/чтения за одно обращение к памяти; • слово –> адрес (может быть и побайтовая адресация); • длина слова – количество битов.

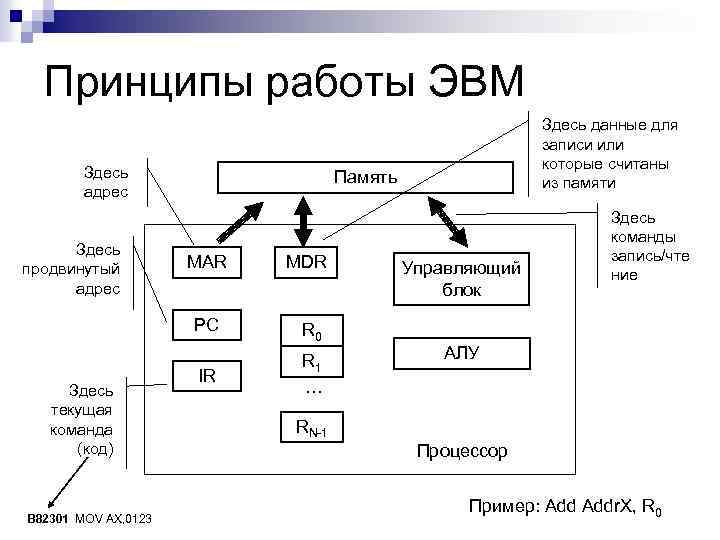

Принципы работы ЭВМ Здесь адрес Здесь продвинутый адрес Память MAR MDR PC Здесь текущая команда (код) B 82301 MOV AX, 0123 Здесь данные для записи или которые считаны из памяти R 0 IR R 1 … Управляющий блок Здесь команды запись/чте ние АЛУ RN-1 Процессор Пример: Addr. X, R 0

Принципы работы ЭВМ Здесь адрес Здесь продвинутый адрес Память MAR MDR PC Здесь текущая команда (код) B 82301 MOV AX, 0123 Здесь данные для записи или которые считаны из памяти R 0 IR R 1 … Управляющий блок Здесь команды запись/чте ние АЛУ RN-1 Процессор Пример: Addr. X, R 0

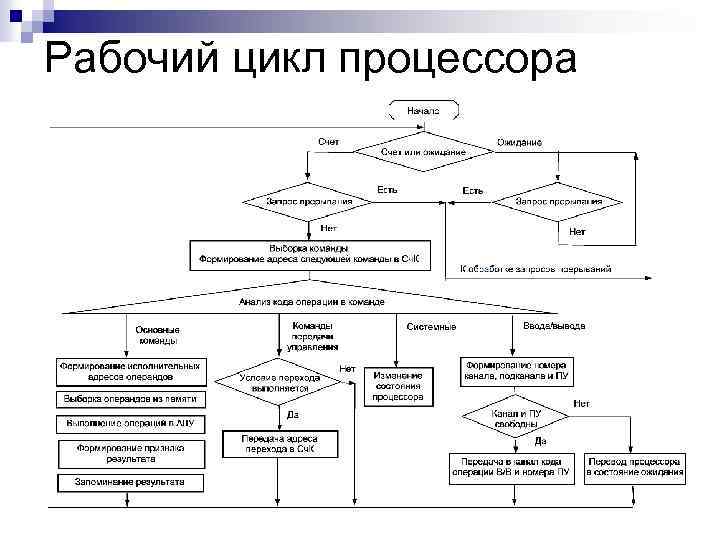

Рабочий цикл процессора

Рабочий цикл процессора

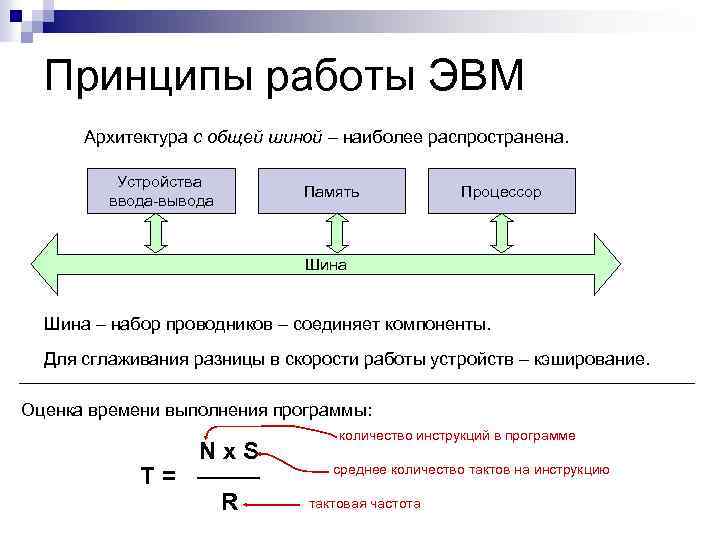

Принципы работы ЭВМ Архитектура с общей шиной – наиболее распространена. Устройства ввода-вывода Память Процессор Шина – набор проводников – соединяет компоненты. Для сглаживания разницы в скорости работы устройств – кэширование. Оценка времени выполнения программы: T= Nx. S R количество инструкций в программе среднее количество тактов на инструкцию тактовая частота

Принципы работы ЭВМ Архитектура с общей шиной – наиболее распространена. Устройства ввода-вывода Память Процессор Шина – набор проводников – соединяет компоненты. Для сглаживания разницы в скорости работы устройств – кэширование. Оценка времени выполнения программы: T= Nx. S R количество инструкций в программе среднее количество тактов на инструкцию тактовая частота