Организация ЭВМ и систем Лекция 2, 3 Архитектура и принцип работы процессора

Организация ЭВМ и систем Лекция 2, 3 Архитектура и принцип работы процессора

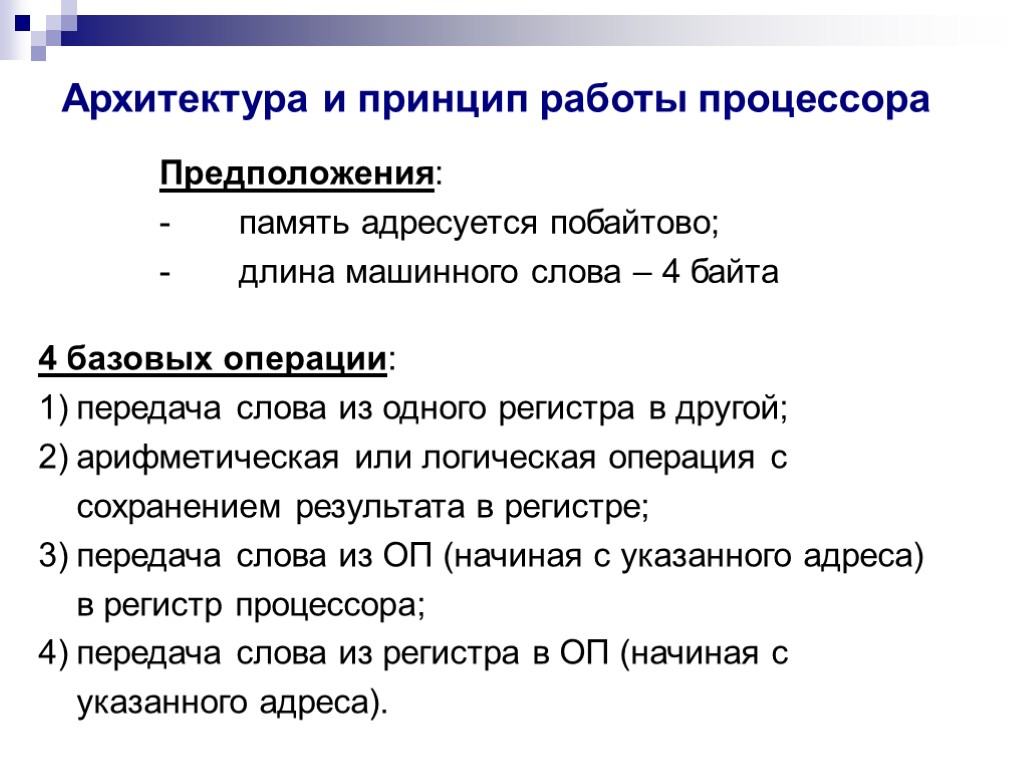

Архитектура и принцип работы процессора Предположения: память адресуется побайтово; длина машинного слова – 4 байта 4 базовых операции: передача слова из одного регистра в другой; арифметическая или логическая операция с сохранением результата в регистре; передача слова из ОП (начиная с указанного адреса) в регистр процессора; передача слова из регистра в ОП (начиная с указанного адреса).

Архитектура и принцип работы процессора Предположения: память адресуется побайтово; длина машинного слова – 4 байта 4 базовых операции: передача слова из одного регистра в другой; арифметическая или логическая операция с сохранением результата в регистре; передача слова из ОП (начиная с указанного адреса) в регистр процессора; передача слова из регистра в ОП (начиная с указанного адреса).

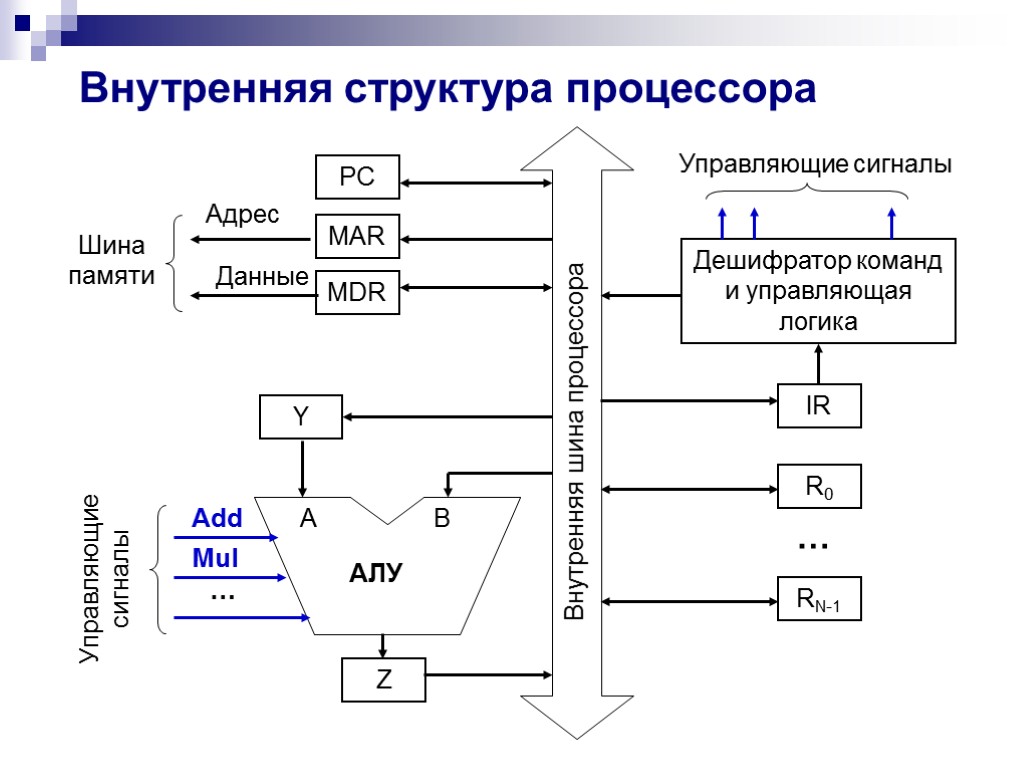

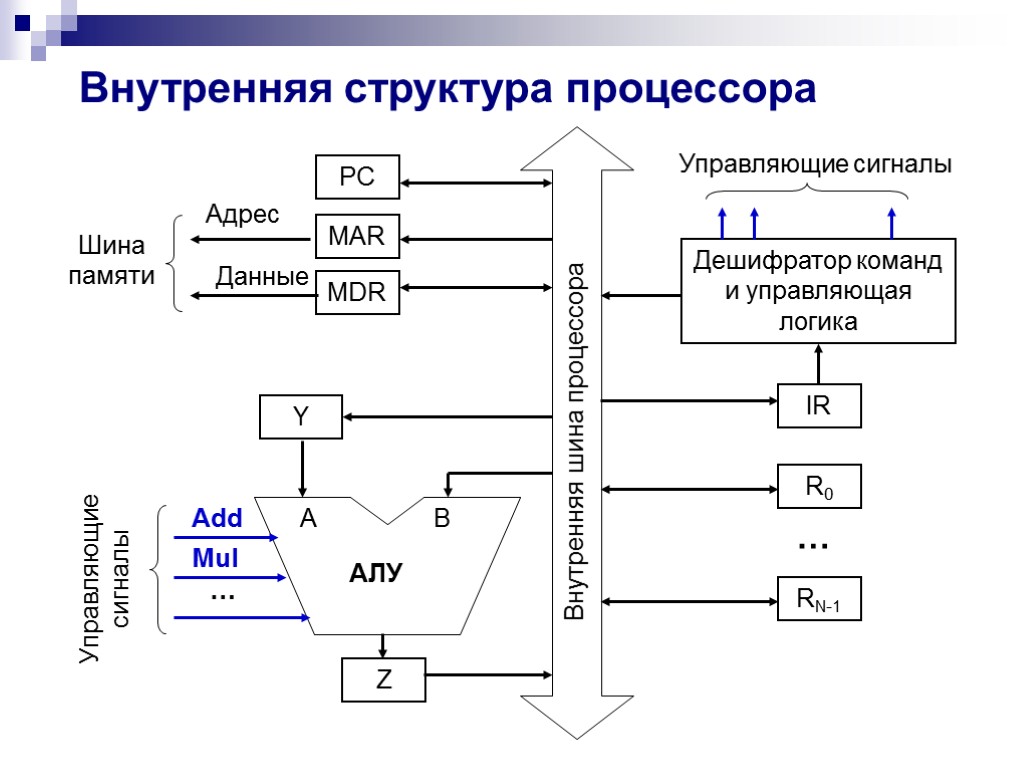

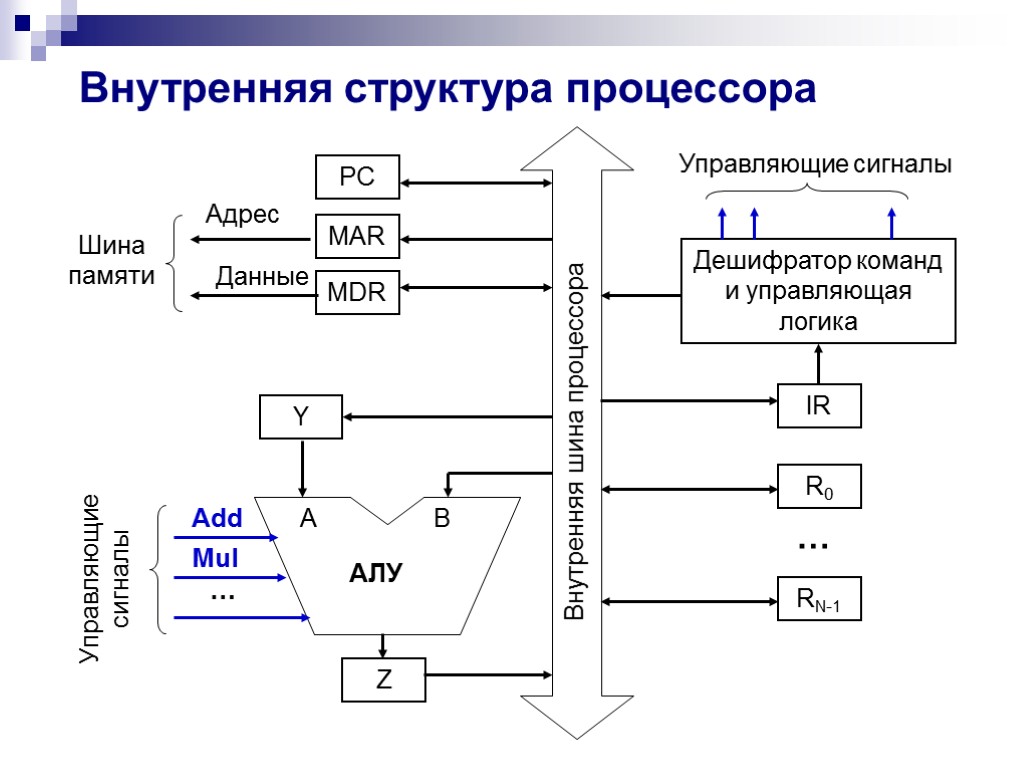

Внутренняя структура процессора PC MAR MDR Y Z Add Mul … Управляющие сигналы Адрес Данные Шина памяти Внутренняя шина процессора IR R0 Дешифратор команд и управляющая логика RN-1 … Управляющие сигналы

Внутренняя структура процессора PC MAR MDR Y Z Add Mul … Управляющие сигналы Адрес Данные Шина памяти Внутренняя шина процессора IR R0 Дешифратор команд и управляющая логика RN-1 … Управляющие сигналы

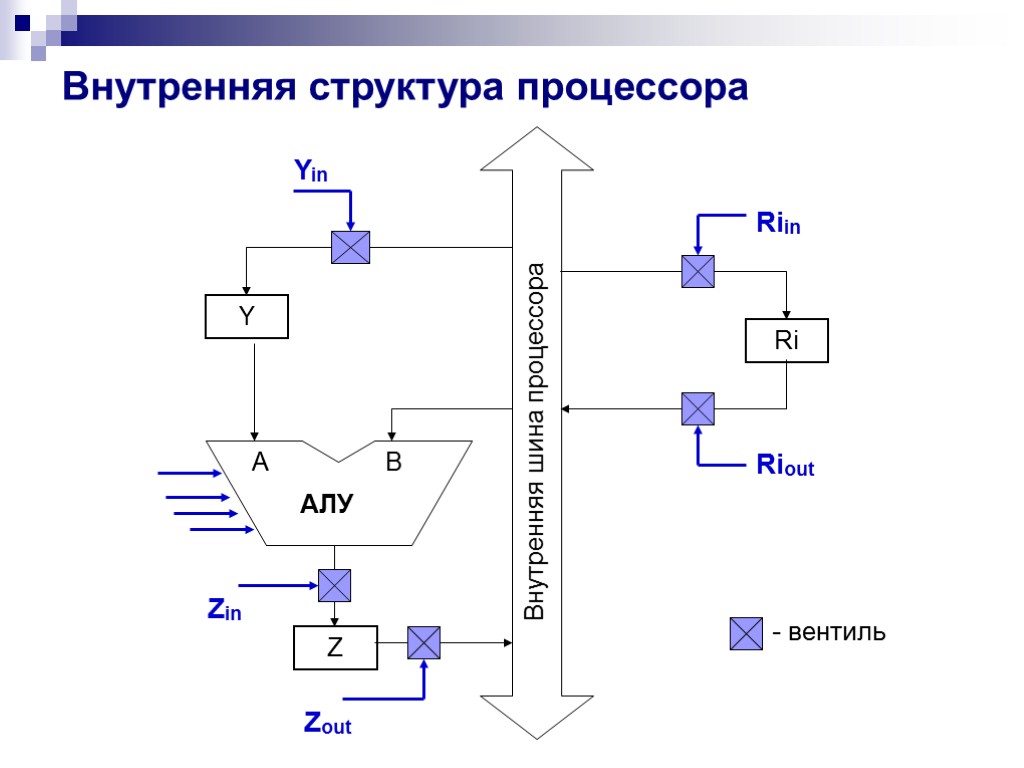

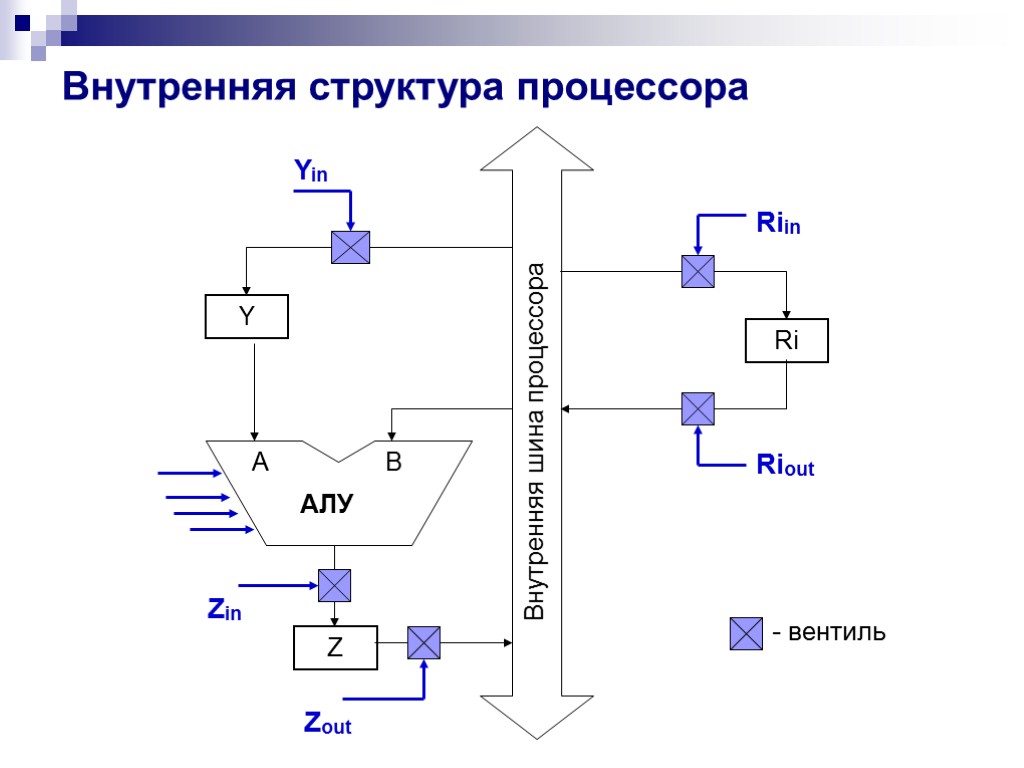

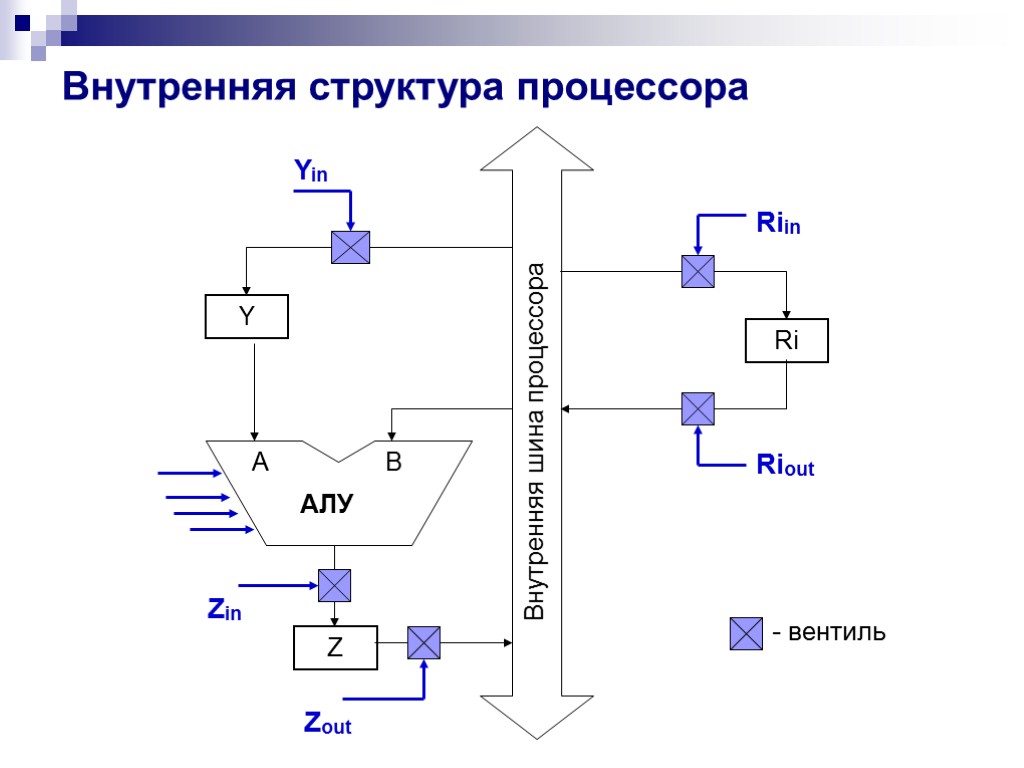

Y Z Zin Zout Ri Riin Riout - вентиль Внутренняя структура процессора

Y Z Zin Zout Ri Riin Riout - вентиль Внутренняя структура процессора

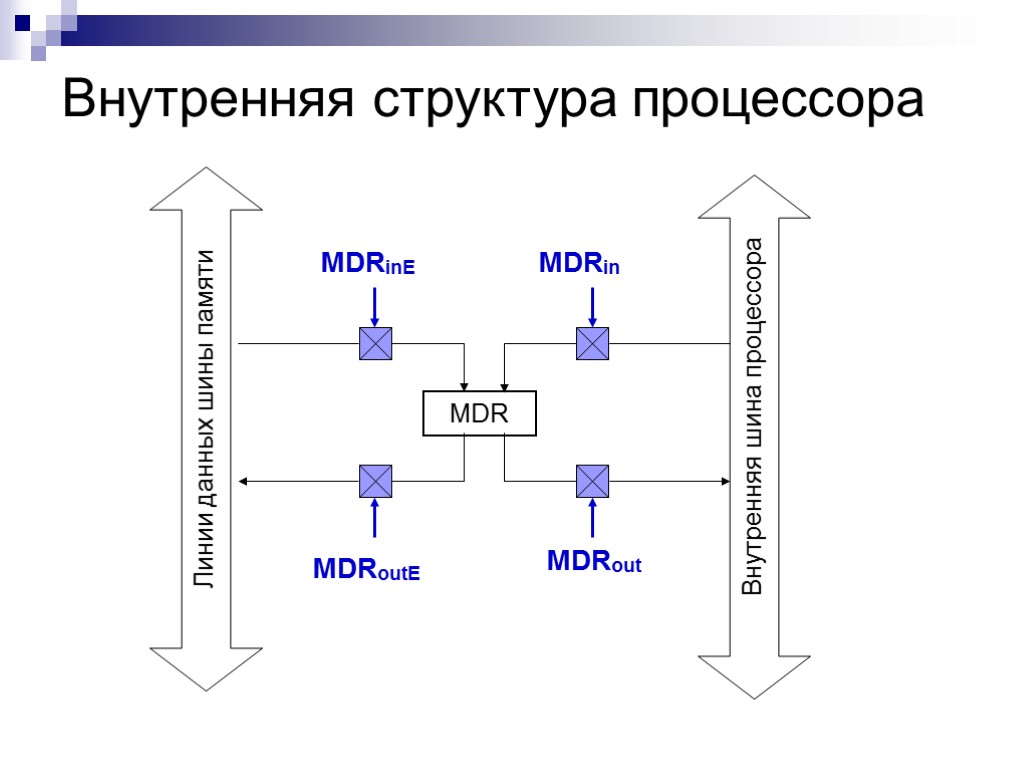

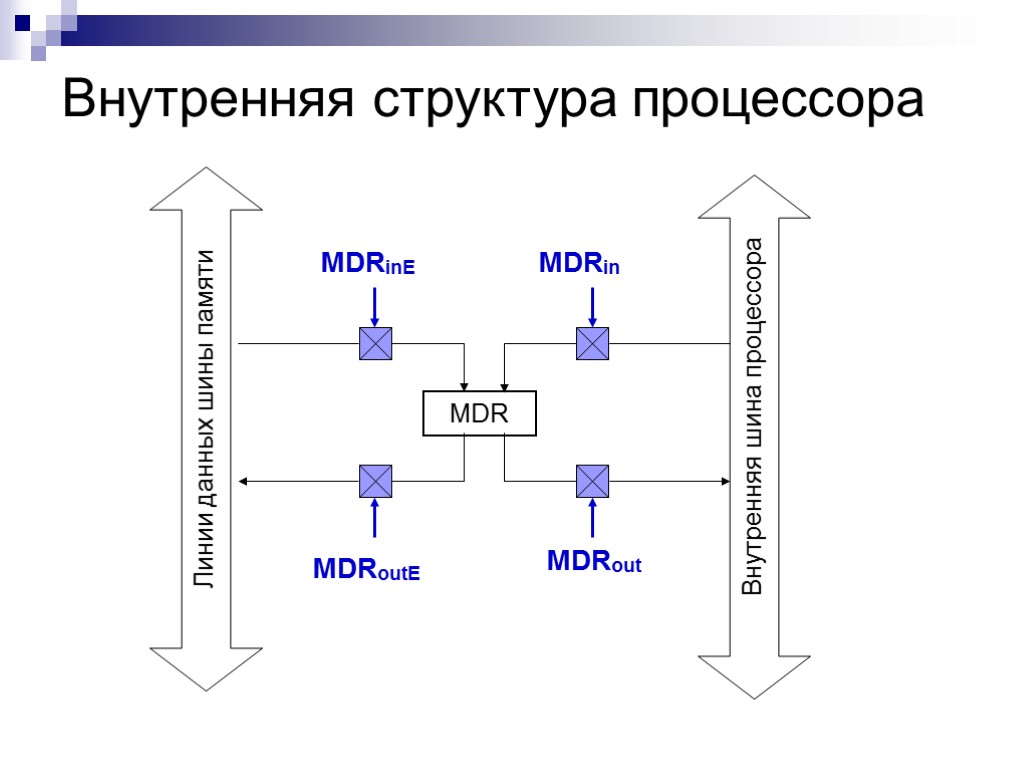

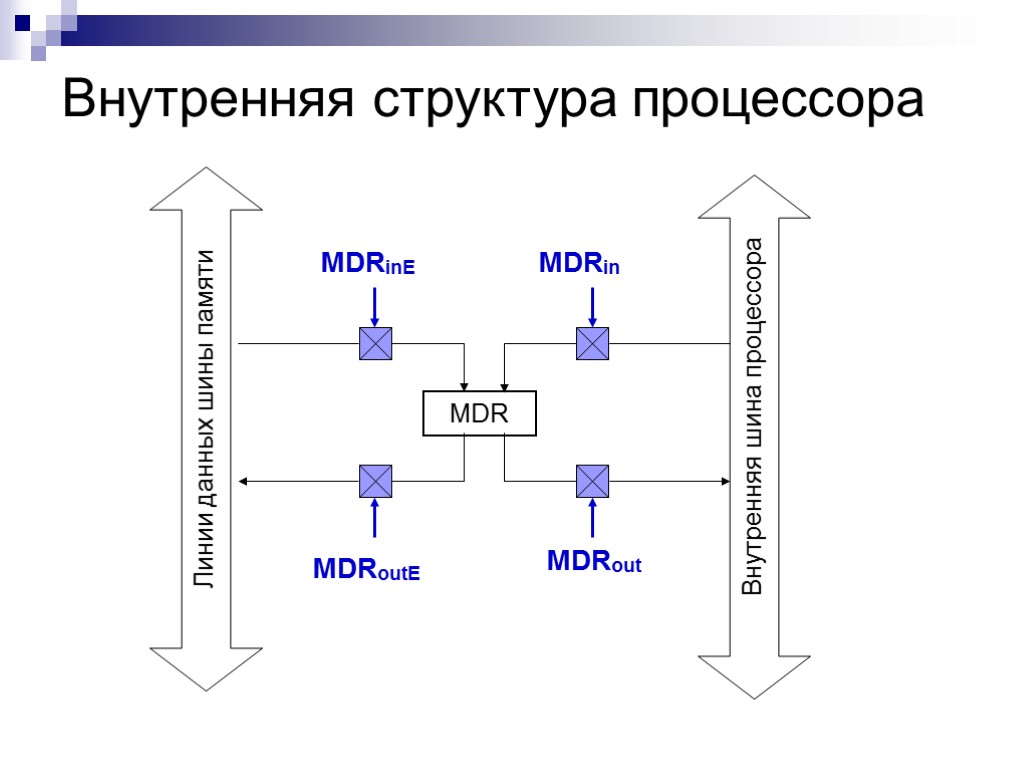

Внутренняя структура процессора MDR MDRinE MDRoutE MDRin MDRout

Внутренняя структура процессора MDR MDRinE MDRoutE MDRin MDRout

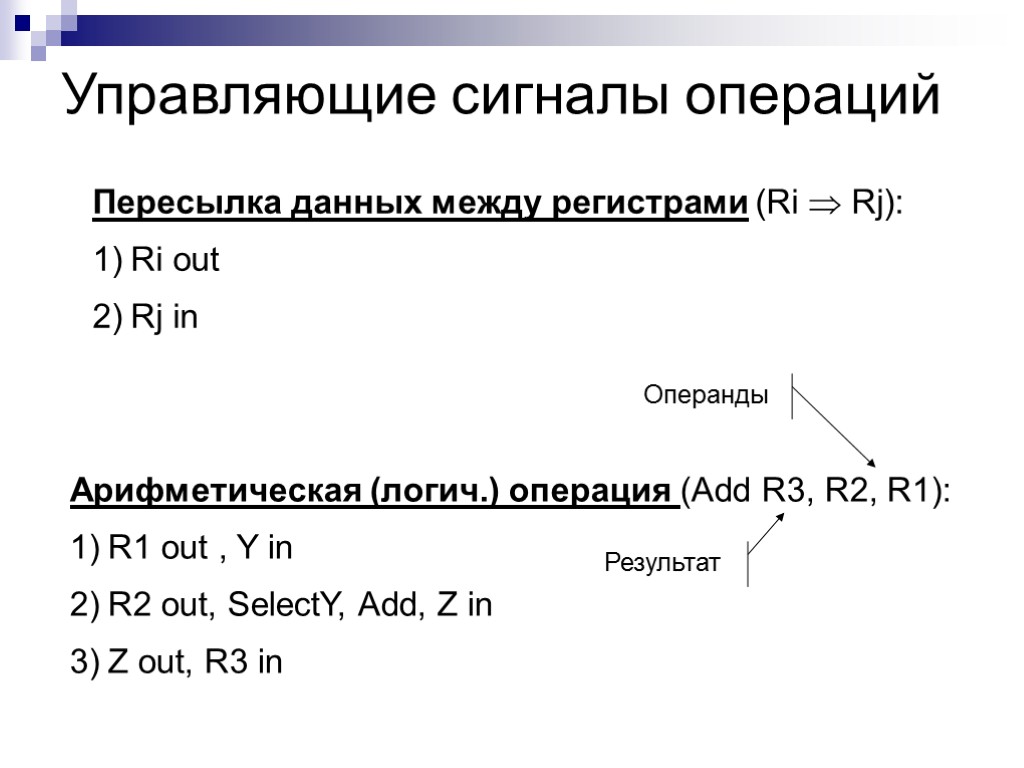

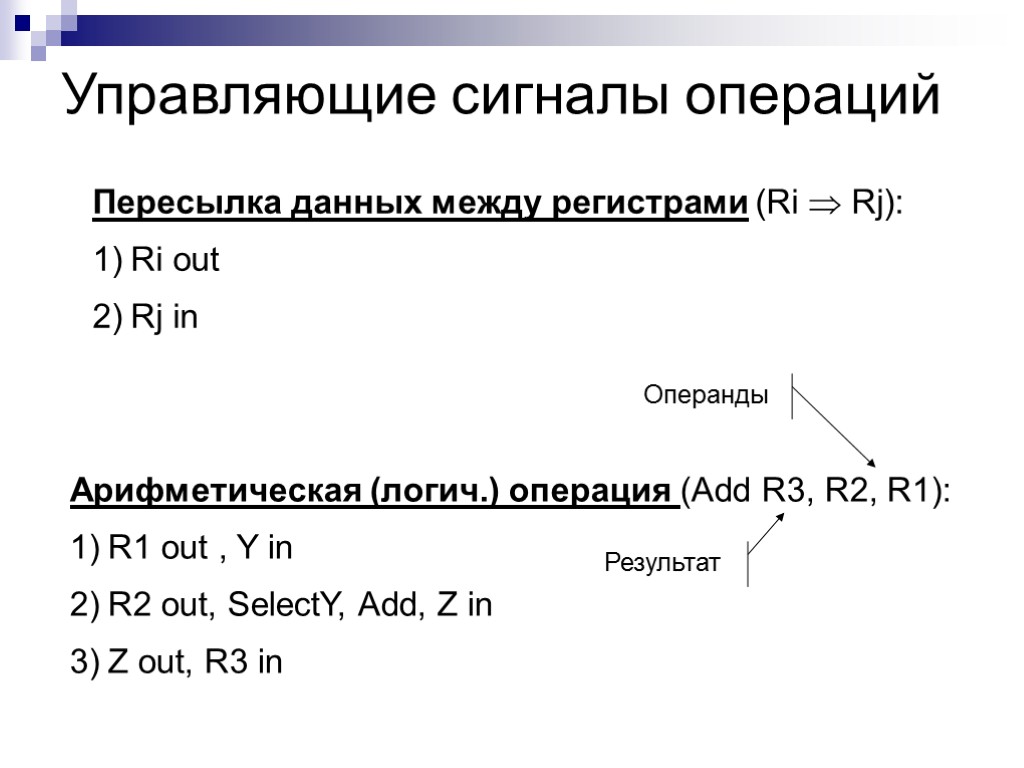

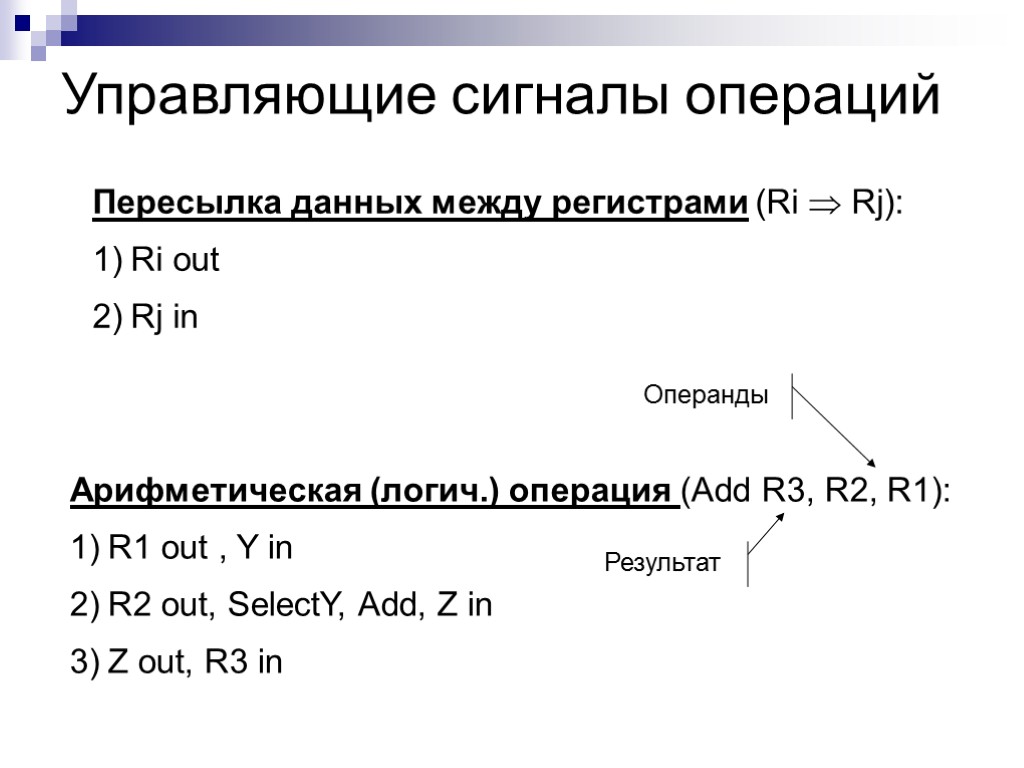

Управляющие сигналы операций Пересылка данных между регистрами (Ri Rj): Ri out Rj in Арифметическая (логич.) операция (Add R3, R2, R1): R1 out , Y in R2 out, SelectY, Add, Z in Z out, R3 in Результат Операнды

Управляющие сигналы операций Пересылка данных между регистрами (Ri Rj): Ri out Rj in Арифметическая (логич.) операция (Add R3, R2, R1): R1 out , Y in R2 out, SelectY, Add, Z in Z out, R3 in Результат Операнды

![>Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 >Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 ](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_7.jpg) Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 MAR Начало чтения Ожидание MFC * Считывание данных с шины памяти в MDR MDR MAR Сюда - результат Здесь адрес * - память – медленная, поэтому CPU не стоит во время чтения из памяти, а делает другую работу и возвращается к процедуре чтения по возникновению сигнала MFC (Memory Function Complete)

Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 MAR Начало чтения Ожидание MFC * Считывание данных с шины памяти в MDR MDR MAR Сюда - результат Здесь адрес * - память – медленная, поэтому CPU не стоит во время чтения из памяти, а делает другую работу и возвращается к процедуре чтения по возникновению сигнала MFC (Memory Function Complete)

![>Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 out, >Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 out,](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_8.jpg) Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 out, MAR in, Read MDR inE, WMFC MDR out, R2 in (предполагаем, что MAR inE активен всегда)

Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 out, MAR in, Read MDR inE, WMFC MDR out, R2 in (предполагаем, что MAR inE активен всегда)

![>Управляющие сигналы операций Сохранение слова в памяти ( Mov [R1], R2 ) R1 out, >Управляющие сигналы операций Сохранение слова в памяти ( Mov [R1], R2 ) R1 out,](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_9.jpg) Управляющие сигналы операций Сохранение слова в памяти ( Mov [R1], R2 ) R1 out, MAR in R2 out, MDR in, Write MDR outE, WMFC (предполагаем, что MAR inE активен всегда)

Управляющие сигналы операций Сохранение слова в памяти ( Mov [R1], R2 ) R1 out, MAR in R2 out, MDR in, Write MDR outE, WMFC (предполагаем, что MAR inE активен всегда)

![>Управляющие сигналы операций Вся команда ( Напр. Add R1, [R3] ): PC out, MAR >Управляющие сигналы операций Вся команда ( Напр. Add R1, [R3] ): PC out, MAR](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_10.jpg) Управляющие сигналы операций Вся команда ( Напр. Add R1, [R3] ): PC out, MAR in, Read, Select4, Add, Z in Z out, PC in, Y in, WMFC MDR out, IR in R3 out, MAR in, Read R1 out, Y in, WMFC MDR out, SelectY, Add, Z in Z out, R1 in, End Фаза выборки Фаза выполнения

Управляющие сигналы операций Вся команда ( Напр. Add R1, [R3] ): PC out, MAR in, Read, Select4, Add, Z in Z out, PC in, Y in, WMFC MDR out, IR in R3 out, MAR in, Read R1 out, Y in, WMFC MDR out, SelectY, Add, Z in Z out, R1 in, End Фаза выборки Фаза выполнения

![Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 ](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_7.jpg)

![Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 out, Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 out,](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_8.jpg)

![Управляющие сигналы операций Сохранение слова в памяти ( Mov [R1], R2 ) R1 out, Управляющие сигналы операций Сохранение слова в памяти ( Mov [R1], R2 ) R1 out,](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_9.jpg)

![Управляющие сигналы операций Вся команда ( Напр. Add R1, [R3] ): PC out, MAR Управляющие сигналы операций Вся команда ( Напр. Add R1, [R3] ): PC out, MAR](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_10.jpg)

![Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 ](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_7.jpg)

![Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 out, Управляющие сигналы операций Выборка слова из памяти ( Mov R2, [R1] ) R1 out,](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_8.jpg)

![Управляющие сигналы операций Сохранение слова в памяти ( Mov [R1], R2 ) R1 out, Управляющие сигналы операций Сохранение слова в памяти ( Mov [R1], R2 ) R1 out,](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_9.jpg)

![Управляющие сигналы операций Вся команда ( Напр. Add R1, [R3] ): PC out, MAR Управляющие сигналы операций Вся команда ( Напр. Add R1, [R3] ): PC out, MAR](https://present5.com/customparser/5335999_132403931 --- org-evm-2.ppt/slide_10.jpg)