1612.ppt

- Количество слайдов: 32

Организация ЭВМ и систем

Организация ЭВМ и систем

Архитектура системы команд Понятия: система команд и архитектура системы команд

Архитектура системы команд Понятия: система команд и архитектура системы команд

Время выполнения программы (Твыч) Твыч =Nком х CP 1 х пр

Время выполнения программы (Твыч) Твыч =Nком х CP 1 х пр

Взаимосвязь между системой команд и факторами, определяющими эффективность вычислений Исходный код на языке высокого уровня Оптимизирующий компилятор Система команд Nком Выборка команд Декодирование команд CP 1 и пр Объектный код на машинном языке Исполнение команд

Взаимосвязь между системой команд и факторами, определяющими эффективность вычислений Исходный код на языке высокого уровня Оптимизирующий компилятор Система команд Nком Выборка команд Декодирование команд CP 1 и пр Объектный код на машинном языке Исполнение команд

Общая характеристика архитектуры системы команд ВМ складывается из ответов на следующие вопросы: 1. 2. 3. 4. 5. 6. 7. Какого вида данные будут представлены в вычислительной машине и в какой форме? Где эти данные могут храниться помимо основной памяти? Каким образом будет осуществляться доступ к данным? Какие операции могут быть выполнены над данными? Сколько операндов может присутствовать в команде? Как будет определяться адрес очередной команды? Каким образом будут закодированы команды?

Общая характеристика архитектуры системы команд ВМ складывается из ответов на следующие вопросы: 1. 2. 3. 4. 5. 6. 7. Какого вида данные будут представлены в вычислительной машине и в какой форме? Где эти данные могут храниться помимо основной памяти? Каким образом будет осуществляться доступ к данным? Какие операции могут быть выполнены над данными? Сколько операндов может присутствовать в команде? Как будет определяться адрес очередной команды? Каким образом будут закодированы команды?

КЛАССИФИКАЦИЯ АРХИТЕКТУР СИСТЕМЫ КОМАНД

КЛАССИФИКАЦИЯ АРХИТЕКТУР СИСТЕМЫ КОМАНД

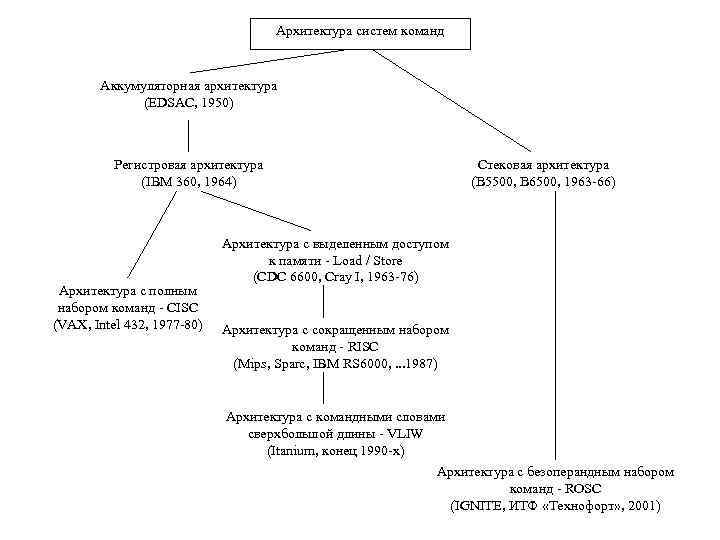

Архитектура систем команд Аккумуляторная архитектура (EDSAC, 1950) Регистровая архитектура (IBM 360, 1964) Архитектура с полным набором команд - CISC (VAX, Intel 432, 1977 -80) Стековая архитектура (В 5500, В 6500, 1963 -66) Архитектура с выделенным доступом к памяти - Load / Store (CDC 6600, Cray I, 1963 -76) Архитектура с сокращенным набором команд - RISC (Mips, Sparc, IBM RS 6000, . . . 1987) Архитектура с командными словами сверхбольшой длины - VLIW (Itanium, конец 1990 -х) Архитектура с безоперандным набором команд - ROSC (IGNITE, ИТФ «Технофорт» , 2001)

Архитектура систем команд Аккумуляторная архитектура (EDSAC, 1950) Регистровая архитектура (IBM 360, 1964) Архитектура с полным набором команд - CISC (VAX, Intel 432, 1977 -80) Стековая архитектура (В 5500, В 6500, 1963 -66) Архитектура с выделенным доступом к памяти - Load / Store (CDC 6600, Cray I, 1963 -76) Архитектура с сокращенным набором команд - RISC (Mips, Sparc, IBM RS 6000, . . . 1987) Архитектура с командными словами сверхбольшой длины - VLIW (Itanium, конец 1990 -х) Архитектура с безоперандным набором команд - ROSC (IGNITE, ИТФ «Технофорт» , 2001)

Классификация по составу и сложности команд Три подхода • архитектура с полным набором команд: CISC (Complex Instruction Set Computer); • архитектура с сокращенным набором команд: RISC (Reduced Instruction Set Computer); • архитектура с командными словами сверхбольшой длины: VLIW (Very Long Instruction Word).

Классификация по составу и сложности команд Три подхода • архитектура с полным набором команд: CISC (Complex Instruction Set Computer); • архитектура с сокращенным набором команд: RISC (Reduced Instruction Set Computer); • архитектура с командными словами сверхбольшой длины: VLIW (Very Long Instruction Word).

Классификация по месту хранения операндов Виды архитектур системы команд: • стековая; • аккумуляторная; • регистровая; • с выделенным доступом к памяти.

Классификация по месту хранения операндов Виды архитектур системы команд: • стековая; • аккумуляторная; • регистровая; • с выделенным доступом к памяти.

Стековая архитектура Стек образует множество логически взаимосвязанных ячеек, взаимодействующих по принципу «последним вошел, первым вышел» (LIFO, Last In First Out).

Стековая архитектура Стек образует множество логически взаимосвязанных ячеек, взаимодействующих по принципу «последним вошел, первым вышел» (LIFO, Last In First Out).

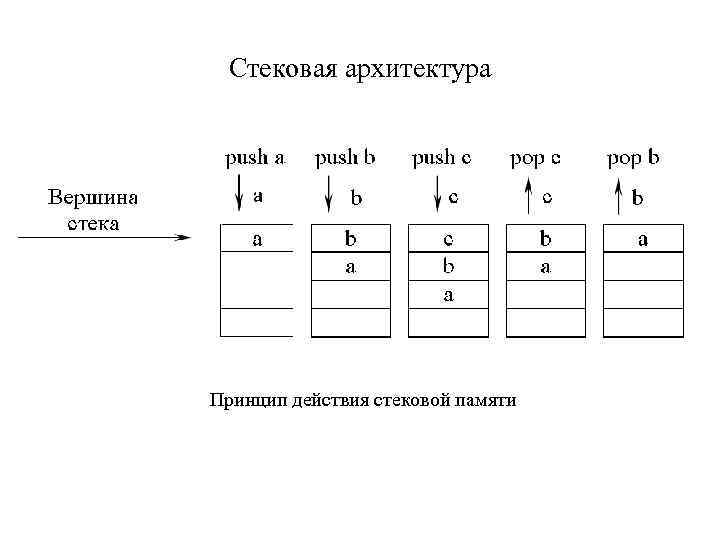

Стековая архитектура Принцип действия стековой памяти

Стековая архитектура Принцип действия стековой памяти

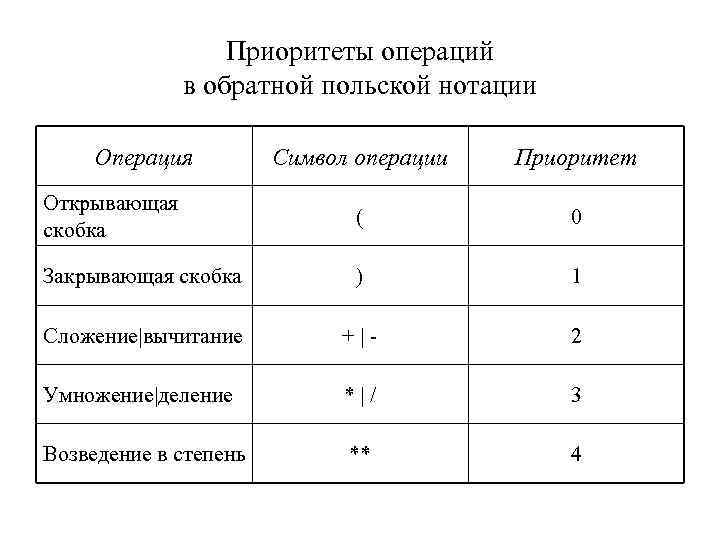

Приоритеты операций в обратной польской нотации Операция Символ операции Приоритет Открывающая скобка ( 0 Закрывающая скобка ) 1 Сложение|вычитание +|- 2 Умножение|деление *|/ 3 Возведение в степень ** 4

Приоритеты операций в обратной польской нотации Операция Символ операции Приоритет Открывающая скобка ( 0 Закрывающая скобка ) 1 Сложение|вычитание +|- 2 Умножение|деление *|/ 3 Возведение в степень ** 4

Формирование обратной польской записи для выражения а = а + b + а х с Просматриваемый символ 1 2 3 4 5 6 7 Входная строка a + b + a x c Состояние стека последовательности операций Выходная строка + a x + b + а = ab+acх+ (постфиксная форма) 9 + + a 8 c x +

Формирование обратной польской записи для выражения а = а + b + а х с Просматриваемый символ 1 2 3 4 5 6 7 Входная строка a + b + a x c Состояние стека последовательности операций Выходная строка + a x + b + а = ab+acх+ (постфиксная форма) 9 + + a 8 c x +

Формирование выходной строки в обратной польской нотации 1. Исходная строка с выражением просматривается слева направо. 2. Операнды переписываются в выходную строку. 3. Знаки операций заносятся в стек последовательности операции (СПО) по следующим правилам: - если СПО пуст, то операция из входной строки переписывается в СПО; - операция выталкивает из СПО в выходную строку все операции с большим или равным приоритетом; - если очередной символ из исходной строки есть открывающая скобка, то он проталкивается в СПО; - закрывающая круглая скобка выталкивает все операции из СПО до ближайшей открывающей скобки, сами скобки в выходную строку не переписываются, а уничтожают друга.

Формирование выходной строки в обратной польской нотации 1. Исходная строка с выражением просматривается слева направо. 2. Операнды переписываются в выходную строку. 3. Знаки операций заносятся в стек последовательности операции (СПО) по следующим правилам: - если СПО пуст, то операция из входной строки переписывается в СПО; - операция выталкивает из СПО в выходную строку все операции с большим или равным приоритетом; - если очередной символ из исходной строки есть открывающая скобка, то он проталкивается в СПО; - закрывающая круглая скобка выталкивает все операции из СПО до ближайшей открывающей скобки, сами скобки в выходную строку не переписываются, а уничтожают друга.

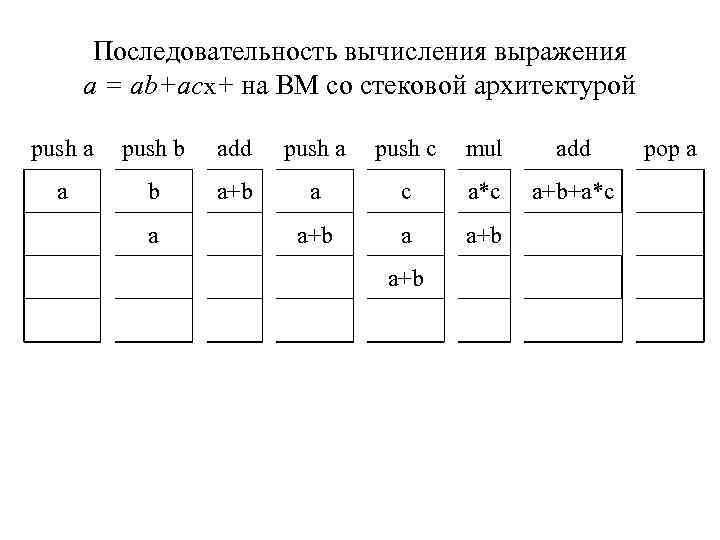

Последовательность вычисления выражения а = ab+acх+ на ВМ со стековой архитектурой push a push b add push a push c mul add a b a+b a c a*c a+b+a*c a+b a a+b pop a

Последовательность вычисления выражения а = ab+acх+ на ВМ со стековой архитектурой push a push b add push a push c mul add a b a+b a c a*c a+b+a*c a+b a a+b pop a

Достоинства АСК на базе стека: • возможность сокращения адресной части команд; • код программы получается компактным; • достаточно просто реализуется декодирование команд. Недостатки: • стековая АСК по определению не предполагает произвольного доступа к памяти, из-за чего компилятору трудно создать эффективный программный код; • стек становится «узким местом» ВМ в плане повышения производительности.

Достоинства АСК на базе стека: • возможность сокращения адресной части команд; • код программы получается компактным; • достаточно просто реализуется декодирование команд. Недостатки: • стековая АСК по определению не предполагает произвольного доступа к памяти, из-за чего компилятору трудно создать эффективный программный код; • стек становится «узким местом» ВМ в плане повышения производительности.

Аккумуляторная архитектура Для хранения одного из операндов арифметической или логической операции в процессоре имеется выделенный регистр — аккумулятор. В этот же регистр заносится и результат операции. Достоинства: короткие команды и простота декодирования команд. Недостатки: наличие всего одного регистра порождает многократные обращения к основной памяти.

Аккумуляторная архитектура Для хранения одного из операндов арифметической или логической операции в процессоре имеется выделенный регистр — аккумулятор. В этот же регистр заносится и результат операции. Достоинства: короткие команды и простота декодирования команд. Недостатки: наличие всего одного регистра порождает многократные обращения к основной памяти.

Регистровая архитектура В машинах данного типа процессор включает в себя массив регистров (регистровый файл), известных как регистры общего назначения (РОН). Расположение операндов осуществляется в одной из двух запоминающих сред: основной памяти или регистрах. Выделяю три подвида команд обработки: • регистр-регистр; • регистр-память; • память-память.

Регистровая архитектура В машинах данного типа процессор включает в себя массив регистров (регистровый файл), известных как регистры общего назначения (РОН). Расположение операндов осуществляется в одной из двух запоминающих сред: основной памяти или регистрах. Выделяю три подвида команд обработки: • регистр-регистр; • регистр-память; • память-память.

Достоинства регистровых АСК: компактность получаемого кода, высокая скорость вычислений за счет замены обращений к основной памяти на обращения к быстрым регистрам. Недостатки: данная архитектура требует более длинных инструкций по сравнению с аккумуляторной архитектурой

Достоинства регистровых АСК: компактность получаемого кода, высокая скорость вычислений за счет замены обращений к основной памяти на обращения к быстрым регистрам. Недостатки: данная архитектура требует более длинных инструкций по сравнению с аккумуляторной архитектурой

Архитектура с выделенным доступом к памяти Обращение к основной памяти осуществляется только с помощью двух специальных команд: load и store. Достоинства АСК: простота декодирования и исполнения команды.

Архитектура с выделенным доступом к памяти Обращение к основной памяти осуществляется только с помощью двух специальных команд: load и store. Достоинства АСК: простота декодирования и исполнения команды.

ТИПЫ И ФОРМАТЫ ОПЕРАНДОВ

ТИПЫ И ФОРМАТЫ ОПЕРАНДОВ

Числовая информация

Числовая информация

Числа в форме с фиксированной запятой

Числа в форме с фиксированной запятой

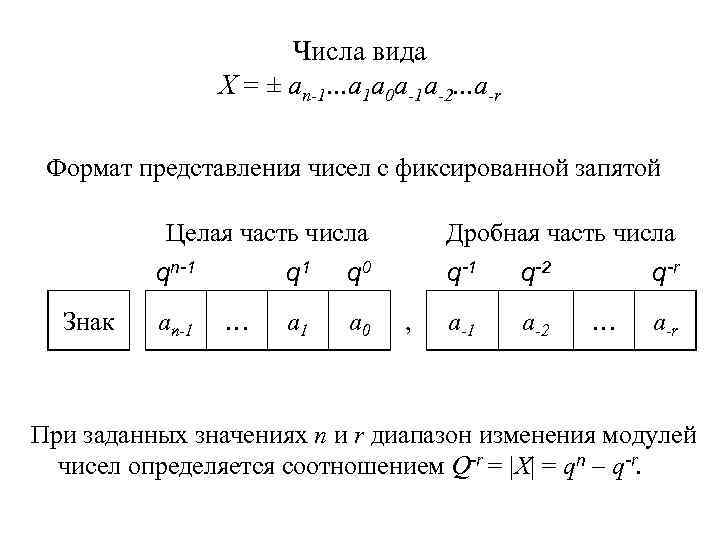

Числа вида X = ± an-1. . . a 1 a 0 a-1 a-2. . . a-r Формат представления чисел с фиксированной запятой Целая часть числа qn-1 Знак an-1 q 1 … q 0 a 1 a 0 Дробная часть числа q-1 , q-2 a-1 a-2 q-r … a-r При заданных значениях п и r диапазон изменения модулей чисел определяется соотношением Q-r = |X| = qn – q-r.

Числа вида X = ± an-1. . . a 1 a 0 a-1 a-2. . . a-r Формат представления чисел с фиксированной запятой Целая часть числа qn-1 Знак an-1 q 1 … q 0 a 1 a 0 Дробная часть числа q-1 , q-2 a-1 a-2 q-r … a-r При заданных значениях п и r диапазон изменения модулей чисел определяется соотношением Q-r = |X| = qn – q-r.

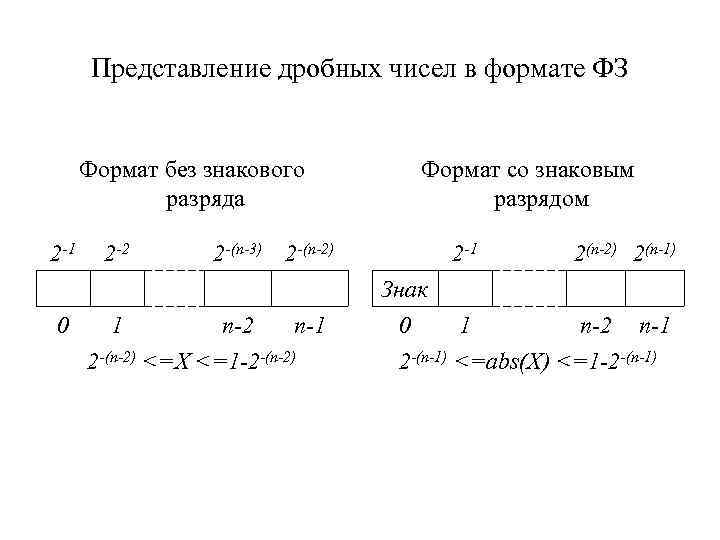

Представление дробных чисел в формате ФЗ Формат без знакового разряда 2 -1 2 -2 Формат со знаковым разрядом 2 -(n-3) 2 -(n-2) 2 -1 2(n-2) 2(n-1) Знак 0 1 n-2 n-1 2 -(n-2) <=X <=1 -2 -(n-2) 0 1 n-2 n-1 2 -(n-1) <=abs(X) <=1 -2 -(n-1)

Представление дробных чисел в формате ФЗ Формат без знакового разряда 2 -1 2 -2 Формат со знаковым разрядом 2 -(n-3) 2 -(n-2) 2 -1 2(n-2) 2(n-1) Знак 0 1 n-2 n-1 2 -(n-2) <=X <=1 -2 -(n-2) 0 1 n-2 n-1 2 -(n-1) <=abs(X) <=1 -2 -(n-1)

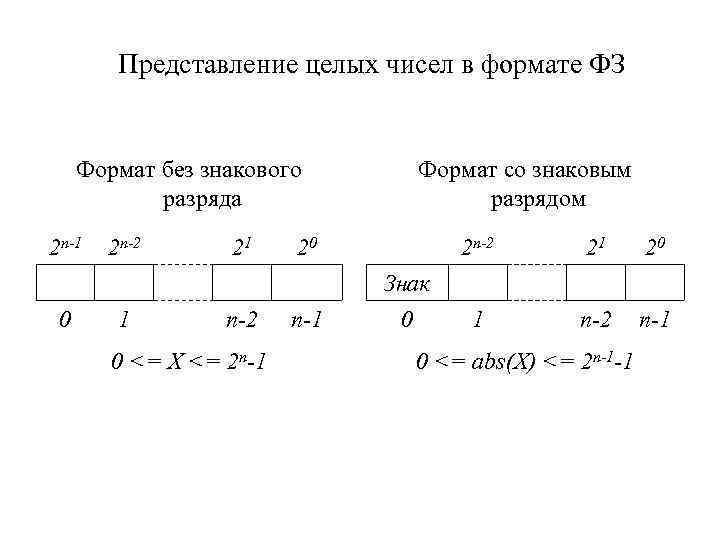

Представление целых чисел в формате ФЗ Формат без знакового разряда 2 n-1 2 n-2 21 Формат со знаковым разрядом 20 2 n-2 21 20 1 n-2 n-1 Знак 0 1 n-2 0 <= X <= 2 n-1 0 0 <= abs(X) <= 2 n-1 -1

Представление целых чисел в формате ФЗ Формат без знакового разряда 2 n-1 2 n-2 21 Формат со знаковым разрядом 20 2 n-2 21 20 1 n-2 n-1 Знак 0 1 n-2 0 <= X <= 2 n-1 0 0 <= abs(X) <= 2 n-1 -1

Упакованные целые числа

Упакованные целые числа

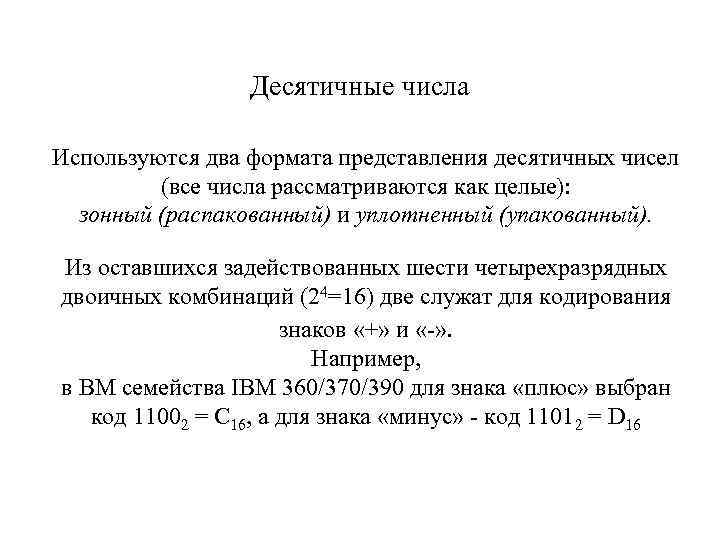

Десятичные числа Используются два формата представления десятичных чисел (все числа рассматриваются как целые): зонный (распакованный) и уплотненный (упакованный). Из оставшихся задействованных шести четырехразрядных двоичных комбинаций (24=16) две служат для кодирования знаков «+» и «-» . Например, в ВМ семейства IBM 360/370/390 для знака «плюс» выбран код 11002 = С 16, а для знака «минус» - код 11012 = D 16

Десятичные числа Используются два формата представления десятичных чисел (все числа рассматриваются как целые): зонный (распакованный) и уплотненный (упакованный). Из оставшихся задействованных шести четырехразрядных двоичных комбинаций (24=16) две служат для кодирования знаков «+» и «-» . Например, в ВМ семейства IBM 360/370/390 для знака «плюс» выбран код 11002 = С 16, а для знака «минус» - код 11012 = D 16

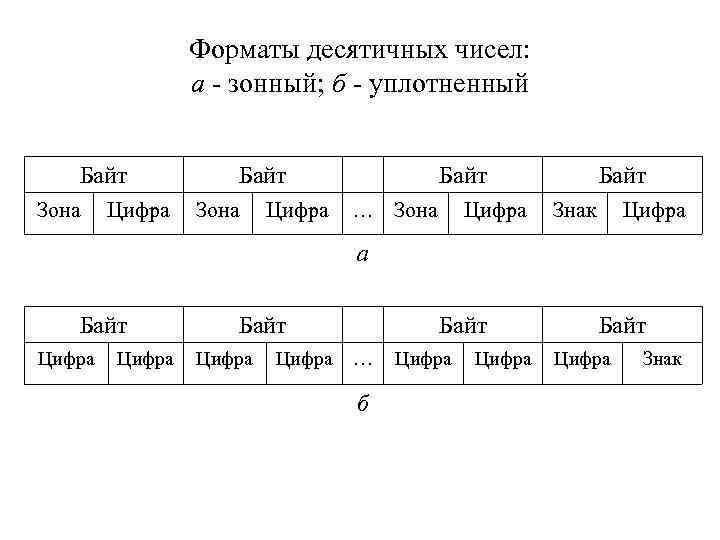

Форматы десятичных чисел: а - зонный; б - уплотненный Байт Зона Цифра Байт … Зона Цифра Байт Знак Цифра а Байт Цифра Байт … б Цифра Байт Цифра Знак

Форматы десятичных чисел: а - зонный; б - уплотненный Байт Зона Цифра Байт … Зона Цифра Байт Знак Цифра а Байт Цифра Байт … б Цифра Байт Цифра Знак

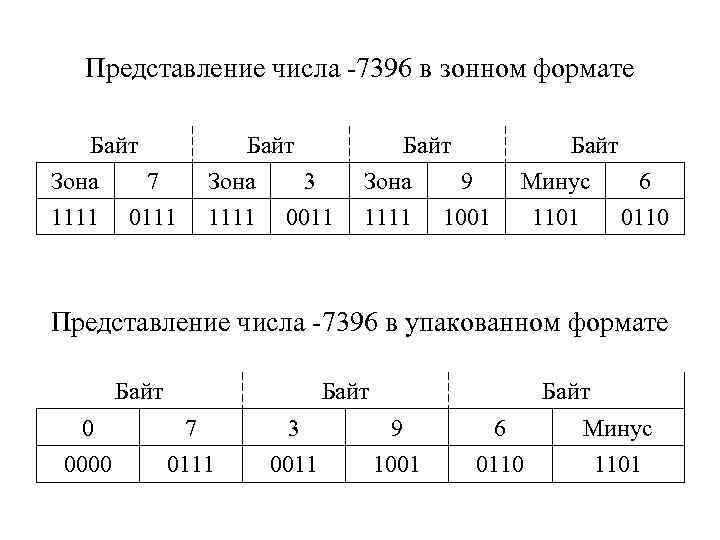

Представление числа -7396 в зонном формате Байт Зона 7 Байт Зона 3 Байт Зона 9 1111 0011 Байт Минус 6 1001 1101 0110 Представление числа -7396 в упакованном формате Байт 0 7 3 9 6 Минус 0000 0111 0011 1001 0110 1101

Представление числа -7396 в зонном формате Байт Зона 7 Байт Зона 3 Байт Зона 9 1111 0011 Байт Минус 6 1001 1101 0110 Представление числа -7396 в упакованном формате Байт 0 7 3 9 6 Минус 0000 0111 0011 1001 0110 1101

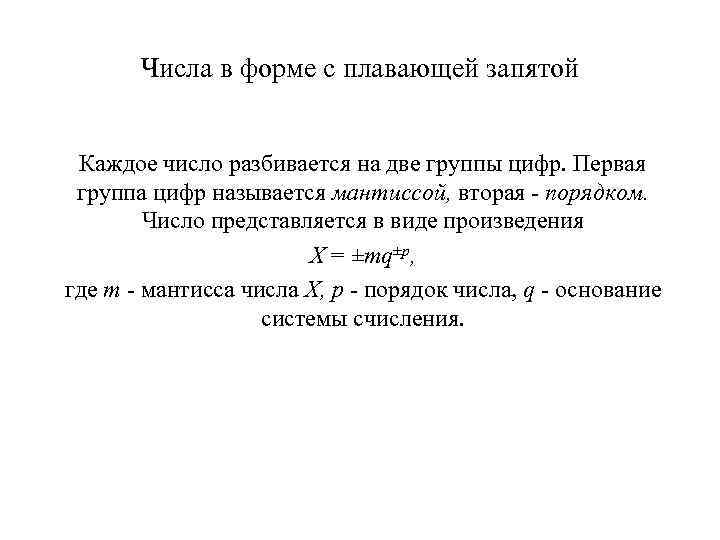

Числа в форме с плавающей запятой Каждое число разбивается на две группы цифр. Первая группа цифр называется мантиссой, вторая - порядком. Число представляется в виде произведения X = ±mq±p, где т - мантисса числа X, р - порядок числа, q - основание системы счисления.

Числа в форме с плавающей запятой Каждое число разбивается на две группы цифр. Первая группа цифр называется мантиссой, вторая - порядком. Число представляется в виде произведения X = ±mq±p, где т - мантисса числа X, р - порядок числа, q - основание системы счисления.

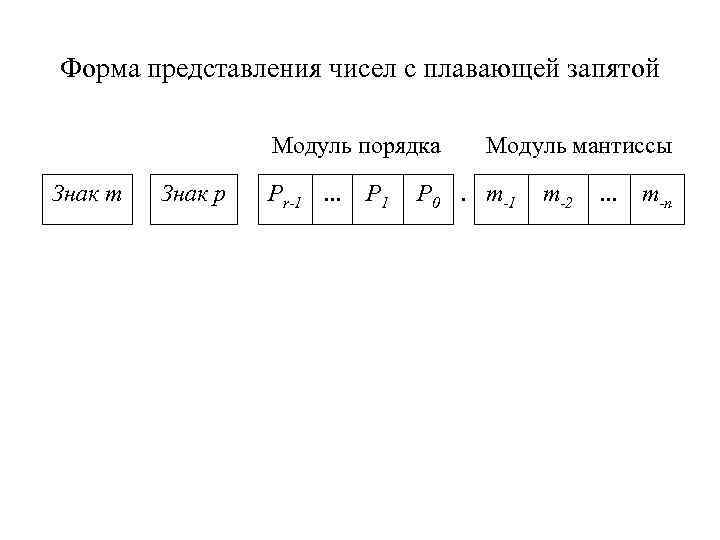

Форма представления чисел с плавающей запятой Модуль порядка Знак m Знак р Pr-1 … P 1 Модуль мантиссы P 0. m-1 m-2 … m-n

Форма представления чисел с плавающей запятой Модуль порядка Знак m Знак р Pr-1 … P 1 Модуль мантиссы P 0. m-1 m-2 … m-n