cpu.ppt

- Количество слайдов: 30

Организация ЭВМ 3. Организация процессоров общего назначения 1

Организация ЭВМ План 1 Понятие о процессоре 2 Классификация процессоров 3 Логическая схема процессора (подсистемы) 4 Магистральный процессор 5 Виды операционных устройств 6 Архитектура системы команд. RISC и CISC 7 Задачи УУ. Этапы выполнения команды 8 Микроархитектура, выполняющая команду 9 Способы повышения производительности 10 Развитие архитектур процессоров x 86 2

Организация ЭВМ 1 Понятие о процессоре Процессор - устройство, выполняющее автоматическую обработку данных (по заданным алгоритмам) и программное управление этим процессом. 3

Организация ЭВМ 2 Классификация процессоров 2. 1 Система счисления : - позиционная; - непозиционная (например, СОК). 2. 2 По способу обработки разрядов: - последовательная; - параллельная; - смешанная. 4

Организация ЭВМ 2 Классификация процессоров 2. 3 Состав операций : - общего назначения; - специализированные (например, ЦОС, GPU); - проблемно-ориентированные (например, MPEG) 2. 4 По месту в системе: - ЦПУ (CPU); - сопроцессор; - периферийный; - канальный (связной); - ПЭ. 5

Организация ЭВМ 2 Классификация процессоров 2. 5 Тип операндов : - скалярный; - векторный; - и те, и другие (например, скалярный + SSE). 2. 6 Организация обработки адресов: - на общем операционном устройстве (ОУ); - на отдельном (адресном) ОУ. 6

Организация ЭВМ 2 Классификация процессоров 2. 7 Организация ОУ : - ОУ процедурного типа (I-процессор, M-процессор); - с арифметическим конвейером; - блочное ОУ. 7

Организация ЭВМ 2 Классификация процессоров 2. 8 Логика управления (УУ) : - жесткая (на триггерном УА); - микропрограммная (хранимая) на базе памяти микропрограмм. 8

Организация ЭВМ 2 Классификация процессоров 2. 9 Архитектура системы команд (ISA) : - CISC (Complete Instruction Set Computer); - RISC (Reduced Instruction Set Computer); - MISC (Minimal Instruction Set Computer); - CISC со внутренними RISC-инструкциями; - VLIW (Very Long Instruction Word) 9

Организация ЭВМ 2 Классификация процессоров 2. 10 Способ обработки потока(ов) команд : - последовательная обработка (фон Нейман), (IPC < 1 CPI > 1); - конвейер команд (IPC = 1); - суперскалярный процессор (IPC > 1); - с длинным командным словом (VLIW); - гиперпоточность (hyper threading); - многоядерные процессоры (multicore). 10

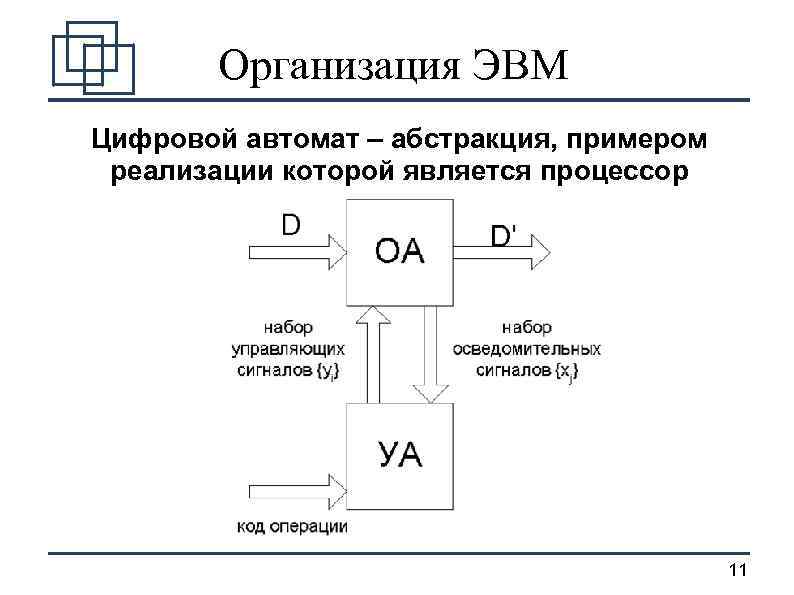

Организация ЭВМ Цифровой автомат – абстракция, примером реализации которой является процессор 11

Организация ЭВМ 3 Логическая организация (подсистемы) процессора общего назначения 12

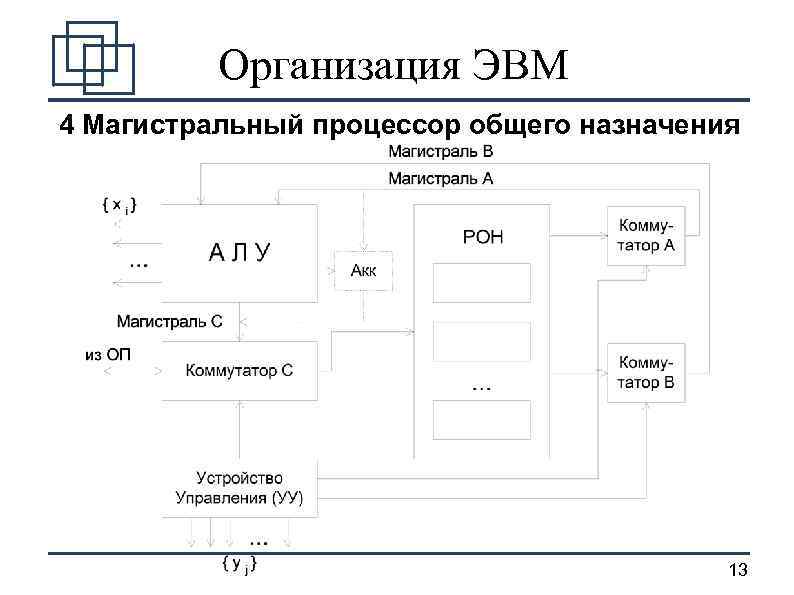

Организация ЭВМ 4 Магистральный процессор общего назначения 13

Организация ЭВМ 5 Виды операционных устройств - процедурные ОУ (I-процессор, М-процессор) описаны во 2 лабораторной работе на примере косвенного умножителя; - арифметические конвейеры (пример – аппаратные матричные и древовидные умножители); - блочные ОУ (несколько блоков, работающих параллельно). 14

Организация ЭВМ 6 Две базовые архитектуры систем команд (ISA) CISC - много команд; - неравнозначная сложность; - сложно конвейеризовать; - мало регистров; -команды память; сложное УУ. RISC - меньше команд; - много регистров; -команды загрузки и сохранения в память; - простое УУ; - трехадресные ; - жесткая логика УУ; - однотипные, легко построить конвейер 15

Организация ЭВМ 7 Этапы выполнения команды 1 - загрузка команды из памяти (IF); 2 - декодирование команды (ID); 3 - исполнение команды (EX) (один или несколько тактов); 4 - возможно – обращение к памяти (MEM); 5 - завершение выполнения команды, формир. адреса след. и переход к ней (WB). 16

Организация ЭВМ 7 Устройство управления 7. 1 Задачи УУ : 1 – управление выполнением команд (!!!); 2 – управление выполнением программ; 3 – управление процессором в целом 7. 2 Варианты построения УУ : 1 – микропрограммное с ПЗУ микропрограмм; 2 – с жесткой логикой (триггеры и КС управления) 17

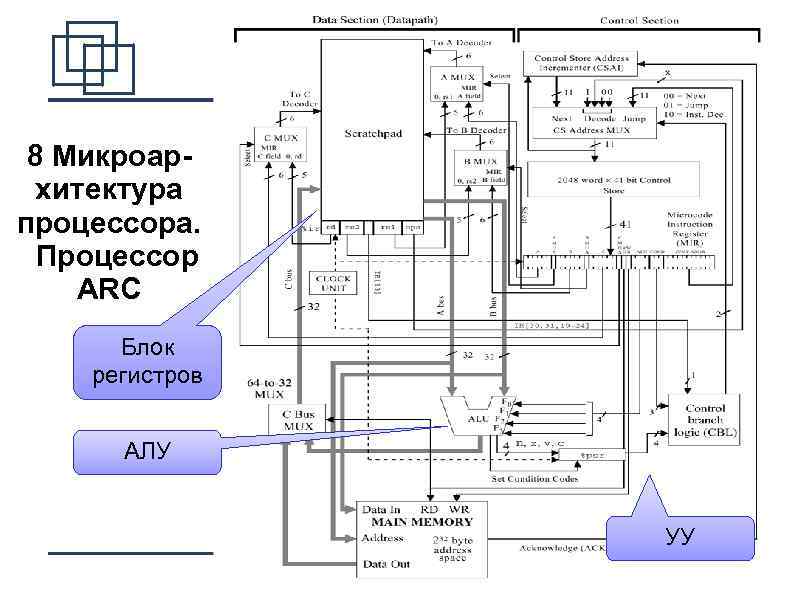

Организация ЭВМ 8 Микроархитектура процессора. Процессор ARC Блок регистров АЛУ УУ 18

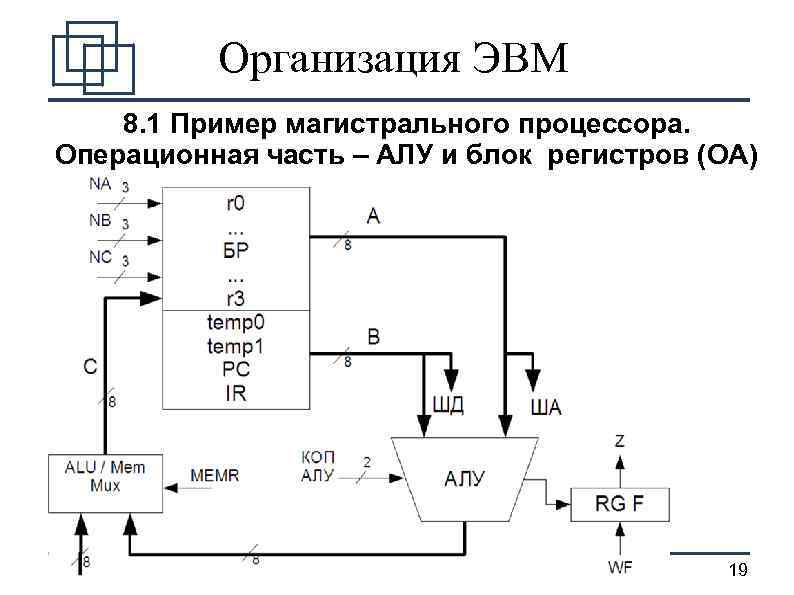

Организация ЭВМ 8. 1 Пример магистрального процессора. Операционная часть – АЛУ и блок регистров (ОА) 19

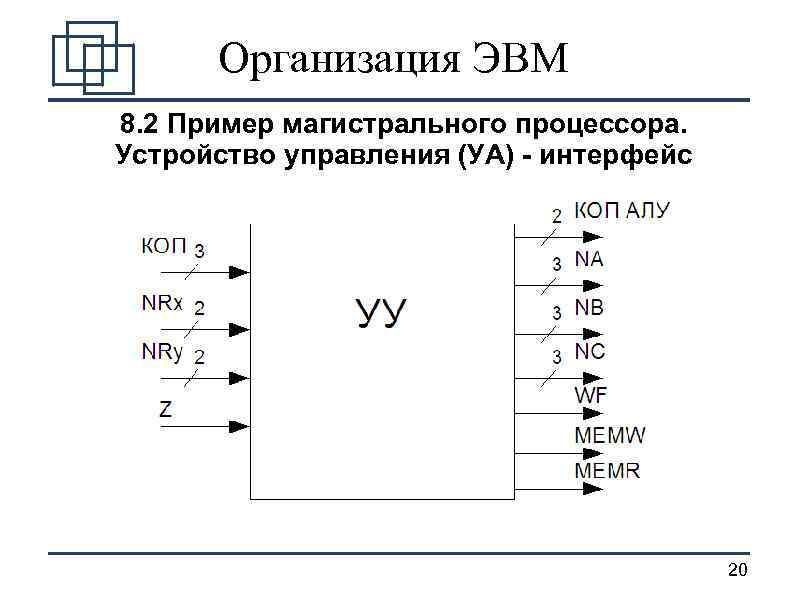

Организация ЭВМ 8. 2 Пример магистрального процессора. Устройство управления (УА) - интерфейс 20

Организация ЭВМ 8. 2 Пример магистрального процессора. Микропрограммное устройство управления РМК — регистр микрокоманды, ПМП — память микропрограмм, CSAddr — устройство формирования адреса микрокоманды в ПМП 21

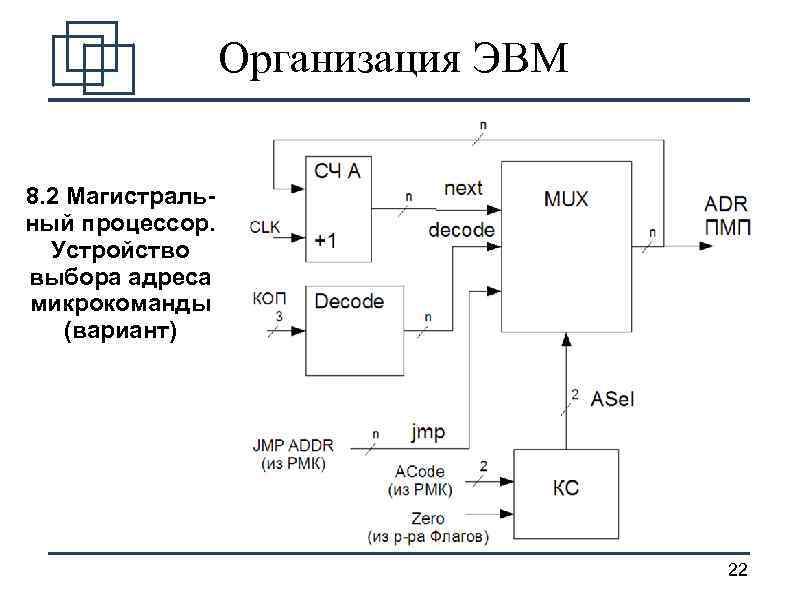

Организация ЭВМ 8. 2 Магистральный процессор. Устройство выбора адреса микрокоманды (вариант) 22

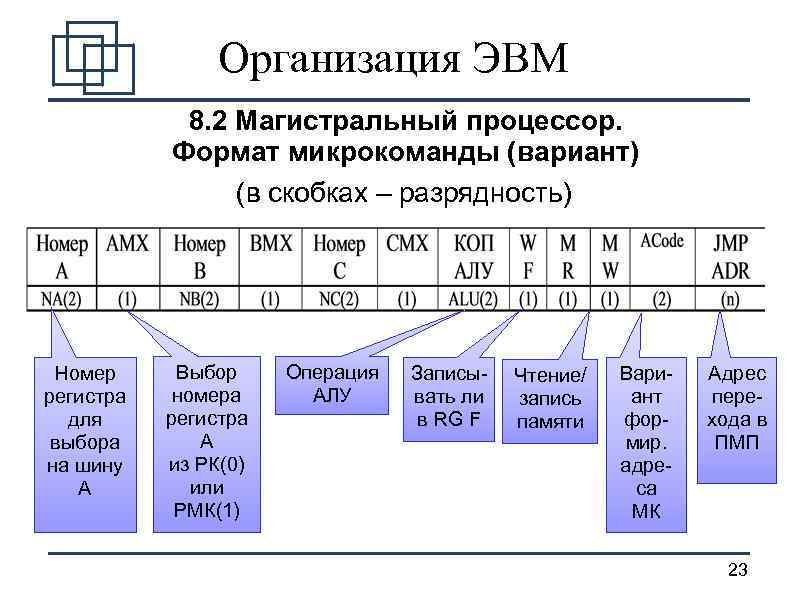

Организация ЭВМ 8. 2 Магистральный процессор. Формат микрокоманды (вариант) (в скобках – разрядность) Номер регистра для выбора на шину А Выбор номера регистра А из РК(0) или РМК(1) Операция АЛУ Записывать ли в RG F Чтение/ запись памяти Вариант формир. адреса МК Адрес перехода в ПМП 23

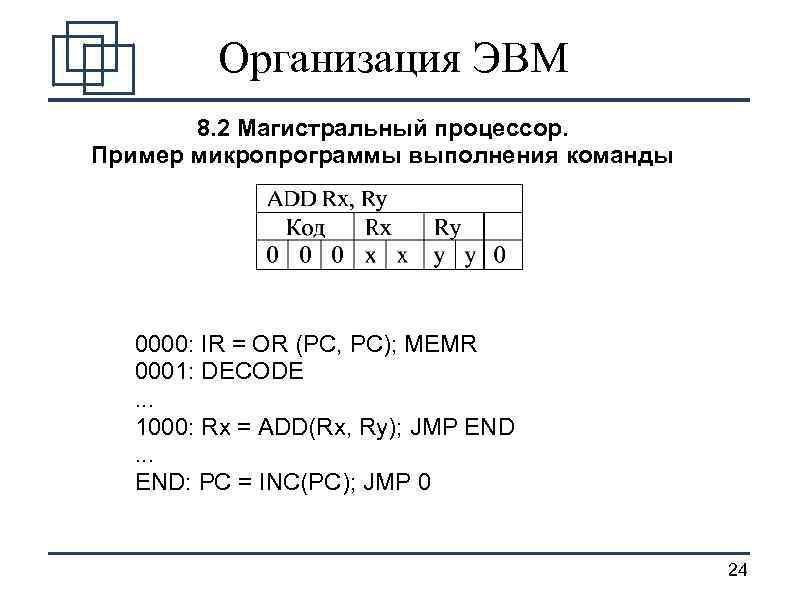

Организация ЭВМ 8. 2 Магистральный процессор. Пример микропрограммы выполнения команды 0000: IR = OR (PC, PC); MEMR 0001: DECODE. . . 1000: Rx = ADD(Rx, Ry); JMP END. . . END: PC = INC(PC); JMP 0 24

Организация ЭВМ 8. 2 Магистральный процессор. Пример микропрограммы с кодировкой микрокоманд 0000: IR = NAND (PC, PC); MEMR; NEXT A=B=PC; AMX=BMX=1; C=IR; CMX=1; ALU=NAND (00); MRD=1; MWR=0; WF=0; ACode=Next(00); JAddr=0 0001: DECODE A=B=C=Temp 0; AMX=BMX=CMX=1; ALU=NAND (00); MRD=MWR=0; WF=0; ACode=Decode(01); JAddr=0. . . 1000: Rx = ADD(Rx, Ry); JMP END A=B=C=0; AMX=BMX=CMX=0; ALU=ADD (01); MRD=MWR=0; WF=1; Acode=JMP(11); JAddr =END. . . END: PC = INC(PC); JMP 0 A=B=C=PC; AMX=BMX=CMX=1; ALU=INC (11); MRD=MWR=0; WF=0; Acode=JMP(11); JAddr =0 25

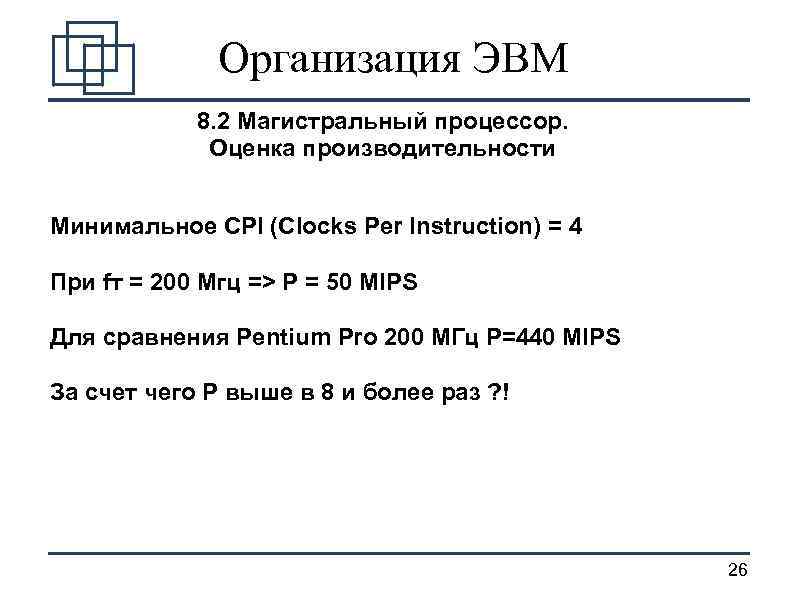

Организация ЭВМ 8. 2 Магистральный процессор. Оценка производительности Минимальное CPI (Clocks Per Instruction) = 4 При fт = 200 Мгц => P = 50 MIPS Для сравнения Pentium Pro 200 МГц P=440 MIPS За счет чего P выше в 8 и более раз ? ! 26

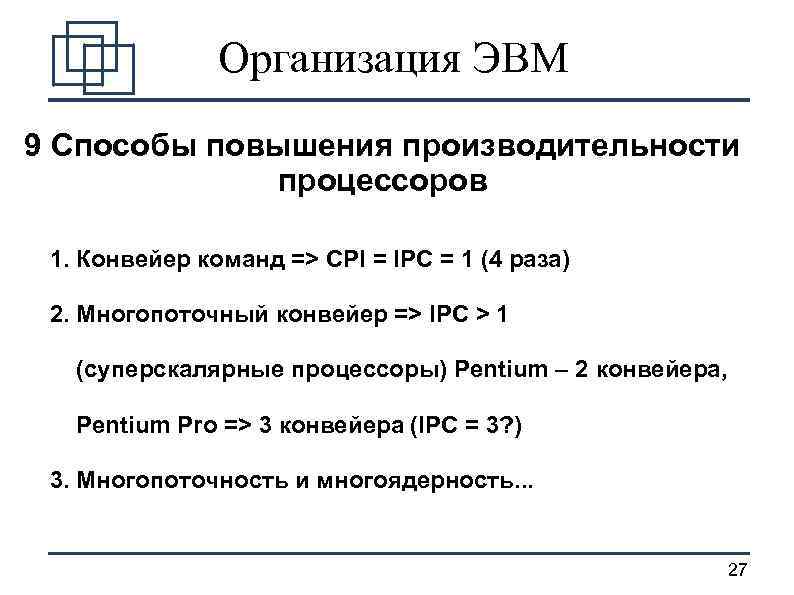

Организация ЭВМ 9 Способы повышения производительности процессоров 1. Конвейер команд => CPI = IPC = 1 (4 раза) 2. Многопоточный конвейер => IPC > 1 (суперскалярные процессоры) Pentium – 2 конвейера, Pentium Pro => 3 конвейера (IPC = 3? ) 3. Многопоточность и многоядерность. . . 27

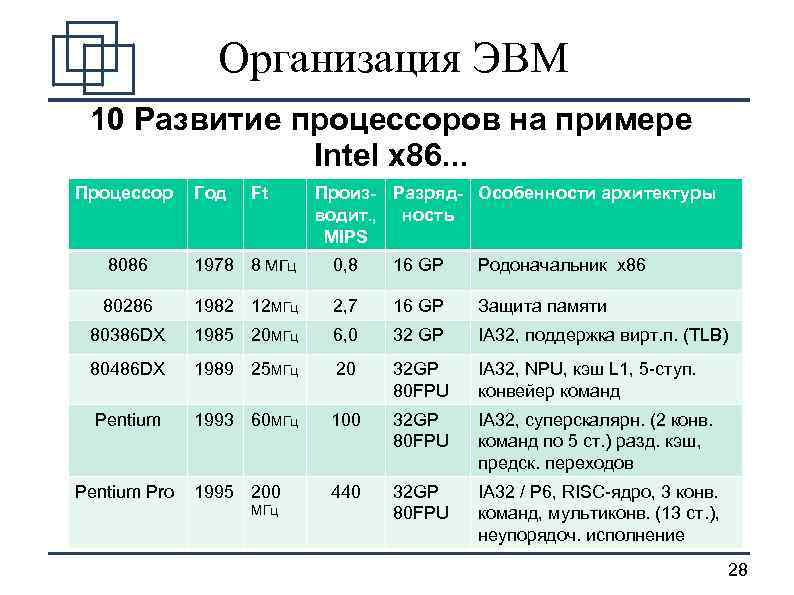

Организация ЭВМ 10 Развитие процессоров на примере Intel x 86. . . Процессор Год Ft Произ- Разряд- Особенности архитектуры водит. , ность MIPS 8086 1978 8 МГц 0, 8 16 GP Родоначальник x 86 80286 1982 12 МГц 2, 7 16 GP Защита памяти 80386 DX 1985 20 МГц 6, 0 32 GP IA 32, поддержка вирт. п. (TLB) 80486 DX 1989 25 МГц 20 32 GP 80 FPU IA 32, NPU, кэш L 1, 5 -ступ. конвейер команд Pentium 1993 60 МГц 100 32 GP 80 FPU IA 32, суперскалярн. (2 конв. команд по 5 ст. ) разд. кэш, предск. переходов 1995 200 440 32 GP 80 FPU IA 32 / P 6, RISC-ядро, 3 конв. команд, мультиконв. (13 ст. ), неупорядоч. исполнение Pentium Pro МГц 28

Организация ЭВМ 10 Развитие процессоров на примере Intel x 86. . . (? ) Процессор Год Ft Производит. , MIPS Разрядность Особенности архитектуры Pentium II 1997 266 Мгц ~700 32 GP 80 FPU 64 MMX P 6 + MMX, L 2 кэш в том же корпусе Pentium III 1999 500 МГц ~1400 32 GP 80 FPU 64 MMX 128 XMM P 6 + SSE, L 2 кэш на кристалле Pentium IV 2000 1, 5 ГГц ~3000 32 GP 80 FPU 64 MMX 128 XMM Net. Burst (6, 4 Гб/с – пр-ть работы с памятью), гиперконвейер (24 ст. ), кэш микро-инструкций, HT 29

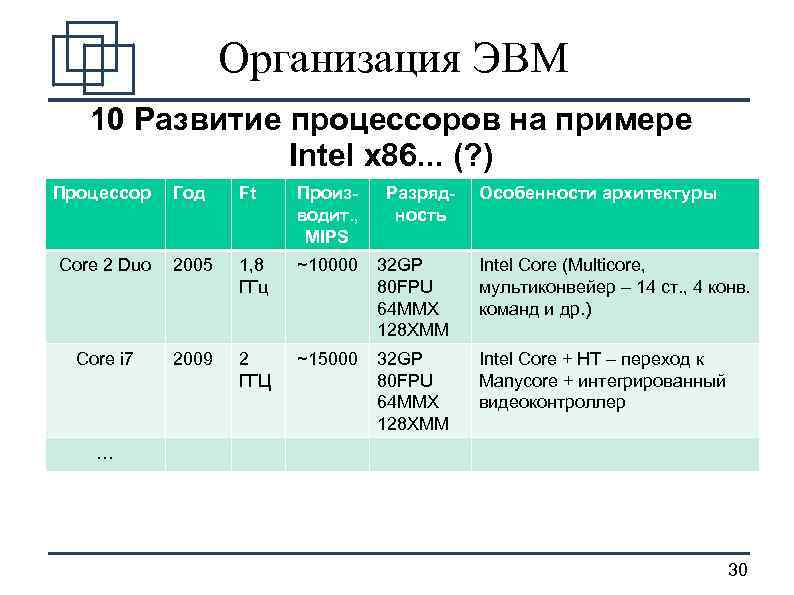

Организация ЭВМ 10 Развитие процессоров на примере Intel x 86. . . (? ) Процессор Год Ft Производит. , MIPS Разрядность Особенности архитектуры Core 2 Duo 2005 1, 8 ГГц ~10000 32 GP 80 FPU 64 MMX 128 XMM Intel Core (Multicore, мультиконвейер – 14 ст. , 4 конв. команд и др. ) Core i 7 2009 2 ГГЦ ~15000 32 GP 80 FPU 64 MMX 128 XMM Intel Core + HT – переход к Manycore + интегрированный видеоконтроллер … 30

cpu.ppt