c92515da1fe9acf3f79b4f4503a4221f.ppt

- Количество слайдов: 71

ORGANISASI KOMPUTER INPUT OUTPUT ORGANIZATION

ORGANISASI KOMPUTER INPUT OUTPUT ORGANIZATION

Mengakses Peralatan I/O Menerima input, memproses, dan menghasilkan output merupakan kemampuan dari konputer. Berarti komputer harus memiliki kemampuan untuk mengakses peralatan input dan output. Untuk itulah komputer harus memiliki fungsi : R Addressing atau pemilihan peralatan I/0 untuk suatu operasi transfer yang diinginkan. R Pemindahan data ke dan dari peralatan yang dipilih. R Sinkronisasi atau koordinasi waktu untuk operasi input dan output.

Mengakses Peralatan I/O Menerima input, memproses, dan menghasilkan output merupakan kemampuan dari konputer. Berarti komputer harus memiliki kemampuan untuk mengakses peralatan input dan output. Untuk itulah komputer harus memiliki fungsi : R Addressing atau pemilihan peralatan I/0 untuk suatu operasi transfer yang diinginkan. R Pemindahan data ke dan dari peralatan yang dipilih. R Sinkronisasi atau koordinasi waktu untuk operasi input dan output.

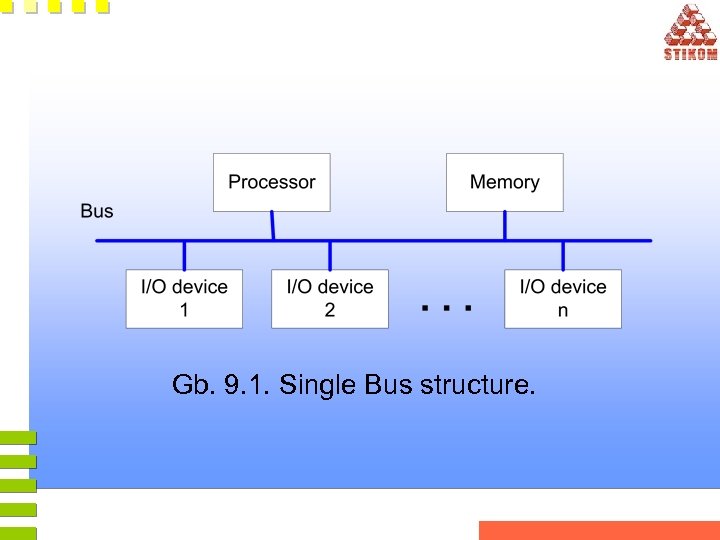

èStruktur Single Bus: Prosesor, Memory, dan peralatan I/O dihubungkan pada 1 bus, yg terdiri dari 3 set line yg digunakan utk membawa address, data dan control signal. Ø Setiap peralatan I/O diberi satu set address. Ø Jika prosesor menempatkan suatu address tertentu pada address lines, peralatan tsb dapat mengenalinya dan memberikan respon kepada perintah pada control line. Ø Prosesor meminta operasi Read atau Write, dan data yg diminta dikirim melalui data line.

èStruktur Single Bus: Prosesor, Memory, dan peralatan I/O dihubungkan pada 1 bus, yg terdiri dari 3 set line yg digunakan utk membawa address, data dan control signal. Ø Setiap peralatan I/O diberi satu set address. Ø Jika prosesor menempatkan suatu address tertentu pada address lines, peralatan tsb dapat mengenalinya dan memberikan respon kepada perintah pada control line. Ø Prosesor meminta operasi Read atau Write, dan data yg diminta dikirim melalui data line.

Gb. 9. 1. Single Bus structure.

Gb. 9. 1. Single Bus structure.

q. Peralatan I/O dan memory yg berbagi ruang address yg sama disebut sebagai memory-mapped I/O. q. Intruksi mesin yg digunakan utk mengakses memory dapat digunakan utk memindahkan data ke dan dari peralatan I/O.

q. Peralatan I/O dan memory yg berbagi ruang address yg sama disebut sebagai memory-mapped I/O. q. Intruksi mesin yg digunakan utk mengakses memory dapat digunakan utk memindahkan data ke dan dari peralatan I/O.

Mis: Ø Move DATAIN, R 0 utk membaca data dari DATAIN dan menyimpannya di register R 0. DATAIN: address input buffer yg berhubungan dg keyboard. Ø Move R 0, DATAOUT mengirim isi register R 0 ke lokasi DATAOUT, yg dapat berupa output data buffer dari suatu display atau sebuah printer. Contoh prosesor yg menggunakan memorymapped I/O: 68000.

Mis: Ø Move DATAIN, R 0 utk membaca data dari DATAIN dan menyimpannya di register R 0. DATAIN: address input buffer yg berhubungan dg keyboard. Ø Move R 0, DATAOUT mengirim isi register R 0 ke lokasi DATAOUT, yg dapat berupa output data buffer dari suatu display atau sebuah printer. Contoh prosesor yg menggunakan memorymapped I/O: 68000.

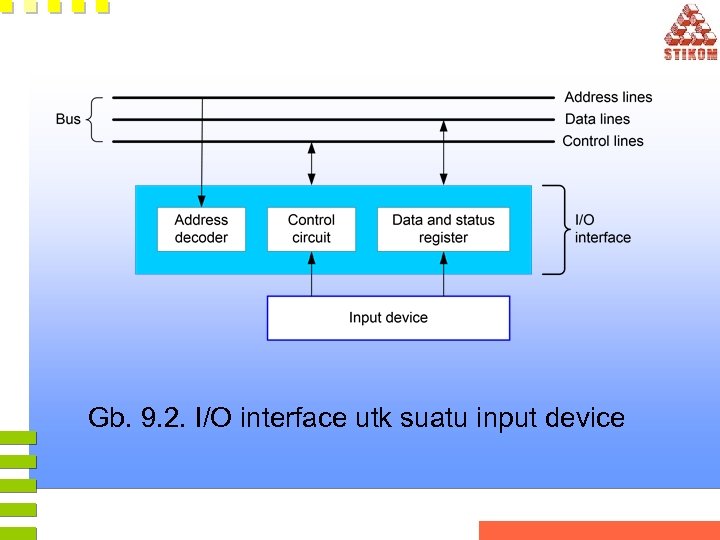

Ø Prosesor Intel memiliki instruksi I/O khusus dan ruang address khusus utk peralatan I/O. Ø Pada prosesor Power PC, peralatan I/O dapat ditempatkan pd address yg sama atau terpisah dari memory. Prosesor ini memiliki control register yg dapat digunakan utk berpindah dr satu ruang address ke yg lain. Gambar berikut menunjukkan hardware yg digunakan utk menghubungkan peralatan I/O ke bus yg disebut Interface.

Ø Prosesor Intel memiliki instruksi I/O khusus dan ruang address khusus utk peralatan I/O. Ø Pada prosesor Power PC, peralatan I/O dapat ditempatkan pd address yg sama atau terpisah dari memory. Prosesor ini memiliki control register yg dapat digunakan utk berpindah dr satu ruang address ke yg lain. Gambar berikut menunjukkan hardware yg digunakan utk menghubungkan peralatan I/O ke bus yg disebut Interface.

Gb. 9. 2. I/O interface utk suatu input device

Gb. 9. 2. I/O interface utk suatu input device

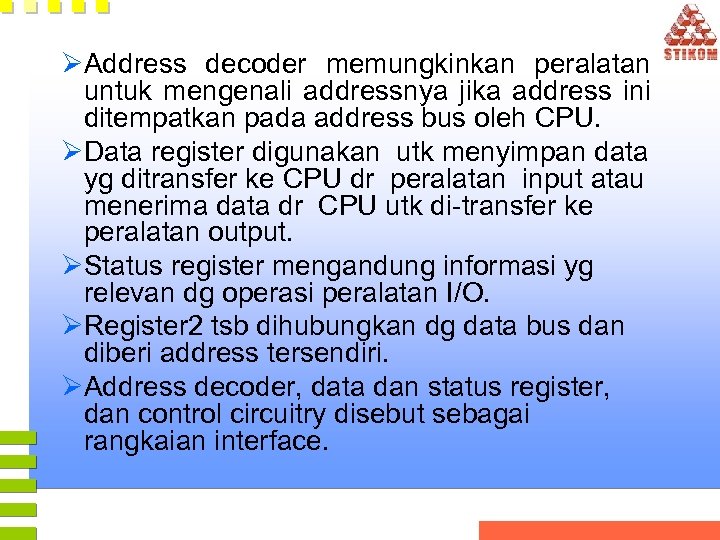

ØAddress decoder memungkinkan peralatan untuk mengenali addressnya jika address ini ditempatkan pada address bus oleh CPU. ØData register digunakan utk menyimpan data yg ditransfer ke CPU dr peralatan input atau menerima data dr CPU utk di-transfer ke peralatan output. ØStatus register mengandung informasi yg relevan dg operasi peralatan I/O. ØRegister 2 tsb dihubungkan dg data bus dan diberi address tersendiri. ØAddress decoder, data dan status register, dan control circuitry disebut sebagai rangkaian interface.

ØAddress decoder memungkinkan peralatan untuk mengenali addressnya jika address ini ditempatkan pada address bus oleh CPU. ØData register digunakan utk menyimpan data yg ditransfer ke CPU dr peralatan input atau menerima data dr CPU utk di-transfer ke peralatan output. ØStatus register mengandung informasi yg relevan dg operasi peralatan I/O. ØRegister 2 tsb dihubungkan dg data bus dan diberi address tersendiri. ØAddress decoder, data dan status register, dan control circuitry disebut sebagai rangkaian interface.

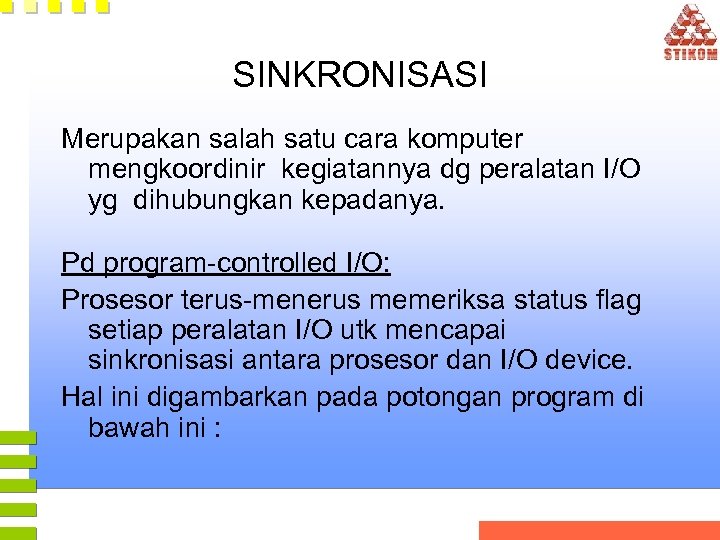

SINKRONISASI Merupakan salah satu cara komputer mengkoordinir kegiatannya dg peralatan I/O yg dihubungkan kepadanya. Pd program-controlled I/O: Prosesor terus-menerus memeriksa status flag setiap peralatan I/O utk mencapai sinkronisasi antara prosesor dan I/O device. Hal ini digambarkan pada potongan program di bawah ini :

SINKRONISASI Merupakan salah satu cara komputer mengkoordinir kegiatannya dg peralatan I/O yg dihubungkan kepadanya. Pd program-controlled I/O: Prosesor terus-menerus memeriksa status flag setiap peralatan I/O utk mencapai sinkronisasi antara prosesor dan I/O device. Hal ini digambarkan pada potongan program di bawah ini :

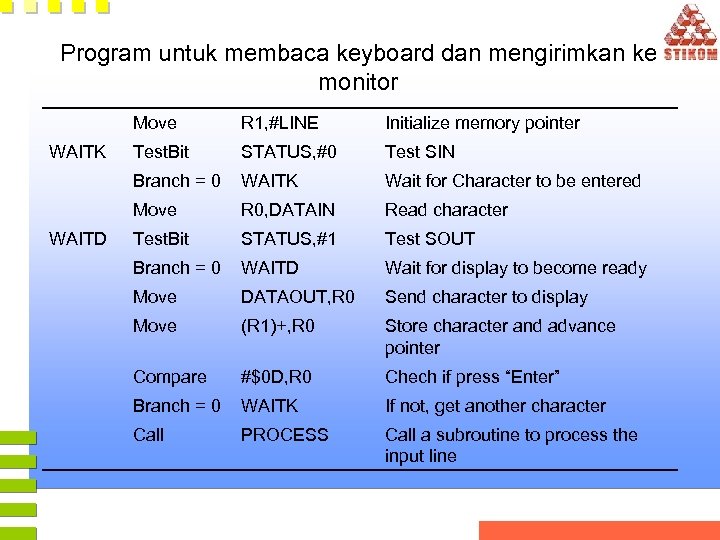

Program untuk membaca keyboard dan mengirimkan ke monitor Move Test. Bit STATUS, #0 Test SIN WAITK Wait for Character to be entered Move WAITD Initialize memory pointer Branch = 0 WAITK R 1, #LINE R 0, DATAIN Read character Test. Bit STATUS, #1 Test SOUT Branch = 0 WAITD Wait for display to become ready Move DATAOUT, R 0 Send character to display Move (R 1)+, R 0 Store character and advance pointer Compare #$0 D, R 0 Chech if press “Enter” Branch = 0 WAITK If not, get another character Call PROCESS Call a subroutine to process the input line

Program untuk membaca keyboard dan mengirimkan ke monitor Move Test. Bit STATUS, #0 Test SIN WAITK Wait for Character to be entered Move WAITD Initialize memory pointer Branch = 0 WAITK R 1, #LINE R 0, DATAIN Read character Test. Bit STATUS, #1 Test SOUT Branch = 0 WAITD Wait for display to become ready Move DATAOUT, R 0 Send character to display Move (R 1)+, R 0 Store character and advance pointer Compare #$0 D, R 0 Chech if press “Enter” Branch = 0 WAITK If not, get another character Call PROCESS Call a subroutine to process the input line

Terdapat 2 mekanisme lain yg umum digunakan utk mengimplementasikan operasi I/O: · Interrupts · Direct Memory Access

Terdapat 2 mekanisme lain yg umum digunakan utk mengimplementasikan operasi I/O: · Interrupts · Direct Memory Access

INTERRUPT Ø Digunakan untuk meningkatkan kinerja processor dalam penanganan peralatan I/O yang dimilikinya. Ø CPU tidak harus selalu mengecek status peralatan I/O Ø Bila terdapat peralatan I/O yang meminta pelayanan, maka peralatan tersebut akan mengirim sinyal interrupt kepada CPU. Sinyal interrupt ini disebut juga sebagai Interrupt Request (INTR) Ø Sinyal interrupt dikirim melalui jalur kontrol bus yang disebut interrupt request line.

INTERRUPT Ø Digunakan untuk meningkatkan kinerja processor dalam penanganan peralatan I/O yang dimilikinya. Ø CPU tidak harus selalu mengecek status peralatan I/O Ø Bila terdapat peralatan I/O yang meminta pelayanan, maka peralatan tersebut akan mengirim sinyal interrupt kepada CPU. Sinyal interrupt ini disebut juga sebagai Interrupt Request (INTR) Ø Sinyal interrupt dikirim melalui jalur kontrol bus yang disebut interrupt request line.

Processor akan merespon interrupt yang diterima dengan menghentikan proses yang sedang berjalan dan mengecek status peralatan I/O untuk mencari peralatan yang meminta interrupt. Selanjutnya processor akan menjalankan suatu program untuk merespon interrupt yang diterimanya. Program ini disebut sebagai interrupt-service routine (ISR). Berikut contoh processor dalam menjalankan ISR untuk merespon interrupt pencetakan ke printer :

Processor akan merespon interrupt yang diterima dengan menghentikan proses yang sedang berjalan dan mengecek status peralatan I/O untuk mencari peralatan yang meminta interrupt. Selanjutnya processor akan menjalankan suatu program untuk merespon interrupt yang diterimanya. Program ini disebut sebagai interrupt-service routine (ISR). Berikut contoh processor dalam menjalankan ISR untuk merespon interrupt pencetakan ke printer :

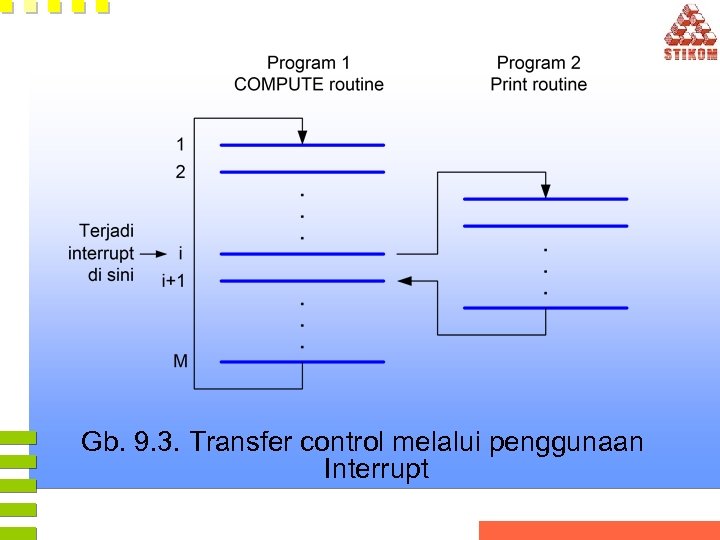

Gb. 9. 3. Transfer control melalui penggunaan Interrupt

Gb. 9. 3. Transfer control melalui penggunaan Interrupt

Keterangan gambar : Ø Saat processor menjalankan compute routine (perhitungan) pada langkah ke-i, processor menerima sinyal interrupt yang meminta proses pencetakan (print). Ø Setelah processor selesai melaksanakan instruksi ke-i processor menghentikan sementara eksekusi terhadap compute routine dan menyimpan hasil-hasil sementara proses tersebut ke register khusus (register stack).

Keterangan gambar : Ø Saat processor menjalankan compute routine (perhitungan) pada langkah ke-i, processor menerima sinyal interrupt yang meminta proses pencetakan (print). Ø Setelah processor selesai melaksanakan instruksi ke-i processor menghentikan sementara eksekusi terhadap compute routine dan menyimpan hasil-hasil sementara proses tersebut ke register khusus (register stack).

Ø Processor kemudian menjalankan print routine. Jika print routine selesai dilaksanakan, maka processor kembali ke program semula (compute routine) pada langkah ke-(i + 1) dengan mengambil informasi yang sebelumnya diimpan.

Ø Processor kemudian menjalankan print routine. Jika print routine selesai dilaksanakan, maka processor kembali ke program semula (compute routine) pada langkah ke-(i + 1) dengan mengambil informasi yang sebelumnya diimpan.

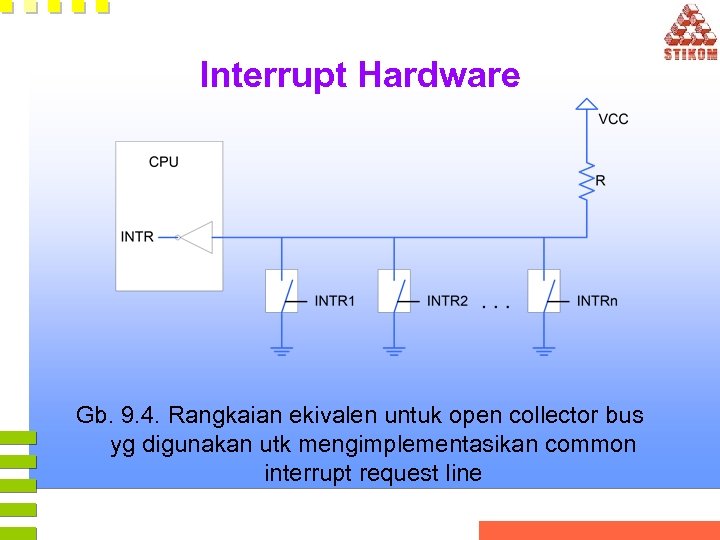

Interrupt Hardware Gb. 9. 4. Rangkaian ekivalen untuk open collector bus yg digunakan utk mengimplementasikan common interrupt request line

Interrupt Hardware Gb. 9. 4. Rangkaian ekivalen untuk open collector bus yg digunakan utk mengimplementasikan common interrupt request line

Gambar di atas merupakan gambar jalur interrupt dengan menggunakan singgle line. Jalur interrupt beberapa peralatan hanya dihubungkan dengan menggunakan satu jalur. Sehingga interrupt yang diterima processor adalah apabila ada satu atau lebih peralatan mengirimkan sinyal interrupt. Untuk mencari peralatan mana yang mengirimkan interrupt, processor memeriksa Ready Bit setiap peralatan dengan cara pooling.

Gambar di atas merupakan gambar jalur interrupt dengan menggunakan singgle line. Jalur interrupt beberapa peralatan hanya dihubungkan dengan menggunakan satu jalur. Sehingga interrupt yang diterima processor adalah apabila ada satu atau lebih peralatan mengirimkan sinyal interrupt. Untuk mencari peralatan mana yang mengirimkan interrupt, processor memeriksa Ready Bit setiap peralatan dengan cara pooling.

Kelemahan dari metode interrupt ini adalah adanya pooling oleh processor untuk mencari peralatan yang mengirimkan interrupt. Apabila terdapat beberapa peralatan yang mengirimkan interrupt secara bersamaan maka yang dilayani terlebih dahulu adalah peralatan yang terdekat dengan processor secara pengkabelan.

Kelemahan dari metode interrupt ini adalah adanya pooling oleh processor untuk mencari peralatan yang mengirimkan interrupt. Apabila terdapat beberapa peralatan yang mengirimkan interrupt secara bersamaan maka yang dilayani terlebih dahulu adalah peralatan yang terdekat dengan processor secara pengkabelan.

Catatan : Ø Pada saat peralatan I/O mengirimkan sinyal interrupt, processor akan menjawabnya dengan sinyal interrupt acknowledge (INTA). Sinyal ini mengindikasikan bahwa processor menerima interrupt tsb dan peralatan I/O dapat menghentikan sinyal interrupt-nya. Ø Terdapat tenggang waktu antara saat peralatan I/O mengirimkan sinyal interrupt sampai dilayani permintaan interrupt tsb (start ISR execution). Tenggang waktu ini disebut interrupt latency.

Catatan : Ø Pada saat peralatan I/O mengirimkan sinyal interrupt, processor akan menjawabnya dengan sinyal interrupt acknowledge (INTA). Sinyal ini mengindikasikan bahwa processor menerima interrupt tsb dan peralatan I/O dapat menghentikan sinyal interrupt-nya. Ø Terdapat tenggang waktu antara saat peralatan I/O mengirimkan sinyal interrupt sampai dilayani permintaan interrupt tsb (start ISR execution). Tenggang waktu ini disebut interrupt latency.

Enabling and Disabling Interrupt Tidak semua permintaan interrupt bisa dilayani oleh processor. Adakalanya saat processor menjalankan suatu program, program tersebut tidak boleh disela oleh proses lain. Atau bisa juga pada saat itu sedang dilayani suatu interrupt hingga tidak mungkin menerima interrupt lain. Untuk itu diperlukan fasilitas enable dan disable interrupt untuk mengindikasikan bisa tidaknya interrupt diterima.

Enabling and Disabling Interrupt Tidak semua permintaan interrupt bisa dilayani oleh processor. Adakalanya saat processor menjalankan suatu program, program tersebut tidak boleh disela oleh proses lain. Atau bisa juga pada saat itu sedang dilayani suatu interrupt hingga tidak mungkin menerima interrupt lain. Untuk itu diperlukan fasilitas enable dan disable interrupt untuk mengindikasikan bisa tidaknya interrupt diterima.

Cara enable dan disable interrupt : Ø Pada processor dilengkapi dengan interrupt mask. Yaitu salah satu bit pada register processor status (PS). Interrupt mask ini digunakan sebagai status interrupt, jika interrupt mask = 1, maka interrupt disable). Ø Pada ISR diberikan interrupt-disable instruction sebagai instruksi pertama dan interrupt-enable instruction sebagi instruksi terakhir pada program. Ø Untuk melakukan interrupt handling maka langkah-langkah yang terjadi adalah sbb (diasumsikan interrupt sedang enable) :

Cara enable dan disable interrupt : Ø Pada processor dilengkapi dengan interrupt mask. Yaitu salah satu bit pada register processor status (PS). Interrupt mask ini digunakan sebagai status interrupt, jika interrupt mask = 1, maka interrupt disable). Ø Pada ISR diberikan interrupt-disable instruction sebagai instruksi pertama dan interrupt-enable instruction sebagi instruksi terakhir pada program. Ø Untuk melakukan interrupt handling maka langkah-langkah yang terjadi adalah sbb (diasumsikan interrupt sedang enable) :

1. Peralatan (I/O) mengirimkan sinyal interrupt request. 2. Processor menginterupsi program yang sedang dieksekusi. 3. Processor me-disable interrupt 4. Peralatan I/O diberitahu bahwa requestnya telah dikenali, dan peralatan tersebut merespon dengan menghentikan sinyal interrrupt requestnya. 5. Menjalankan interrupt service routine (ISR) yang berkaiatan dengan interrupt yang diminta. 6. Interrupt dienable dan prosessor melanjutkan eksekusi program sebelumnya.

1. Peralatan (I/O) mengirimkan sinyal interrupt request. 2. Processor menginterupsi program yang sedang dieksekusi. 3. Processor me-disable interrupt 4. Peralatan I/O diberitahu bahwa requestnya telah dikenali, dan peralatan tersebut merespon dengan menghentikan sinyal interrrupt requestnya. 5. Menjalankan interrupt service routine (ISR) yang berkaiatan dengan interrupt yang diminta. 6. Interrupt dienable dan prosessor melanjutkan eksekusi program sebelumnya.

Menangani Beberapa Peralatan Di sini dibicarakan penanganan jika terjadi permintaan interrupt oleh beberapa peralatan I/O, baik secara bersamaan atau pada saat yang lain sedang dieksekusi. Dalam hal ini ada beberapa persoalan yang perlu dipikirkan : 1. Bagaimana processor mengenali perangkat yang meminta interrupt.

Menangani Beberapa Peralatan Di sini dibicarakan penanganan jika terjadi permintaan interrupt oleh beberapa peralatan I/O, baik secara bersamaan atau pada saat yang lain sedang dieksekusi. Dalam hal ini ada beberapa persoalan yang perlu dipikirkan : 1. Bagaimana processor mengenali perangkat yang meminta interrupt.

2. Misalkan terdapat beberapa perangkat meminta interrupt service routine yang berbeda, bagaimana processor dapat memperoleh alamat awal routine yang sesuai untuk setiap permintaan tersebut. 3. Apakah suatu perangkat diijinkan untuk menginterupsi prosessor pada saat interrupt lain dilayani? 4. Bagaimana dua atau lebih interrupt request ditangani?

2. Misalkan terdapat beberapa perangkat meminta interrupt service routine yang berbeda, bagaimana processor dapat memperoleh alamat awal routine yang sesuai untuk setiap permintaan tersebut. 3. Apakah suatu perangkat diijinkan untuk menginterupsi prosessor pada saat interrupt lain dilayani? 4. Bagaimana dua atau lebih interrupt request ditangani?

Pada saat suatu request diterima, diperlukan informasi tambahan untuk mengindentifikasi perangkat tertentu yang mengaktifkan jalur tersebut. Jika yang mengaktifkan jalur tersebut lebih dari satu, maka perlu dilakukan pemilahan dan pemilihan satu diantara beberapa request. Informasi yang diperlukan untuk menentukan apakah suatu perangkat meminta interrupt disediakan dalam status register. Misalkan bit KIRQ untuk keyboard dan DIRQ untuk display. Gambar register status interface keyboard dan memory

Pada saat suatu request diterima, diperlukan informasi tambahan untuk mengindentifikasi perangkat tertentu yang mengaktifkan jalur tersebut. Jika yang mengaktifkan jalur tersebut lebih dari satu, maka perlu dilakukan pemilahan dan pemilihan satu diantara beberapa request. Informasi yang diperlukan untuk menentukan apakah suatu perangkat meminta interrupt disediakan dalam status register. Misalkan bit KIRQ untuk keyboard dan DIRQ untuk display. Gambar register status interface keyboard dan memory

Selanjutnya untuk mengenali peralatan yang meng -interrupt adalah dengan mempolling semua peralatan yang terhubung. Skema polling mudah diimplementasikan tetapi waktu yang dihabiskan untuk proses ini cukup memakan waktu.

Selanjutnya untuk mengenali peralatan yang meng -interrupt adalah dengan mempolling semua peralatan yang terhubung. Skema polling mudah diimplementasikan tetapi waktu yang dihabiskan untuk proses ini cukup memakan waktu.

Vectored Interrupt Untuk mengatasi kelemahan metode interrupt di atas digunakan metode vectored interrupt. Peralatan yang meminta interrupt menyertakan kode khusus yang merupakan identitas dari peralatan tersebut. Sehingga proscessor langsung dapat mengenali peralatan yang mengirimkan interrupt. Kode ini dapat berupa alamat dari peralatan pengirim.

Vectored Interrupt Untuk mengatasi kelemahan metode interrupt di atas digunakan metode vectored interrupt. Peralatan yang meminta interrupt menyertakan kode khusus yang merupakan identitas dari peralatan tersebut. Sehingga proscessor langsung dapat mengenali peralatan yang mengirimkan interrupt. Kode ini dapat berupa alamat dari peralatan pengirim.

Untuk menjalankan proses interupt vektor ini awalnya peralatan I/O mengirim sinyal interrupt request (INTR) pada prosessor. Selanjutnya jika prosessor siap untuk melayani permintaan, maka prosessor mengirim sinyal interrupt acknowledge (INTA) untuk merespon IR dari peralatan I/O. Setelah I/O menerima sinyal INTA, peralatan. I/O mematikan sinyal INTR dan mengirimkan data interrupt vektor. Umumnya perangkat I/O mengirim kode interrupt vektor melalui bus data, menggunakan sinyal kontrol bus untuk memastikan bahwa perangkat tidak saling mempengaruhi.

Untuk menjalankan proses interupt vektor ini awalnya peralatan I/O mengirim sinyal interrupt request (INTR) pada prosessor. Selanjutnya jika prosessor siap untuk melayani permintaan, maka prosessor mengirim sinyal interrupt acknowledge (INTA) untuk merespon IR dari peralatan I/O. Setelah I/O menerima sinyal INTA, peralatan. I/O mematikan sinyal INTR dan mengirimkan data interrupt vektor. Umumnya perangkat I/O mengirim kode interrupt vektor melalui bus data, menggunakan sinyal kontrol bus untuk memastikan bahwa perangkat tidak saling mempengaruhi.

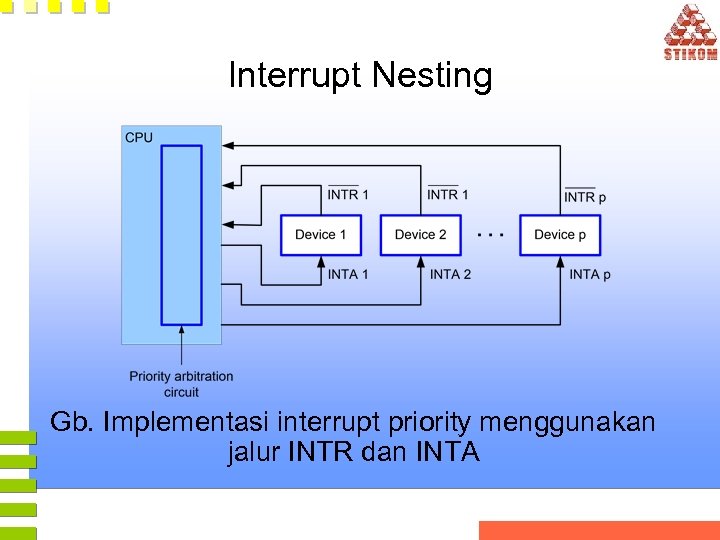

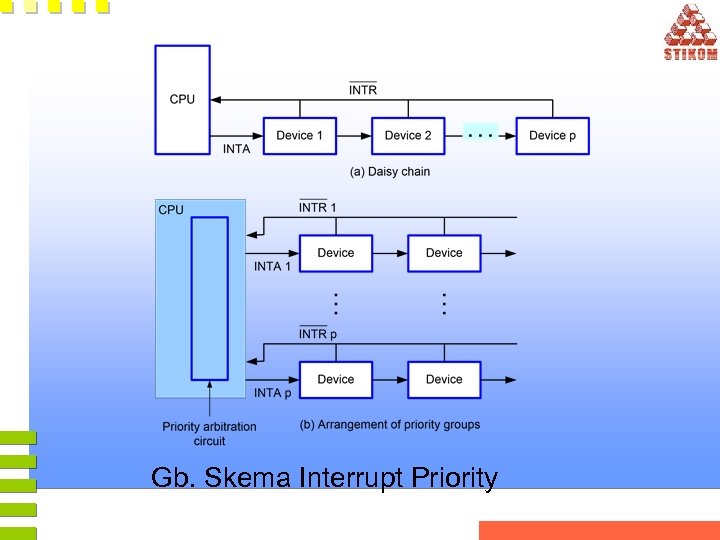

Interrupt Nesting Gb. Implementasi interrupt priority menggunakan jalur INTR dan INTA

Interrupt Nesting Gb. Implementasi interrupt priority menggunakan jalur INTR dan INTA

Dengan menggunakan gambar rangkaian di atas, dimungkinkan untuk menerima beberapa interrupt secara bersamaan atau menerima interrupt pada saat processor menjalankan interrupt yang lain. Penerimaan interrupt berdasarkan prioritas yang telah diberikan oleh rangkaian Priority Arbitration. Peralatan yang memiliki prioritas lebih tinggi harus diutamakan meskipun processor sedang memproses interrupt peralatan lain. Sedang peralatan yang memiliki prioritas lebih rendah tidak dapat menghentikan proses interrupt oleh peralatan yang memiliki prioritas lebih tinggi.

Dengan menggunakan gambar rangkaian di atas, dimungkinkan untuk menerima beberapa interrupt secara bersamaan atau menerima interrupt pada saat processor menjalankan interrupt yang lain. Penerimaan interrupt berdasarkan prioritas yang telah diberikan oleh rangkaian Priority Arbitration. Peralatan yang memiliki prioritas lebih tinggi harus diutamakan meskipun processor sedang memproses interrupt peralatan lain. Sedang peralatan yang memiliki prioritas lebih rendah tidak dapat menghentikan proses interrupt oleh peralatan yang memiliki prioritas lebih tinggi.

Simultaneus Request Permintaan beberapa interrupt secara bersamaan dapat diatasi dengan penggunaan priority arbitration circuit (PAC), tetapi jumlah peralatan yang bisa dipasang dibatasi oleh jumlah jalur yang dimiliki oleh PAC. Dan jumlah kabel yang diperlukan cukup banyak. Untuk menangani jumlah peralatan yang sangat banyak, biasanya penggunaan PAC dipadukan dengan metode daisy chain seperti yang digambarkan berikut ini.

Simultaneus Request Permintaan beberapa interrupt secara bersamaan dapat diatasi dengan penggunaan priority arbitration circuit (PAC), tetapi jumlah peralatan yang bisa dipasang dibatasi oleh jumlah jalur yang dimiliki oleh PAC. Dan jumlah kabel yang diperlukan cukup banyak. Untuk menangani jumlah peralatan yang sangat banyak, biasanya penggunaan PAC dipadukan dengan metode daisy chain seperti yang digambarkan berikut ini.

Gb. Skema Interrupt Priority

Gb. Skema Interrupt Priority

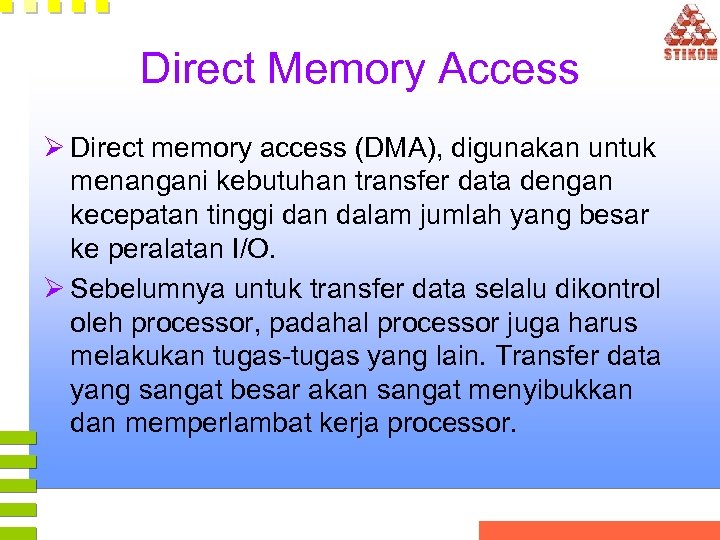

Direct Memory Access Ø Direct memory access (DMA), digunakan untuk menangani kebutuhan transfer data dengan kecepatan tinggi dan dalam jumlah yang besar ke peralatan I/O. Ø Sebelumnya untuk transfer data selalu dikontrol oleh processor, padahal processor juga harus melakukan tugas-tugas yang lain. Transfer data yang sangat besar akan sangat menyibukkan dan memperlambat kerja processor.

Direct Memory Access Ø Direct memory access (DMA), digunakan untuk menangani kebutuhan transfer data dengan kecepatan tinggi dan dalam jumlah yang besar ke peralatan I/O. Ø Sebelumnya untuk transfer data selalu dikontrol oleh processor, padahal processor juga harus melakukan tugas-tugas yang lain. Transfer data yang sangat besar akan sangat menyibukkan dan memperlambat kerja processor.

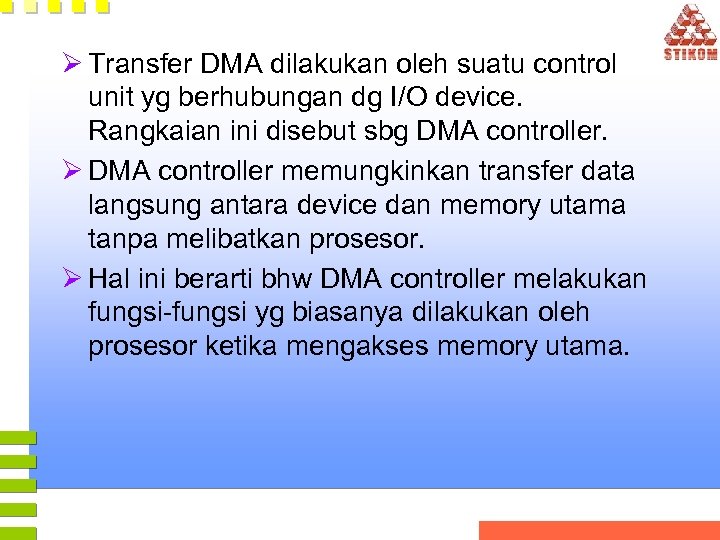

Ø Transfer DMA dilakukan oleh suatu control unit yg berhubungan dg I/O device. Rangkaian ini disebut sbg DMA controller. Ø DMA controller memungkinkan transfer data langsung antara device dan memory utama tanpa melibatkan prosesor. Ø Hal ini berarti bhw DMA controller melakukan fungsi-fungsi yg biasanya dilakukan oleh prosesor ketika mengakses memory utama.

Ø Transfer DMA dilakukan oleh suatu control unit yg berhubungan dg I/O device. Rangkaian ini disebut sbg DMA controller. Ø DMA controller memungkinkan transfer data langsung antara device dan memory utama tanpa melibatkan prosesor. Ø Hal ini berarti bhw DMA controller melakukan fungsi-fungsi yg biasanya dilakukan oleh prosesor ketika mengakses memory utama.

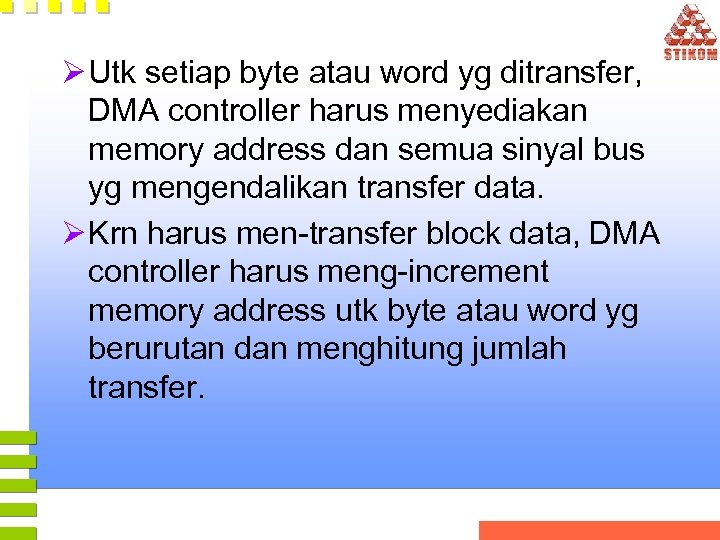

Ø Utk setiap byte atau word yg ditransfer, DMA controller harus menyediakan memory address dan semua sinyal bus yg mengendalikan transfer data. Ø Krn harus men-transfer block data, DMA controller harus meng-increment memory address utk byte atau word yg berurutan dan menghitung jumlah transfer.

Ø Utk setiap byte atau word yg ditransfer, DMA controller harus menyediakan memory address dan semua sinyal bus yg mengendalikan transfer data. Ø Krn harus men-transfer block data, DMA controller harus meng-increment memory address utk byte atau word yg berurutan dan menghitung jumlah transfer.

Ø Walaupun DMA controller dapat mentransfer data tanpa intervensi prosesor, operasinya harus di bawah kontrol suatu program yg di eksekusi oleh prossesor. Ø Untuk memulai transfer suatu blok word, prosesor mengirimkan data berikut ke controller: üAlamat awal data di memory yang akan ditransfer üJumlah word data dalam blok üArah transfer (read atau write).

Ø Walaupun DMA controller dapat mentransfer data tanpa intervensi prosesor, operasinya harus di bawah kontrol suatu program yg di eksekusi oleh prossesor. Ø Untuk memulai transfer suatu blok word, prosesor mengirimkan data berikut ke controller: üAlamat awal data di memory yang akan ditransfer üJumlah word data dalam blok üArah transfer (read atau write).

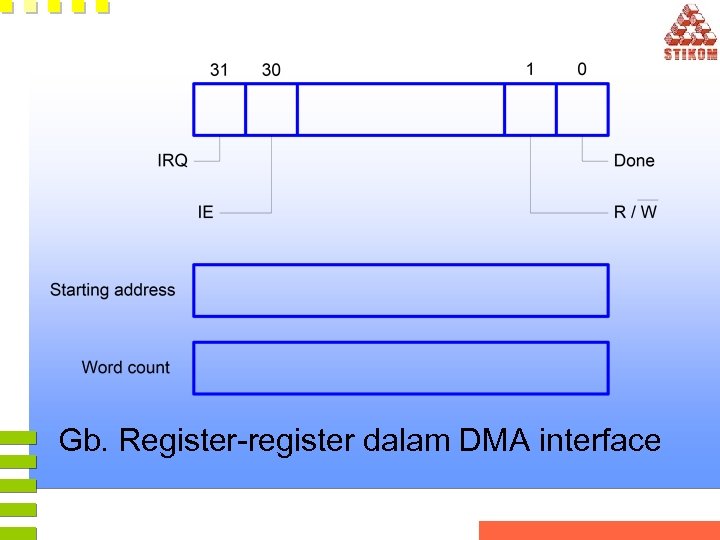

Ø Setelah menerima informasi tsb, DMA controller melanjutkan utk melakukan transfer yg diminta. Ø Setelah semua blok di-transfer, controller memberitahu prosesor dengan mengirimkan sinyal interrupt. Berikut gambar register yang ada pada DMA interface.

Ø Setelah menerima informasi tsb, DMA controller melanjutkan utk melakukan transfer yg diminta. Ø Setelah semua blok di-transfer, controller memberitahu prosesor dengan mengirimkan sinyal interrupt. Berikut gambar register yang ada pada DMA interface.

Gb. Register-register dalam DMA interface

Gb. Register-register dalam DMA interface

Ø Gambar di atas menunjukkan suatu contoh register-register dlm sebuah DMA controller yg dilihat oleh programmer. Ø Register-register ini di-akses dg cara yg sama dg semua I/O device interface yg lain. Dua register digunakan utk menyimpan alamat awal dan hitungan word. Ø Register yg ketiga mengandung status dan control flag.

Ø Gambar di atas menunjukkan suatu contoh register-register dlm sebuah DMA controller yg dilihat oleh programmer. Ø Register-register ini di-akses dg cara yg sama dg semua I/O device interface yg lain. Dua register digunakan utk menyimpan alamat awal dan hitungan word. Ø Register yg ketiga mengandung status dan control flag.

Ø Bit R/W menentukan arah transfer dan digunakan utk mengendalikan line yg berhubungan pd bus. Jika bit ini di set ke 1 oleh instruksi program, controller melakukan suatu operasi read, yaitu transfer data dilakukan dari memory ke I/O device. Jika tidak, maka dilakukan operasi write. Ø Ketika controller telah menyelesaikan transfer suatu blok data dan siap menerima command yg lain, flag Done di set menjadi 1.

Ø Bit R/W menentukan arah transfer dan digunakan utk mengendalikan line yg berhubungan pd bus. Jika bit ini di set ke 1 oleh instruksi program, controller melakukan suatu operasi read, yaitu transfer data dilakukan dari memory ke I/O device. Jika tidak, maka dilakukan operasi write. Ø Ketika controller telah menyelesaikan transfer suatu blok data dan siap menerima command yg lain, flag Done di set menjadi 1.

ØBit 30 adl Interrupt enable flag. Jika di set ke 1, flag ini menyebabkan controller membangkitkan interrupt setelah menyelesaikan transfer sebuah blok data. ØAkhirnya, controller men-set bit IRQ ke 1 ketika telah meminta interrupt.

ØBit 30 adl Interrupt enable flag. Jika di set ke 1, flag ini menyebabkan controller membangkitkan interrupt setelah menyelesaikan transfer sebuah blok data. ØAkhirnya, controller men-set bit IRQ ke 1 ketika telah meminta interrupt.

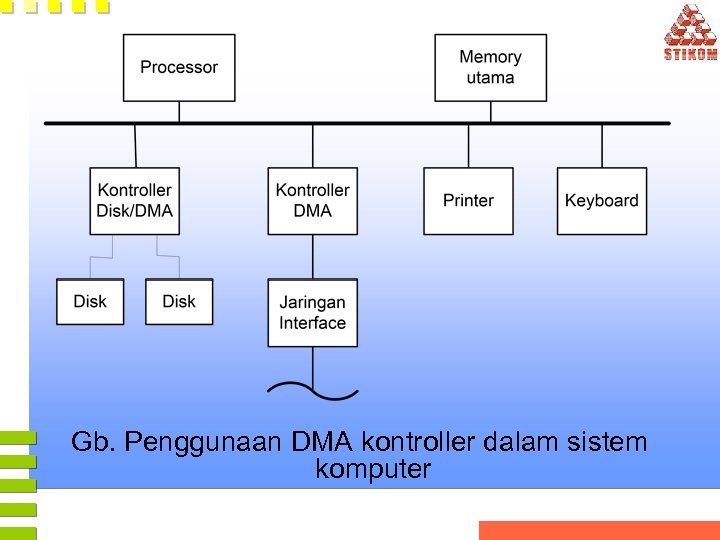

Gambar di bawah adalah contoh penggunaan kontroller DMA pada sistem komputer, yang terdiri dari : Kontroller DMA yang menghubungkan jaringan high speed ke bus komputer. Kontroller Disk/DMA yang mengontrol dua disk. Kontroller ini dapat melakukan dua operasi DMA mandiri.

Gambar di bawah adalah contoh penggunaan kontroller DMA pada sistem komputer, yang terdiri dari : Kontroller DMA yang menghubungkan jaringan high speed ke bus komputer. Kontroller Disk/DMA yang mengontrol dua disk. Kontroller ini dapat melakukan dua operasi DMA mandiri.

Gb. Penggunaan DMA kontroller dalam sistem komputer

Gb. Penggunaan DMA kontroller dalam sistem komputer

Ø Utk memulai transfer DMA suatu blok data, suatu program yg biasanya sebuah routine dlm sistem operasi, menulis informasi berikut ke register DMA channel yg ditugaskan ke printer: R Alamat memory R Hitungan word R Fungsi yg akan dilakukan (Read atau Write) Ø DMA controller kemudian melanjutkan sendiri utk mengimplementasikan fungsi yg ditentukan.

Ø Utk memulai transfer DMA suatu blok data, suatu program yg biasanya sebuah routine dlm sistem operasi, menulis informasi berikut ke register DMA channel yg ditugaskan ke printer: R Alamat memory R Hitungan word R Fungsi yg akan dilakukan (Read atau Write) Ø DMA controller kemudian melanjutkan sendiri utk mengimplementasikan fungsi yg ditentukan.

Ø Ketika transfer DMA telah selesai, hal ini disimpan dlm register status dan control dari DMA controller dg men-set bit Done. Ø Pd saat yg sama, jika bit IE di-set, controller mengirimkan suatu permintaan interrupt kpd prosesor dan men-set bit IRQ. Ø Register status juga dapat digunakan utk menyimpan informasi, spt apakah transfer berlangsung dg benar atau terjadi error. Ø Ketika transfer DMA berlangsung, program yg meminta transfer tidak dapat dilanjutkan. Tetapi prosesor dapat digunakan untuk meng -eksekusi program yg lain.

Ø Ketika transfer DMA telah selesai, hal ini disimpan dlm register status dan control dari DMA controller dg men-set bit Done. Ø Pd saat yg sama, jika bit IE di-set, controller mengirimkan suatu permintaan interrupt kpd prosesor dan men-set bit IRQ. Ø Register status juga dapat digunakan utk menyimpan informasi, spt apakah transfer berlangsung dg benar atau terjadi error. Ø Ketika transfer DMA berlangsung, program yg meminta transfer tidak dapat dilanjutkan. Tetapi prosesor dapat digunakan untuk meng -eksekusi program yg lain.

Bus Arbritration Konflik mungkin terjadi jika Prosesor dan DMA Controller mencoba untuk menggunakan bus pd saat yg sama dg akses ke memory utama. Krn beberapa DMA controller yg melayani I/O device yg berbeda dapat dihubungkan dg bus. Dlm hal ini, dua atau lebih controller mencoba utk menggunakan bus secara bersamaan.

Bus Arbritration Konflik mungkin terjadi jika Prosesor dan DMA Controller mencoba untuk menggunakan bus pd saat yg sama dg akses ke memory utama. Krn beberapa DMA controller yg melayani I/O device yg berbeda dapat dihubungkan dg bus. Dlm hal ini, dua atau lebih controller mencoba utk menggunakan bus secara bersamaan.

Utk mengatasi konflik ini, suatu rangkaian khusus yg disebut bus arbiter disediakan utk mengkoordinir kegiatan semua peralatan yg meminta transfer memory. Berikut gambar pengaturan processor dengan bus arbiter circuitry.

Utk mengatasi konflik ini, suatu rangkaian khusus yg disebut bus arbiter disediakan utk mengkoordinir kegiatan semua peralatan yg meminta transfer memory. Berikut gambar pengaturan processor dengan bus arbiter circuitry.

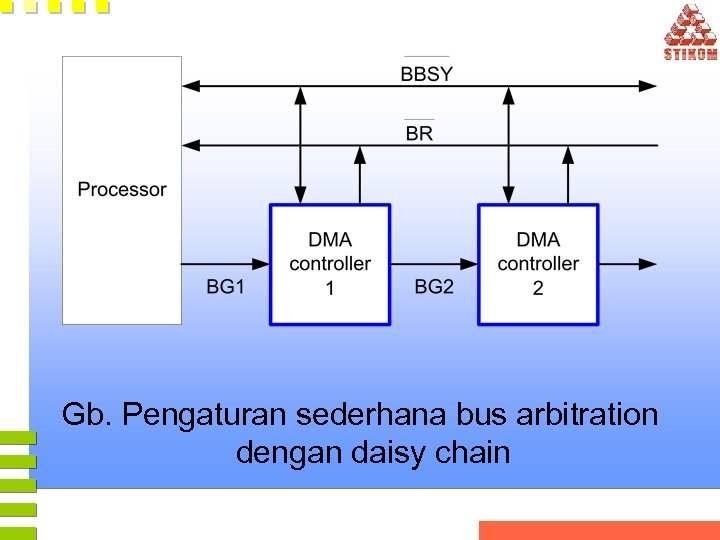

Gb. Pengaturan sederhana bus arbitration dengan daisy chain

Gb. Pengaturan sederhana bus arbitration dengan daisy chain

Cara kerja dari blok diagram di atas sama dengan blok diagram interrupt. Saat salah satu DMA controller memerlukan bus untuk transfer data, maka DMA controller tersebut mengirim sinyal Bus Request (BR) ke processor. Processor merespon dengan mengirimkan sinyal Bus Grant (BG) yang terhubung ke semua DMA controller secara daisy chain. Sinyal BG juga menjadi indikator bahwa bus data sedang tidak terpakai (free).

Cara kerja dari blok diagram di atas sama dengan blok diagram interrupt. Saat salah satu DMA controller memerlukan bus untuk transfer data, maka DMA controller tersebut mengirim sinyal Bus Request (BR) ke processor. Processor merespon dengan mengirimkan sinyal Bus Grant (BG) yang terhubung ke semua DMA controller secara daisy chain. Sinyal BG juga menjadi indikator bahwa bus data sedang tidak terpakai (free).

Sinyal BG ini akan diterima oleh DMA 1, apabila DMA 1 meminta request maka sinyal ini tidak diteruskan ke DMA controller yang lain. Tetapi bila tidak sinyal BG akan diteruskan ke DMA 2, begitu seterusnya. Kemudian DMA yang meminta request mengirimkan sinyal Bussy (BBSY) kepada processor dan DMA controller yang lain agar tidak ada yang memakai data bus kecuali DMA tersebut. Maka saat itu DMA yang meminta request dapat mentransfer data yang diperlukan, dan setelah selesai maka DMA tersebut menonaktifkan BBSY untuk memberitahukan bahwa data bus telah free.

Sinyal BG ini akan diterima oleh DMA 1, apabila DMA 1 meminta request maka sinyal ini tidak diteruskan ke DMA controller yang lain. Tetapi bila tidak sinyal BG akan diteruskan ke DMA 2, begitu seterusnya. Kemudian DMA yang meminta request mengirimkan sinyal Bussy (BBSY) kepada processor dan DMA controller yang lain agar tidak ada yang memakai data bus kecuali DMA tersebut. Maka saat itu DMA yang meminta request dapat mentransfer data yang diperlukan, dan setelah selesai maka DMA tersebut menonaktifkan BBSY untuk memberitahukan bahwa data bus telah free.

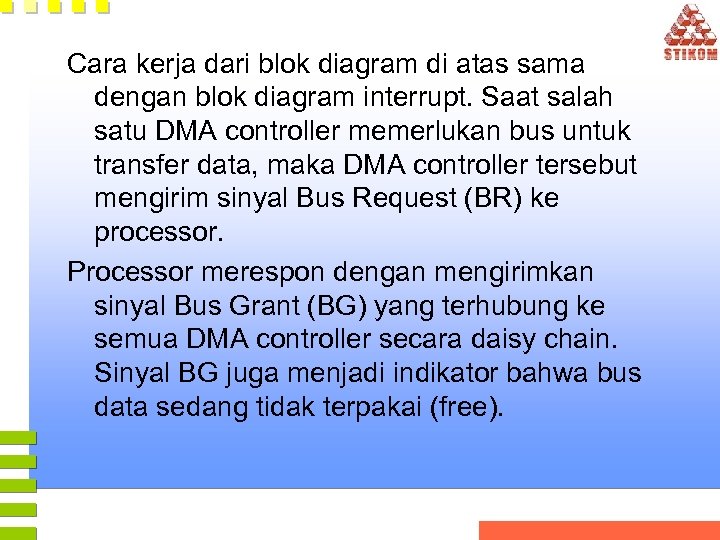

Gb. Rangkaian sinyal dalam transfer bus mastership

Gb. Rangkaian sinyal dalam transfer bus mastership

Gambar di atas menggambarkan saat kontroler DMA 2 me-request dan mendapatkan bus mastership dan kemudian melepaskannya. Selama menjadi bus master, kontroller tersebut dapat melakukan satu atau dua operasi transfer data

Gambar di atas menggambarkan saat kontroler DMA 2 me-request dan mendapatkan bus mastership dan kemudian melepaskannya. Selama menjadi bus master, kontroller tersebut dapat melakukan satu atau dua operasi transfer data

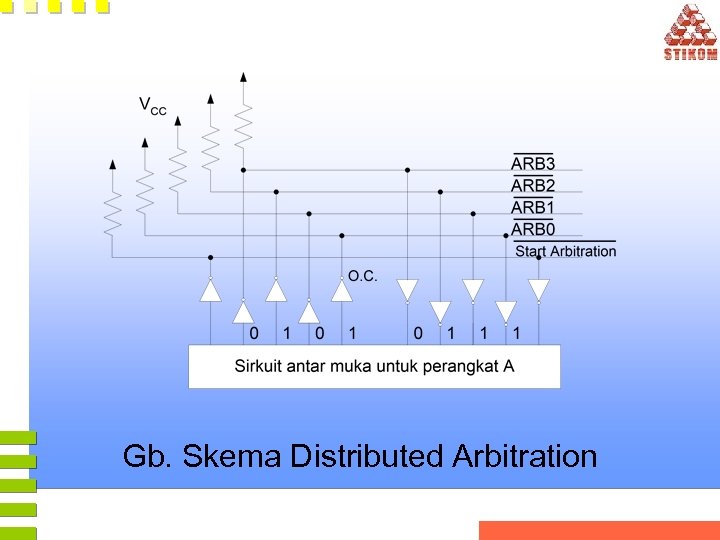

Distributed Arbitration Distributed arbitration berarti semua perangkat yang menunggu untuk menggunakan bus, memiliki tanggung jawab yang sama dalam melaksanakan proses arbitrasi, tanpa menggunakan arbiter pusat. Skema distributed arbitration digambarkan di bawah ini :

Distributed Arbitration Distributed arbitration berarti semua perangkat yang menunggu untuk menggunakan bus, memiliki tanggung jawab yang sama dalam melaksanakan proses arbitrasi, tanpa menggunakan arbiter pusat. Skema distributed arbitration digambarkan di bawah ini :

Gb. Skema Distributed Arbitration

Gb. Skema Distributed Arbitration

Dengan menggunakan skema di atas, tiap perangkat pada bus tersebut diidentifikasi dengan bilangan 4 -bit. Saat satu atau lebih perangkat merequest bus tersebut, perangkat tersebut menyatakan sinyal Start-Arbitration dan meletakkan nomor ID 4 -bitnya pada empat jalur open-collector. Pemenangnya di pilih berdasarkan nomor ID tertinggi. Dengan jalur tipe open-collector, berlaku fungsi logika OR dengan logika 1 sebagai pemenang.

Dengan menggunakan skema di atas, tiap perangkat pada bus tersebut diidentifikasi dengan bilangan 4 -bit. Saat satu atau lebih perangkat merequest bus tersebut, perangkat tersebut menyatakan sinyal Start-Arbitration dan meletakkan nomor ID 4 -bitnya pada empat jalur open-collector. Pemenangnya di pilih berdasarkan nomor ID tertinggi. Dengan jalur tipe open-collector, berlaku fungsi logika OR dengan logika 1 sebagai pemenang.

Untuk lebih jelasnya kita coba analisa kasus berikut : Ø Misal dua perangkat A dan B, memiliki nomor ID 5 dan 6 (0101 dan 0110). Jika kedua kode ini masuk pada bus dan dibaca, maka pada logika OR, ID ini akan terbaca oleh kedua parangkat sebagai 0111. Ø Maka perangkat A dan B akan membandingkan kode pada jalur arbritasi tersebut dengan kode IDnya masing-masing, dimulai dari most significant bit. Ø Jika dideteksi terdapat perbedaan pada posisi manapun, maka perangkat tersebut mendisable drivernya. Ø Maka saat A mendetaksi jalur ARB 1, mengakibatkan A mendisable drivernya, sehingga B menjadi pemenangnya.

Untuk lebih jelasnya kita coba analisa kasus berikut : Ø Misal dua perangkat A dan B, memiliki nomor ID 5 dan 6 (0101 dan 0110). Jika kedua kode ini masuk pada bus dan dibaca, maka pada logika OR, ID ini akan terbaca oleh kedua parangkat sebagai 0111. Ø Maka perangkat A dan B akan membandingkan kode pada jalur arbritasi tersebut dengan kode IDnya masing-masing, dimulai dari most significant bit. Ø Jika dideteksi terdapat perbedaan pada posisi manapun, maka perangkat tersebut mendisable drivernya. Ø Maka saat A mendetaksi jalur ARB 1, mengakibatkan A mendisable drivernya, sehingga B menjadi pemenangnya.

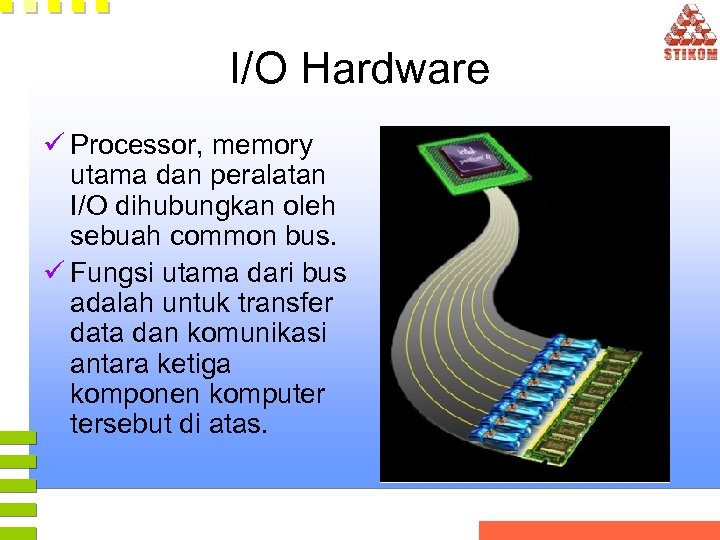

I/O Hardware ü Processor, memory utama dan peralatan I/O dihubungkan oleh sebuah common bus. ü Fungsi utama dari bus adalah untuk transfer data dan komunikasi antara ketiga komponen komputer tersebut di atas.

I/O Hardware ü Processor, memory utama dan peralatan I/O dihubungkan oleh sebuah common bus. ü Fungsi utama dari bus adalah untuk transfer data dan komunikasi antara ketiga komponen komputer tersebut di atas.

Processor Bus ü Sebuah bus terdiri dari tiga set jalur, yaitu jalur data, alamat dan kontrol. ü Sinyal kontrol untuk transfer data terdiri dari dua informasi, yaitu : jenis transfer dan timing. ü Jenis transfer data adalah berupa informasi read atau write data. Jika transfer data dalam ukuran besar juga disertakan ukuran data dalam byte, word atau long word.

Processor Bus ü Sebuah bus terdiri dari tiga set jalur, yaitu jalur data, alamat dan kontrol. ü Sinyal kontrol untuk transfer data terdiri dari dua informasi, yaitu : jenis transfer dan timing. ü Jenis transfer data adalah berupa informasi read atau write data. Jika transfer data dalam ukuran besar juga disertakan ukuran data dalam byte, word atau long word.

ü Informasi sinyal timing berupa sinyal waktu bagaimana processor dan peralatan I/O meletakkan dan mengambil data, ke dan dari bus. q Synchronous Bus Pada synchronous bus , seluruh peralatan komputer mendapatkan informasi timing dari sebuah common clock. Jarak waktu antar pulsa ON disebut sebagai time interval, dan setiap time interval merupakan sebuah bus cycle yang merupakan waktu dimana data yang akan ditransfer dapat diletakkan.

ü Informasi sinyal timing berupa sinyal waktu bagaimana processor dan peralatan I/O meletakkan dan mengambil data, ke dan dari bus. q Synchronous Bus Pada synchronous bus , seluruh peralatan komputer mendapatkan informasi timing dari sebuah common clock. Jarak waktu antar pulsa ON disebut sebagai time interval, dan setiap time interval merupakan sebuah bus cycle yang merupakan waktu dimana data yang akan ditransfer dapat diletakkan.

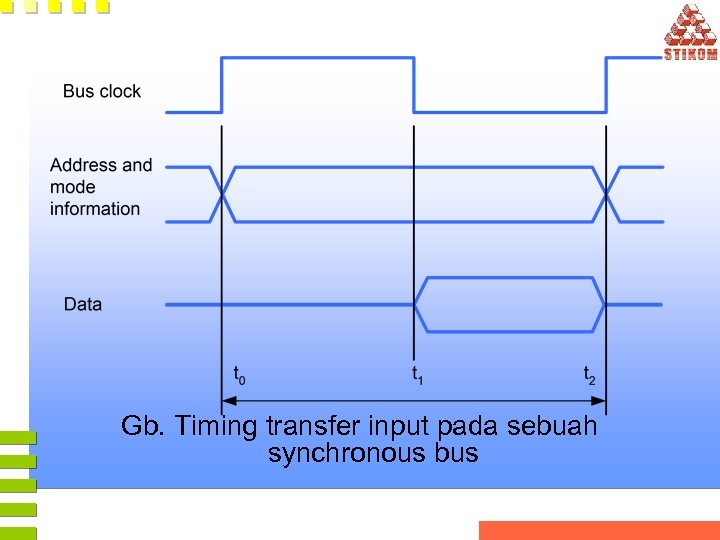

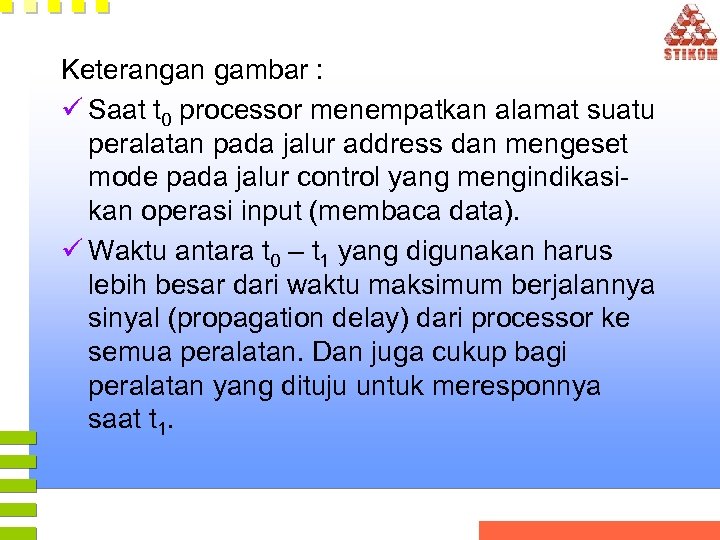

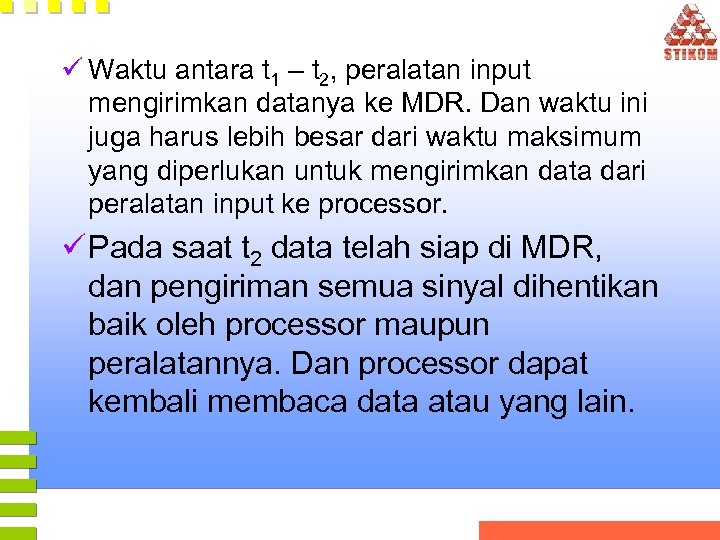

Gb. Timing transfer input pada sebuah synchronous bus

Gb. Timing transfer input pada sebuah synchronous bus

Keterangan gambar : ü Saat t 0 processor menempatkan alamat suatu peralatan pada jalur address dan mengeset mode pada jalur control yang mengindikasikan operasi input (membaca data). ü Waktu antara t 0 – t 1 yang digunakan harus lebih besar dari waktu maksimum berjalannya sinyal (propagation delay) dari processor ke semua peralatan. Dan juga cukup bagi peralatan yang dituju untuk meresponnya saat t 1.

Keterangan gambar : ü Saat t 0 processor menempatkan alamat suatu peralatan pada jalur address dan mengeset mode pada jalur control yang mengindikasikan operasi input (membaca data). ü Waktu antara t 0 – t 1 yang digunakan harus lebih besar dari waktu maksimum berjalannya sinyal (propagation delay) dari processor ke semua peralatan. Dan juga cukup bagi peralatan yang dituju untuk meresponnya saat t 1.

ü Waktu antara t 1 – t 2, peralatan input mengirimkan datanya ke MDR. Dan waktu ini juga harus lebih besar dari waktu maksimum yang diperlukan untuk mengirimkan data dari peralatan input ke processor. ü Pada saat t 2 data telah siap di MDR, dan pengiriman semua sinyal dihentikan baik oleh processor maupun peralatannya. Dan processor dapat kembali membaca data atau yang lain.

ü Waktu antara t 1 – t 2, peralatan input mengirimkan datanya ke MDR. Dan waktu ini juga harus lebih besar dari waktu maksimum yang diperlukan untuk mengirimkan data dari peralatan input ke processor. ü Pada saat t 2 data telah siap di MDR, dan pengiriman semua sinyal dihentikan baik oleh processor maupun peralatannya. Dan processor dapat kembali membaca data atau yang lain.

Bagan dari sychronous bus sangat sederhana juga dalam desain interfacenya. Tetapi panjang clock yang digunakan harus diatur untuk mengakomodasi peralatan yang berkecepatan rendah dan mempunyai delay terlama. Apabila waktu yang digunakan lebih cepat atau terjadi error pengiriman data sedang waktu telah habis, maka akan terjadi kesalahan dalam pengiriman data.

Bagan dari sychronous bus sangat sederhana juga dalam desain interfacenya. Tetapi panjang clock yang digunakan harus diatur untuk mengakomodasi peralatan yang berkecepatan rendah dan mempunyai delay terlama. Apabila waktu yang digunakan lebih cepat atau terjadi error pengiriman data sedang waktu telah habis, maka akan terjadi kesalahan dalam pengiriman data.

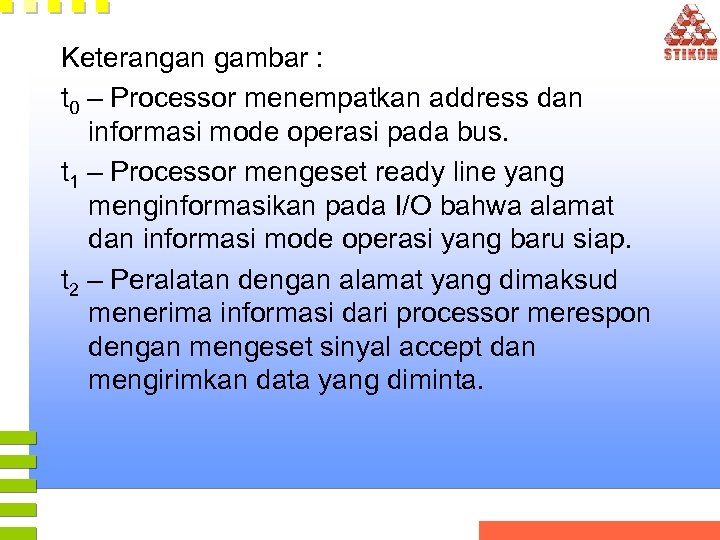

q. Asynchronous Bus Ø Merupakan cara lain pengiriman data. Clock yang digunakan antara processor dan peralatan yang digunakan berbeda. Agar tidak terjadi miscomunication digunakan sinyal ready dan accept sebagai pengganti sinyal clock. Ø Digunakan handshake protocol untuk proses pengiriman data sbb:

q. Asynchronous Bus Ø Merupakan cara lain pengiriman data. Clock yang digunakan antara processor dan peralatan yang digunakan berbeda. Agar tidak terjadi miscomunication digunakan sinyal ready dan accept sebagai pengganti sinyal clock. Ø Digunakan handshake protocol untuk proses pengiriman data sbb:

ü Processor akan megirimkan sinyal address dan mode operasi yang diinginkan. Disusul kemudian dikirimkan sinyal ready ke semua peralatan. ü Peralatan yang mempunyai alamat sesuai dengan yang dikirimkan akan merespon dengan mengirimkan sinyal accept dan data yang diminta. Sesaat setelah sinyal accept dan datang pada processor, maka processor akan menghentikan sinyal ready dan kemudian sinyal address.

ü Processor akan megirimkan sinyal address dan mode operasi yang diinginkan. Disusul kemudian dikirimkan sinyal ready ke semua peralatan. ü Peralatan yang mempunyai alamat sesuai dengan yang dikirimkan akan merespon dengan mengirimkan sinyal accept dan data yang diminta. Sesaat setelah sinyal accept dan datang pada processor, maka processor akan menghentikan sinyal ready dan kemudian sinyal address.

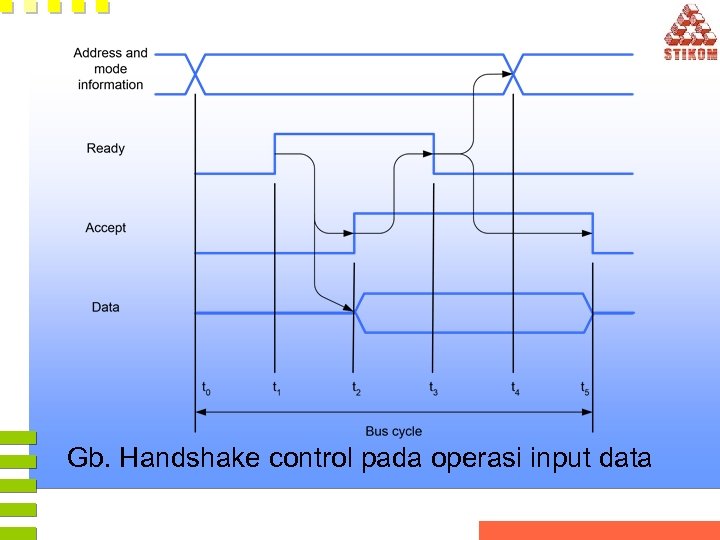

Gb. Handshake control pada operasi input data

Gb. Handshake control pada operasi input data

Keterangan gambar : t 0 – Processor menempatkan address dan informasi mode operasi pada bus. t 1 – Processor mengeset ready line yang menginformasikan pada I/O bahwa alamat dan informasi mode operasi yang baru siap. t 2 – Peralatan dengan alamat yang dimaksud menerima informasi dari processor merespon dengan mengeset sinyal accept dan mengirimkan data yang diminta.

Keterangan gambar : t 0 – Processor menempatkan address dan informasi mode operasi pada bus. t 1 – Processor mengeset ready line yang menginformasikan pada I/O bahwa alamat dan informasi mode operasi yang baru siap. t 2 – Peralatan dengan alamat yang dimaksud menerima informasi dari processor merespon dengan mengeset sinyal accept dan mengirimkan data yang diminta.

t 3 – Sinyal accept yang datang pada processor mengindikasikan bahwa data telah tersedia di bus. Setelah data diterima maka pada saat itu juga processor mereset sinyal ready. t 4 – Processor menghentikan pengiriman sinyal address dan mode, kemudian menggantinya dengan adreess dan mode yang baru jika diperlukan. t 5 – Ketika peralatan input menerima perubahan sinyal ready dari 1 ke 0, beberapa saat kemudian maka ia menghentikan pengiriman datanya dan mereset sinyal accept. Hal ini menandai selesainya proses input transfer

t 3 – Sinyal accept yang datang pada processor mengindikasikan bahwa data telah tersedia di bus. Setelah data diterima maka pada saat itu juga processor mereset sinyal ready. t 4 – Processor menghentikan pengiriman sinyal address dan mode, kemudian menggantinya dengan adreess dan mode yang baru jika diperlukan. t 5 – Ketika peralatan input menerima perubahan sinyal ready dari 1 ke 0, beberapa saat kemudian maka ia menghentikan pengiriman datanya dan mereset sinyal accept. Hal ini menandai selesainya proses input transfer

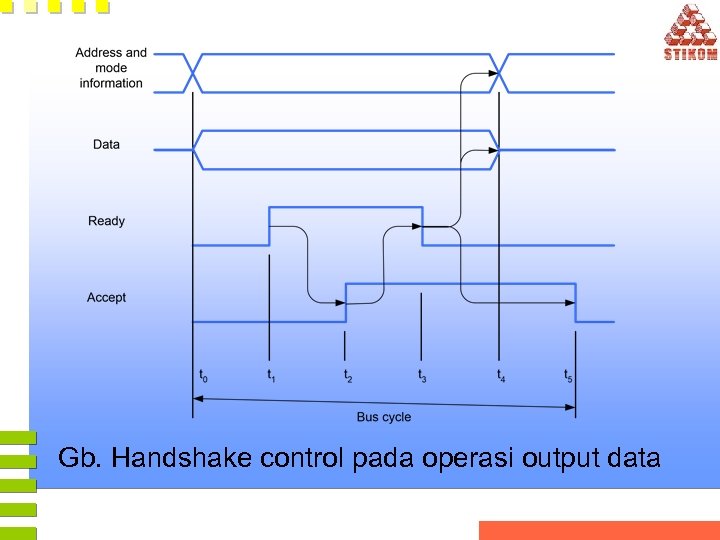

Gb. Handshake control pada operasi output data

Gb. Handshake control pada operasi output data