d2080ae4caf45046bc0681ea80aa4766.ppt

- Количество слайдов: 11

Оптимизация параметров микросхемы без изменения логического описания при технологических нормах 28 нм А. О. Власов ФГУ ФНЦ Научно-Исследовательский Институт Системных Исследований РАН Москва 2016

Содержание • • • Введение Выбор оптимального для проектирования набора стандартных ячеек CPU 28 нм Использование нескольких библиотек стандартных ячеек для оптимизации статической мощности Выбор комплекта блоков памяти Оптимальное использование наборов библиотечных элементов при проектировании CPU Заключение НИИСИ РАН 2

Введение • • • Проектные нормы 28 нм. Компромисс между быстродействием и потребляемой мощности Статическая мощность ~ 50% всей мощности Эффективное использование библиотечных элементов CPU (КОМДИВ 64) Design Compiler (Synopsys) и SOC Encounter (Cadence) НИИСИ РАН 3

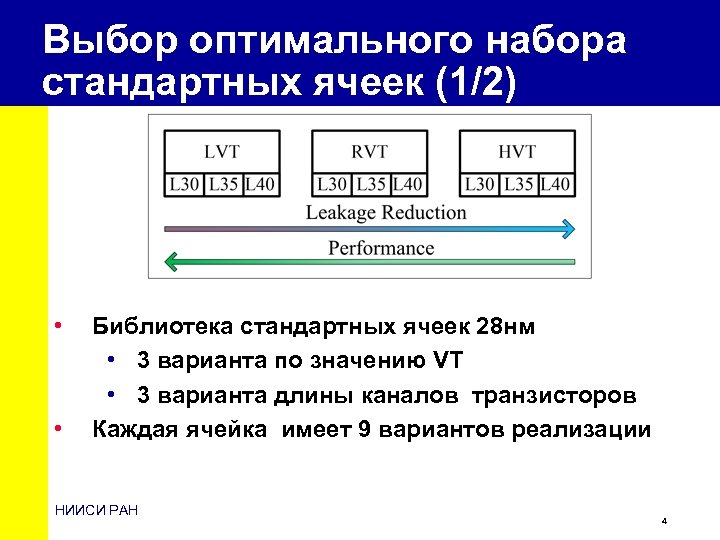

Выбор оптимального набора стандартных ячеек (1/2) • • Библиотека стандартных ячеек 28 нм • 3 варианта по значению VT • 3 варианта длины каналов транзисторов Каждая ячейка имеет 9 вариантов реализации НИИСИ РАН 4

Выбор оптимального набора стандартных ячеек (2/2) • • • Блок int_mult_div RVT L 35 – базовая имплементация Относительное изменение • Быстродействия • Статической мощности НИИСИ РАН 5

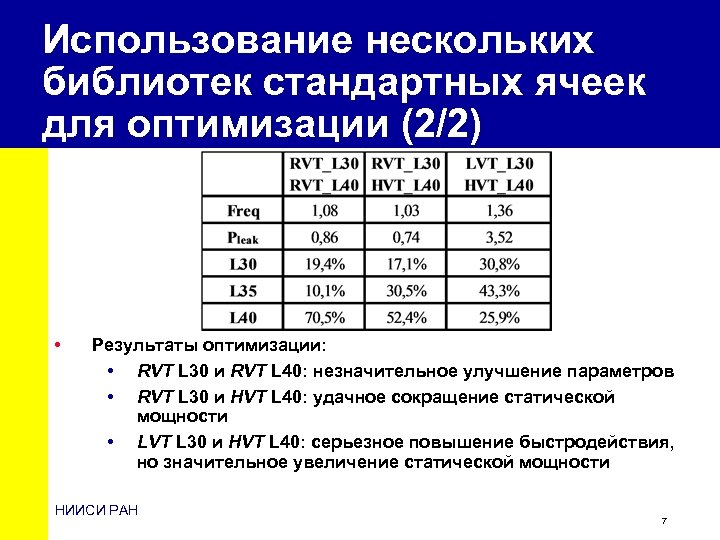

Использование нескольких библиотек стандартных ячеек для оптимизации (1/2) • • • Базовая имплементация RVT L 35 Критичные пути – более быстрые ячейки Некритичные пути – более «экономные» Варианты оптимизации: • RVT L 30 и RVT L 40 • RVT L 30 и HVT L 40 • LVT L 30 и HVT L 40 Больше библиотек – меньше эффективность, увеличение времени работы САПР НИИСИ РАН 6

Использование нескольких библиотек стандартных ячеек для оптимизации (2/2) • Результаты оптимизации: • RVT L 30 и RVT L 40: незначительное улучшение параметров • RVT L 30 и HVT L 40: удачное сокращение статической мощности • LVT L 30 и HVT L 40: серьезное повышение быстродействия, но значительное увеличение статической мощности НИИСИ РАН 7

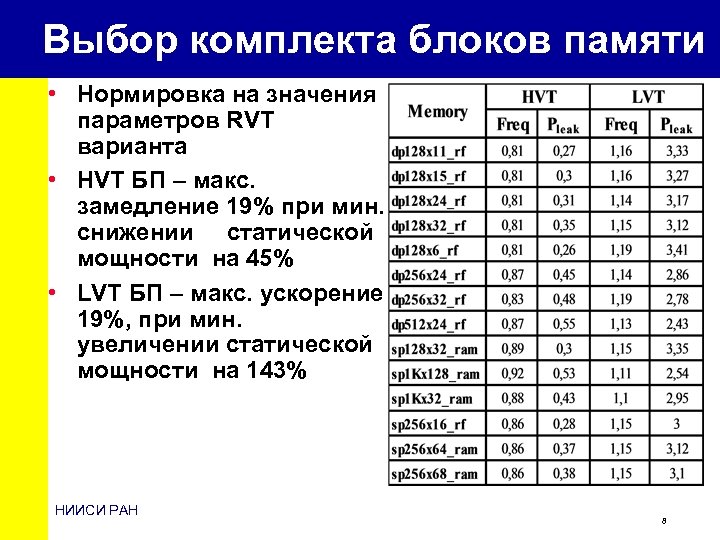

Выбор комплекта блоков памяти • Нормировка на значения параметров RVT варианта • HVT БП – макс. замедление 19% при мин. снижении статической мощности на 45% • LVT БП – макс. ускорение 19%, при мин. увеличении статической мощности на 143% НИИСИ РАН 8

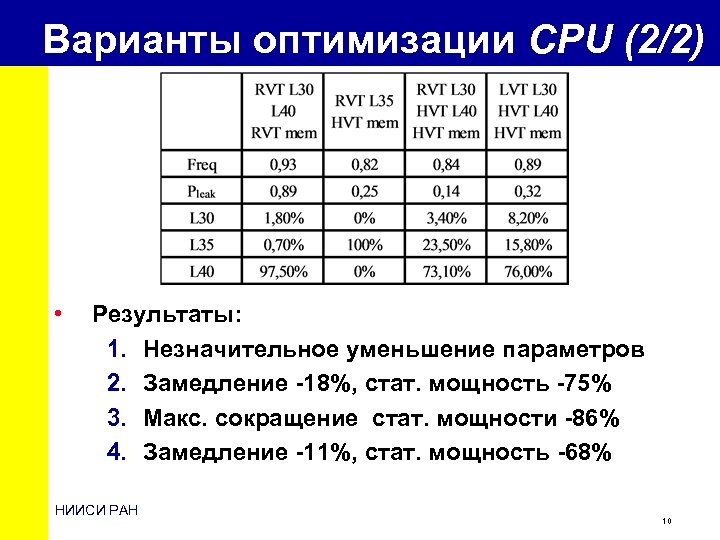

Варианты оптимизации CPU (1/2) • • Базовая реализация CPU: RVT L 35 стандартные ячейки и RVT блоки памяти (БП) Рассматриваемые оптимизации: • Оптимизация стандартными ячейками из библиотек RVT L 30 и RVT L 40 • Замена RVT БП на HVT БП и последующая оптимизация быстродействия • Замена RVT БП на HVT БП и оптимизация стандартными ячейками из библиотек RVT L 30 и HVT L 40 • Замена RVT БП на HVT БП и оптимизация стандартными ячейками из библиотек LVT L 30 и HVT L 40 НИИСИ РАН 9

Варианты оптимизации CPU (2/2) • Результаты: 1. Незначительное уменьшение параметров 2. Замедление -18%, стат. мощность -75% 3. Макс. сокращение стат. мощности -86% 4. Замедление -11%, стат. мощность -68% НИИСИ РАН 10

Заключение • • Рассмотрена взаимосвязь быстродействия и статической мощности с транзисторными опциями технологии TSMC 28 HPC Найденный набор библиотечных данных позволил снизить более чем в 7 раз статическую мощность с потерей производительности на 16%. НИИСИ РАН 11

d2080ae4caf45046bc0681ea80aa4766.ppt