Цифровая схемотехника 2013 Лекция 19 Memory In VHDL.ppt

- Количество слайдов: 46

Описание памяти с использованием VHDL

Описание памяти с использованием VHDL

Описание памяти как массива l l l Память – это массив векторов. Количество ячеек (векторов) определяет разрядность. Разрядность отдельного вектора = разрядность ячейки. 2

Описание памяти как массива l l l Память – это массив векторов. Количество ячеек (векторов) определяет разрядность. Разрядность отдельного вектора = разрядность ячейки. 2

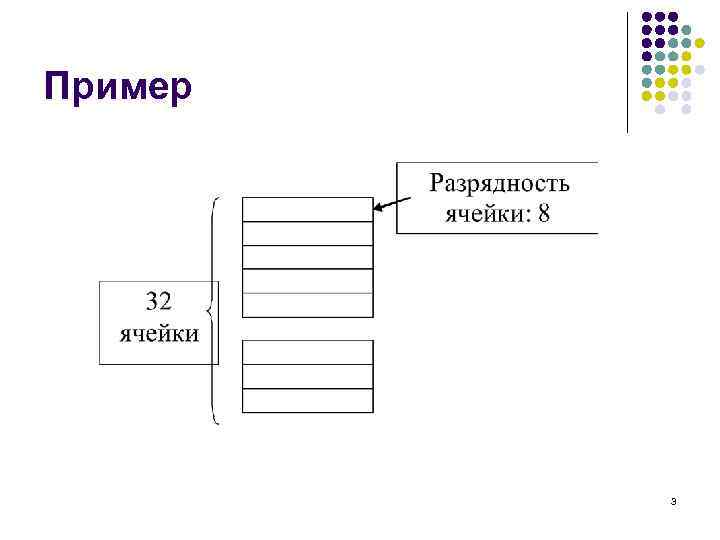

Пример 3

Пример 3

Объявление памяти l Описать тип l l type mem is array (0 to 31) of std_logic_vector (7 downto 0); Описать адресные входы и выходы данных. l l Тип данных для данных должен совпадать с типом данных для ячеек. Тип данных для адреса – integer или основанные на нем типы 4

Объявление памяти l Описать тип l l type mem is array (0 to 31) of std_logic_vector (7 downto 0); Описать адресные входы и выходы данных. l l Тип данных для данных должен совпадать с типом данных для ячеек. Тип данных для адреса – integer или основанные на нем типы 4

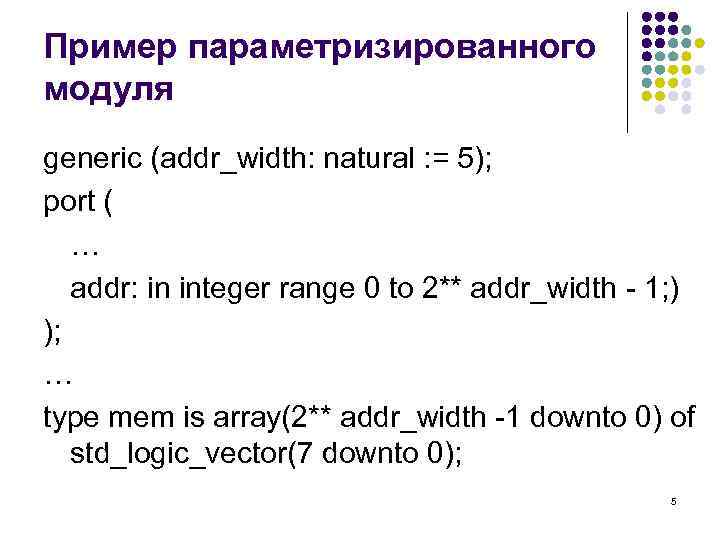

Пример параметризированного модуля generic (addr_width: natural : = 5); port ( … addr: in integer range 0 to 2** addr_width - 1; ) ); … type mem is array(2** addr_width -1 downto 0) of std_logic_vector(7 downto 0); 5

Пример параметризированного модуля generic (addr_width: natural : = 5); port ( … addr: in integer range 0 to 2** addr_width - 1; ) ); … type mem is array(2** addr_width -1 downto 0) of std_logic_vector(7 downto 0); 5

Преобразование типов numeric_std signed to_integer () signed () to_signed () std_logic_vector () std_logic_1164 std_logic_vector integer standart unsigned () to_integer () to_unsigned () std_logic_vector () unsigned numeric_std 6

Преобразование типов numeric_std signed to_integer () signed () to_signed () std_logic_vector () std_logic_1164 std_logic_vector integer standart unsigned () to_integer () to_unsigned () std_logic_vector () unsigned numeric_std 6

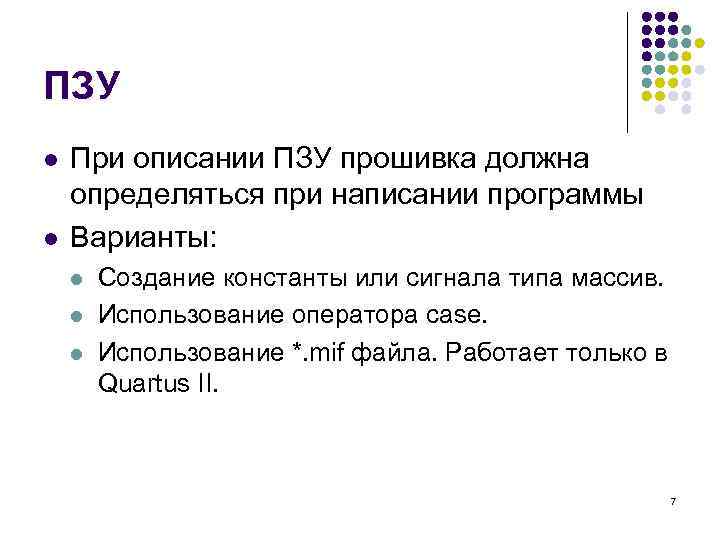

ПЗУ l l При описании ПЗУ прошивка должна определяться при написании программы Варианты: l l l Создание константы или сигнала типа массив. Использование оператора case. Использование *. mif файла. Работает только в Quartus II. 7

ПЗУ l l При описании ПЗУ прошивка должна определяться при написании программы Варианты: l l l Создание константы или сигнала типа массив. Использование оператора case. Использование *. mif файла. Работает только в Quartus II. 7

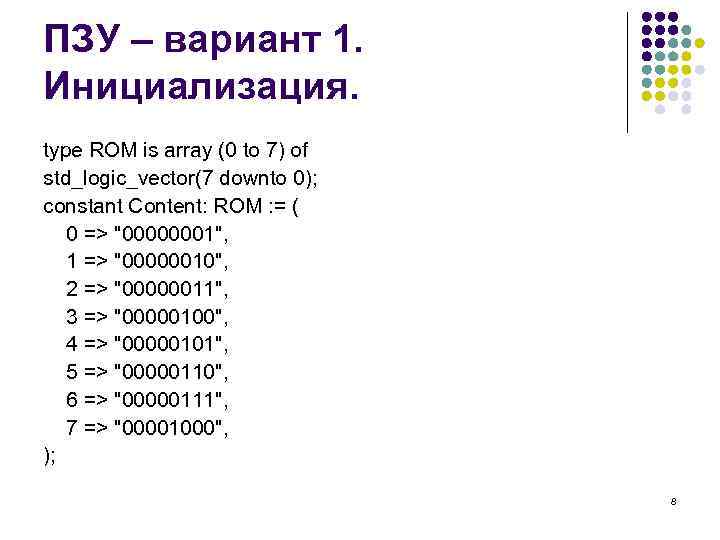

ПЗУ – вариант 1. Инициализация. type ROM is array (0 to 7) of std_logic_vector(7 downto 0); constant Content: ROM : = ( 0 => "00000001", 1 => "00000010", 2 => "00000011", 3 => "00000100", 4 => "00000101", 5 => "00000110", 6 => "00000111", 7 => "00001000", ); 8

ПЗУ – вариант 1. Инициализация. type ROM is array (0 to 7) of std_logic_vector(7 downto 0); constant Content: ROM : = ( 0 => "00000001", 1 => "00000010", 2 => "00000011", 3 => "00000100", 4 => "00000101", 5 => "00000110", 6 => "00000111", 7 => "00001000", ); 8

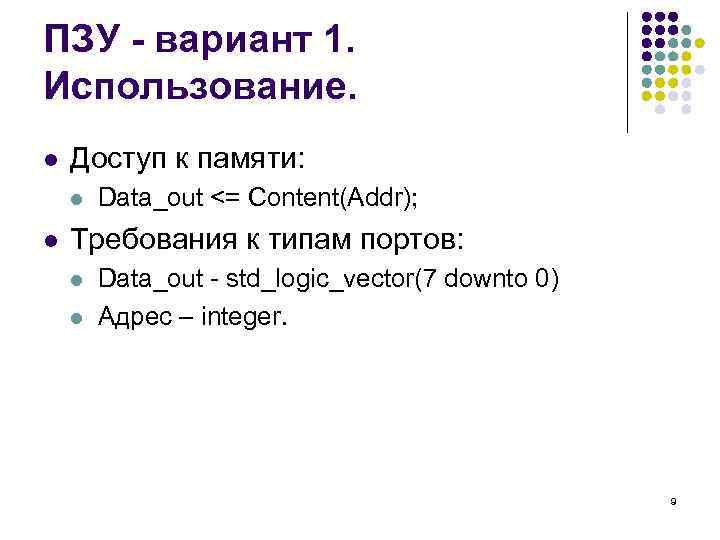

ПЗУ - вариант 1. Использование. l Доступ к памяти: l l Data_out <= Content(Addr); Требования к типам портов: l l Data_out - std_logic_vector(7 downto 0) Адрес – integer. 9

ПЗУ - вариант 1. Использование. l Доступ к памяти: l l Data_out <= Content(Addr); Требования к типам портов: l l Data_out - std_logic_vector(7 downto 0) Адрес – integer. 9

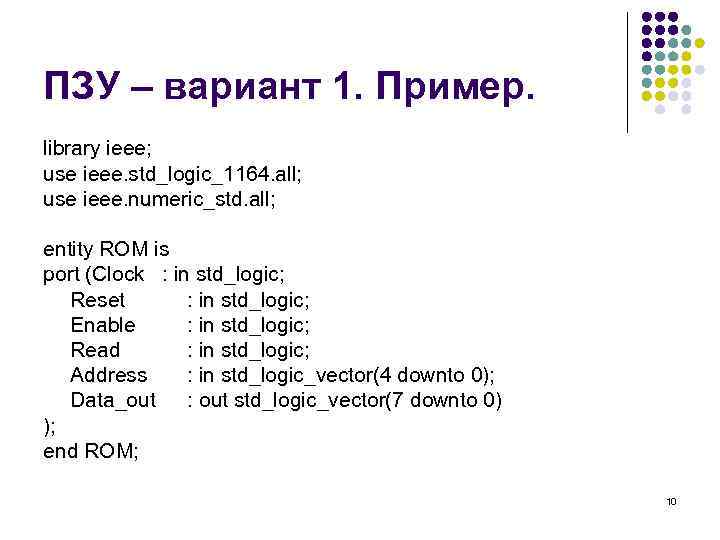

ПЗУ – вариант 1. Пример. library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity ROM is port (Clock : in std_logic; Reset : in std_logic; Enable : in std_logic; Read : in std_logic; Address : in std_logic_vector(4 downto 0); Data_out : out std_logic_vector(7 downto 0) ); end ROM; 10

ПЗУ – вариант 1. Пример. library ieee; use ieee. std_logic_1164. all; use ieee. numeric_std. all; entity ROM is port (Clock : in std_logic; Reset : in std_logic; Enable : in std_logic; Read : in std_logic; Address : in std_logic_vector(4 downto 0); Data_out : out std_logic_vector(7 downto 0) ); end ROM; 10

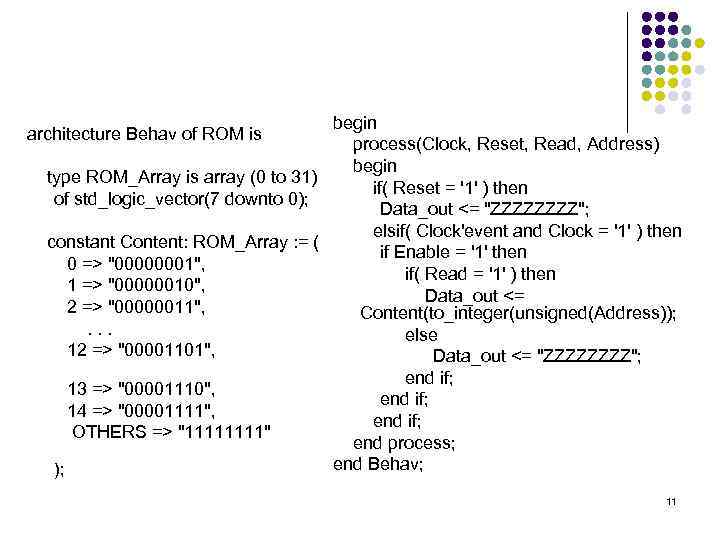

begin process(Clock, Reset, Read, Address) begin type ROM_Array is array (0 to 31) if( Reset = '1' ) then of std_logic_vector(7 downto 0); Data_out <= "ZZZZ"; elsif( Clock'event and Clock = '1' ) then constant Content: ROM_Array : = ( if Enable = '1' then 0 => "00000001", if( Read = '1' ) then 1 => "00000010", Data_out <= 2 => "00000011", Content(to_integer(unsigned(Address)); . . . else 12 => "00001101", Data_out <= "ZZZZ"; end if; 13 => "00001110", end if; 14 => "00001111", end if; OTHERS => "1111" end process; end Behav; ); architecture Behav of ROM is 11

begin process(Clock, Reset, Read, Address) begin type ROM_Array is array (0 to 31) if( Reset = '1' ) then of std_logic_vector(7 downto 0); Data_out <= "ZZZZ"; elsif( Clock'event and Clock = '1' ) then constant Content: ROM_Array : = ( if Enable = '1' then 0 => "00000001", if( Read = '1' ) then 1 => "00000010", Data_out <= 2 => "00000011", Content(to_integer(unsigned(Address)); . . . else 12 => "00001101", Data_out <= "ZZZZ"; end if; 13 => "00001110", end if; 14 => "00001111", end if; OTHERS => "1111" end process; end Behav; ); architecture Behav of ROM is 11

Результаты моделирования 12

Результаты моделирования 12

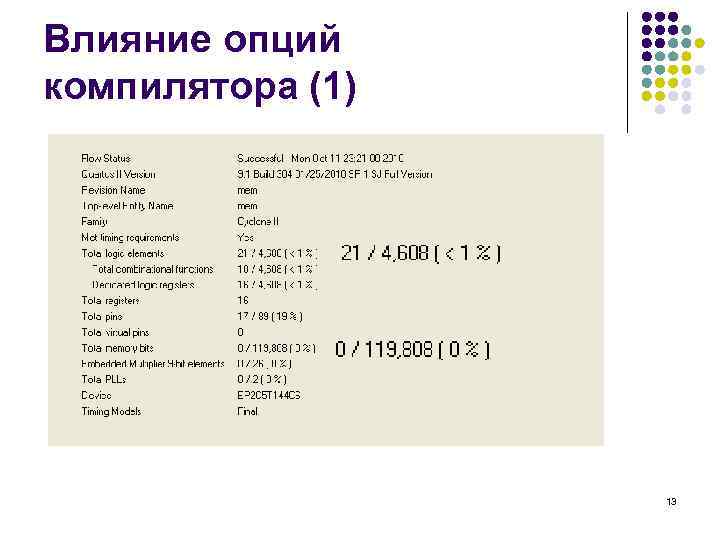

Влияние опций компилятора (1) 13

Влияние опций компилятора (1) 13

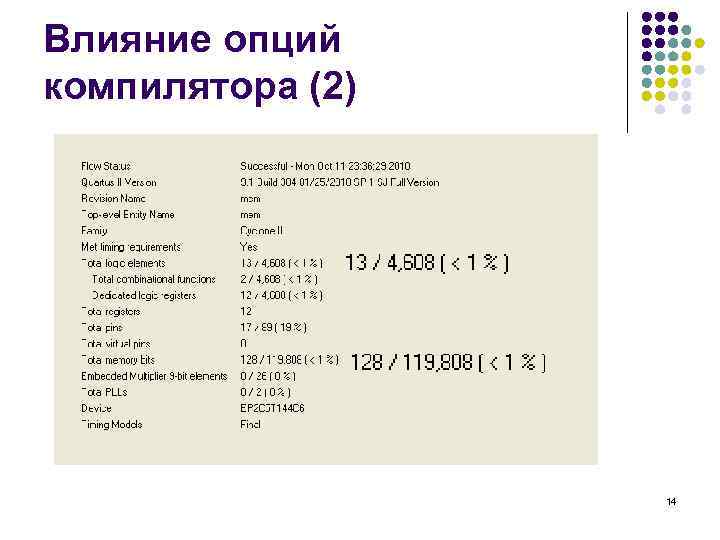

Влияние опций компилятора (2) 14

Влияние опций компилятора (2) 14

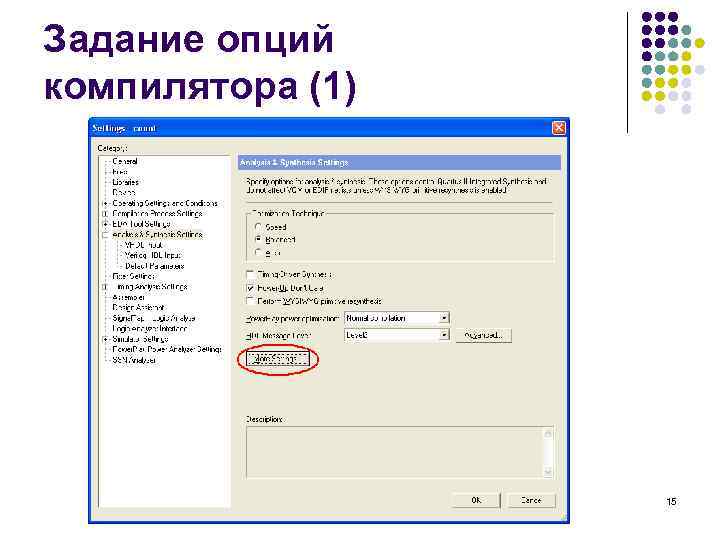

Задание опций компилятора (1) 15

Задание опций компилятора (1) 15

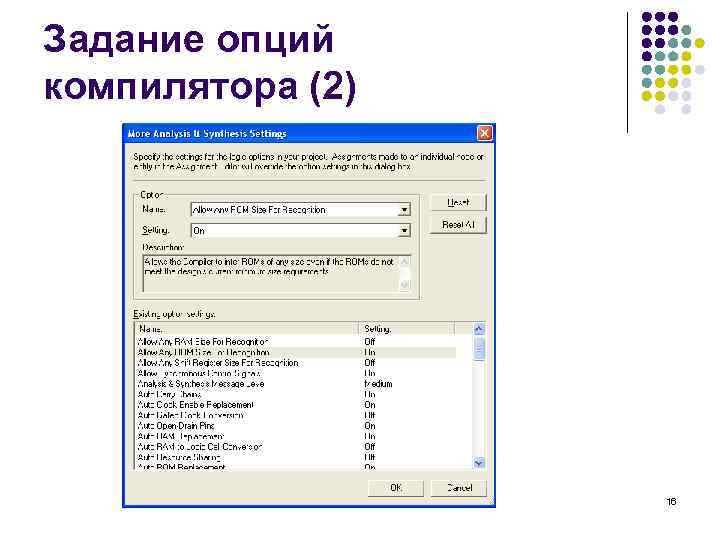

Задание опций компилятора (2) 16

Задание опций компилятора (2) 16

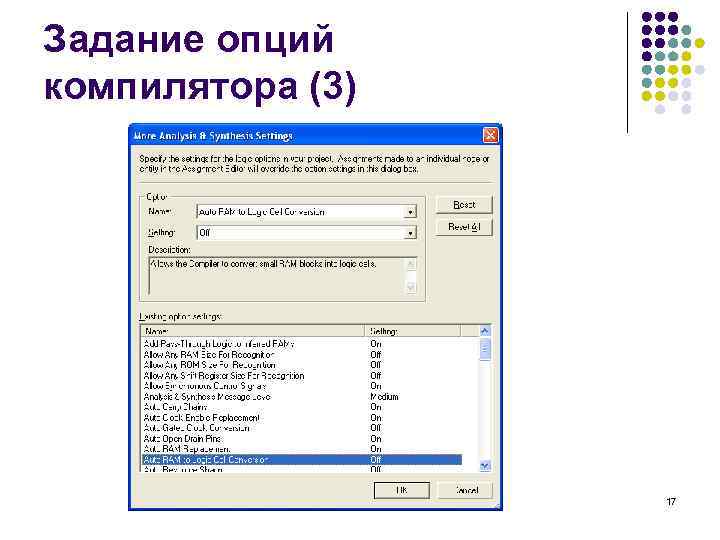

Задание опций компилятора (3) 17

Задание опций компилятора (3) 17

Задание опций компилятора (4) l Меню Assignments -> Settings… l l Страница Analysis and Synthesis Settings Кнопка More Settings… Диалог More Analysis & Synthesis Settings Изменяем параметры: l l Allow Any RAM Size For Recognition, Allow Any ROM Size For Recognition – размещение любых по размеру блоков ОЗУ и ПЗУ во встроенных блоках ПЛИС. Auto RAM to Logic Cell Conversion – автоматическое размещение небольших блоков памяти в логических элементах. 18

Задание опций компилятора (4) l Меню Assignments -> Settings… l l Страница Analysis and Synthesis Settings Кнопка More Settings… Диалог More Analysis & Synthesis Settings Изменяем параметры: l l Allow Any RAM Size For Recognition, Allow Any ROM Size For Recognition – размещение любых по размеру блоков ОЗУ и ПЗУ во встроенных блоках ПЛИС. Auto RAM to Logic Cell Conversion – автоматическое размещение небольших блоков памяти в логических элементах. 18

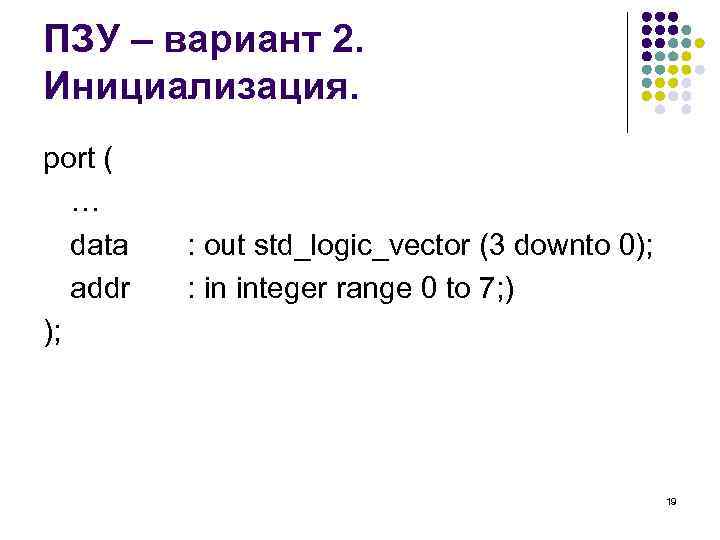

ПЗУ – вариант 2. Инициализация. port ( … data addr ); : out std_logic_vector (3 downto 0); : in integer range 0 to 7; ) 19

ПЗУ – вариант 2. Инициализация. port ( … data addr ); : out std_logic_vector (3 downto 0); : in integer range 0 to 7; ) 19

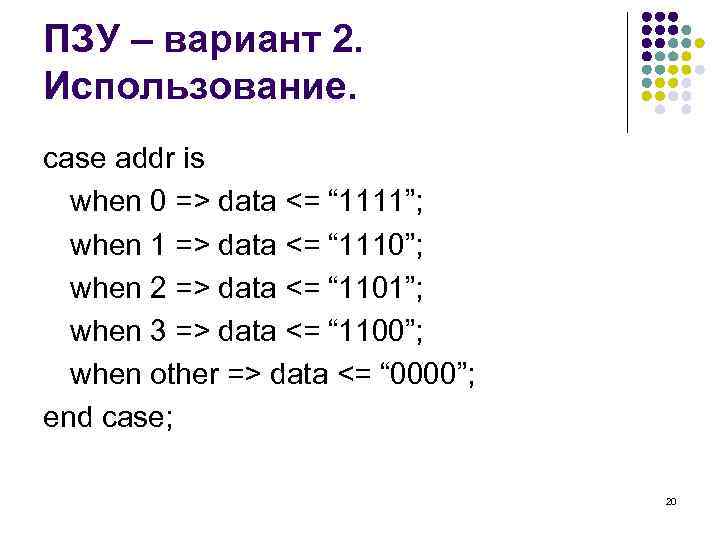

ПЗУ – вариант 2. Использование. case addr is when 0 => data <= “ 1111”; when 1 => data <= “ 1110”; when 2 => data <= “ 1101”; when 3 => data <= “ 1100”; when other => data <= “ 0000”; end case; 20

ПЗУ – вариант 2. Использование. case addr is when 0 => data <= “ 1111”; when 1 => data <= “ 1110”; when 2 => data <= “ 1101”; when 3 => data <= “ 1100”; when other => data <= “ 0000”; end case; 20

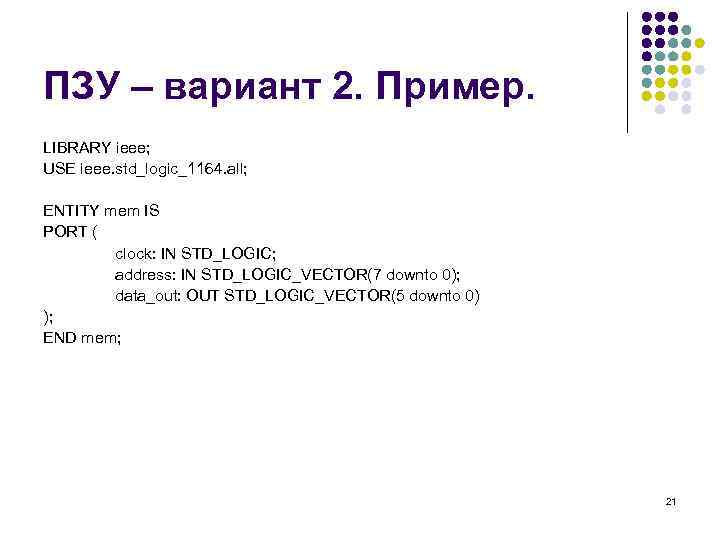

ПЗУ – вариант 2. Пример. LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY mem IS PORT ( clock: IN STD_LOGIC; address: IN STD_LOGIC_VECTOR(7 downto 0); data_out: OUT STD_LOGIC_VECTOR(5 downto 0) ); END mem; 21

ПЗУ – вариант 2. Пример. LIBRARY ieee; USE ieee. std_logic_1164. all; ENTITY mem IS PORT ( clock: IN STD_LOGIC; address: IN STD_LOGIC_VECTOR(7 downto 0); data_out: OUT STD_LOGIC_VECTOR(5 downto 0) ); END mem; 21

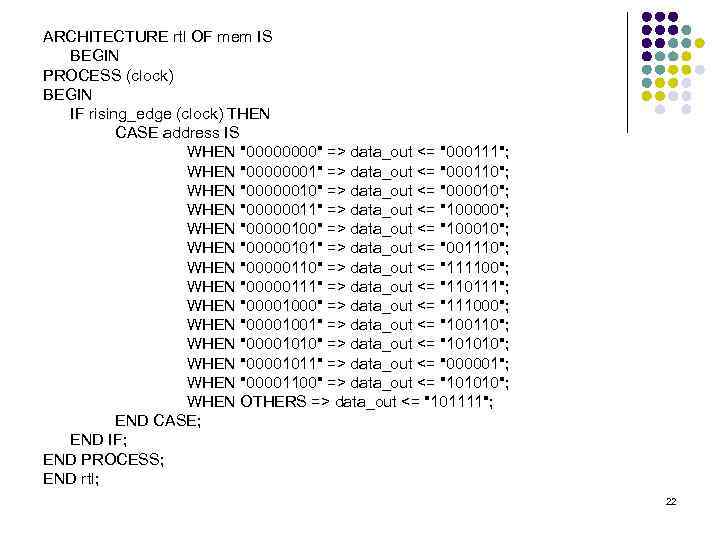

ARCHITECTURE rtl OF mem IS BEGIN PROCESS (clock) BEGIN IF rising_edge (clock) THEN CASE address IS WHEN "0000" => data_out <= "000111"; WHEN "00000001" => data_out <= "000110"; WHEN "00000010" => data_out <= "000010"; WHEN "00000011" => data_out <= "100000"; WHEN "00000100" => data_out <= "100010"; WHEN "00000101" => data_out <= "001110"; WHEN "00000110" => data_out <= "111100"; WHEN "00000111" => data_out <= "110111"; WHEN "00001000" => data_out <= "111000"; WHEN "00001001" => data_out <= "100110"; WHEN "00001010" => data_out <= "101010"; WHEN "00001011" => data_out <= "000001"; WHEN "00001100" => data_out <= "101010"; WHEN OTHERS => data_out <= "101111"; END CASE; END IF; END PROCESS; END rtl; 22

ARCHITECTURE rtl OF mem IS BEGIN PROCESS (clock) BEGIN IF rising_edge (clock) THEN CASE address IS WHEN "0000" => data_out <= "000111"; WHEN "00000001" => data_out <= "000110"; WHEN "00000010" => data_out <= "000010"; WHEN "00000011" => data_out <= "100000"; WHEN "00000100" => data_out <= "100010"; WHEN "00000101" => data_out <= "001110"; WHEN "00000110" => data_out <= "111100"; WHEN "00000111" => data_out <= "110111"; WHEN "00001000" => data_out <= "111000"; WHEN "00001001" => data_out <= "100110"; WHEN "00001010" => data_out <= "101010"; WHEN "00001011" => data_out <= "000001"; WHEN "00001100" => data_out <= "101010"; WHEN OTHERS => data_out <= "101111"; END CASE; END IF; END PROCESS; END rtl; 22

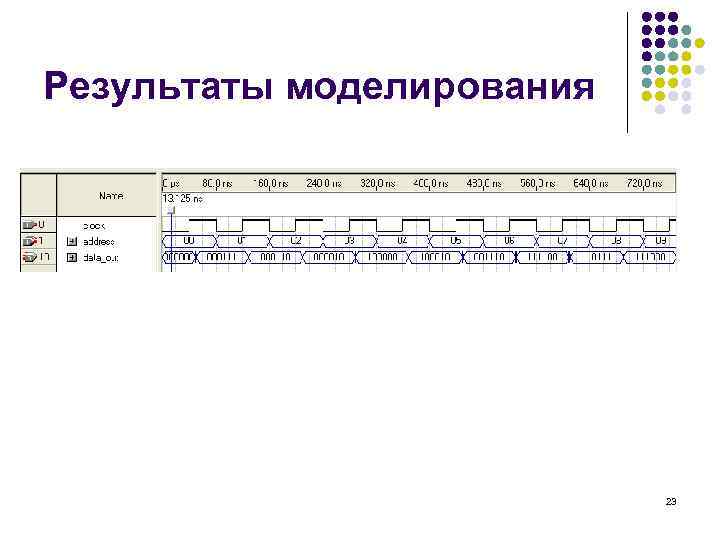

Результаты моделирования 23

Результаты моделирования 23

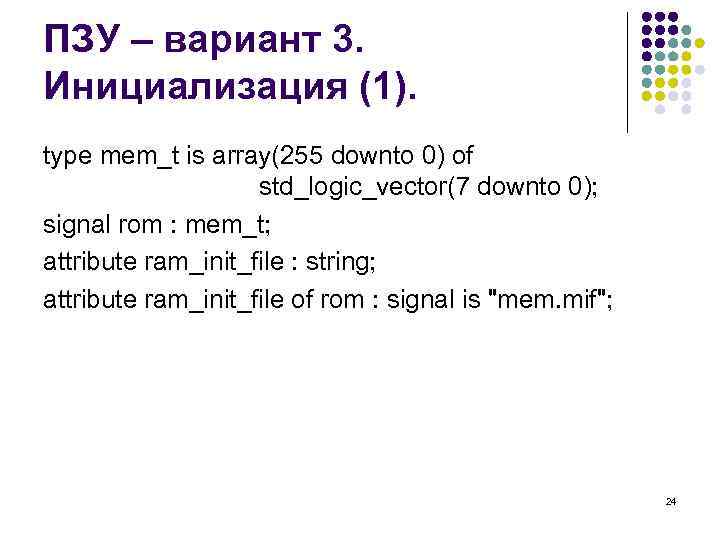

ПЗУ – вариант 3. Инициализация (1). type mem_t is array(255 downto 0) of std_logic_vector(7 downto 0); signal rom : mem_t; attribute ram_init_file : string; attribute ram_init_file of rom : signal is "mem. mif"; 24

ПЗУ – вариант 3. Инициализация (1). type mem_t is array(255 downto 0) of std_logic_vector(7 downto 0); signal rom : mem_t; attribute ram_init_file : string; attribute ram_init_file of rom : signal is "mem. mif"; 24

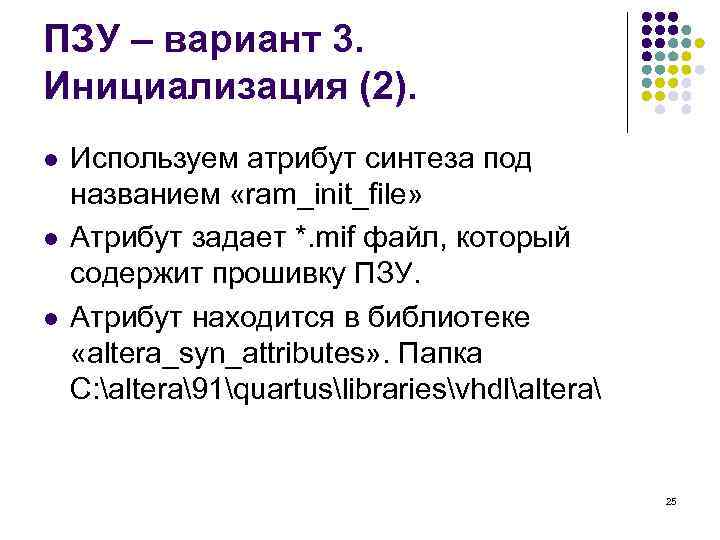

ПЗУ – вариант 3. Инициализация (2). l l l Используем атрибут синтеза под названием «ram_init_file» Атрибут задает *. mif файл, который содержит прошивку ПЗУ. Атрибут находится в библиотеке «altera_syn_attributes» . Папка C: altera91quartuslibrariesvhdlaltera 25

ПЗУ – вариант 3. Инициализация (2). l l l Используем атрибут синтеза под названием «ram_init_file» Атрибут задает *. mif файл, который содержит прошивку ПЗУ. Атрибут находится в библиотеке «altera_syn_attributes» . Папка C: altera91quartuslibrariesvhdlaltera 25

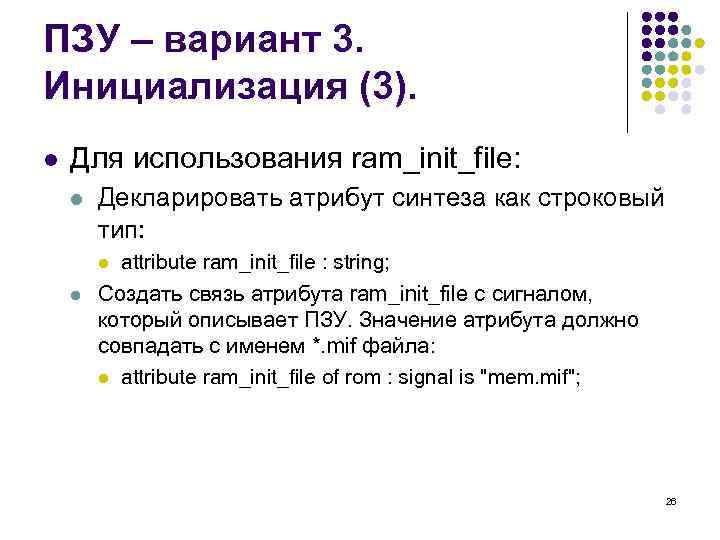

ПЗУ – вариант 3. Инициализация (3). l Для использования ram_init_file: l Декларировать атрибут синтеза как строковый тип: attribute ram_init_file : string; Создать связь атрибута ram_init_file с сигналом, который описывает ПЗУ. Значение атрибута должно совпадать с именем *. mif файла: l attribute ram_init_file of rom : signal is "mem. mif"; l l 26

ПЗУ – вариант 3. Инициализация (3). l Для использования ram_init_file: l Декларировать атрибут синтеза как строковый тип: attribute ram_init_file : string; Создать связь атрибута ram_init_file с сигналом, который описывает ПЗУ. Значение атрибута должно совпадать с именем *. mif файла: l attribute ram_init_file of rom : signal is "mem. mif"; l l 26

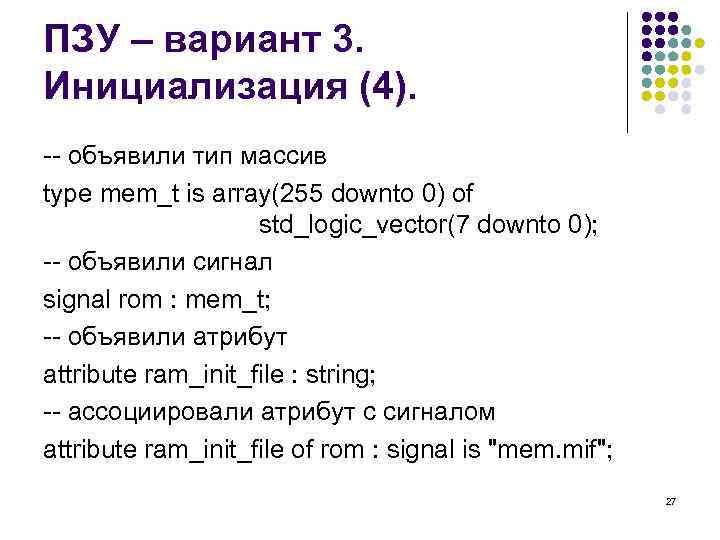

ПЗУ – вариант 3. Инициализация (4). -- объявили тип массив type mem_t is array(255 downto 0) of std_logic_vector(7 downto 0); -- объявили сигнал signal rom : mem_t; -- объявили атрибут attribute ram_init_file : string; -- ассоциировали атрибут с сигналом attribute ram_init_file of rom : signal is "mem. mif"; 27

ПЗУ – вариант 3. Инициализация (4). -- объявили тип массив type mem_t is array(255 downto 0) of std_logic_vector(7 downto 0); -- объявили сигнал signal rom : mem_t; -- объявили атрибут attribute ram_init_file : string; -- ассоциировали атрибут с сигналом attribute ram_init_file of rom : signal is "mem. mif"; 27

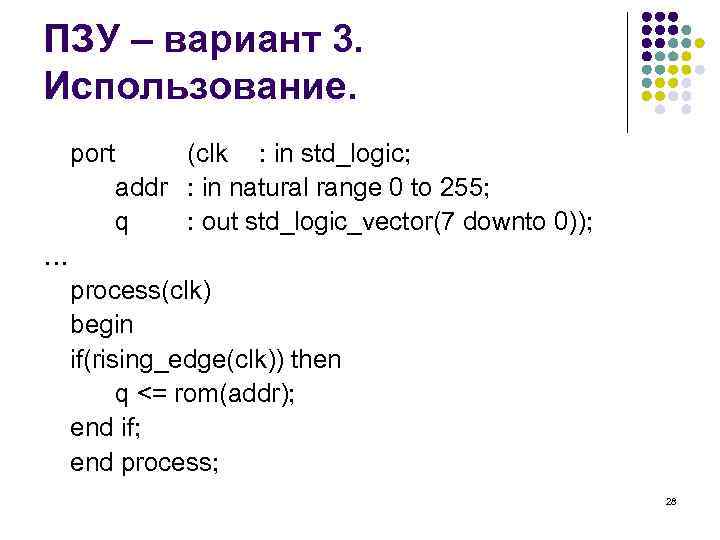

ПЗУ – вариант 3. Использование. port (clk : in std_logic; addr : in natural range 0 to 255; q : out std_logic_vector(7 downto 0)); … process(clk) begin if(rising_edge(clk)) then q <= rom(addr); end if; end process; 28

ПЗУ – вариант 3. Использование. port (clk : in std_logic; addr : in natural range 0 to 255; q : out std_logic_vector(7 downto 0)); … process(clk) begin if(rising_edge(clk)) then q <= rom(addr); end if; end process; 28

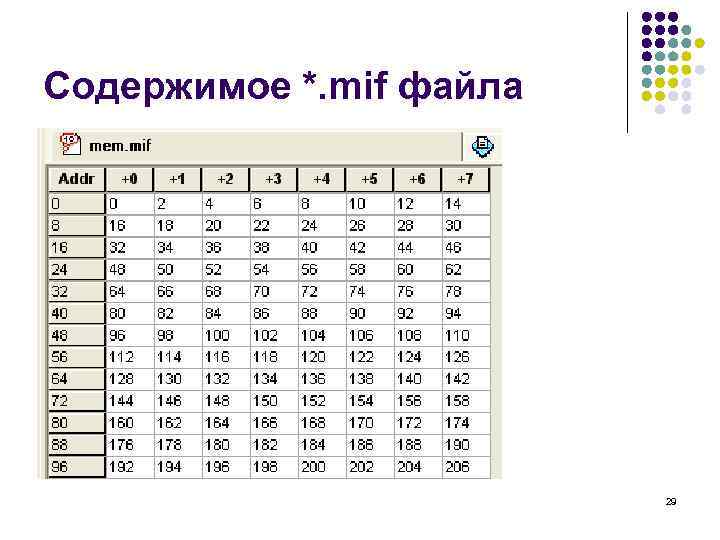

Содержимое *. mif файла 29

Содержимое *. mif файла 29

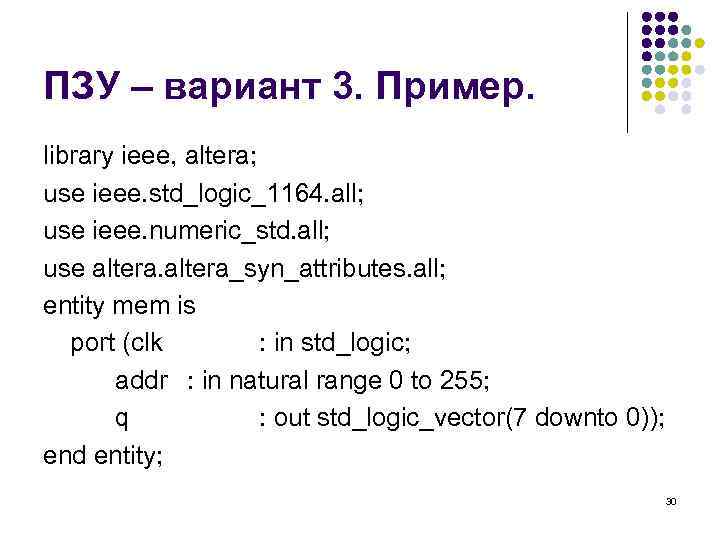

ПЗУ – вариант 3. Пример. library ieee, altera; use ieee. std_logic_1164. all; use ieee. numeric_std. all; use altera_syn_attributes. all; entity mem is port (clk : in std_logic; addr : in natural range 0 to 255; q : out std_logic_vector(7 downto 0)); end entity; 30

ПЗУ – вариант 3. Пример. library ieee, altera; use ieee. std_logic_1164. all; use ieee. numeric_std. all; use altera_syn_attributes. all; entity mem is port (clk : in std_logic; addr : in natural range 0 to 255; q : out std_logic_vector(7 downto 0)); end entity; 30

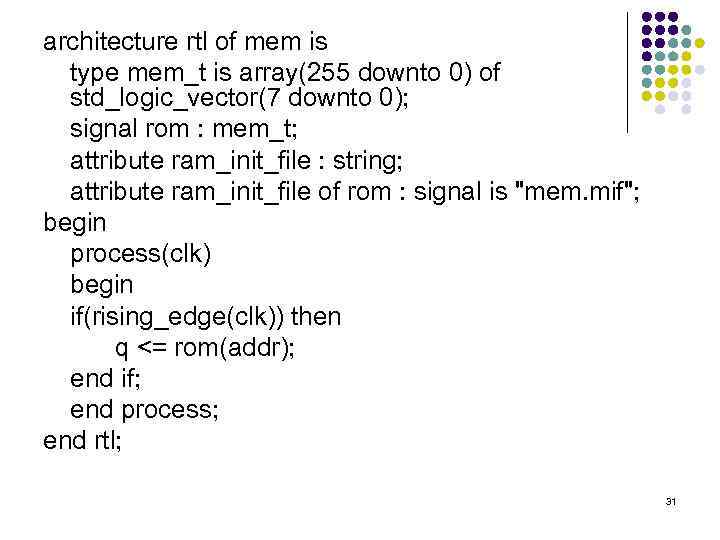

architecture rtl of mem is type mem_t is array(255 downto 0) of std_logic_vector(7 downto 0); signal rom : mem_t; attribute ram_init_file : string; attribute ram_init_file of rom : signal is "mem. mif"; begin process(clk) begin if(rising_edge(clk)) then q <= rom(addr); end if; end process; end rtl; 31

architecture rtl of mem is type mem_t is array(255 downto 0) of std_logic_vector(7 downto 0); signal rom : mem_t; attribute ram_init_file : string; attribute ram_init_file of rom : signal is "mem. mif"; begin process(clk) begin if(rising_edge(clk)) then q <= rom(addr); end if; end process; end rtl; 31

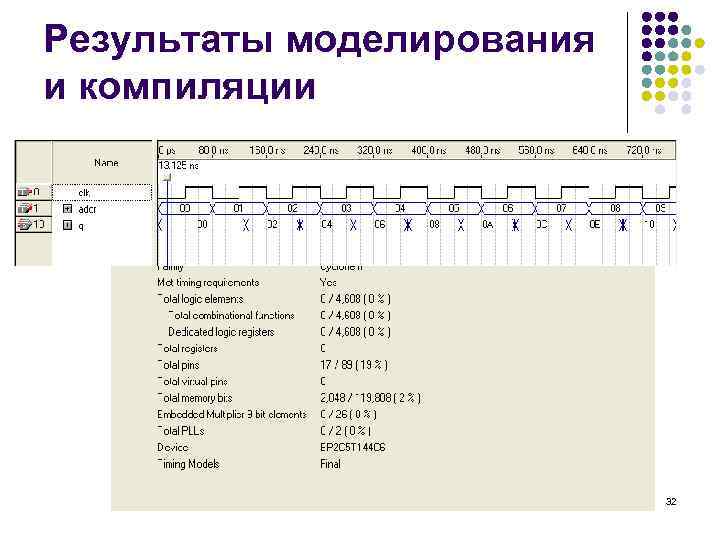

Результаты моделирования и компиляции 32

Результаты моделирования и компиляции 32

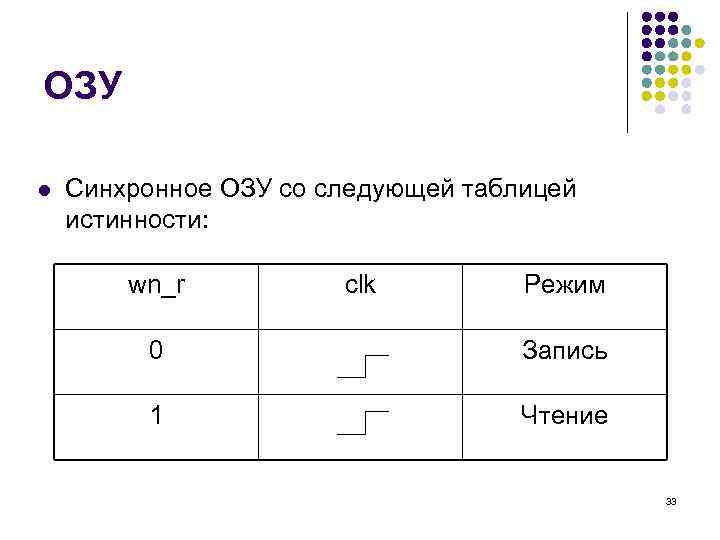

ОЗУ l Синхронное ОЗУ со следующей таблицей истинности: wn_r clk Режим 0 Запись 1 Чтение 33

ОЗУ l Синхронное ОЗУ со следующей таблицей истинности: wn_r clk Режим 0 Запись 1 Чтение 33

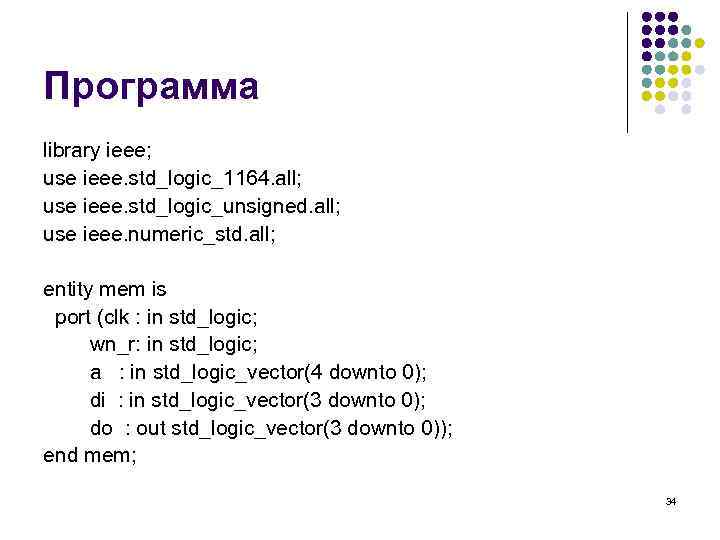

Программа library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; use ieee. numeric_std. all; entity mem is port (clk : in std_logic; wn_r: in std_logic; a : in std_logic_vector(4 downto 0); di : in std_logic_vector(3 downto 0); do : out std_logic_vector(3 downto 0)); end mem; 34

Программа library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; use ieee. numeric_std. all; entity mem is port (clk : in std_logic; wn_r: in std_logic; a : in std_logic_vector(4 downto 0); di : in std_logic_vector(3 downto 0); do : out std_logic_vector(3 downto 0)); end mem; 34

architecture syn of mem is type ram_type is array (31 downto 0) of std_logic_vector (3 downto 0); signal RAM : ram_type; begin process (clk) begin if (clk'event and clk = '1') then if (wn_r = '0') then -- запись при « 0» , чтение по « 1» RAM(to_integer(unsigned(a))) <= di; else do <= RAM(to_integer(unsigned(a))); end if; end process; end syn; 35

architecture syn of mem is type ram_type is array (31 downto 0) of std_logic_vector (3 downto 0); signal RAM : ram_type; begin process (clk) begin if (clk'event and clk = '1') then if (wn_r = '0') then -- запись при « 0» , чтение по « 1» RAM(to_integer(unsigned(a))) <= di; else do <= RAM(to_integer(unsigned(a))); end if; end process; end syn; 35

Результаты моделирования 36

Результаты моделирования 36

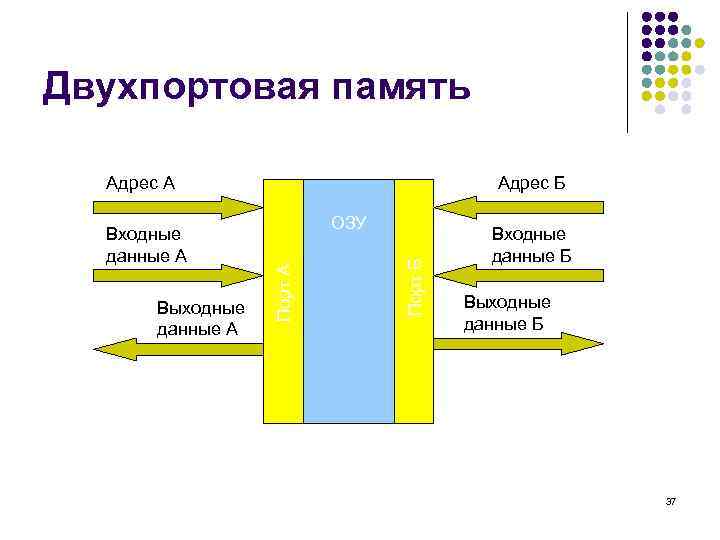

Двухпортовая память Адрес А Порт Б Выходные данные А ОЗУ Порт А Входные данные А Адрес Б Входные данные Б Выходные данные Б 37

Двухпортовая память Адрес А Порт Б Выходные данные А ОЗУ Порт А Входные данные А Адрес Б Входные данные Б Выходные данные Б 37

Достоинства двухпортовой памяти l l Возможность одновременного чтения и записи данных в один блок памяти. Увеличение быстродействия. 38

Достоинства двухпортовой памяти l l Возможность одновременного чтения и записи данных в один блок памяти. Увеличение быстродействия. 38

Проблемы двухпортовой памяти l l Необходимо четко определить поведение во время операции «чтение во время записи» Поддерживается не всеми семействами и микросхемами. 39

Проблемы двухпортовой памяти l l Необходимо четко определить поведение во время операции «чтение во время записи» Поддерживается не всеми семействами и микросхемами. 39

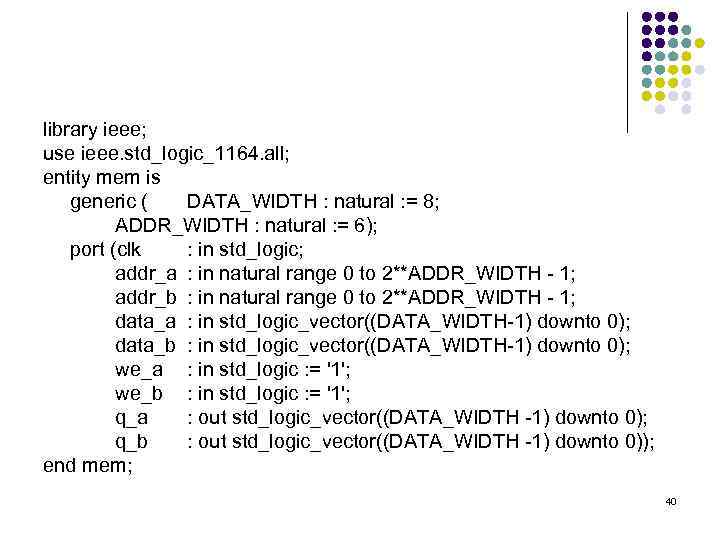

library ieee; use ieee. std_logic_1164. all; entity mem is generic ( DATA_WIDTH : natural : = 8; ADDR_WIDTH : natural : = 6); port (clk : in std_logic; addr_a : in natural range 0 to 2**ADDR_WIDTH - 1; addr_b : in natural range 0 to 2**ADDR_WIDTH - 1; data_a : in std_logic_vector((DATA_WIDTH-1) downto 0); data_b : in std_logic_vector((DATA_WIDTH-1) downto 0); we_a : in std_logic : = '1'; we_b : in std_logic : = '1'; q_a : out std_logic_vector((DATA_WIDTH -1) downto 0); q_b : out std_logic_vector((DATA_WIDTH -1) downto 0)); end mem; 40

library ieee; use ieee. std_logic_1164. all; entity mem is generic ( DATA_WIDTH : natural : = 8; ADDR_WIDTH : natural : = 6); port (clk : in std_logic; addr_a : in natural range 0 to 2**ADDR_WIDTH - 1; addr_b : in natural range 0 to 2**ADDR_WIDTH - 1; data_a : in std_logic_vector((DATA_WIDTH-1) downto 0); data_b : in std_logic_vector((DATA_WIDTH-1) downto 0); we_a : in std_logic : = '1'; we_b : in std_logic : = '1'; q_a : out std_logic_vector((DATA_WIDTH -1) downto 0); q_b : out std_logic_vector((DATA_WIDTH -1) downto 0)); end mem; 40

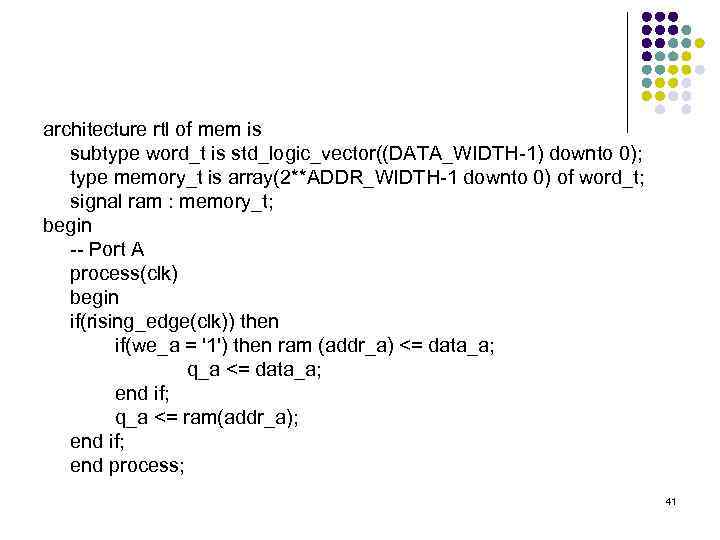

architecture rtl of mem is subtype word_t is std_logic_vector((DATA_WIDTH-1) downto 0); type memory_t is array(2**ADDR_WIDTH-1 downto 0) of word_t; signal ram : memory_t; begin -- Port A process(clk) begin if(rising_edge(clk)) then if(we_a = '1') then ram (addr_a) <= data_a; q_a <= data_a; end if; q_a <= ram(addr_a); end if; end process; 41

architecture rtl of mem is subtype word_t is std_logic_vector((DATA_WIDTH-1) downto 0); type memory_t is array(2**ADDR_WIDTH-1 downto 0) of word_t; signal ram : memory_t; begin -- Port A process(clk) begin if(rising_edge(clk)) then if(we_a = '1') then ram (addr_a) <= data_a; q_a <= data_a; end if; q_a <= ram(addr_a); end if; end process; 41

-- Port B process(clk) begin if(rising_edge(clk)) then if(we_b = '1') then ram(addr_b) <= data_b; q_b <= data_b; end if; q_b <= ram(addr_b); end if; end process; end rtl; 42

-- Port B process(clk) begin if(rising_edge(clk)) then if(we_b = '1') then ram(addr_b) <= data_b; q_b <= data_b; end if; q_b <= ram(addr_b); end if; end process; end rtl; 42

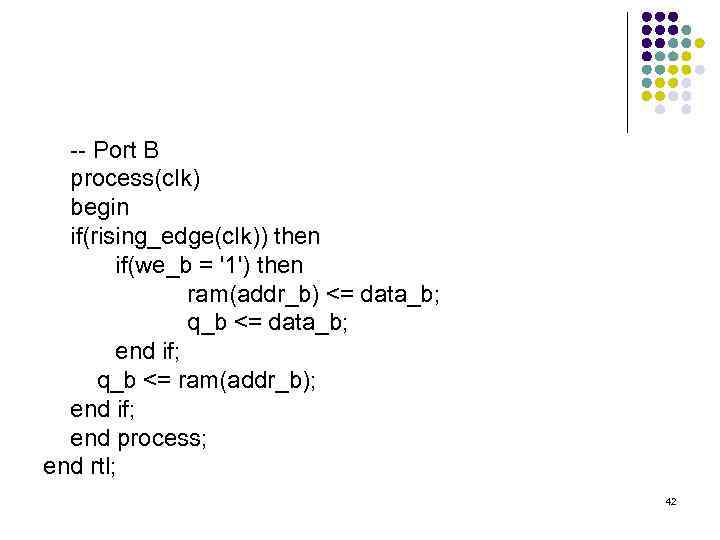

Результаты компиляции. Cyclone II. 43

Результаты компиляции. Cyclone II. 43

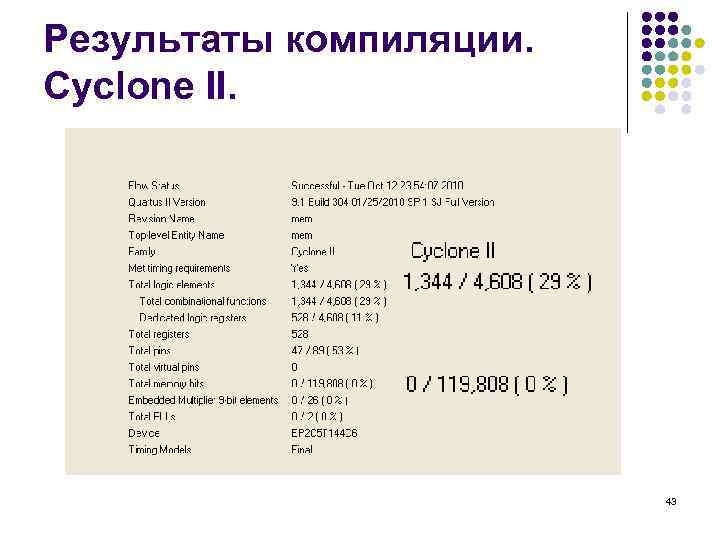

Результаты компиляции. Cyclone III. 44

Результаты компиляции. Cyclone III. 44

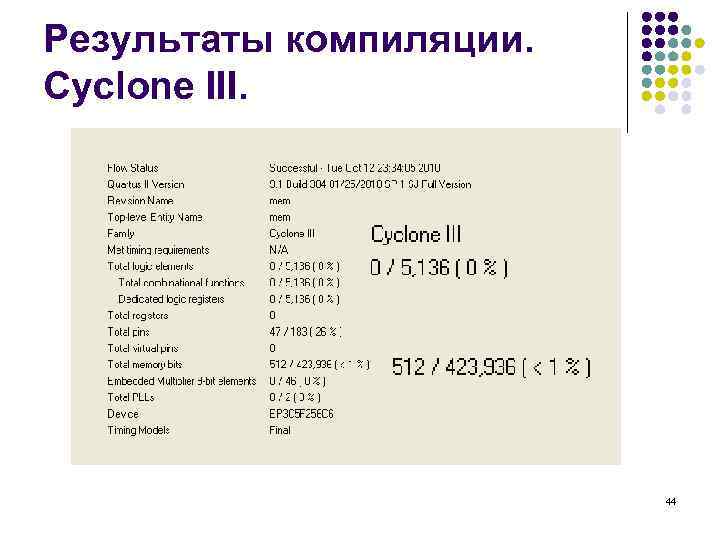

Результаты моделирования 45

Результаты моделирования 45

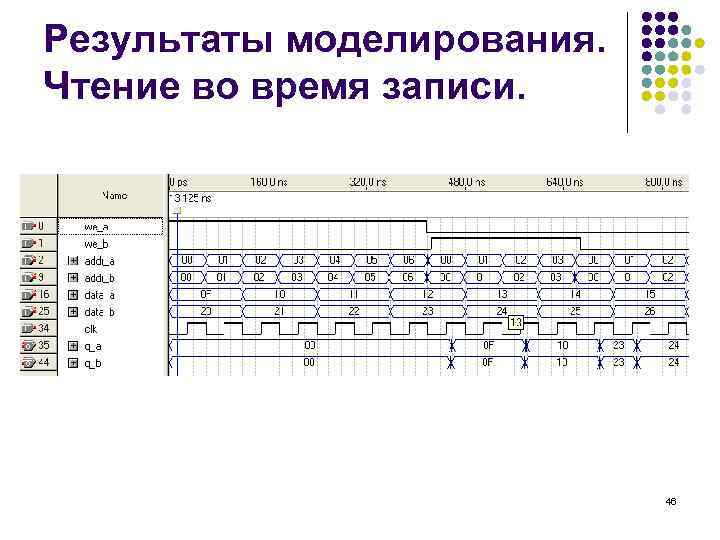

Результаты моделирования. Чтение во время записи. 46

Результаты моделирования. Чтение во время записи. 46