Л7. ОЗУ.ppt

- Количество слайдов: 29

Оперативное Запоминающее Устройство

Оперативное Запоминающее Устройство

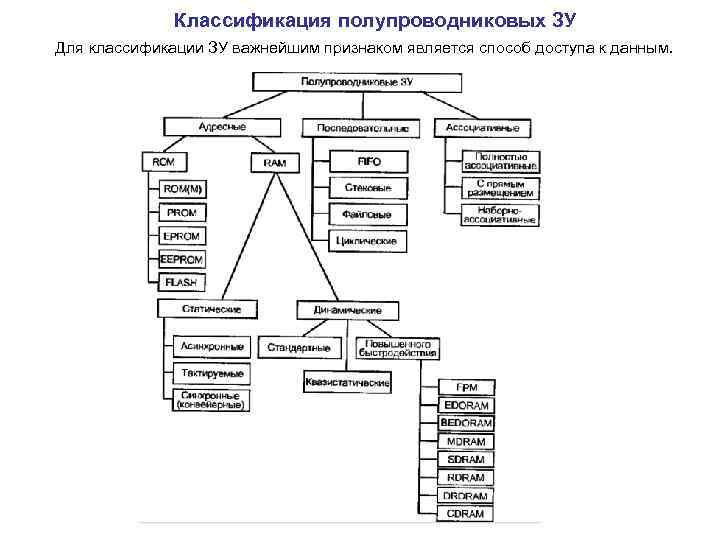

Классификация полупроводниковых ЗУ Для классификации ЗУ важнейшим признаком является способ доступа к данным.

Классификация полупроводниковых ЗУ Для классификации ЗУ важнейшим признаком является способ доступа к данным.

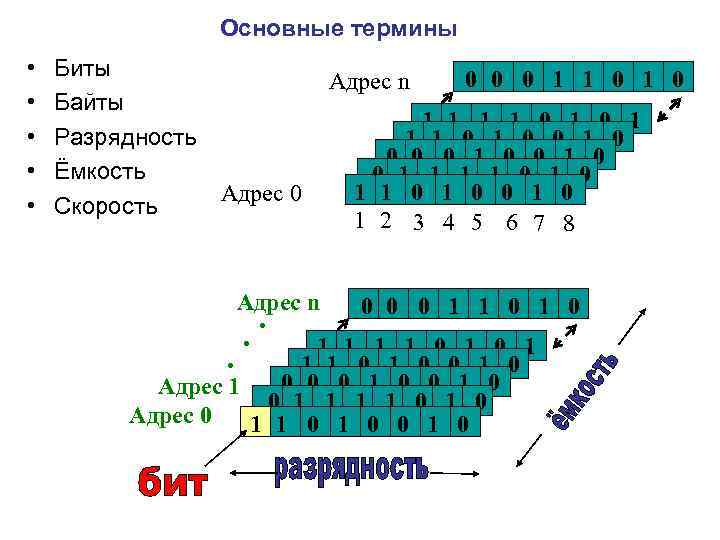

Основные термины • • • Биты Байты Разрядность Ёмкость Скорость Адрес n Адрес 0 Адрес n . . 0 0 0 1 1 0 1 0 1 1 1 0 0 1 0 0 1 1 0 0 1 2 3 4 5 6 7 8 0 0 0 1 1 0 1 0 1 1 1 0 0 1 0 0 1 0 Адрес 1 0 1 0 Адрес 0 1 1 0 0 1 0 .

Основные термины • • • Биты Байты Разрядность Ёмкость Скорость Адрес n Адрес 0 Адрес n . . 0 0 0 1 1 0 1 0 1 1 1 0 0 1 0 0 1 1 0 0 1 2 3 4 5 6 7 8 0 0 0 1 1 0 1 0 1 1 1 0 0 1 0 0 1 0 Адрес 1 0 1 0 Адрес 0 1 1 0 0 1 0 .

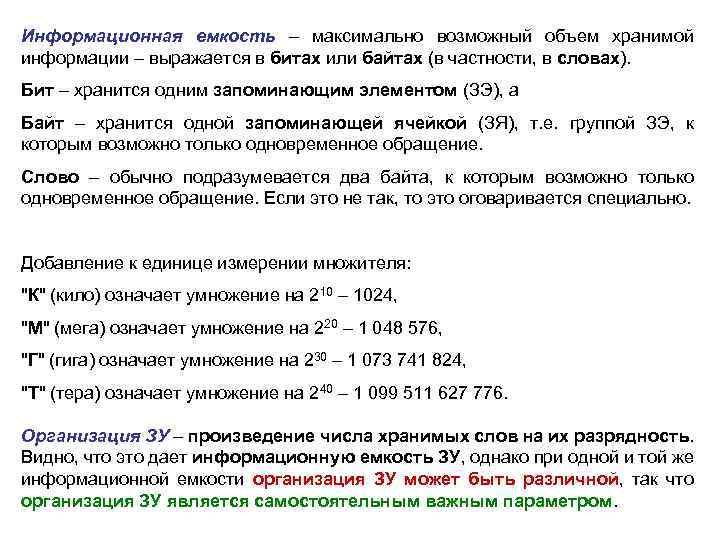

Информационная емкость – максимально возможный объем хранимой информации – выражается в битах или байтах (в частности, в словах). Бит – хранится одним запоминающим элементом (ЗЭ), а Байт – хранится одной запоминающей ячейкой (ЗЯ), т. е. группой ЗЭ, к которым возможно только одновременное обращение. Слово – обычно подразумевается два байта, к которым возможно только одновременное обращение. Если это не так, то это оговаривается специально. Добавление к единице измерении множителя: "К" (кило) означает умножение на 210 – 1024, "М" (мега) означает умножение на 220 – 1 048 576, "Г" (гига) означает умножение на 230 – 1 073 741 824, "Т" (тера) означает умножение на 240 – 1 099 511 627 776. Организация ЗУ – произведение числа хранимых слов на их разрядность. Видно, что это дает информационную емкость ЗУ, однако при одной и той же информационной емкости организация ЗУ может быть различной, так что организация ЗУ является самостоятельным важным параметром.

Информационная емкость – максимально возможный объем хранимой информации – выражается в битах или байтах (в частности, в словах). Бит – хранится одним запоминающим элементом (ЗЭ), а Байт – хранится одной запоминающей ячейкой (ЗЯ), т. е. группой ЗЭ, к которым возможно только одновременное обращение. Слово – обычно подразумевается два байта, к которым возможно только одновременное обращение. Если это не так, то это оговаривается специально. Добавление к единице измерении множителя: "К" (кило) означает умножение на 210 – 1024, "М" (мега) означает умножение на 220 – 1 048 576, "Г" (гига) означает умножение на 230 – 1 073 741 824, "Т" (тера) означает умножение на 240 – 1 099 511 627 776. Организация ЗУ – произведение числа хранимых слов на их разрядность. Видно, что это дает информационную емкость ЗУ, однако при одной и той же информационной емкости организация ЗУ может быть различной, так что организация ЗУ является самостоятельным важным параметром.

Основные операции с ОЗУ Операции чтения и записи в память Чтение (READ) ЗАПИСЬ (WRITE) 0 0 0 1 1 0 1 0

Основные операции с ОЗУ Операции чтения и записи в память Чтение (READ) ЗАПИСЬ (WRITE) 0 0 0 1 1 0 1 0

Быстродействие (производительность) ЗУ (время доступа) оценивают : • • • временем считывания, временем записи, длительностью циклов чтения/записи. Время считывания – интервал времени между моментами появления сигнала чтения и запрашиваемой информации (слова) на выходе ЗУ. Время записи – интервал времени после появления сигнала записи, достаточный для установления ЗУ в состояние, задаваемое входным словом. Минимально допустимый интервал времени между последовательными чтениями или записями образует соответствующий цикл чтения/записи. Длительности циклов могут превышать времена чтения или записи, т. к. после этих операций может потребоваться время для восстановления необходимого начального состояния ЗУ. Скорость (Время доступа) Запрос на чтение / запись данных Время

Быстродействие (производительность) ЗУ (время доступа) оценивают : • • • временем считывания, временем записи, длительностью циклов чтения/записи. Время считывания – интервал времени между моментами появления сигнала чтения и запрашиваемой информации (слова) на выходе ЗУ. Время записи – интервал времени после появления сигнала записи, достаточный для установления ЗУ в состояние, задаваемое входным словом. Минимально допустимый интервал времени между последовательными чтениями или записями образует соответствующий цикл чтения/записи. Длительности циклов могут превышать времена чтения или записи, т. к. после этих операций может потребоваться время для восстановления необходимого начального состояния ЗУ. Скорость (Время доступа) Запрос на чтение / запись данных Время

Время чтении, записи и длительности циклов – это статические (традиционные) параметры. Для некоторых современных типов ЗУ они должны быть дополнены новыми – динамическими. Причиной является более сложный характер доступа к хранимым в памяти данным, когда обращение к первому слову некоторой группы слов (пакета) требует большего времени, чем обращение к последующим. Для таких режимов вводят параметр времени доступа при первом обращении (Latency) и темпа передач для последующих слов пакета (Bandwidth). Темп передач в свою очередь оценивается двумя значениями — предельным (внутри пакета) и усредненным (с учетом Latency). С уменьшением пакета усредненный темп снижается, все более отличаясь от предельного. Перечисленные выше динамические эксплуатационными (измеряемыми). параметры являются Помимо указанных основных статических и динамических параметров для ЗУ указывают еще целый набор временных интервалов.

Время чтении, записи и длительности циклов – это статические (традиционные) параметры. Для некоторых современных типов ЗУ они должны быть дополнены новыми – динамическими. Причиной является более сложный характер доступа к хранимым в памяти данным, когда обращение к первому слову некоторой группы слов (пакета) требует большего времени, чем обращение к последующим. Для таких режимов вводят параметр времени доступа при первом обращении (Latency) и темпа передач для последующих слов пакета (Bandwidth). Темп передач в свою очередь оценивается двумя значениями — предельным (внутри пакета) и усредненным (с учетом Latency). С уменьшением пакета усредненный темп снижается, все более отличаясь от предельного. Перечисленные выше динамические эксплуатационными (измеряемыми). параметры являются Помимо указанных основных статических и динамических параметров для ЗУ указывают еще целый набор временных интервалов.

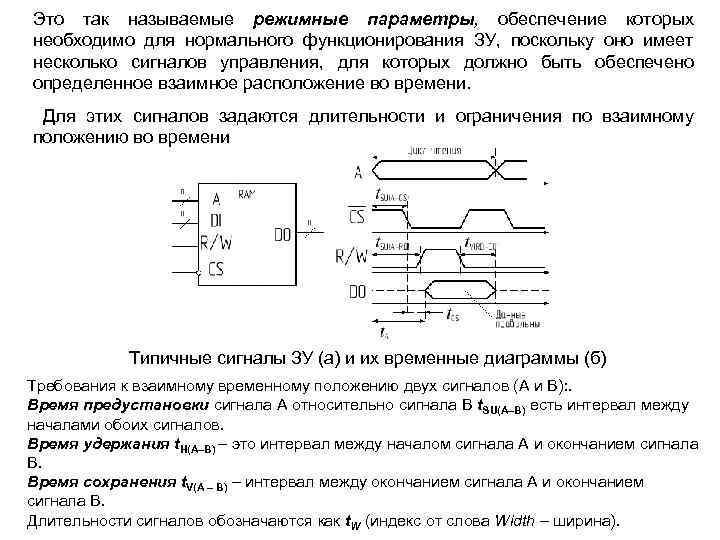

Это так называемые режимные параметры, обеспечение которых необходимо для нормального функционирования ЗУ, поскольку оно имеет несколько сигналов управления, для которых должно быть обеспечено определенное взаимное расположение во времени. Для этих сигналов задаются длительности и ограничения по взаимному положению во времени Типичные сигналы ЗУ (а) и их временные диаграммы (б) Требования к взаимному временному положению двух сигналов (А и В): . Время предустановки сигнала А относительно сигнала В t. SU(A–B) есть интервал между началами обоих сигналов. Время удержания t. H(A–В) – это интервал между началом сигнала А и окончанием сигнала В. Время сохранения t. V(A – В) – интервал между окончанием сигнала А и окончанием сигнала В. Длительности сигналов обозначаются как t. W (индекс от слова Width – ширина).

Это так называемые режимные параметры, обеспечение которых необходимо для нормального функционирования ЗУ, поскольку оно имеет несколько сигналов управления, для которых должно быть обеспечено определенное взаимное расположение во времени. Для этих сигналов задаются длительности и ограничения по взаимному положению во времени Типичные сигналы ЗУ (а) и их временные диаграммы (б) Требования к взаимному временному положению двух сигналов (А и В): . Время предустановки сигнала А относительно сигнала В t. SU(A–B) есть интервал между началами обоих сигналов. Время удержания t. H(A–В) – это интервал между началом сигнала А и окончанием сигнала В. Время сохранения t. V(A – В) – интервал между окончанием сигнала А и окончанием сигнала В. Длительности сигналов обозначаются как t. W (индекс от слова Width – ширина).

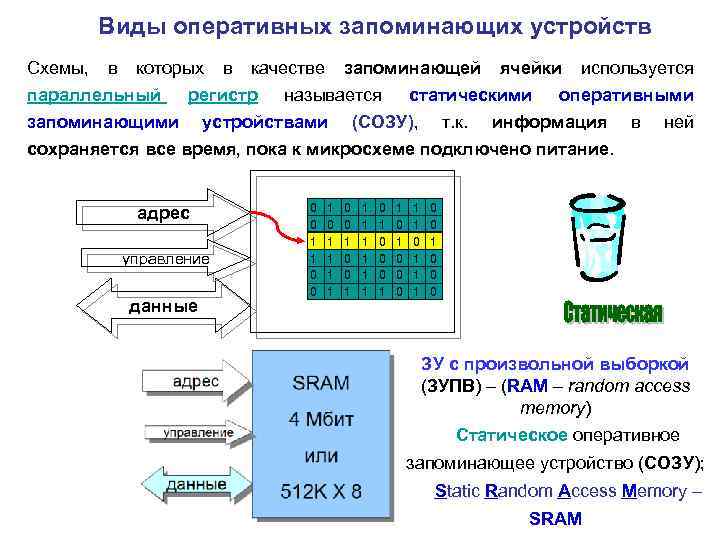

Виды оперативных запоминающих устройств Схемы, в которых в качестве запоминающей ячейки используется параллельный регистр называется статическими оперативными запоминающими устройствами (СОЗУ), т. к. информация в ней сохраняется все время, пока к микросхеме подключено питание. адрес управление данные 0 0 1 1 1 1 0 0 1 1 1 1 0 1 0 0 0 1 1 1 0 0 0 ЗУ с произвольной выборкой (ЗУПВ) – (RAM – random access memory) Статическое оперативное запоминающее устройство (СОЗУ); Static Random Access Memory – SRAM

Виды оперативных запоминающих устройств Схемы, в которых в качестве запоминающей ячейки используется параллельный регистр называется статическими оперативными запоминающими устройствами (СОЗУ), т. к. информация в ней сохраняется все время, пока к микросхеме подключено питание. адрес управление данные 0 0 1 1 1 1 0 0 1 1 1 1 0 1 0 0 0 1 1 1 0 0 0 ЗУ с произвольной выборкой (ЗУПВ) – (RAM – random access memory) Статическое оперативное запоминающее устройство (СОЗУ); Static Random Access Memory – SRAM

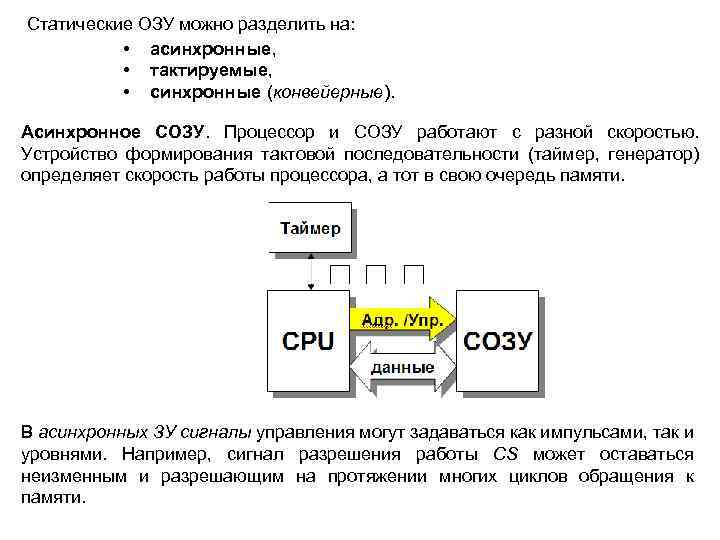

Статические ОЗУ можно разделить на: • асинхронные, • тактируемые, • синхронные (конвейерные). Асинхронное СОЗУ. Процессор и СОЗУ работают с разной скоростью. Устройство формирования тактовой последовательности (таймер, генератор) определяет скорость работы процессора, а тот в свою очередь памяти. В асинхронных ЗУ сигналы управления могут задаваться как импульсами, так и уровнями. Например, сигнал разрешения работы CS может оставаться неизменным и разрешающим на протяжении многих циклов обращения к памяти.

Статические ОЗУ можно разделить на: • асинхронные, • тактируемые, • синхронные (конвейерные). Асинхронное СОЗУ. Процессор и СОЗУ работают с разной скоростью. Устройство формирования тактовой последовательности (таймер, генератор) определяет скорость работы процессора, а тот в свою очередь памяти. В асинхронных ЗУ сигналы управления могут задаваться как импульсами, так и уровнями. Например, сигнал разрешения работы CS может оставаться неизменным и разрешающим на протяжении многих циклов обращения к памяти.

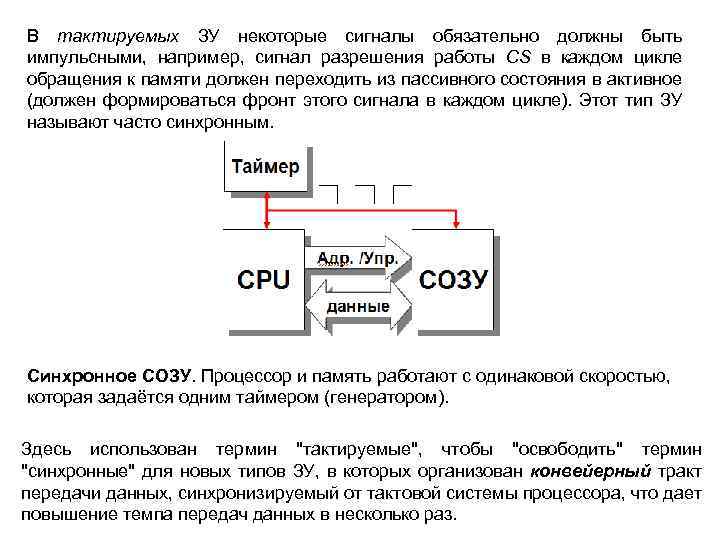

В тактируемых ЗУ некоторые сигналы обязательно должны быть импульсными, например, сигнал разрешения работы CS в каждом цикле обращения к памяти должен переходить из пассивного состояния в активное (должен формироваться фронт этого сигнала в каждом цикле). Этот тип ЗУ называют часто синхронным. Синхронное СОЗУ. Процессор и память работают с одинаковой скоростью, которая задаётся одним таймером (генератором). Здесь использован термин "тактируемые", чтобы "освободить" термин "синхронные" для новых типов ЗУ, в которых организован конвейерный тракт передачи данных, синхронизируемый от тактовой системы процессора, что дает повышение темпа передач данных в несколько раз.

В тактируемых ЗУ некоторые сигналы обязательно должны быть импульсными, например, сигнал разрешения работы CS в каждом цикле обращения к памяти должен переходить из пассивного состояния в активное (должен формироваться фронт этого сигнала в каждом цикле). Этот тип ЗУ называют часто синхронным. Синхронное СОЗУ. Процессор и память работают с одинаковой скоростью, которая задаётся одним таймером (генератором). Здесь использован термин "тактируемые", чтобы "освободить" термин "синхронные" для новых типов ЗУ, в которых организован конвейерный тракт передачи данных, синхронизируемый от тактовой системы процессора, что дает повышение темпа передач данных в несколько раз.

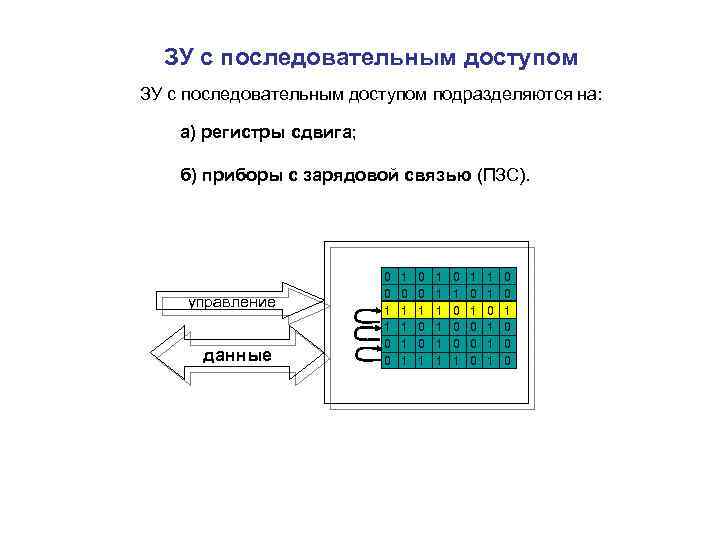

ЗУ с последовательным доступом подразделяются на: а) регистры сдвига; б) приборы с зарядовой связью (ПЗС). управление данные 0 0 1 1 1 1 0 0 1 1 1 1 0 1 0 0 0 1 1 1 0 0 0

ЗУ с последовательным доступом подразделяются на: а) регистры сдвига; б) приборы с зарядовой связью (ПЗС). управление данные 0 0 1 1 1 1 0 0 1 1 1 1 0 1 0 0 0 1 1 1 0 0 0

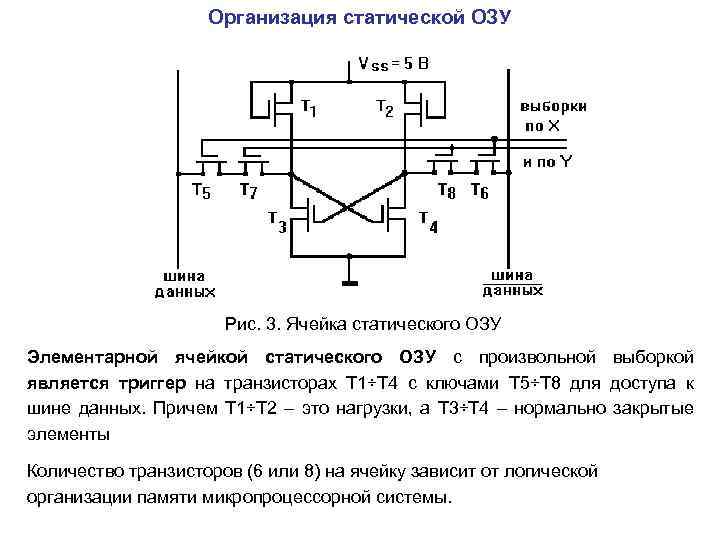

Организация статической ОЗУ Рис. 3. Ячейка статического ОЗУ Элементарной ячейкой статического ОЗУ с произвольной выборкой является триггер на транзисторах Т 1÷Т 4 с ключами Т 5÷Т 8 для доступа к шине данных. Причем Т 1÷Т 2 – это нагрузки, а Т 3÷Т 4 – нормально закрытые элементы Количество транзисторов (6 или 8) на ячейку зависит от логической организации памяти микропроцессорной системы.

Организация статической ОЗУ Рис. 3. Ячейка статического ОЗУ Элементарной ячейкой статического ОЗУ с произвольной выборкой является триггер на транзисторах Т 1÷Т 4 с ключами Т 5÷Т 8 для доступа к шине данных. Причем Т 1÷Т 2 – это нагрузки, а Т 3÷Т 4 – нормально закрытые элементы Количество транзисторов (6 или 8) на ячейку зависит от логической организации памяти микропроцессорной системы.

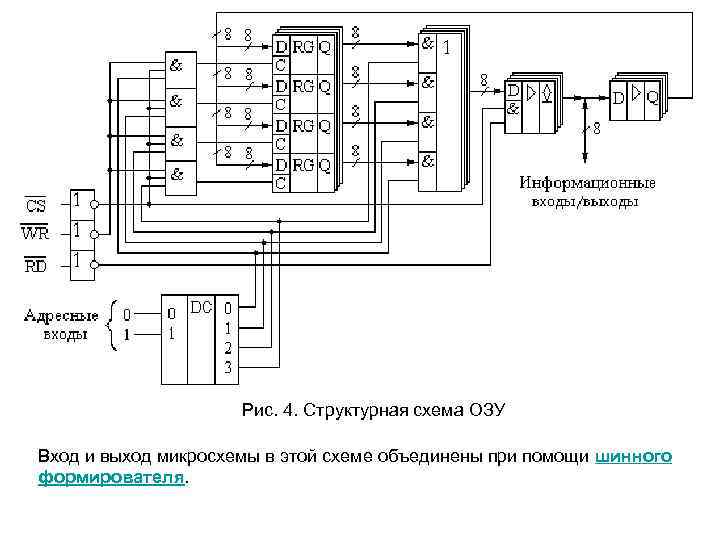

Рис. 4. Структурная схема ОЗУ Вход и выход микросхемы в этой схеме объединены при помощи шинного формирователя.

Рис. 4. Структурная схема ОЗУ Вход и выход микросхемы в этой схеме объединены при помощи шинного формирователя.

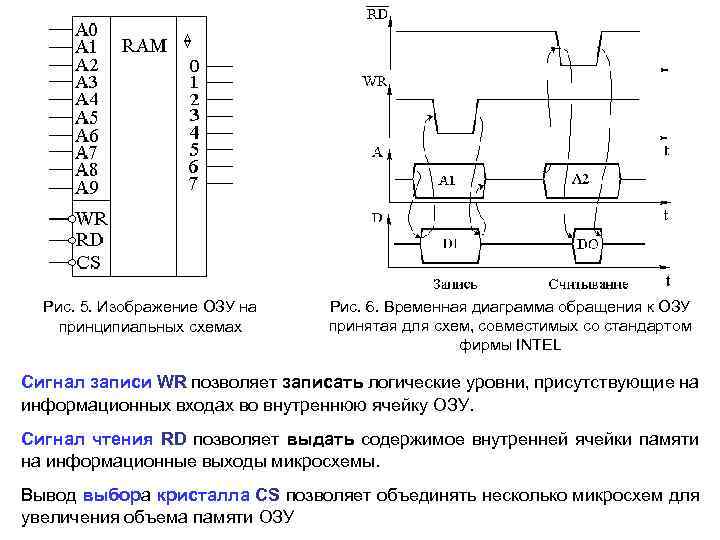

Рис. 5. Изображение ОЗУ на принципиальных схемах Рис. 6. Временная диаграмма обращения к ОЗУ принятая для схем, совместимых со стандартом фирмы INTEL Сигнал записи WR позволяет записать логические уровни, присутствующие на информационных входах во внутреннюю ячейку ОЗУ. Сигнал чтения RD позволяет выдать содержимое внутренней ячейки памяти на информационные выходы микросхемы. Вывод выбора кристалла CS позволяет объединять несколько микросхем для увеличения объема памяти ОЗУ

Рис. 5. Изображение ОЗУ на принципиальных схемах Рис. 6. Временная диаграмма обращения к ОЗУ принятая для схем, совместимых со стандартом фирмы INTEL Сигнал записи WR позволяет записать логические уровни, присутствующие на информационных входах во внутреннюю ячейку ОЗУ. Сигнал чтения RD позволяет выдать содержимое внутренней ячейки памяти на информационные выходы микросхемы. Вывод выбора кристалла CS позволяет объединять несколько микросхем для увеличения объема памяти ОЗУ

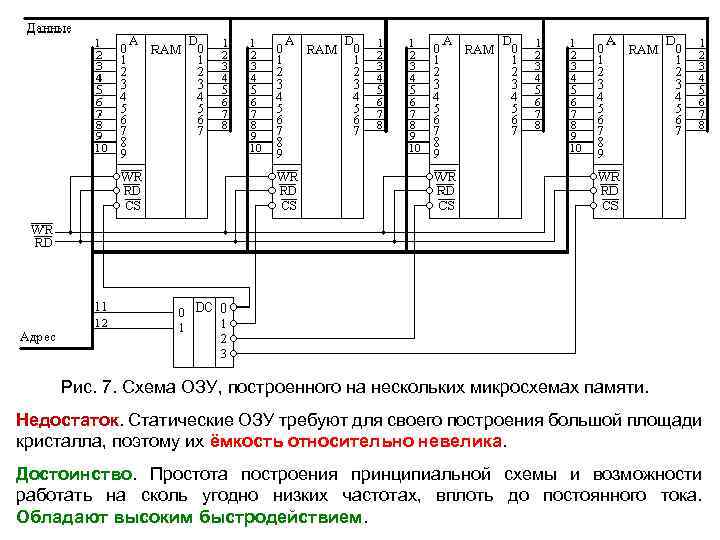

Рис. 7. Схема ОЗУ, построенного на нескольких микросхемах памяти. Недостаток. Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их ёмкость относительно невелика. Достоинство. Простота построения принципиальной схемы и возможности работать на сколь угодно низких частотах, вплоть до постоянного тока. Обладают высоким быстродействием.

Рис. 7. Схема ОЗУ, построенного на нескольких микросхемах памяти. Недостаток. Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их ёмкость относительно невелика. Достоинство. Простота построения принципиальной схемы и возможности работать на сколь угодно низких частотах, вплоть до постоянного тока. Обладают высоким быстродействием.

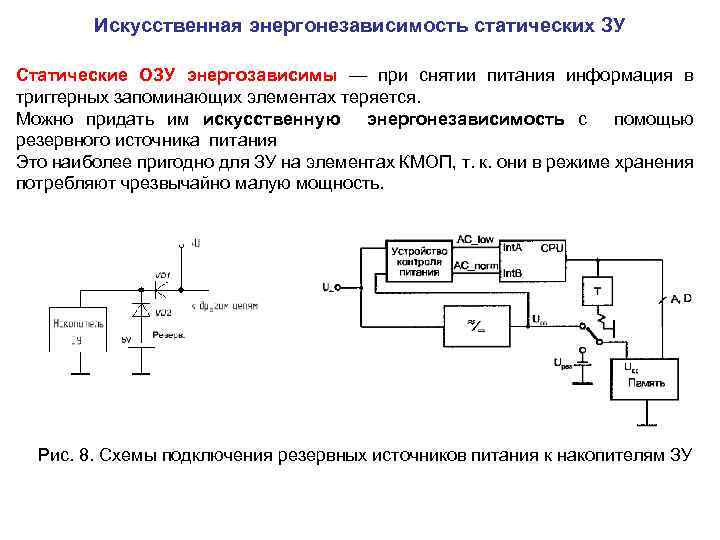

Искусственная энергонезависимость статических ЗУ Статические ОЗУ энергозависимы — при снятии питания информация в триггерных запоминающих элементах теряется. Можно придать им искусственную энергонезависимость с помощью резервного источника питания Это наиболее пригодно для ЗУ на элементах КМОП, т. к. они в режиме хранения потребляют чрезвычайно малую мощность. Рис. 8. Схемы подключения резервных источников питания к накопителям ЗУ

Искусственная энергонезависимость статических ЗУ Статические ОЗУ энергозависимы — при снятии питания информация в триггерных запоминающих элементах теряется. Можно придать им искусственную энергонезависимость с помощью резервного источника питания Это наиболее пригодно для ЗУ на элементах КМОП, т. к. они в режиме хранения потребляют чрезвычайно малую мощность. Рис. 8. Схемы подключения резервных источников питания к накопителям ЗУ

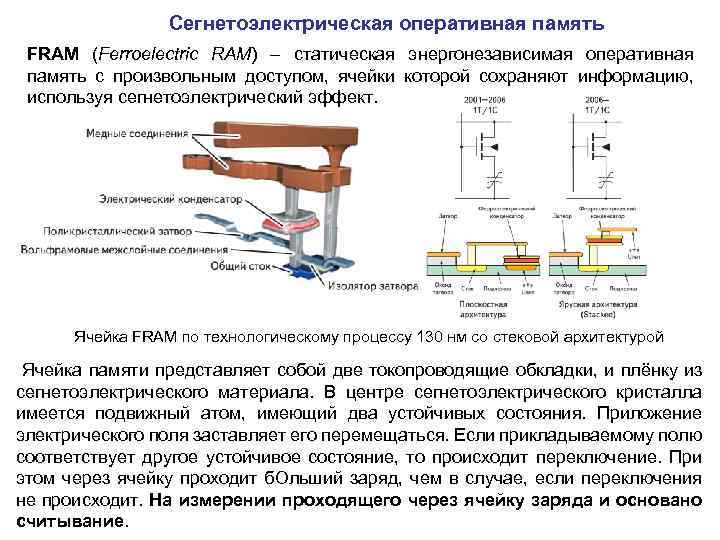

Сегнетоэлектрическая оперативная память FRAM (Ferroelectric RAM) – статическая энергонезависимая оперативная память с произвольным доступом, ячейки которой сохраняют информацию, используя сегнетоэлектрический эффект. Ячейка FRAM по технологическому процессу 130 нм со стековой архитектурой Ячейка памяти представляет собой две токопроводящие обкладки, и плёнку из сегнетоэлектрического материала. В центре сегнетоэлектрического кристалла имеется подвижный атом, имеющий два устойчивых состояния. Приложение электрического поля заставляет его перемещаться. Если прикладываемому полю соответствует другое устойчивое состояние, то происходит переключение. При этом через ячейку проходит б. Ольший заряд, чем в случае, если переключения не происходит. На измерении проходящего через ячейку заряда и основано считывание.

Сегнетоэлектрическая оперативная память FRAM (Ferroelectric RAM) – статическая энергонезависимая оперативная память с произвольным доступом, ячейки которой сохраняют информацию, используя сегнетоэлектрический эффект. Ячейка FRAM по технологическому процессу 130 нм со стековой архитектурой Ячейка памяти представляет собой две токопроводящие обкладки, и плёнку из сегнетоэлектрического материала. В центре сегнетоэлектрического кристалла имеется подвижный атом, имеющий два устойчивых состояния. Приложение электрического поля заставляет его перемещаться. Если прикладываемому полю соответствует другое устойчивое состояние, то происходит переключение. При этом через ячейку проходит б. Ольший заряд, чем в случае, если переключения не происходит. На измерении проходящего через ячейку заряда и основано считывание.

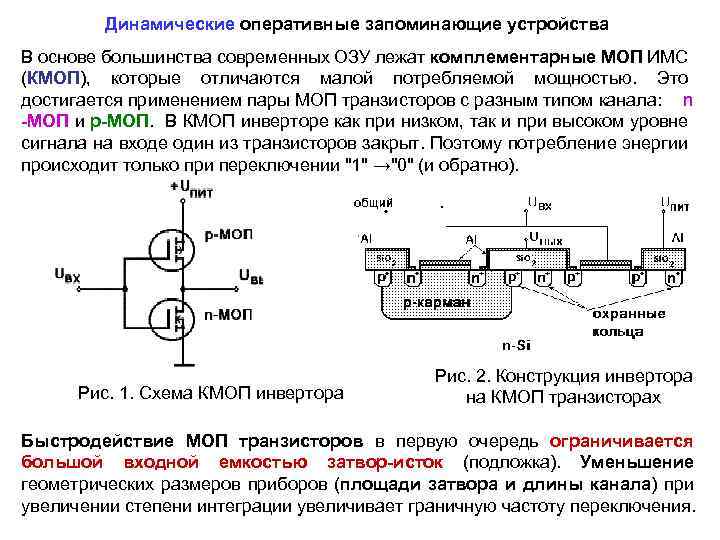

Динамические оперативные запоминающие устройства В основе большинства современных ОЗУ лежат комплементарные МОП ИМС (КМОП), которые отличаются малой потребляемой мощностью. Это достигается применением пары МОП транзисторов с разным типом канала: n -МОП и p-МОП. В КМОП инверторе как при низком, так и при высоком уровне сигнала на входе один из транзисторов закрыт. Поэтому потребление энергии происходит только при переключении "1" →"0" (и обратно). Рис. 1. Схема КМОП инвертора Рис. 2. Конструкция инвертора на КМОП транзисторах Быстродействие МОП транзисторов в первую очередь ограничивается большой входной емкостью затвор-исток (подложка). Уменьшение геометрических размеров приборов (площади затвора и длины канала) при увеличении степени интеграции увеличивает граничную частоту переключения.

Динамические оперативные запоминающие устройства В основе большинства современных ОЗУ лежат комплементарные МОП ИМС (КМОП), которые отличаются малой потребляемой мощностью. Это достигается применением пары МОП транзисторов с разным типом канала: n -МОП и p-МОП. В КМОП инверторе как при низком, так и при высоком уровне сигнала на входе один из транзисторов закрыт. Поэтому потребление энергии происходит только при переключении "1" →"0" (и обратно). Рис. 1. Схема КМОП инвертора Рис. 2. Конструкция инвертора на КМОП транзисторах Быстродействие МОП транзисторов в первую очередь ограничивается большой входной емкостью затвор-исток (подложка). Уменьшение геометрических размеров приборов (площади затвора и длины канала) при увеличении степени интеграции увеличивает граничную частоту переключения.

Динамические запоминающие устройства Рис. 8. Запоминающая ячейка динамического ОЗУ. В динамических ЗУ необходима постоянная регенерация информации. Но для хранения одного бита в динамическом оперативном запоминающем устройстве (ДОЗУ) нужны всего 1 -2 транзистора и накопительный конденсатор. В микросхеме динамического ОЗУ есть один или несколько тактовых генераторов и логическая схема для восстановления информационного заряда, стекающего с конденсатора. Это несколько усложняет конструкцию ИМС.

Динамические запоминающие устройства Рис. 8. Запоминающая ячейка динамического ОЗУ. В динамических ЗУ необходима постоянная регенерация информации. Но для хранения одного бита в динамическом оперативном запоминающем устройстве (ДОЗУ) нужны всего 1 -2 транзистора и накопительный конденсатор. В микросхеме динамического ОЗУ есть один или несколько тактовых генераторов и логическая схема для восстановления информационного заряда, стекающего с конденсатора. Это несколько усложняет конструкцию ИМС.

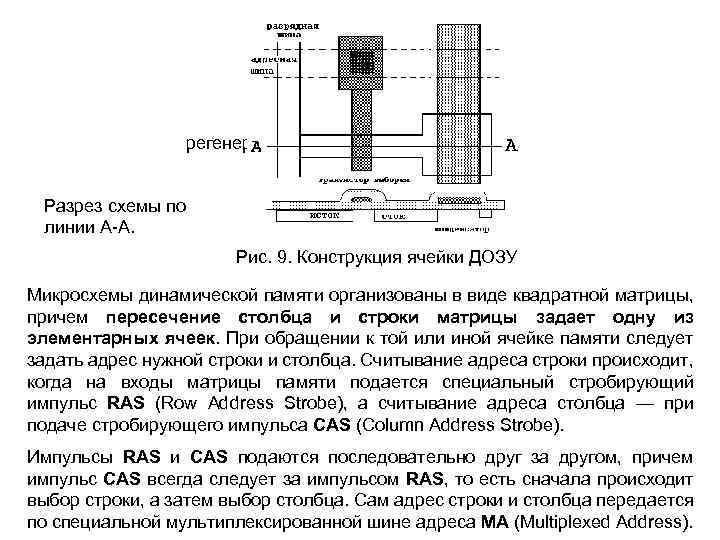

регенерация Разрез схемы по линии А-А. Рис. 9. Конструкция ячейки ДОЗУ Микросхемы динамической памяти организованы в виде квадратной матрицы, причем пересечение столбца и строки матрицы задает одну из элементарных ячеек. При обращении к той или иной ячейке памяти следует задать адрес нужной строки и столбца. Считывание адреса строки происходит, когда на входы матрицы памяти подается специальный стробирующий импульс RAS (Row Address Strobe), а считывание адреса столбца — при подаче стробирующего импульса CAS (Column Address Strobe). Импульсы RAS и CAS подаются последовательно друг за другом, причем импульс CAS всегда следует за импульсом RAS, то есть сначала происходит выбор строки, а затем выбор столбца. Сам адрес строки и столбца передается по специальной мультиплексированной шине адреса MA (Multiplexed Address).

регенерация Разрез схемы по линии А-А. Рис. 9. Конструкция ячейки ДОЗУ Микросхемы динамической памяти организованы в виде квадратной матрицы, причем пересечение столбца и строки матрицы задает одну из элементарных ячеек. При обращении к той или иной ячейке памяти следует задать адрес нужной строки и столбца. Считывание адреса строки происходит, когда на входы матрицы памяти подается специальный стробирующий импульс RAS (Row Address Strobe), а считывание адреса столбца — при подаче стробирующего импульса CAS (Column Address Strobe). Импульсы RAS и CAS подаются последовательно друг за другом, причем импульс CAS всегда следует за импульсом RAS, то есть сначала происходит выбор строки, а затем выбор столбца. Сам адрес строки и столбца передается по специальной мультиплексированной шине адреса MA (Multiplexed Address).

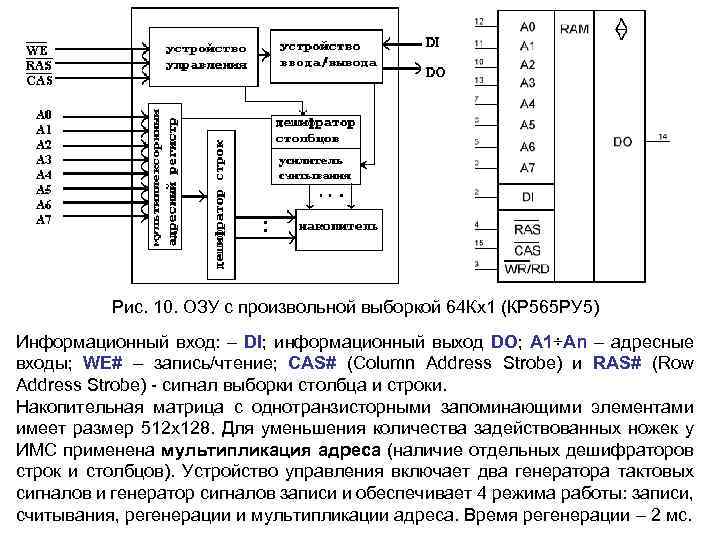

Рис. 10. ОЗУ с произвольной выборкой 64 Кx 1 (КР 565 РУ 5) Информационный вход: – DI; информационный выход DO; A 1÷An – адресные входы; WE# – запись/чтение; CAS# (Column Address Strobe) и RAS# (Row Address Strobe) - сигнал выборки столбца и строки. Накопительная матрица с однотранзисторными запоминающими элементами имеет размер 512 x 128. Для уменьшения количества задействованных ножек у ИМС применена мультипликация адреса (наличие отдельных дешифраторов строк и столбцов). Устройство управления включает два генератора тактовых сигналов и генератор сигналов записи и обеспечивает 4 режима работы: записи, считывания, регенерации и мультипликации адреса. Время регенерации – 2 мс.

Рис. 10. ОЗУ с произвольной выборкой 64 Кx 1 (КР 565 РУ 5) Информационный вход: – DI; информационный выход DO; A 1÷An – адресные входы; WE# – запись/чтение; CAS# (Column Address Strobe) и RAS# (Row Address Strobe) - сигнал выборки столбца и строки. Накопительная матрица с однотранзисторными запоминающими элементами имеет размер 512 x 128. Для уменьшения количества задействованных ножек у ИМС применена мультипликация адреса (наличие отдельных дешифраторов строк и столбцов). Устройство управления включает два генератора тактовых сигналов и генератор сигналов записи и обеспечивает 4 режима работы: записи, считывания, регенерации и мультипликации адреса. Время регенерации – 2 мс.

Характеристики динамической памяти Главная характеристика – пропускная способность, то есть максимальное количество данных, которое можно считать из памяти или записать в память в единицу времени. Для того чтобы определить пропускную способность памяти, нужно частоту системной шины умножить на количество байт, передаваемых за один такт. Память SDRAM имеет 64 -битную (8 -байтную) шину данных. RAS to CAS Delay (t. RCD) – задержка подачи сигнала CAS относительно сигнала RAS измеряемый в тактах системной шины. CAS Latency (t. CL) – задержка по времени в тактах, которая происходит с момента подачи сигнала CAS до выдачи первого элемента данных на шину. Каждый последующий элемент данных появляется на шине данных в очередном такте. У SDRAM-памяти эта задержка составляет 2 или 3 такта. Завершение цикла обращения к банку памяти осуществляется подачей команды деактивации. Эта команда подается за один или за два такта перед выдачей последнего элемента данных. Время деактивации RAS Precharge (t. RP) также измеряется в тактах и может быть равно двум или трем. Эти задержки определяют так называемый тайминг памяти, записываемый в виде последовательности t. CL – t. RCD – t. RP. Чем меньше тайминг, тем более быстродействующей является память. Память с таймингом 3 -3 -3 менее быстродействующая, чем память с таймингом 2 -2 -2.

Характеристики динамической памяти Главная характеристика – пропускная способность, то есть максимальное количество данных, которое можно считать из памяти или записать в память в единицу времени. Для того чтобы определить пропускную способность памяти, нужно частоту системной шины умножить на количество байт, передаваемых за один такт. Память SDRAM имеет 64 -битную (8 -байтную) шину данных. RAS to CAS Delay (t. RCD) – задержка подачи сигнала CAS относительно сигнала RAS измеряемый в тактах системной шины. CAS Latency (t. CL) – задержка по времени в тактах, которая происходит с момента подачи сигнала CAS до выдачи первого элемента данных на шину. Каждый последующий элемент данных появляется на шине данных в очередном такте. У SDRAM-памяти эта задержка составляет 2 или 3 такта. Завершение цикла обращения к банку памяти осуществляется подачей команды деактивации. Эта команда подается за один или за два такта перед выдачей последнего элемента данных. Время деактивации RAS Precharge (t. RP) также измеряется в тактах и может быть равно двум или трем. Эти задержки определяют так называемый тайминг памяти, записываемый в виде последовательности t. CL – t. RCD – t. RP. Чем меньше тайминг, тем более быстродействующей является память. Память с таймингом 3 -3 -3 менее быстродействующая, чем память с таймингом 2 -2 -2.

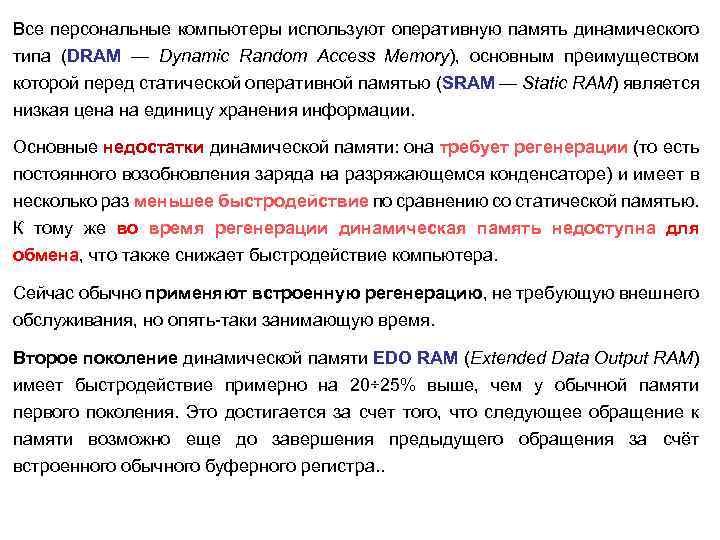

Все персональные компьютеры используют оперативную память динамического типа (DRAM — Dynamic Random Access Memory), основным преимуществом которой перед статической оперативной памятью (SRAM — Static RAM) является низкая цена на единицу хранения информации. Основные недостатки динамической памяти: она требует регенерации (то есть постоянного возобновления заряда на разряжающемся конденсаторе) и имеет в несколько раз меньшее быстродействие по сравнению со статической памятью. К тому же во время регенерации динамическая память недоступна для обмена, что также снижает быстродействие компьютера. Сейчас обычно применяют встроенную регенерацию, не требующую внешнего обслуживания, но опять-таки занимающую время. Второе поколение динамической памяти EDO RAM (Extended Data Output RAM) имеет быстродействие примерно на 20÷ 25% выше, чем у обычной памяти первого поколения. Это достигается за счет того, что следующее обращение к памяти возможно еще до завершения предыдущего обращения за счёт встроенного обычного буферного регистра. .

Все персональные компьютеры используют оперативную память динамического типа (DRAM — Dynamic Random Access Memory), основным преимуществом которой перед статической оперативной памятью (SRAM — Static RAM) является низкая цена на единицу хранения информации. Основные недостатки динамической памяти: она требует регенерации (то есть постоянного возобновления заряда на разряжающемся конденсаторе) и имеет в несколько раз меньшее быстродействие по сравнению со статической памятью. К тому же во время регенерации динамическая память недоступна для обмена, что также снижает быстродействие компьютера. Сейчас обычно применяют встроенную регенерацию, не требующую внешнего обслуживания, но опять-таки занимающую время. Второе поколение динамической памяти EDO RAM (Extended Data Output RAM) имеет быстродействие примерно на 20÷ 25% выше, чем у обычной памяти первого поколения. Это достигается за счет того, что следующее обращение к памяти возможно еще до завершения предыдущего обращения за счёт встроенного обычного буферного регистра. .

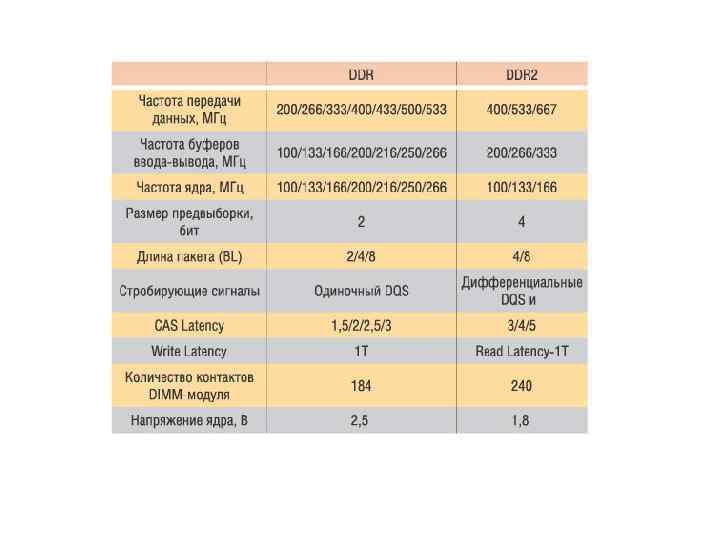

Третье поколение динамической памяти – синхронная динамическая память SDRAM (Synchronous DRAM) или SDR (Single Data Rate) Вся современная память является SDRAM, предназначена для работы с системными частотами 100 и 133, 166 и 200, 216, 250 и 266 МГц.

Третье поколение динамической памяти – синхронная динамическая память SDRAM (Synchronous DRAM) или SDR (Single Data Rate) Вся современная память является SDRAM, предназначена для работы с системными частотами 100 и 133, 166 и 200, 216, 250 и 266 МГц.

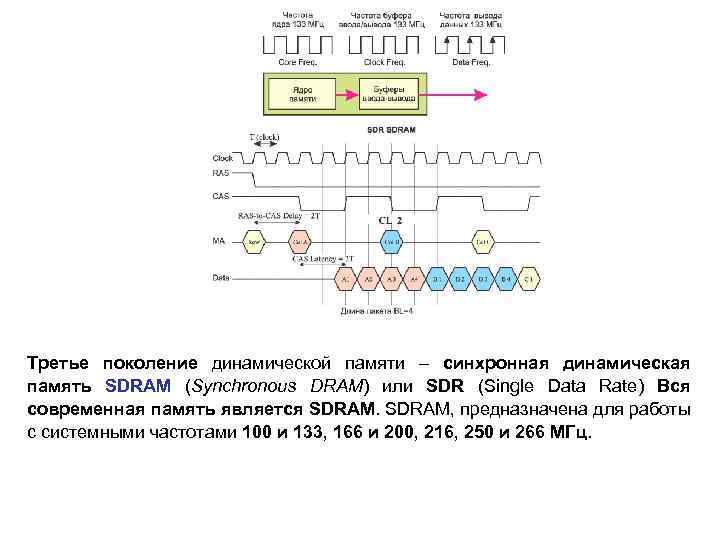

Рис. 11. Память DDR-400, выборка данных по принципу 2 n-prefetch Развитием SDRAM является ещё более быстродействующая память — DDR (Double Data Rate) – частота до 400 МГц, и память RDRAM (частота до 1 ГГц и даже выше). В стандарте DDR реализована схема выборки 2 -х битов за такт по внутренней шине данных (за счет применения мультиплексора/демультиплексора типа 2 -1), позволяющую функционировать микросхемам памяти на частоте, вдвое меньшей относительно эффективной частоты внешней шины данных. Так, микросхемы модулей DDR-400 функционируют на частоте 200 МГц.

Рис. 11. Память DDR-400, выборка данных по принципу 2 n-prefetch Развитием SDRAM является ещё более быстродействующая память — DDR (Double Data Rate) – частота до 400 МГц, и память RDRAM (частота до 1 ГГц и даже выше). В стандарте DDR реализована схема выборки 2 -х битов за такт по внутренней шине данных (за счет применения мультиплексора/демультиплексора типа 2 -1), позволяющую функционировать микросхемам памяти на частоте, вдвое меньшей относительно эффективной частоты внешней шины данных. Так, микросхемы модулей DDR-400 функционируют на частоте 200 МГц.

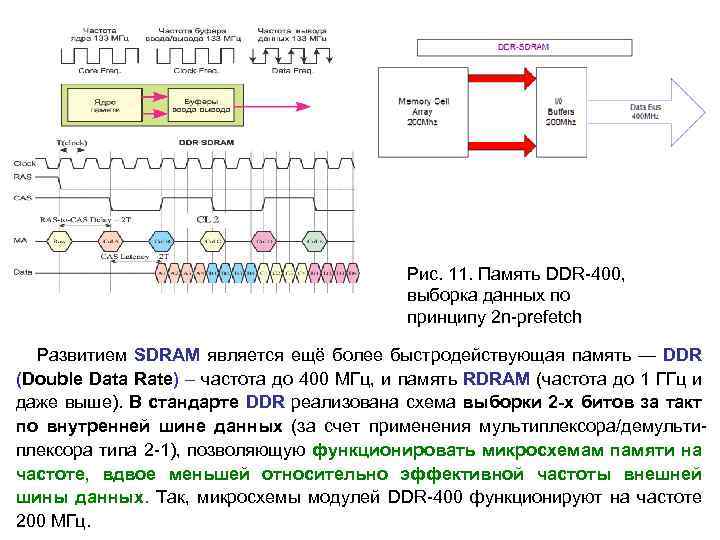

Рис. 12. Память DDR 2 -400, выборка данных по принципу 4 n-prefetch В стандарте DDR 2 реализована схема выборки 4 -х битов за такт (т. е. вводится более сложный мультиплексор типа 4 -1 Преимущества— выборка 4 -х битов за такт позволяет достигать пропускную способность памяти, эквивалентную равночастотной DDR при вдвое меньшей собственной частоте микросхем памяти (микросхемы модулей DDR 2 -400 функционируют на частоте 100 МГц), что, в свою очередь, способствует снижению энергопотребления модулей памяти. Недостаток — усложнение схемы преобразования данных непременно сопровождается возрастанием задержек – таймингов.

Рис. 12. Память DDR 2 -400, выборка данных по принципу 4 n-prefetch В стандарте DDR 2 реализована схема выборки 4 -х битов за такт (т. е. вводится более сложный мультиплексор типа 4 -1 Преимущества— выборка 4 -х битов за такт позволяет достигать пропускную способность памяти, эквивалентную равночастотной DDR при вдвое меньшей собственной частоте микросхем памяти (микросхемы модулей DDR 2 -400 функционируют на частоте 100 МГц), что, в свою очередь, способствует снижению энергопотребления модулей памяти. Недостаток — усложнение схемы преобразования данных непременно сопровождается возрастанием задержек – таймингов.

Микросхем DDR 2, электрически несовместимы с DDR! Модули памяти типа DDR 2 производятся в виде 240 -контактных модулей DIMM, электрически несовместимых со слотами для модулей памяти типа DDR (по количеству выводов, расстоянию между выводами и цоколевке модулей).

Микросхем DDR 2, электрически несовместимы с DDR! Модули памяти типа DDR 2 производятся в виде 240 -контактных модулей DIMM, электрически несовместимых со слотами для модулей памяти типа DDR (по количеству выводов, расстоянию между выводами и цоколевке модулей).