Оперативная память

Оперативная память

Электронная память o o o Оперативная память Кэш-память Постоянная память Полупостоянная память Буферная память Внешняя память

Электронная память o o o Оперативная память Кэш-память Постоянная память Полупостоянная память Буферная память Внешняя память

Оперативная (основная) память - Main Memory, RAM, ОЗУ Используется для оперативного обмена информацией (командами и данными) между процессором, внешней памятью и периферийными устройствами. Требования: • Большой объем • Быстродействие и производительность, позволяющие реализовать вычислительную мощность процессора • Высокая надежность хранения данных

Оперативная (основная) память - Main Memory, RAM, ОЗУ Используется для оперативного обмена информацией (командами и данными) между процессором, внешней памятью и периферийными устройствами. Требования: • Большой объем • Быстродействие и производительность, позволяющие реализовать вычислительную мощность процессора • Высокая надежность хранения данных

Кэш-память - Cache Memory, СОЗУ, сверхоперативная память Буфер между оперативной памятью и её «клиентами» процессором и другими абонентами системной шины. Информация в ней неадресуема, хранит копии блоков ОЗУ, к которым происходили последние обращения. Эффективность зависит от алгоритма кэширования.

Кэш-память - Cache Memory, СОЗУ, сверхоперативная память Буфер между оперативной памятью и её «клиентами» процессором и другими абонентами системной шины. Информация в ней неадресуема, хранит копии блоков ОЗУ, к которым происходили последние обращения. Эффективность зависит от алгоритма кэширования.

Постоянная память - ROM, ПЗУ Используется для энергонезависимого хранения системной информации. Требуемый объем невелик (BIOS PC/XT 8 Кб, сейчас 128 Кб – 2 Мб) Быстродействие ниже, чем у оперативной памяти В последнее время вытесняется флэш-памятью и другими видами энергонезависимой памяти (EEPROM, FRAM)

Постоянная память - ROM, ПЗУ Используется для энергонезависимого хранения системной информации. Требуемый объем невелик (BIOS PC/XT 8 Кб, сейчас 128 Кб – 2 Мб) Быстродействие ниже, чем у оперативной памяти В последнее время вытесняется флэш-памятью и другими видами энергонезависимой памяти (EEPROM, FRAM)

Полупостоянная память - В основном используется для хранения информации о конфигурации компьютера Небольшой объем (CMOS Memory + CMOS RTC несколько десятков байт) Сохранность данных CMOS обеспечивается маломощной внутренней батарейкой. Есть и энергонезависимая полупостоянная память (NV RAM)

Полупостоянная память - В основном используется для хранения информации о конфигурации компьютера Небольшой объем (CMOS Memory + CMOS RTC несколько десятков байт) Сохранность данных CMOS обеспечивается маломощной внутренней батарейкой. Есть и энергонезависимая полупостоянная память (NV RAM)

Буферная память - Разделяется между процессором (точнее, абонентами системной шины) и контроллерами различных устройств, например: • Видеопамять дисплейного адаптера • 16 -байтные FIFO-буферы COM-портов • 16 -мегабайтные (и более) кэш-буферы SCSI-адаптеров

Буферная память - Разделяется между процессором (точнее, абонентами системной шины) и контроллерами различных устройств, например: • Видеопамять дисплейного адаптера • 16 -байтные FIFO-буферы COM-портов • 16 -мегабайтные (и более) кэш-буферы SCSI-адаптеров

Внешняя память - Flash Drive и др. Высокое (для внешней памяти) быстродействие, однако высокая стоимость хранения информации и довольно медленная запись

Внешняя память - Flash Drive и др. Высокое (для внешней памяти) быстродействие, однако высокая стоимость хранения информации и довольно медленная запись

Построение оперативной памяти Основной груз оперативного хранения информации приходится на динамическую память, имеющую наилучшее сочетание объема, плотности упаковки, энергопотребления и цены. Однако она обладает невысоким быстродействием, и ей на помощь приходит статическая память. Мы обсудим: • Быстродействие и производительность памяти • Достоверность хранения информации • Идеи организации кэширования памяти

Построение оперативной памяти Основной груз оперативного хранения информации приходится на динамическую память, имеющую наилучшее сочетание объема, плотности упаковки, энергопотребления и цены. Однако она обладает невысоким быстродействием, и ей на помощь приходит статическая память. Мы обсудим: • Быстродействие и производительность памяти • Достоверность хранения информации • Идеи организации кэширования памяти

Быстродействие и производительность памяти Быстродействие памяти определяется временем выполнения операций записи и считывания данных Время доступа (access time) – задержка появления действительных данных на выходе памяти относительно начала цикла чтения Длительность цикла – минимальный период следующих друг за другом обращений к памяти (циклы чтения и записи могут быть различны) Длительность цикла = Время доступа + Время возврата к исходному состоянию

Быстродействие и производительность памяти Быстродействие памяти определяется временем выполнения операций записи и считывания данных Время доступа (access time) – задержка появления действительных данных на выходе памяти относительно начала цикла чтения Длительность цикла – минимальный период следующих друг за другом обращений к памяти (циклы чтения и записи могут быть различны) Длительность цикла = Время доступа + Время возврата к исходному состоянию

Быстродействие и производительность памяти Производительность памяти можно характеризовать как скорость потока записываемых или считываемых данных (Мб/с) Производительность памяти обычно характеризуют длительностью пакетных циклов чтения (Memory Burst Read Cycle). Она выражается числом тактов системной шины, требуемых для передачи порции данных в пакете (например, 53 -3 -3). Первое число характеризует латентность (latency) памяти – время ожидания данных, последующие – скорость передачи. Хороший результат: 5 -1 -1 -1 при частоте шины 100 или 133 МГц

Быстродействие и производительность памяти Производительность памяти можно характеризовать как скорость потока записываемых или считываемых данных (Мб/с) Производительность памяти обычно характеризуют длительностью пакетных циклов чтения (Memory Burst Read Cycle). Она выражается числом тактов системной шины, требуемых для передачи порции данных в пакете (например, 53 -3 -3). Первое число характеризует латентность (latency) памяти – время ожидания данных, последующие – скорость передачи. Хороший результат: 5 -1 -1 -1 при частоте шины 100 или 133 МГц

Быстродействие и производительность памяти Производительность подсистемы памяти зависит от: • Типа и быстродействия применяемых запоминающих элементов • Разрядности шины памяти • Некоторых «хитростей» архитектуры Производительность микросхем и модулей повышают за счет различных вариантов конвейеризации

Быстродействие и производительность памяти Производительность подсистемы памяти зависит от: • Типа и быстродействия применяемых запоминающих элементов • Разрядности шины памяти • Некоторых «хитростей» архитектуры Производительность микросхем и модулей повышают за счет различных вариантов конвейеризации

Быстродействие и производительность памяти Разрядность шины памяти – это количество байт (бит), для которых операция чтения или записи может быть выполнена одновременно. Обычно согласуется с разрядностью внешней шины процессора (8088 - 1 байт; 8086, 80286, 386 SX – 2 байта; 386 DX, 486 – 4 байта, Pentium и выше – 8 байт).

Быстродействие и производительность памяти Разрядность шины памяти – это количество байт (бит), для которых операция чтения или записи может быть выполнена одновременно. Обычно согласуется с разрядностью внешней шины процессора (8088 - 1 байт; 8086, 80286, 386 SX – 2 байта; 386 DX, 486 – 4 байта, Pentium и выше – 8 байт).

Быстродействие и производительность памяти Банком памяти называют комплект микросхем или модулей ( а также их посадочных мест – «кроваток» для микросхем, слотов для SIMM или DIMM), обеспечивающий требуемую для данной системы разрядность хранимых данных. Работоспособным может быть только полностью заполненный банк (486 – SIMM 72 или четверка SIMM-30, 5 -6 поколение – пара SIMM-72 или один DIMM или RIMM, Pentium 4 и платы с чипсетом i 850 – пара RIMM). Микросхемы SDRAM имеют внутреннюю многобанковую организацию Чередование банков (bank interleaving) – смежные блоки данных располагаются поочередно в разных банках, и при последовательном обращении к данным банки будут работать поочередно, причем активная фаза обращения к одному может выполняться во время фазы восстановления другого

Быстродействие и производительность памяти Банком памяти называют комплект микросхем или модулей ( а также их посадочных мест – «кроваток» для микросхем, слотов для SIMM или DIMM), обеспечивающий требуемую для данной системы разрядность хранимых данных. Работоспособным может быть только полностью заполненный банк (486 – SIMM 72 или четверка SIMM-30, 5 -6 поколение – пара SIMM-72 или один DIMM или RIMM, Pentium 4 и платы с чипсетом i 850 – пара RIMM). Микросхемы SDRAM имеют внутреннюю многобанковую организацию Чередование банков (bank interleaving) – смежные блоки данных располагаются поочередно в разных банках, и при последовательном обращении к данным банки будут работать поочередно, причем активная фаза обращения к одному может выполняться во время фазы восстановления другого

Достоверность хранения данных Современные технологии позволяют выпускать высоконадежные микросхемы памяти, у которых при правильной эксплуатации (напряжение питания, температура, временная диаграмма, уровни сигналов, нагрузка на выходные шины…) вероятность ошибки достаточно мала, но всё-таки не нулевая Отказ ячейки памяти – потеря её работоспособности, обычно требующая замены элемента, однако возможно и самопроизвольное восстановление работоспособности. Отказы происходят при неисправности контакта или нарушении условий эксплуатации Сбой может произойти и в исправной микросхеме (например, при пролете ионизирующей частицы). Следующая же запись в ячейку произойдет нормально

Достоверность хранения данных Современные технологии позволяют выпускать высоконадежные микросхемы памяти, у которых при правильной эксплуатации (напряжение питания, температура, временная диаграмма, уровни сигналов, нагрузка на выходные шины…) вероятность ошибки достаточно мала, но всё-таки не нулевая Отказ ячейки памяти – потеря её работоспособности, обычно требующая замены элемента, однако возможно и самопроизвольное восстановление работоспособности. Отказы происходят при неисправности контакта или нарушении условий эксплуатации Сбой может произойти и в исправной микросхеме (например, при пролете ионизирующей частицы). Следующая же запись в ячейку произойдет нормально

Достоверность хранения данных Контроль четности: каждый байт памяти сопровождается битом паритета (дополняющим количество единиц до нечетного). Значение бита паритета аппаратно генерируется при записи и проверяется при считывании. При обнаружении ошибки вырабатывается немаскируемое прерывание (NMI). Специальными битами конфигурационных регистров его вырабатывание можно запретить или игнорировать. Правильные биты паритета генерируются во время теста POST. Fake Parity (Parity Generator) – логическая схема сумматора по модулю два, используемая в схемах памяти без контроля паритета для обмана плат, требующих наличие бита паритета (обычно модули называются BP, VT, GSM, MPEC)

Достоверность хранения данных Контроль четности: каждый байт памяти сопровождается битом паритета (дополняющим количество единиц до нечетного). Значение бита паритета аппаратно генерируется при записи и проверяется при считывании. При обнаружении ошибки вырабатывается немаскируемое прерывание (NMI). Специальными битами конфигурационных регистров его вырабатывание можно запретить или игнорировать. Правильные биты паритета генерируются во время теста POST. Fake Parity (Parity Generator) – логическая схема сумматора по модулю два, используемая в схемах памяти без контроля паритета для обмана плат, требующих наличие бита паритета (обычно модули называются BP, VT, GSM, MPEC)

Достоверность хранения данных ECC Memory (Error Checking and Correcting) – память с обнаружением и исправлением ошибок – для каждого записываемого слова вычисляется функция свертки, результат которой разрядностью в несколько бит также хранится в памяти (для 64 -битного слова 7 -8 дополнительных бит) ECC-память работает медленнее неконтролируемой Контроль осуществляет чипсет и его реакцию можно задать настройками ECC используется в процессорах P 6 и выше для контроля кэша второго уровня Достоверность информации, хранимой в постоянной и полупостоянной памяти проверяется с помощью контрольной суммы (checksum) во время теста POST

Достоверность хранения данных ECC Memory (Error Checking and Correcting) – память с обнаружением и исправлением ошибок – для каждого записываемого слова вычисляется функция свертки, результат которой разрядностью в несколько бит также хранится в памяти (для 64 -битного слова 7 -8 дополнительных бит) ECC-память работает медленнее неконтролируемой Контроль осуществляет чипсет и его реакцию можно задать настройками ECC используется в процессорах P 6 и выше для контроля кэша второго уровня Достоверность информации, хранимой в постоянной и полупостоянной памяти проверяется с помощью контрольной суммы (checksum) во время теста POST

Кэширование оперативной памяти Из-за того, что основная память компьютеров реализуются на относительно медленной динамической памяти (DRAM), процессор простаивает, появляются такты ожидания. Компромисс состоит в иерархической организации оперативной памяти – основная память на DRAM и относительно небольшая кэш-память на быстродействующих микросхемах SRAM. Кэш ( «тайник» , «заначка» ) является дополнительным хранилищем копий блоков информации из основной памяти, вероятность обращения к которым в ближайшее время велика. Он хранит ограниченное количество блоков данных и каталог (cache directory) – список их текущего соответствия областям основной памяти. Кэшироваться может и не вся оперативная память (настройками регистров чипсета или процессора некоторые области памяти могут быть объявлены некэшируемыми).

Кэширование оперативной памяти Из-за того, что основная память компьютеров реализуются на относительно медленной динамической памяти (DRAM), процессор простаивает, появляются такты ожидания. Компромисс состоит в иерархической организации оперативной памяти – основная память на DRAM и относительно небольшая кэш-память на быстродействующих микросхемах SRAM. Кэш ( «тайник» , «заначка» ) является дополнительным хранилищем копий блоков информации из основной памяти, вероятность обращения к которым в ближайшее время велика. Он хранит ограниченное количество блоков данных и каталог (cache directory) – список их текущего соответствия областям основной памяти. Кэшироваться может и не вся оперативная память (настройками регистров чипсета или процессора некоторые области памяти могут быть объявлены некэшируемыми).

Кэширование оперативной памяти При каждом обращении к памяти контроллер кэш-памяти по каталогу проверяет, есть ли действительная копия требуемых данных в кэше. Если есть, то это случай кэш-попадания (cache hit) и данные берутся их кэша. Если нет, это случай кэшпромаха (cache miss): данные берутся из основной памяти и в соответствии с алгоритмом кэширования блок данных из основной памяти замещает какой-либо блок кэша. Обращение к основной памяти может начинаться одновременно с поиском в каталоге (архитектура Look Aside) или только после фиксации промаха (архитектура Look Through).

Кэширование оперативной памяти При каждом обращении к памяти контроллер кэш-памяти по каталогу проверяет, есть ли действительная копия требуемых данных в кэше. Если есть, то это случай кэш-попадания (cache hit) и данные берутся их кэша. Если нет, это случай кэшпромаха (cache miss): данные берутся из основной памяти и в соответствии с алгоритмом кэширования блок данных из основной памяти замещает какой-либо блок кэша. Обращение к основной памяти может начинаться одновременно с поиском в каталоге (архитектура Look Aside) или только после фиксации промаха (архитектура Look Through).

Кэширование оперативной памяти Кэш в современных компьютерах строится по двух-, а иногда и трехуровневой системе: • Первичный кэш (Level 1 Cache, кэш первого уровня) – внутренний (Internal, Integrated) кэш процессоров 486+ (и некоторых моделей 386). 8 – 128 Кбайт, для повышение производительности используется раздельный • Вторичный кэш (Level 2 Cache, кэш второго уровня). Для процессоров вплоть до Pentium это внешний (External) кэш, установленный на системной плате. В P 6 и более мощных процессорах вторичный кэш расположен в одном корпусе с процессором • Кэшем третьего уровня оказывается кэш, установленный на системной плате с сокетом 7, когда в него устанавливают процессор AMD K 6 -3 со встроенным двухуровневым кэшем

Кэширование оперативной памяти Кэш в современных компьютерах строится по двух-, а иногда и трехуровневой системе: • Первичный кэш (Level 1 Cache, кэш первого уровня) – внутренний (Internal, Integrated) кэш процессоров 486+ (и некоторых моделей 386). 8 – 128 Кбайт, для повышение производительности используется раздельный • Вторичный кэш (Level 2 Cache, кэш второго уровня). Для процессоров вплоть до Pentium это внешний (External) кэш, установленный на системной плате. В P 6 и более мощных процессорах вторичный кэш расположен в одном корпусе с процессором • Кэшем третьего уровня оказывается кэш, установленный на системной плате с сокетом 7, когда в него устанавливают процессор AMD K 6 -3 со встроенным двухуровневым кэшем

Динамическая память

Динамическая память

Динамическая память – DRAM (Dynamic RAM) – получила свое название от принципа действия её запоминающих ячеек, которые выполнены в виде конденсаторов. При записи логической единицы в ячейку, конденсатор заряжается, а при записи нуля – разряжается. Схема считывания разряжает конденсатор через себя, и если заряд был ненулевым, подзаряжает его до прежнего уровня. При отсутствии обращений к ячейки в течении долгого времени за счет токов утечки ячейки конденсатор разряжается и информация теряется. Поэтому динамическая память требует периодического обращения ко всем ячейкам (в отличие от статической памяти). Это самая дешевая полупроводниковая память достаточно высокого быстродействия с умеренным энергопотреблением, используемая в качестве основной памяти компьютера.

Динамическая память – DRAM (Dynamic RAM) – получила свое название от принципа действия её запоминающих ячеек, которые выполнены в виде конденсаторов. При записи логической единицы в ячейку, конденсатор заряжается, а при записи нуля – разряжается. Схема считывания разряжает конденсатор через себя, и если заряд был ненулевым, подзаряжает его до прежнего уровня. При отсутствии обращений к ячейки в течении долгого времени за счет токов утечки ячейки конденсатор разряжается и информация теряется. Поэтому динамическая память требует периодического обращения ко всем ячейкам (в отличие от статической памяти). Это самая дешевая полупроводниковая память достаточно высокого быстродействия с умеренным энергопотреблением, используемая в качестве основной памяти компьютера.

Основы работы DRAM Запоминающие ячейки микросхем DRAM организованы в виде двумерной матрицы. Адрес строки и столбца передаются по мультиплексированной шине адреса и стробируется по спаду импульсов RAS# (Row Access Strobe) и CAS# (Column Access Strobe). Тип обращения определяется сигналами WE# и CAS#. При чтении данные на выходе появляются относительно начала цикла (сигнала RAS#) не раньше чем через время доступа (40 100 нс). За всю историю его удалось улучшить всего на порядок, а частота процессоров выросла гораздо больше. Поэтому разрыв между потребностями процессора и возможностями ячеек памяти увеличивается. Для преодоления этого разрыва, во-первых, увеличивают разрядность данных памяти, а во-вторых, строят вокруг массивов ячеек памяти разные хитрые оболочки.

Основы работы DRAM Запоминающие ячейки микросхем DRAM организованы в виде двумерной матрицы. Адрес строки и столбца передаются по мультиплексированной шине адреса и стробируется по спаду импульсов RAS# (Row Access Strobe) и CAS# (Column Access Strobe). Тип обращения определяется сигналами WE# и CAS#. При чтении данные на выходе появляются относительно начала цикла (сигнала RAS#) не раньше чем через время доступа (40 100 нс). За всю историю его удалось улучшить всего на порядок, а частота процессоров выросла гораздо больше. Поэтому разрыв между потребностями процессора и возможностями ячеек памяти увеличивается. Для преодоления этого разрыва, во-первых, увеличивают разрядность данных памяти, а во-вторых, строят вокруг массивов ячеек памяти разные хитрые оболочки.

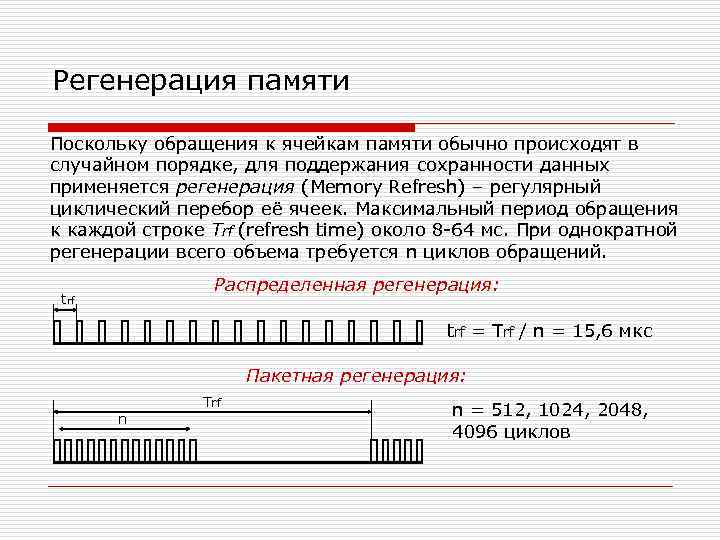

Регенерация памяти Поскольку обращения к ячейкам памяти обычно происходят в случайном порядке, для поддержания сохранности данных применяется регенерация (Memory Refresh) – регулярный циклический перебор её ячеек. Максимальный период обращения к каждой строке Trf (refresh time) около 8 -64 мс. При однократной регенерации всего объема требуется n циклов обращений. Распределенная регенерация: trf = Trf / n = 15, 6 мкс Пакетная регенерация: Trf n n = 512, 1024, 2048, 4096 циклов

Регенерация памяти Поскольку обращения к ячейкам памяти обычно происходят в случайном порядке, для поддержания сохранности данных применяется регенерация (Memory Refresh) – регулярный циклический перебор её ячеек. Максимальный период обращения к каждой строке Trf (refresh time) около 8 -64 мс. При однократной регенерации всего объема требуется n циклов обращений. Распределенная регенерация: trf = Trf / n = 15, 6 мкс Пакетная регенерация: Trf n n = 512, 1024, 2048, 4096 циклов

Регенерация памяти В современных компьютерах регенерацию основной памяти берет на себя чипсет, и его задача – по возможности использовать для регенерации циклы шины, не занятые ей абонентами. Контроллеры регенерации smart refresh ставят запросы на регенерацию в очередь, которую обслуживают в свободное для шины время или если запросов накопилось больше предельного количества. При использовании чередования банков целесообразно производить регенерацию одного во время полезного обращения к другому. Динамическая память в видеобуферах графических адаптеров регенерации, как правило, не требует (частота её чтения вполне достаточна для сохранения информации)

Регенерация памяти В современных компьютерах регенерацию основной памяти берет на себя чипсет, и его задача – по возможности использовать для регенерации циклы шины, не занятые ей абонентами. Контроллеры регенерации smart refresh ставят запросы на регенерацию в очередь, которую обслуживают в свободное для шины время или если запросов накопилось больше предельного количества. При использовании чередования банков целесообразно производить регенерацию одного во время полезного обращения к другому. Динамическая память в видеобуферах графических адаптеров регенерации, как правило, не требует (частота её чтения вполне достаточна для сохранения информации)

Асинхронная память: FPM, EDO и BEDO Если последовательно обращаться к ячейкам, располагающимся в одной строке матрицы, адрес строки можно выставлять на шине только один раз и удерживать RAS# на низком уровне во время всех последующих циклов обращений. Такой режим называется режимом быстрого страничного обмена FPM (Fast Page Mode). Для памяти с временем доступа 60 нс время цикла обмена внутри страницы может быть сокращено до 35 нс. Способность работать в режиме FPM является заслугой не микросхем памяти, а контроллера (т. е. чипсета). Однако по сложившейся терминологии название FPM относят к стандартным модулям памяти (не EDO, BEDO или SDRAM). Стандартная память с временем доступа 60 -70 нс при частоте шины 66 МГц может обеспечить лучший пакетный цикл чтения 5 -3 -3 -3.

Асинхронная память: FPM, EDO и BEDO Если последовательно обращаться к ячейкам, располагающимся в одной строке матрицы, адрес строки можно выставлять на шине только один раз и удерживать RAS# на низком уровне во время всех последующих циклов обращений. Такой режим называется режимом быстрого страничного обмена FPM (Fast Page Mode). Для памяти с временем доступа 60 нс время цикла обмена внутри страницы может быть сокращено до 35 нс. Способность работать в режиме FPM является заслугой не микросхем памяти, а контроллера (т. е. чипсета). Однако по сложившейся терминологии название FPM относят к стандартным модулям памяти (не EDO, BEDO или SDRAM). Стандартная память с временем доступа 60 -70 нс при частоте шины 66 МГц может обеспечить лучший пакетный цикл чтения 5 -3 -3 -3.

Асинхронная память: FPM, EDO и BEDO Следующей модификацией памяти, направленной на повышение производительности при том же быстродействии запоминающих элементов, явилась память EDO DRAM (Extended или Enhanced Data Out). Эта память содержит регистр-защелку (data latch) выходных данных, который по подъему сигнала CAS# фиксирует значение выходных данных, и потому их считывание внешними схемами может производиться вплоть до следующего спада CAS#. Время цикла внутри страницы понижается с 35 нс до 25 нс (производительность повышается на 40%). Лучший пакетный цикл при частоте шины 66 МГц - 5 -2 -2 -2. В памяти BEDO (Burst EDO) появился ещё и внутренний счетчик адреса колонок для пакетного цикла. Для BEDO-памяти с временем доступа 60 нс при частоте шины 66 МГц обеспечивается лучший пакетный цикл 5 -1 -1 -1.

Асинхронная память: FPM, EDO и BEDO Следующей модификацией памяти, направленной на повышение производительности при том же быстродействии запоминающих элементов, явилась память EDO DRAM (Extended или Enhanced Data Out). Эта память содержит регистр-защелку (data latch) выходных данных, который по подъему сигнала CAS# фиксирует значение выходных данных, и потому их считывание внешними схемами может производиться вплоть до следующего спада CAS#. Время цикла внутри страницы понижается с 35 нс до 25 нс (производительность повышается на 40%). Лучший пакетный цикл при частоте шины 66 МГц - 5 -2 -2 -2. В памяти BEDO (Burst EDO) появился ещё и внутренний счетчик адреса колонок для пакетного цикла. Для BEDO-памяти с временем доступа 60 нс при частоте шины 66 МГц обеспечивается лучший пакетный цикл 5 -1 -1 -1.

Синхронная память: SDRAM и DDR SDRAM Микросхемы синхронной динамической памяти SDRAM (Synchronous DRAM) представляют собой конвейеризированные устройства, которые на основе вполне обычных ячеек (время доступа 50 -70 нс) обеспечивают цикл 5 -1 -1 -1 при частоте шины 100 МГц и выше. Синхронный интерфейс в сочетании с внутренней мультибанковой организацией повышает производительность памяти при множественных обращениях (современные процессоры способны формировать новые запросы к памяти, не дожидаясь результатов выполнения предыдущих, кроме того, к памяти обращаются и другие устройства). В SDRAM можно параллельно активировать строки в разных банках (и в разных микросхемах) и закрывать их после серии обращений к их элементам.

Синхронная память: SDRAM и DDR SDRAM Микросхемы синхронной динамической памяти SDRAM (Synchronous DRAM) представляют собой конвейеризированные устройства, которые на основе вполне обычных ячеек (время доступа 50 -70 нс) обеспечивают цикл 5 -1 -1 -1 при частоте шины 100 МГц и выше. Синхронный интерфейс в сочетании с внутренней мультибанковой организацией повышает производительность памяти при множественных обращениях (современные процессоры способны формировать новые запросы к памяти, не дожидаясь результатов выполнения предыдущих, кроме того, к памяти обращаются и другие устройства). В SDRAM можно параллельно активировать строки в разных банках (и в разных микросхемах) и закрывать их после серии обращений к их элементам.

Синхронная память: SDRAM и DDR SDRAM Микросхемы SDRAM оптимизированы для пакетной передачи. При инициализации у них программируется длина пакета (1, 2, 4, 8 элементов), порядок адресов в пакете (wrap mode: interleave/linear) и операционный режим. Также SDRAM имеет средства энергосбережения. По тактовой частоте для SDRAM, используемой в качестве ОЗУ, имеется 3 градации: PC 66, PC 100 и PC 133 для максимальных частот 66, 100 и 133 МГц. Синхронный интерфейс обеспечивает на частоте 100 МГц пиковую производительность 100 Мбит/пин. SDRAM используют в составе модулей DIMM с 8 -байтной разрядностью, что дает 800 Мбайт/с. При частоте шины 133 МГц пиковая производительность достигла 1064 Мбайт/с (не учитывается регенерация и подразумевается, что нужные страницы уже открыты). Возможность SDRAM практически одновременно обслуживать множество запросов будет реализована лишь при достаточно «умном» контроллере памяти.

Синхронная память: SDRAM и DDR SDRAM Микросхемы SDRAM оптимизированы для пакетной передачи. При инициализации у них программируется длина пакета (1, 2, 4, 8 элементов), порядок адресов в пакете (wrap mode: interleave/linear) и операционный режим. Также SDRAM имеет средства энергосбережения. По тактовой частоте для SDRAM, используемой в качестве ОЗУ, имеется 3 градации: PC 66, PC 100 и PC 133 для максимальных частот 66, 100 и 133 МГц. Синхронный интерфейс обеспечивает на частоте 100 МГц пиковую производительность 100 Мбит/пин. SDRAM используют в составе модулей DIMM с 8 -байтной разрядностью, что дает 800 Мбайт/с. При частоте шины 133 МГц пиковая производительность достигла 1064 Мбайт/с (не учитывается регенерация и подразумевается, что нужные страницы уже открыты). Возможность SDRAM практически одновременно обслуживать множество запросов будет реализована лишь при достаточно «умном» контроллере памяти.

Синхронная память: SDRAM и DDR SDRAM Память DDR SDRAM – дальнейшее развитие SDRAM. Как и следует из названия (Dual Data Rate) у микросхем DDR SDRAM данные внутри пакета передаются с удвоенной скоростью – они переключаются по обоим фронтам синхроимпульсов. На частоте 100 МГц эта память имеет пиковую производительность 200 Мбит/пин. В перспективе ожидается появление микросхем DDR-II SDRAM, в которой обмен будет на четырехкратной частоте синхронизации. По причине существенного отличия интерфейса от традиционной асинхронной памяти, микросхемы SDRAM не могут быть установлены в модули SIMM, они применяются в DIMM или устанавливаются прямо на системную или графическую плату.

Синхронная память: SDRAM и DDR SDRAM Память DDR SDRAM – дальнейшее развитие SDRAM. Как и следует из названия (Dual Data Rate) у микросхем DDR SDRAM данные внутри пакета передаются с удвоенной скоростью – они переключаются по обоим фронтам синхроимпульсов. На частоте 100 МГц эта память имеет пиковую производительность 200 Мбит/пин. В перспективе ожидается появление микросхем DDR-II SDRAM, в которой обмен будет на четырехкратной частоте синхронизации. По причине существенного отличия интерфейса от традиционной асинхронной памяти, микросхемы SDRAM не могут быть установлены в модули SIMM, они применяются в DIMM или устанавливаются прямо на системную или графическую плату.

Память Rambus DRAM Память RDRAM (Rambus DRAM) имеет синхронный интерфейс, отличный от SDRAM. Первые модели RDRAM применялись в некоторых моделях видеокарт и игровых приставок. Их интерфейс – Rambus Channel – имел разрядность шины данных в 1 байт, но, работая на частоте 250 -300 МГц, обеспечивал производительность 500 -600 Мбайт/с. Его сменил CRDRAM (300350 МГц, 600 -700 Мбайт/с), а потом и DRDRAM (Direct Rambus DRAM), обеспечивающий производительность 1600 Мбайт/с на двухбайтной шине данных при частоте 400 МГц. По сравнению с DDR SDRAM при той же производительности RDRAM имеет более компактный интерфейс и большую масштабируемость.

Память Rambus DRAM Память RDRAM (Rambus DRAM) имеет синхронный интерфейс, отличный от SDRAM. Первые модели RDRAM применялись в некоторых моделях видеокарт и игровых приставок. Их интерфейс – Rambus Channel – имел разрядность шины данных в 1 байт, но, работая на частоте 250 -300 МГц, обеспечивал производительность 500 -600 Мбайт/с. Его сменил CRDRAM (300350 МГц, 600 -700 Мбайт/с), а потом и DRDRAM (Direct Rambus DRAM), обеспечивающий производительность 1600 Мбайт/с на двухбайтной шине данных при частоте 400 МГц. По сравнению с DDR SDRAM при той же производительности RDRAM имеет более компактный интерфейс и большую масштабируемость.

Память с виртуальными каналами – VC DRAM Идея архитектуры памяти с виртуальными каналами (Virtual Channel Memory Architecture) состоит в помещении между массивом запоминающих ячеек и внешним интерфейсом микросхемы памяти набора канальных буферов. При этом операции обмена данными разделяются на два уровня: фасадный (обмен данными с каналом) и тыловой (обмен между каналами и массивом запоминающих ячеек). Оба процесса выполняются по командам со стороны внешнего интерфейса почти независимо друг от друга. Архитектура виртуальных каналов применима к памяти любого типа, включая ПЗУ и флэш-память, но наиболее интересна она в приложении к динамической памяти – VC DRAM. Именно её подразумевают под аббревиатурой VCM (Virtual-Channel Memory)

Память с виртуальными каналами – VC DRAM Идея архитектуры памяти с виртуальными каналами (Virtual Channel Memory Architecture) состоит в помещении между массивом запоминающих ячеек и внешним интерфейсом микросхемы памяти набора канальных буферов. При этом операции обмена данными разделяются на два уровня: фасадный (обмен данными с каналом) и тыловой (обмен между каналами и массивом запоминающих ячеек). Оба процесса выполняются по командам со стороны внешнего интерфейса почти независимо друг от друга. Архитектура виртуальных каналов применима к памяти любого типа, включая ПЗУ и флэш-память, но наиболее интересна она в приложении к динамической памяти – VC DRAM. Именно её подразумевают под аббревиатурой VCM (Virtual-Channel Memory)

Память с виртуальными каналами – VC DRAM При чтении VC DRAM данные появляются даже позже, чем в SDRAM (у SDRAM CAS Latency составляют 2 -3 такта, а у VC DRAM – 4 такта). Тем не менее, применение VC DRAM дает прирост производительности за счет поддержки многозадачности в самих микросхемах и в контроллере памяти. Контроллер может связать поток от каждого абонента памяти (процессор, порт AGP, Шина PCI) со своим канальным буфером, и поток с хранящими матрицами микросхем будет обмениваться большими блоками. Таким образом, память VC DRAM по сравнению с другими типами динамической памяти обеспечивает меньшее среднее время задержки в многозадачных системах, однако по пиковой скорости передачи она не имеет преимуществ перед SDRAM и уступает RDRAM и DDR SDRAM. Поддержка VC DRAM имеется далеко не во всех чипсетах: её вводят VIA и Si. S, а Intel игнорирует.

Память с виртуальными каналами – VC DRAM При чтении VC DRAM данные появляются даже позже, чем в SDRAM (у SDRAM CAS Latency составляют 2 -3 такта, а у VC DRAM – 4 такта). Тем не менее, применение VC DRAM дает прирост производительности за счет поддержки многозадачности в самих микросхемах и в контроллере памяти. Контроллер может связать поток от каждого абонента памяти (процессор, порт AGP, Шина PCI) со своим канальным буфером, и поток с хранящими матрицами микросхем будет обмениваться большими блоками. Таким образом, память VC DRAM по сравнению с другими типами динамической памяти обеспечивает меньшее среднее время задержки в многозадачных системах, однако по пиковой скорости передачи она не имеет преимуществ перед SDRAM и уступает RDRAM и DDR SDRAM. Поддержка VC DRAM имеется далеко не во всех чипсетах: её вводят VIA и Si. S, а Intel игнорирует.

Внутренний кэш Одним из способов повышения производительности динамической памяти является помещение статической кэш-памяти прямо на кристалл памяти. Эта архитектура реализована в микросхемах CDRAM (Cached DRAM) и EDRAM (Enhanced DRAM). Память с внутренним кэшем значительно эффективнее обычной комбинации DRAM и вторичного кэша, особенно в многозадачных системах, где переключение задач приводит к высокой частоте кэш-промахов обычного кэша.

Внутренний кэш Одним из способов повышения производительности динамической памяти является помещение статической кэш-памяти прямо на кристалл памяти. Эта архитектура реализована в микросхемах CDRAM (Cached DRAM) и EDRAM (Enhanced DRAM). Память с внутренним кэшем значительно эффективнее обычной комбинации DRAM и вторичного кэша, особенно в многозадачных системах, где переключение задач приводит к высокой частоте кэш-промахов обычного кэша.

Модули памяти: SIMM-30 90 1 30 Модули SIMM (Single Inline Memory Mode) представляют собой небольшие печатные платы с односторонним краевым разъемом. У малораспространенных модулей SIPP контакты штырьковые. По логической организации различают односторонние и двусторонние модули. У односторонних микросхемы смонтированы на одной поверхности, у двусторонних двойной комплект – два банка - микросхем смонтированы на обеих сторонах. Емкость односторонних SIMM-30 до 1 Мбайт.

Модули памяти: SIMM-30 90 1 30 Модули SIMM (Single Inline Memory Mode) представляют собой небольшие печатные платы с односторонним краевым разъемом. У малораспространенных модулей SIPP контакты штырьковые. По логической организации различают односторонние и двусторонние модули. У односторонних микросхемы смонтированы на одной поверхности, у двусторонних двойной комплект – два банка - микросхем смонтированы на обеих сторонах. Емкость односторонних SIMM-30 до 1 Мбайт.

Модули памяти: SIMM-72 107, 95 1 36 37 72 «Длинные» , или SIMM-72, модули SIMM имеют 72 печатных вывода и 4 -байтную организацию с возможностью независимого побайтного обращения. Емкость до 64 Мбайт.

Модули памяти: SIMM-72 107, 95 1 36 37 72 «Длинные» , или SIMM-72, модули SIMM имеют 72 печатных вывода и 4 -байтную организацию с возможностью независимого побайтного обращения. Емкость до 64 Мбайт.

Модули памяти: DIMM-168 133, 35 1 10 11 40 85 94 95 124 41 125 84 168 Модуль памяти DIMM (Dual-Inline-Memory Module) имеет 168 независимых печатных выводов, расположенных с обеих сторон. 168 -pin Buffered DIMM – модули DIMM первого поколения, у которых все входные сигналы буферизованы. Оснащаются асинхронной памятью. Модули второго поколения могут использовать SDRAM. 168 -pin Unbuffered DIMM – модули, у которых все цепи не буферизованы. 168 -pin Registered DIMM – модули с регистром-защелкой, использующие только синхронную память. Объем до 1024 Мбайт.

Модули памяти: DIMM-168 133, 35 1 10 11 40 85 94 95 124 41 125 84 168 Модуль памяти DIMM (Dual-Inline-Memory Module) имеет 168 независимых печатных выводов, расположенных с обеих сторон. 168 -pin Buffered DIMM – модули DIMM первого поколения, у которых все входные сигналы буферизованы. Оснащаются асинхронной памятью. Модули второго поколения могут использовать SDRAM. 168 -pin Unbuffered DIMM – модули, у которых все цепи не буферизованы. 168 -pin Registered DIMM – модули с регистром-защелкой, использующие только синхронную память. Объем до 1024 Мбайт.

Модули памяти: DIMM-184 1 93 52 144 53 145 92 184 Модули DIMM-184 предназначены для микросхем DDR SDRAM

Модули памяти: DIMM-184 1 93 52 144 53 145 92 184 Модули DIMM-184 предназначены для микросхем DDR SDRAM

Модули памяти: RIMM Модули RIMM (Rambus Interface Memory Module) специально предназначены для памяти RDRAM. Модуль RIMM содержит до 16 микросхем RDRAM, которые закрыты пластиной радиатора. В отличие от SIMM и DIMM, у которых объем памяти кратен степени числа 2, модули RIMM могут иметь более равномерный ряд объемов – в канал RDRAM память можно добавлять хоть по одной микросхеме.

Модули памяти: RIMM Модули RIMM (Rambus Interface Memory Module) специально предназначены для памяти RDRAM. Модуль RIMM содержит до 16 микросхем RDRAM, которые закрыты пластиной радиатора. В отличие от SIMM и DIMM, у которых объем памяти кратен степени числа 2, модули RIMM могут иметь более равномерный ряд объемов – в канал RDRAM память можно добавлять хоть по одной микросхеме.

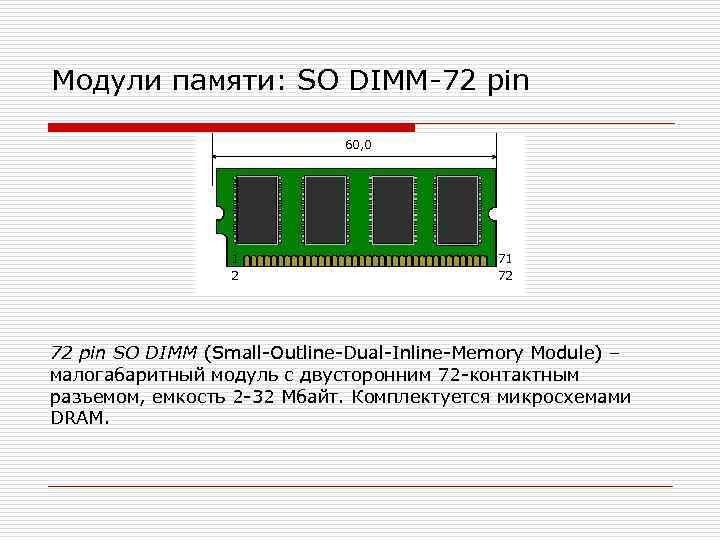

Модули памяти: SO DIMM-72 pin 60, 0 1 2 71 72 72 pin SO DIMM (Small-Outline-Dual-Inline-Memory Module) – малогабаритный модуль с двусторонним 72 -контактным разъемом, емкость 2 -32 Мбайт. Комплектуется микросхемами DRAM.

Модули памяти: SO DIMM-72 pin 60, 0 1 2 71 72 72 pin SO DIMM (Small-Outline-Dual-Inline-Memory Module) – малогабаритный модуль с двусторонним 72 -контактным разъемом, емкость 2 -32 Мбайт. Комплектуется микросхемами DRAM.

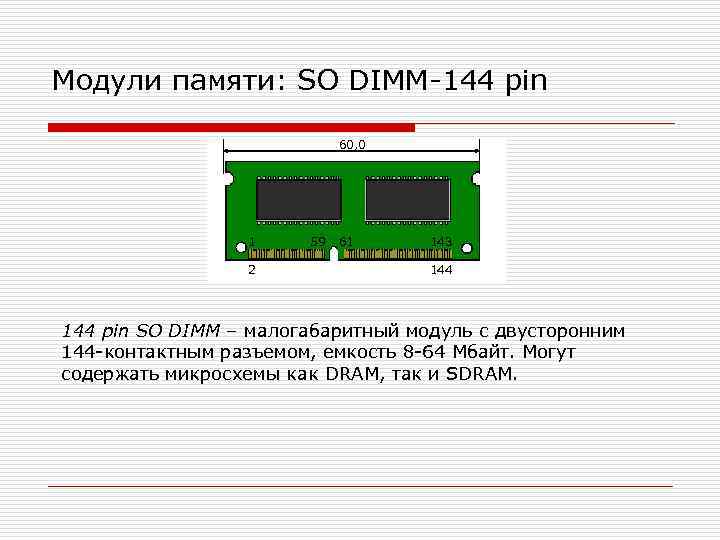

Модули памяти: SO DIMM-144 pin 60, 0 1 2 59 61 143 144 pin SO DIMM – малогабаритный модуль с двусторонним 144 -контактным разъемом, емкость 8 -64 Мбайт. Могут содержать микросхемы как DRAM, так и SDRAM.

Модули памяти: SO DIMM-144 pin 60, 0 1 2 59 61 143 144 pin SO DIMM – малогабаритный модуль с двусторонним 144 -контактным разъемом, емкость 8 -64 Мбайт. Могут содержать микросхемы как DRAM, так и SDRAM.

Распределение памяти (логическая структура)

Распределение памяти (логическая структура)

Распределение памяти Логическая структура памяти PC обусловлена особенностями системы адресации процессоров семейства x 86. Процессоры 8086/88 имели доступное адресное пространство 1 Мбайт (20 бит шины адреса). Они использовали сегментную модель памяти, когда линейный адрес вычисляется по формуле: Addr = Seg*16 + Offset где Seg и Offset – содержимое сегментного и адресного регистров. Таким образом Addr = 00000 – FFFFFh. Заметим, что при Seg = FFFFh и Offset = FFFFh данная формула дает адрес 10 FFEFh, но ввиду 20 -битного ограничения на шину адреса эта комбинация в физической памяти дает 0 FFEFh. Из-за этого при повышении разрядности шины до 24 бит (80286) и далее появились 64 К-16 дополнительных байт, названные «высокой памятью» (High Memory Area, HMA) и пришлось вводить вентиль Gate. A 20.

Распределение памяти Логическая структура памяти PC обусловлена особенностями системы адресации процессоров семейства x 86. Процессоры 8086/88 имели доступное адресное пространство 1 Мбайт (20 бит шины адреса). Они использовали сегментную модель памяти, когда линейный адрес вычисляется по формуле: Addr = Seg*16 + Offset где Seg и Offset – содержимое сегментного и адресного регистров. Таким образом Addr = 00000 – FFFFFh. Заметим, что при Seg = FFFFh и Offset = FFFFh данная формула дает адрес 10 FFEFh, но ввиду 20 -битного ограничения на шину адреса эта комбинация в физической памяти дает 0 FFEFh. Из-за этого при повышении разрядности шины до 24 бит (80286) и далее появились 64 К-16 дополнительных байт, названные «высокой памятью» (High Memory Area, HMA) и пришлось вводить вентиль Gate. A 20.

Распределение памяти 32 -разрядные процессоры позволяют организовать режим, иногда называемый «нереальным» или «большим реальным» , при котором инструкции выполняются, как в реальном, но доступны все 4 Гб памяти Основную часть адресного пространства занимает оперативная память. Объем установленной памяти определятся при загрузке тестом POST, начиная с младших адресов. Натолкнувшись на отсутствие памяти (ошибку), тест останавливается на достигнутом и сообщает системе объем реально работающей памяти

Распределение памяти 32 -разрядные процессоры позволяют организовать режим, иногда называемый «нереальным» или «большим реальным» , при котором инструкции выполняются, как в реальном, но доступны все 4 Гб памяти Основную часть адресного пространства занимает оперативная память. Объем установленной памяти определятся при загрузке тестом POST, начиная с младших адресов. Натолкнувшись на отсутствие памяти (ошибку), тест останавливается на достигнутом и сообщает системе объем реально работающей памяти

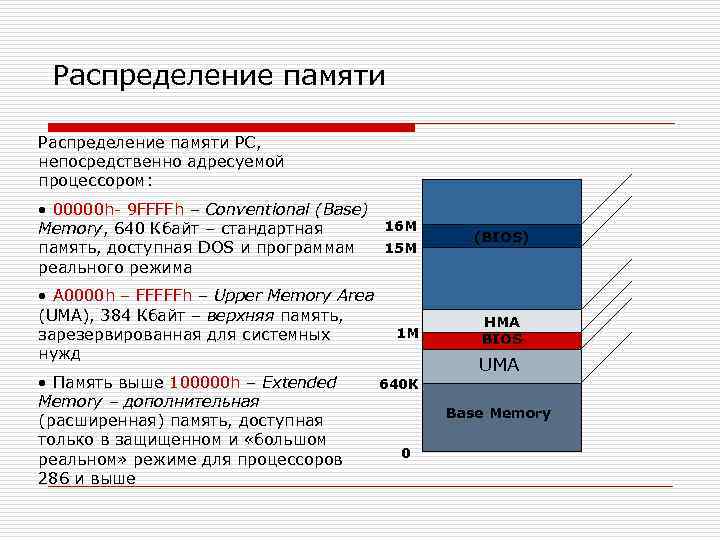

Распределение памяти PC, непосредственно адресуемой процессором: • 00000 h- 9 FFFFh – Conventional (Base) 16 M Memory, 640 Кбайт – стандартная память, доступная DOS и программам 15 M реального режима • A 0000 h – FFFFFh – Upper Memory Area (UMA), 384 Кбайт – верхняя память, зарезервированная для системных нужд • Память выше 100000 h – Extended Memory – дополнительная (расширенная) память, доступная только в защищенном и «большом реальном» режиме для процессоров 286 и выше 1 M (BIOS) HMA BIOS UMA 640 K Base Memory 0

Распределение памяти PC, непосредственно адресуемой процессором: • 00000 h- 9 FFFFh – Conventional (Base) 16 M Memory, 640 Кбайт – стандартная память, доступная DOS и программам 15 M реального режима • A 0000 h – FFFFFh – Upper Memory Area (UMA), 384 Кбайт – верхняя память, зарезервированная для системных нужд • Память выше 100000 h – Extended Memory – дополнительная (расширенная) память, доступная только в защищенном и «большом реальном» режиме для процессоров 286 и выше 1 M (BIOS) HMA BIOS UMA 640 K Base Memory 0

Распределение памяти Вышеприведенное разделение памяти актуально только для приложений и операционных систем реального режима типа MS -DOS. Для ОС защищенного режима доступна вся оперативная память, причем без каких-либо ухищрений вроде EMS или XMS. Однако область UMA, сохраняемая ради совместимости , остается барьером на пути к единой однородной памяти.

Распределение памяти Вышеприведенное разделение памяти актуально только для приложений и операционных систем реального режима типа MS -DOS. Для ОС защищенного режима доступна вся оперативная память, причем без каких-либо ухищрений вроде EMS или XMS. Однако область UMA, сохраняемая ради совместимости , остается барьером на пути к единой однородной памяти.

Распределение памяти Для компьютеров класса AT-286 с 24 -битной шиной адреса верхняя граница оперативной памяти - FDFFFFh (15, 9 Мбайт). Область FE 0000 h – FFFFFFh содержит ПЗУ BIOS, обращение к этой области эквивалентно обращению к ROM BIOS по адресам 0 E 0000 h – 0 FFFFFh. Для 386+ процессоров и 32 -битной шины адреса теоретическая верхняя граница 4 Гбайт, а для P 6 (36 -битная шина) 64 Гбайт. В компьютерах с 32 -разрядной шиной адреса образ BIOS проецируется в адреса FFFE 0000 h – FFFFh (для P 6 необязательно). Иногда используется проекция в область FE 0000 h – FFFFFFh, что не позволяет задействовать более 16 Мбайт ОЗУ. Это отображение можно запретить установкой соответствующего параметра CMOS Setup.

Распределение памяти Для компьютеров класса AT-286 с 24 -битной шиной адреса верхняя граница оперативной памяти - FDFFFFh (15, 9 Мбайт). Область FE 0000 h – FFFFFFh содержит ПЗУ BIOS, обращение к этой области эквивалентно обращению к ROM BIOS по адресам 0 E 0000 h – 0 FFFFFh. Для 386+ процессоров и 32 -битной шины адреса теоретическая верхняя граница 4 Гбайт, а для P 6 (36 -битная шина) 64 Гбайт. В компьютерах с 32 -разрядной шиной адреса образ BIOS проецируется в адреса FFFE 0000 h – FFFFh (для P 6 необязательно). Иногда используется проекция в область FE 0000 h – FFFFFFh, что не позволяет задействовать более 16 Мбайт ОЗУ. Это отображение можно запретить установкой соответствующего параметра CMOS Setup.

Распределение памяти Реально современные платы позволяют установить 512 -2048 Мбайт ОЗУ, для мощных серверных платформ и это не предел. Обращение по адресам, превышающим границу установленной памяти (или максимально возможного объема), транслируется на шину PCI, которая имеет 32 -битную адресацию

Распределение памяти Реально современные платы позволяют установить 512 -2048 Мбайт ОЗУ, для мощных серверных платформ и это не предел. Обращение по адресам, превышающим границу установленной памяти (или максимально возможного объема), транслируется на шину PCI, которая имеет 32 -битную адресацию

Распределение памяти Компьютеры, использующие режим системного управления SMM (System Management Mode) имеют ещё одно адресное пространство памяти – SMRAM. Это адресное пространство «параллельно» пространству обычной памяти и при работе доступно процессору только в режиме обработки SMI. Память SMRAM может представлять собой часть физической оперативной памяти или отдельную микросхему. Её размер – от 32 Кбайт до 4 Гбайт. SMRAM располагается начиная с адреса SMIBASE (по умолчанию 30000 h) и распределяется относительно SMIBASE следующим образом: • FE 00 h – FFFFh – область сохранения контекста (сохраняются почти все регистры процессора, за исключением FPU) • 8000 h – точка входа в обработчик (SMI Handler) • 0 – 7 FFFh – свободная область

Распределение памяти Компьютеры, использующие режим системного управления SMM (System Management Mode) имеют ещё одно адресное пространство памяти – SMRAM. Это адресное пространство «параллельно» пространству обычной памяти и при работе доступно процессору только в режиме обработки SMI. Память SMRAM может представлять собой часть физической оперативной памяти или отдельную микросхему. Её размер – от 32 Кбайт до 4 Гбайт. SMRAM располагается начиная с адреса SMIBASE (по умолчанию 30000 h) и распределяется относительно SMIBASE следующим образом: • FE 00 h – FFFFh – область сохранения контекста (сохраняются почти все регистры процессора, за исключением FPU) • 8000 h – точка входа в обработчик (SMI Handler) • 0 – 7 FFFh – свободная область

Стандартная память – Conventional Memory Стандартная память является самой дефицитной в PC при работе в ОС реального режима. На её небольшой объем претендуют и BIOS и ОС, а остатки отдаются прикладному ПО Стандартная память распределяется следующим образом: • 00000 h – 003 FFh - Interrupt Vectors – векторы прерываний (256 двойных слов) • 00400 h – 004 FFh – BIOS Data Area – область переменных BIOS • 00500 h – 00 xxxh – DOS Area – область DOS • 00 xxxh – 9 FFFFh – User RAM – память, предоставляемая пользователю (до 638 Кбайт). При использовании PS/2 Mouse область 9 FC 00 h – 9 FFFFh используется как расширение BIOS Data Area

Стандартная память – Conventional Memory Стандартная память является самой дефицитной в PC при работе в ОС реального режима. На её небольшой объем претендуют и BIOS и ОС, а остатки отдаются прикладному ПО Стандартная память распределяется следующим образом: • 00000 h – 003 FFh - Interrupt Vectors – векторы прерываний (256 двойных слов) • 00400 h – 004 FFh – BIOS Data Area – область переменных BIOS • 00500 h – 00 xxxh – DOS Area – область DOS • 00 xxxh – 9 FFFFh – User RAM – память, предоставляемая пользователю (до 638 Кбайт). При использовании PS/2 Mouse область 9 FC 00 h – 9 FFFFh используется как расширение BIOS Data Area

Верхняя память - UMA Верхняя память имеет области различного назначения, которые могут быть заполнены буферной памятью адаптеров, постоянной памятью, или оставаться незаполненными. С появлением механизма страничной переадресации (у процессоров 386 и выше) «дыры» стали по возможности заполнять «островками» оперативной памяти, названными блоками верхней памяти UMB (Upper Memory Block). Эти области доступны DOS для размещения резидентных программ и драйверов через драйвер EMM 386.

Верхняя память - UMA Верхняя память имеет области различного назначения, которые могут быть заполнены буферной памятью адаптеров, постоянной памятью, или оставаться незаполненными. С появлением механизма страничной переадресации (у процессоров 386 и выше) «дыры» стали по возможности заполнять «островками» оперативной памяти, названными блоками верхней памяти UMB (Upper Memory Block). Эти области доступны DOS для размещения резидентных программ и драйверов через драйвер EMM 386.

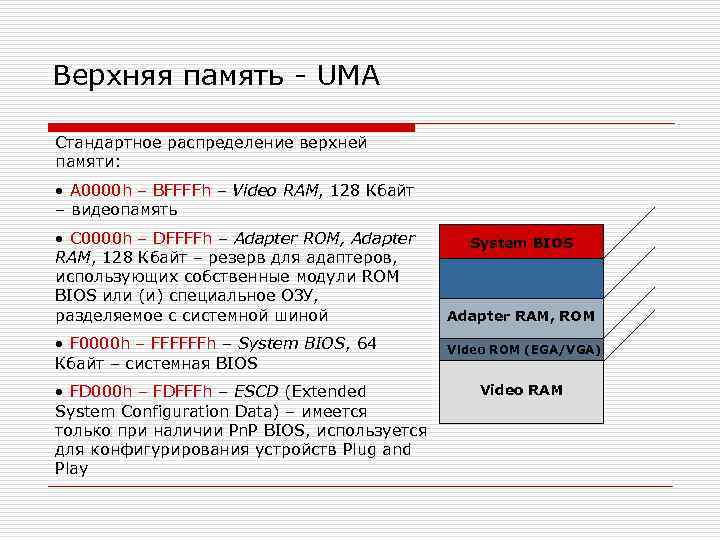

Верхняя память - UMA Стандартное распределение верхней памяти: • A 0000 h – BFFFFh – Video RAM, 128 Кбайт – видеопамять • C 0000 h – DFFFFh – Adapter ROM, Adapter RAM, 128 Кбайт – резерв для адаптеров, использующих собственные модули ROM BIOS или (и) специальное ОЗУ, разделяемое с системной шиной • F 0000 h – FFFFFFh – System BIOS, 64 Кбайт – системная BIOS • FD 000 h – FDFFFh – ESCD (Extended System Configuration Data) – имеется только при наличии Pn. P BIOS, используется для конфигурирования устройств Plug and Play System BIOS Adapter RAM, ROM Video ROM (EGA/VGA) Video RAM

Верхняя память - UMA Стандартное распределение верхней памяти: • A 0000 h – BFFFFh – Video RAM, 128 Кбайт – видеопамять • C 0000 h – DFFFFh – Adapter ROM, Adapter RAM, 128 Кбайт – резерв для адаптеров, использующих собственные модули ROM BIOS или (и) специальное ОЗУ, разделяемое с системной шиной • F 0000 h – FFFFFFh – System BIOS, 64 Кбайт – системная BIOS • FD 000 h – FDFFFh – ESCD (Extended System Configuration Data) – имеется только при наличии Pn. P BIOS, используется для конфигурирования устройств Plug and Play System BIOS Adapter RAM, ROM Video ROM (EGA/VGA) Video RAM

Верхняя память - UMA В области UMA практически всегда присутствует графический адаптер, в зависимости от модели он занимает различные области Также распространенным потребителем UMA являются расширения ROM BIOS, расположенные на платах дисковых контроллеров и микросхемы удаленной загрузки (Boot ROM) на платах адаптеров ЛВС Размер, занимаемый системной ROM BIOS, колеблется от 8 Кбайт (PC/XT) до 128 Кбайт (разумное значение 64 Кбайт). При появлении микросхем ROM и флэш-памяти объемом 1 Мбит, стали использовать большую область, но при этом размер доступной UMA сократился. Тогда стали микросхемы того же (и большего) объема отображать в область F 0000 h – FFFFFh (64 Кбайт)

Верхняя память - UMA В области UMA практически всегда присутствует графический адаптер, в зависимости от модели он занимает различные области Также распространенным потребителем UMA являются расширения ROM BIOS, расположенные на платах дисковых контроллеров и микросхемы удаленной загрузки (Boot ROM) на платах адаптеров ЛВС Размер, занимаемый системной ROM BIOS, колеблется от 8 Кбайт (PC/XT) до 128 Кбайт (разумное значение 64 Кбайт). При появлении микросхем ROM и флэш-памяти объемом 1 Мбит, стали использовать большую область, но при этом размер доступной UMA сократился. Тогда стали микросхемы того же (и большего) объема отображать в область F 0000 h – FFFFFh (64 Кбайт)

Отображаемая и расширенная память – EMS и XMS Отображаемая память EMS (Expanded Memory Specification) – программная спецификация использования дополнительной памяти DOS-программами реального режима. Спецификация LIM EMS – соглашение фирм Lotus, Intel, Microsoft на использование EMS. C помощью специальных аппаратных или программных средств любая область дополнительной памяти может быть отображена на небольшие страницы, расположенные в области UMA (изначально 4 страницы по 16 Кбайт, примыкавшие друг к другу). Обращение прикладных программ к EMS осуществляется через диспетчер памяти, вызываемый по прерыванию Int 67 h. Программа должна сначала запросить выделение области, указав её размер в страницах. В ответ на запрос диспетчер сообщает номер дескриптора EMS (EMS Handler), По которому программа будет ссылаться на выделенную ей область.

Отображаемая и расширенная память – EMS и XMS Отображаемая память EMS (Expanded Memory Specification) – программная спецификация использования дополнительной памяти DOS-программами реального режима. Спецификация LIM EMS – соглашение фирм Lotus, Intel, Microsoft на использование EMS. C помощью специальных аппаратных или программных средств любая область дополнительной памяти может быть отображена на небольшие страницы, расположенные в области UMA (изначально 4 страницы по 16 Кбайт, примыкавшие друг к другу). Обращение прикладных программ к EMS осуществляется через диспетчер памяти, вызываемый по прерыванию Int 67 h. Программа должна сначала запросить выделение области, указав её размер в страницах. В ответ на запрос диспетчер сообщает номер дескриптора EMS (EMS Handler), По которому программа будет ссылаться на выделенную ей область.

Отображаемая и расширенная память – EMS и XMS Далее программа через диспетчер назначает отображение нужной ей логической страницы из дополнительной памяти на физическую страницу, расположенную в UMA. После этого любые программные обращения процессора к физической странице в пределах первого мегабайта будут в действительности работать с дополнительной памятью, расположенной выше первого мегабайта, причем без переключения в защищенный режим. Для работы с другой страницей требуется вызов диспетчера для переназначения отображения. В EMS 4. 0 (на 386+) появилась возможность увеличения числа страниц и отображения их в любую область памяти. Также на 386 появилась возможность программной эмуляции EMS. Система EMS в основном используется для хранения данных: создания виртуальных дисков, хранения очередей заданий для печати. Однако иногда её используют для хранения данных и кода некоторых резидентных программ.

Отображаемая и расширенная память – EMS и XMS Далее программа через диспетчер назначает отображение нужной ей логической страницы из дополнительной памяти на физическую страницу, расположенную в UMA. После этого любые программные обращения процессора к физической странице в пределах первого мегабайта будут в действительности работать с дополнительной памятью, расположенной выше первого мегабайта, причем без переключения в защищенный режим. Для работы с другой страницей требуется вызов диспетчера для переназначения отображения. В EMS 4. 0 (на 386+) появилась возможность увеличения числа страниц и отображения их в любую область памяти. Также на 386 появилась возможность программной эмуляции EMS. Система EMS в основном используется для хранения данных: создания виртуальных дисков, хранения очередей заданий для печати. Однако иногда её используют для хранения данных и кода некоторых резидентных программ.

Отображаемая и расширенная память – EMS и XMS Расширенная память XMS (e. Xtended Memory Specification) – другая программная спецификация использования дополнительной памяти (Lotus, Intel, Microsoft, AST) для процессоров 286+. Диспетчер расширенной памяти – драйвер HIMEM. SYS позволяет программе получить в распоряжение одну или несколько областей дополнительной памяти, а также использовать область HMA (65 520 байт, начиная с 100000 h) и управлять вентилем Gate. A 20. Функции XMS позволяют: • определить размер максимально доступного блока памяти • захватить или освободить блок • копировать данные из одного блока в другой • запереть и отпереть блок • изменить размер выделенного блока

Отображаемая и расширенная память – EMS и XMS Расширенная память XMS (e. Xtended Memory Specification) – другая программная спецификация использования дополнительной памяти (Lotus, Intel, Microsoft, AST) для процессоров 286+. Диспетчер расширенной памяти – драйвер HIMEM. SYS позволяет программе получить в распоряжение одну или несколько областей дополнительной памяти, а также использовать область HMA (65 520 байт, начиная с 100000 h) и управлять вентилем Gate. A 20. Функции XMS позволяют: • определить размер максимально доступного блока памяти • захватить или освободить блок • копировать данные из одного блока в другой • запереть и отпереть блок • изменить размер выделенного блока

Отображаемая и расширенная память – EMS и XMS В ответ на запрос выделения области диспетчер выдает номер дескриптора блока (XMS Handler), по которому выполняются дальнейшие манипуляции с блоком. Размер блока – до 64 Мбайт. XMS позволяет программе копировать данные из доступных областей первого Мбайта в дополнительную память и обратно. Кроме того, XMS определяет пару функций для работы с блоками UMB – захватить или освободить блок требуемого размера. Спецификации EMS и XMS различаются по принципу действия: в EMS используется страничная переадресация, а в XMS – копирование блоков данных. На компьютерах 386+ эти спецификации мирно сосуществуют: поверх драйвера HIMEM. SYS можно ставить драйвер EMM 386. EXE, пользующийся памятью XMS для эмуляции EMS памяти.

Отображаемая и расширенная память – EMS и XMS В ответ на запрос выделения области диспетчер выдает номер дескриптора блока (XMS Handler), по которому выполняются дальнейшие манипуляции с блоком. Размер блока – до 64 Мбайт. XMS позволяет программе копировать данные из доступных областей первого Мбайта в дополнительную память и обратно. Кроме того, XMS определяет пару функций для работы с блоками UMB – захватить или освободить блок требуемого размера. Спецификации EMS и XMS различаются по принципу действия: в EMS используется страничная переадресация, а в XMS – копирование блоков данных. На компьютерах 386+ эти спецификации мирно сосуществуют: поверх драйвера HIMEM. SYS можно ставить драйвер EMM 386. EXE, пользующийся памятью XMS для эмуляции EMS памяти.

Теневая память – Shadow ROM и Shadow RAM В области UMA обычно располагаются устройства с медленной памятью: системная BIOS, расширения BIOS на графическом адаптере, на контроллерах дисков и интерфейсов, ПЗУ начальной загрузке на сетевой карте, видеопамять – реализованные на 8 - или 16 -битных микросхемах. Для ускорения обращений к памяти этих устройств используется теневая память (Shadow Memory) – подмена её системным ОЗУ. Она может быть реализована как аппаратно, так и программно (с помощью страничной переадресации). Обычно теневая память включается через CMOS Setup. На современных системных платах затенение системной BIOS выполняется всегда, на старых им можно было управлять. Затенение BIOS видеоадаптера для работы в Windows с «родным» драйвером может и не давать прироста производительности.

Теневая память – Shadow ROM и Shadow RAM В области UMA обычно располагаются устройства с медленной памятью: системная BIOS, расширения BIOS на графическом адаптере, на контроллерах дисков и интерфейсов, ПЗУ начальной загрузке на сетевой карте, видеопамять – реализованные на 8 - или 16 -битных микросхемах. Для ускорения обращений к памяти этих устройств используется теневая память (Shadow Memory) – подмена её системным ОЗУ. Она может быть реализована как аппаратно, так и программно (с помощью страничной переадресации). Обычно теневая память включается через CMOS Setup. На современных системных платах затенение системной BIOS выполняется всегда, на старых им можно было управлять. Затенение BIOS видеоадаптера для работы в Windows с «родным» драйвером может и не давать прироста производительности.

Теневая память – Shadow ROM и Shadow RAM Затенение ОЗУ и ПЗУ устройств выполняется по-разному: При использовании теневого ПЗУ (Shadow ROM) содержимое затеняемой области копируется в ОЗУ, и при дальнейшем чтении по этим адресам подставляется ОЗУ, а запись в эту область блокируется При использовании теневого ОЗУ (Shadow RAM) запись производится одновременно и в затеняемую область, и в системное ОЗУ, а при чтении обращение идет только к системной памяти. Особенно велик эффект от затенения видеопамяти старых графических адаптеров (она доступна для чтения только во время обратного хода развертки). Однако это применимо только к примитивным графическим картам, устанавливаемым в слот ISA, и то не во всех режимах. Затенение областей разделяемой памяти, модифицируемой со стороны адаптера недопустимо (буферная память сетевых адаптеров, видеопамять адаптеров с графическими сопроцессорами).

Теневая память – Shadow ROM и Shadow RAM Затенение ОЗУ и ПЗУ устройств выполняется по-разному: При использовании теневого ПЗУ (Shadow ROM) содержимое затеняемой области копируется в ОЗУ, и при дальнейшем чтении по этим адресам подставляется ОЗУ, а запись в эту область блокируется При использовании теневого ОЗУ (Shadow RAM) запись производится одновременно и в затеняемую область, и в системное ОЗУ, а при чтении обращение идет только к системной памяти. Особенно велик эффект от затенения видеопамяти старых графических адаптеров (она доступна для чтения только во время обратного хода развертки). Однако это применимо только к примитивным графическим картам, устанавливаемым в слот ISA, и то не во всех режимах. Затенение областей разделяемой памяти, модифицируемой со стороны адаптера недопустимо (буферная память сетевых адаптеров, видеопамять адаптеров с графическими сопроцессорами).

Архитектура унифицированной памяти UMA Видеопамять традиционно является физически выделенной частью памяти небольшого объема, и для неё различными способами обеспечивают максимальную производительность – увеличивают разрядность до 128 бит, повышают частоту, применяют специализированные (в т. ч. двухпортовые) микросхемы памяти. Вместо локальной памяти адаптера была предложена архитектура унифицированной памяти UMA (Unified Memory Architecture). Здесь для видеопамяти выделяется область в общем пространстве единой физической оперативной памяти. UMA применяется в чипсетах системной платы с интегрированной графикой.

Архитектура унифицированной памяти UMA Видеопамять традиционно является физически выделенной частью памяти небольшого объема, и для неё различными способами обеспечивают максимальную производительность – увеличивают разрядность до 128 бит, повышают частоту, применяют специализированные (в т. ч. двухпортовые) микросхемы памяти. Вместо локальной памяти адаптера была предложена архитектура унифицированной памяти UMA (Unified Memory Architecture). Здесь для видеопамяти выделяется область в общем пространстве единой физической оперативной памяти. UMA применяется в чипсетах системной платы с интегрированной графикой.

Виртуальная память (Virtual Memory) представляет собой программно-аппаратное средство расширения пространства памяти, предоставляемой программе в качестве оперативной. Она физически реализуется в оперативной и дисковой памяти. Виртуальное пространство памяти разбито на страницы, в физической оперативной памяти в каждый момент времени присутствует только часть из них. Если затребованная процессором область в данный момент не отображена в физической памяти, он вырабатывает исключение (внутреннее прерывание), по которому операционная система программно организует замещение страницы, называемое своппингом (Swapping). Виртуальную память поддерживают процессоры, работающие в защищенном режиме начиная с 286. Однако реально она начала использоваться только в операционных системах и оболочках для 32 -х разрядных процессоров (386+).

Виртуальная память (Virtual Memory) представляет собой программно-аппаратное средство расширения пространства памяти, предоставляемой программе в качестве оперативной. Она физически реализуется в оперативной и дисковой памяти. Виртуальное пространство памяти разбито на страницы, в физической оперативной памяти в каждый момент времени присутствует только часть из них. Если затребованная процессором область в данный момент не отображена в физической памяти, он вырабатывает исключение (внутреннее прерывание), по которому операционная система программно организует замещение страницы, называемое своппингом (Swapping). Виртуальную память поддерживают процессоры, работающие в защищенном режиме начиная с 286. Однако реально она начала использоваться только в операционных системах и оболочках для 32 -х разрядных процессоров (386+).

Оптимизация использования оперативной памяти Оптимизация использования памяти преследует два цели: увеличение объема памяти, доступной приложениям и повышение быстродействия обращений к памяти. Если размер установленной памяти больше 640 Кбайт, возможны различные варианты использования последних 348 Кбайт из первого мегабайта физической памяти: • память не используется • область (или её часть) перемещается в конец дополнительной памяти (возможно лишь при небольших объемах установленной памяти) • область (или её часть) используется в качестве теневой памяти адаптеров и ROM BIOS

Оптимизация использования оперативной памяти Оптимизация использования памяти преследует два цели: увеличение объема памяти, доступной приложениям и повышение быстродействия обращений к памяти. Если размер установленной памяти больше 640 Кбайт, возможны различные варианты использования последних 348 Кбайт из первого мегабайта физической памяти: • память не используется • область (или её часть) перемещается в конец дополнительной памяти (возможно лишь при небольших объемах установленной памяти) • область (или её часть) используется в качестве теневой памяти адаптеров и ROM BIOS

Оптимизация использования оперативной памяти Острее всего проблема обеспечения памятью стоит для приложений MS-DOS, которым доступна только стандартная память. После загрузки ОС и необходимых резидентных драйверов (русификаторы клавиатуры, экрана и принтера, драйвер мыши) на долю приложений может остаться около 500 Кбайт, а то и меньше. Однако, по крайней мере, часть драйверов можно загрузить в верхнюю память UMA. Для того, чтобы туда поместилось как можно больше модулей, следует провести её оптимизацию, т. е. конфигурирование базовых адресов буферной и постоянной памяти адаптеров, при котором свободные области UMA получались бы максимально возможного размера. Работу приложений MS-DOS значительно ускоряет затенение BIOS (как системной, так и BIOS графического адаптера и дискового контроллера).

Оптимизация использования оперативной памяти Острее всего проблема обеспечения памятью стоит для приложений MS-DOS, которым доступна только стандартная память. После загрузки ОС и необходимых резидентных драйверов (русификаторы клавиатуры, экрана и принтера, драйвер мыши) на долю приложений может остаться около 500 Кбайт, а то и меньше. Однако, по крайней мере, часть драйверов можно загрузить в верхнюю память UMA. Для того, чтобы туда поместилось как можно больше модулей, следует провести её оптимизацию, т. е. конфигурирование базовых адресов буферной и постоянной памяти адаптеров, при котором свободные области UMA получались бы максимально возможного размера. Работу приложений MS-DOS значительно ускоряет затенение BIOS (как системной, так и BIOS графического адаптера и дискового контроллера).

Оптимизация использования оперативной памяти Для многозадачных ОС защищенного режима затенение BIOS ускоряет только процесс загрузки, т. к. в рабочем режиме в основном используются драйверы, загружаемые в ОЗУ. Приложения ОС Windows пользуются виртуальной памятью, но при малом размере физически установленной памяти своппинг становится слишком интенсивным и работа приложений сильно замедляется. Поскольку размер файла подкачки меняется с течением времени, надо следить за фрагментацией диска. При работе приложений реального времени, интенсивно обращающихся к диску, желательно, чтобы файл подкачки находился на другом диске. Увеличение физического объема оперативной памяти может привести и к снижению производительности. Это возможно, когда системная плата (или процессор) не способна кэшировать весь объем ОЗУ и ядро Windows попадает в некэшируемую область.

Оптимизация использования оперативной памяти Для многозадачных ОС защищенного режима затенение BIOS ускоряет только процесс загрузки, т. к. в рабочем режиме в основном используются драйверы, загружаемые в ОЗУ. Приложения ОС Windows пользуются виртуальной памятью, но при малом размере физически установленной памяти своппинг становится слишком интенсивным и работа приложений сильно замедляется. Поскольку размер файла подкачки меняется с течением времени, надо следить за фрагментацией диска. При работе приложений реального времени, интенсивно обращающихся к диску, желательно, чтобы файл подкачки находился на другом диске. Увеличение физического объема оперативной памяти может привести и к снижению производительности. Это возможно, когда системная плата (или процессор) не способна кэшировать весь объем ОЗУ и ядро Windows попадает в некэшируемую область.