79996bc347c87d8d1adcba990c294237.ppt

- Количество слайдов: 23

Операции поддержки алгоритмов шифрования с открытым ключом и их реализация в микропроцессоре «Эльбрус» Выполнил: Скрябин Иван, 513 Научный руководитель: Сахин Ю. Х.

Операции поддержки алгоритмов шифрования с открытым ключом и их реализация в микропроцессоре «Эльбрус» Выполнил: Скрябин Иван, 513 Научный руководитель: Сахин Ю. Х.

Постановка задачи Развитие интернета и электронной коммерции вынуждает производителей микропроцессоров внедрять аппаратную поддержку алгоритмов шифрования: q Intel (Westmere), AMD (Bulldozer) - AES q VIA Padlock Security Engine - AES, SHA-1, SHA-256 - Умножение Монтгомери (поддержка шифров с открытым ключом) q SPARC T 3 (Криптографический ускоритель в каждом из 16 ядер) - DES, AES, Kasumi, MD 5, SHA-1, SHA-256, SHA-512 - Modular Arithmetic Unit (поддержка шифров с открытым ключом) ЗАДАЧА: Предложить решение по аппаратной поддержке алгоритмов шифрования с открытым ключом в микропроцессорах «Эльбрус»

Постановка задачи Развитие интернета и электронной коммерции вынуждает производителей микропроцессоров внедрять аппаратную поддержку алгоритмов шифрования: q Intel (Westmere), AMD (Bulldozer) - AES q VIA Padlock Security Engine - AES, SHA-1, SHA-256 - Умножение Монтгомери (поддержка шифров с открытым ключом) q SPARC T 3 (Криптографический ускоритель в каждом из 16 ядер) - DES, AES, Kasumi, MD 5, SHA-1, SHA-256, SHA-512 - Modular Arithmetic Unit (поддержка шифров с открытым ключом) ЗАДАЧА: Предложить решение по аппаратной поддержке алгоритмов шифрования с открытым ключом в микропроцессорах «Эльбрус»

Два типа алгоритмов шифрования q Шифры с секретным ключом Encrypt Decrypt Bob Alice Ø Многочисленное повторение одного и того же набора простых операций (раундов) над блоками данных 128 / 64 / 256 бит Ø Большое разнообразие шифров – сложно выделить общие операции, эффективней реализовывать конкретные алгоритмы q Шифры с открытым ключом Encrypt Decrypt Bob Alice Ø Сложные операции (умножение по модулю) над очень большими числами (192 – 3072 бит) Ø В основе – операции умножения и возведения в степень по модулю

Два типа алгоритмов шифрования q Шифры с секретным ключом Encrypt Decrypt Bob Alice Ø Многочисленное повторение одного и того же набора простых операций (раундов) над блоками данных 128 / 64 / 256 бит Ø Большое разнообразие шифров – сложно выделить общие операции, эффективней реализовывать конкретные алгоритмы q Шифры с открытым ключом Encrypt Decrypt Bob Alice Ø Сложные операции (умножение по модулю) над очень большими числами (192 – 3072 бит) Ø В основе – операции умножения и возведения в степень по модулю

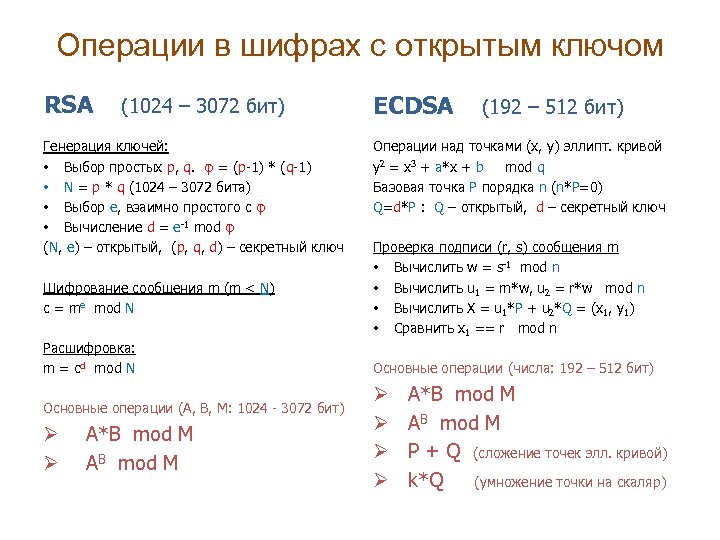

Операции в шифрах с открытым ключом RSA (1024 – 3072 бит) Генерация ключей: • Выбор простых p, q. φ = (p-1) * (q-1) • N = p * q (1024 – 3072 бита) • Выбор e, взаимно простого с φ • Вычисление d = e-1 mod φ (N, e) – открытый, (p, q, d) – секретный ключ Шифрование сообщения m (m < N) c = me mod N Расшифровка: m = cd mod N Основные операции (A, B, M: 1024 - 3072 бит) Ø Ø A*B mod M AB mod M ECDSA (192 – 512 бит) Операции над точками (x, y) эллипт. кривой y 2 = x 3 + a*x + b mod q Базовая точка P порядка n (n*P=0) Q=d*P : Q – открытый, d – секретный ключ Проверка подписи (r, s) сообщения m • Вычислить w = s-1 mod n • Вычислить u 1 = m*w, u 2 = r*w mod n • Вычислить X = u 1*P + u 2*Q = (x 1, y 1) • Сравнить x 1 == r mod n Основные операции (числа: 192 – 512 бит) Ø Ø A*B mod M AB mod M P + Q (сложение точек элл. кривой) k*Q (умножение точки на скаляр)

Операции в шифрах с открытым ключом RSA (1024 – 3072 бит) Генерация ключей: • Выбор простых p, q. φ = (p-1) * (q-1) • N = p * q (1024 – 3072 бита) • Выбор e, взаимно простого с φ • Вычисление d = e-1 mod φ (N, e) – открытый, (p, q, d) – секретный ключ Шифрование сообщения m (m < N) c = me mod N Расшифровка: m = cd mod N Основные операции (A, B, M: 1024 - 3072 бит) Ø Ø A*B mod M AB mod M ECDSA (192 – 512 бит) Операции над точками (x, y) эллипт. кривой y 2 = x 3 + a*x + b mod q Базовая точка P порядка n (n*P=0) Q=d*P : Q – открытый, d – секретный ключ Проверка подписи (r, s) сообщения m • Вычислить w = s-1 mod n • Вычислить u 1 = m*w, u 2 = r*w mod n • Вычислить X = u 1*P + u 2*Q = (x 1, y 1) • Сравнить x 1 == r mod n Основные операции (числа: 192 – 512 бит) Ø Ø A*B mod M AB mod M P + Q (сложение точек элл. кривой) k*Q (умножение точки на скаляр)

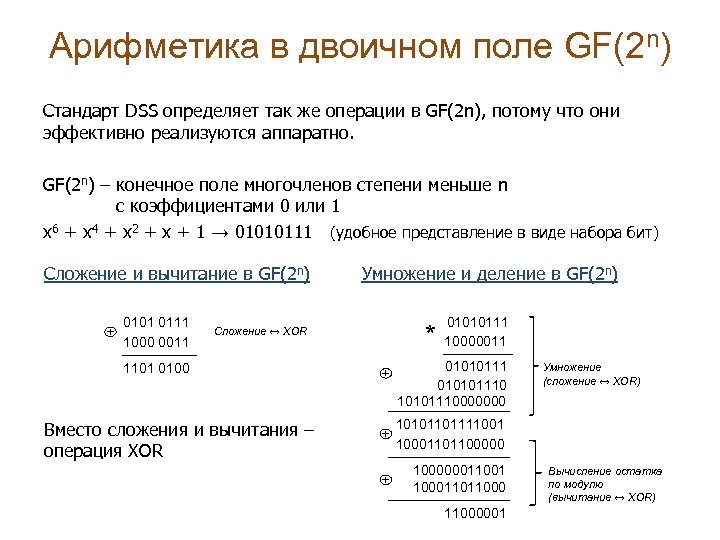

Арифметика в двоичном поле GF(2 n) Стандарт DSS определяет так же операции в GF(2 n), потому что они эффективно реализуются аппаратно. GF(2 n) – конечное поле многочленов степени меньше n с коэффициентами 0 или 1 x 6 + x 4 + x 2 + x + 1 → 01010111 (удобное представление в виде набора бит) Сложение и вычитание в GF(2 n) 0101 0111 1000 0011 Сложение ↔ XOR 1101 0100 Вместо сложения и вычитания – операция XOR Умножение и деление в GF(2 n) * 01010111 10000011 010101110000000 Умножение (сложение ↔ XOR) 10101101111001 10001101100000011001 100011011000001 Вычисление остатка по модулю (вычитание ↔ XOR)

Арифметика в двоичном поле GF(2 n) Стандарт DSS определяет так же операции в GF(2 n), потому что они эффективно реализуются аппаратно. GF(2 n) – конечное поле многочленов степени меньше n с коэффициентами 0 или 1 x 6 + x 4 + x 2 + x + 1 → 01010111 (удобное представление в виде набора бит) Сложение и вычитание в GF(2 n) 0101 0111 1000 0011 Сложение ↔ XOR 1101 0100 Вместо сложения и вычитания – операция XOR Умножение и деление в GF(2 n) * 01010111 10000011 010101110000000 Умножение (сложение ↔ XOR) 10101101111001 10001101100000011001 100011011000001 Вычисление остатка по модулю (вычитание ↔ XOR)

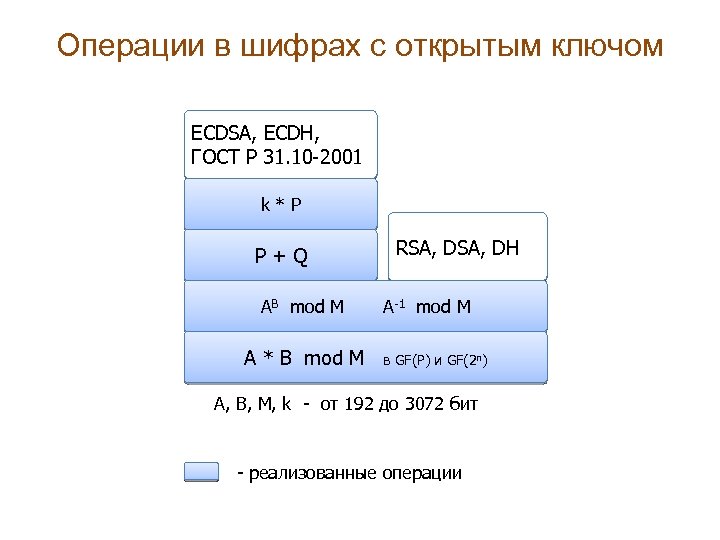

Операции в шифрах с открытым ключом ECDSA, ECDH, ГОСТ Р 31. 10 -2001 k*P P+Q AB mod M A * B mod M RSA, DH A-1 mod M в GF(P) и GF(2 n) A, B, M, k - от 192 до 3072 бит - реализованные операции

Операции в шифрах с открытым ключом ECDSA, ECDH, ГОСТ Р 31. 10 -2001 k*P P+Q AB mod M A * B mod M RSA, DH A-1 mod M в GF(P) и GF(2 n) A, B, M, k - от 192 до 3072 бит - реализованные операции

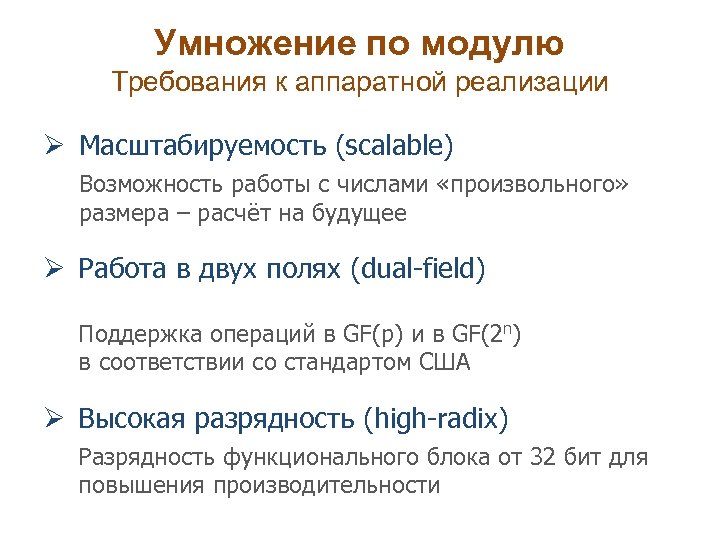

Умножение по модулю Требования к аппаратной реализации Ø Масштабируемость (scalable) Возможность работы с числами «произвольного» размера – расчёт на будущее Ø Работа в двух полях (dual-field) Поддержка операций в GF(p) и в GF(2 n) в соответствии со стандартом США Ø Высокая разрядность (high-radix) Разрядность функционального блока от 32 бит для повышения производительности

Умножение по модулю Требования к аппаратной реализации Ø Масштабируемость (scalable) Возможность работы с числами «произвольного» размера – расчёт на будущее Ø Работа в двух полях (dual-field) Поддержка операций в GF(p) и в GF(2 n) в соответствии со стандартом США Ø Высокая разрядность (high-radix) Разрядность функционального блока от 32 бит для повышения производительности

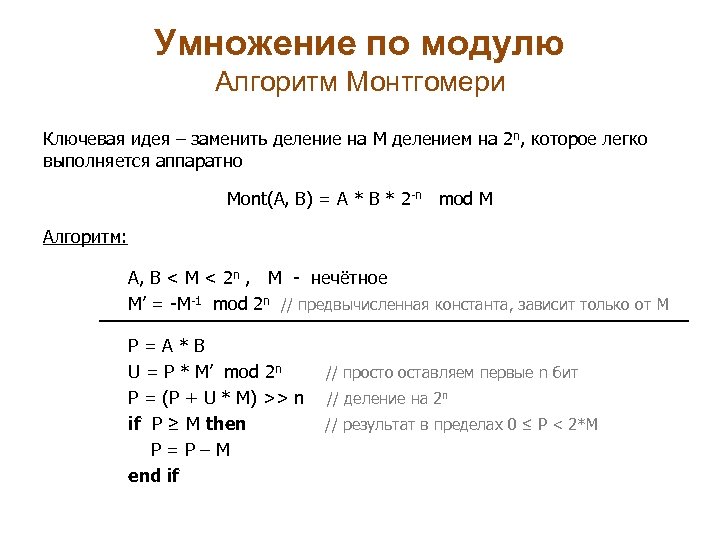

Умножение по модулю Алгоритм Монтгомери Ключевая идея – заменить деление на M делением на 2 n, которое легко выполняется аппаратно Mont(A, B) = A * B * 2 -n mod M Алгоритм: A, B < M < 2 n , M - нечётное M’ = -M-1 mod 2 n // предвычисленная константа, зависит только от M P=A*B U = P * M’ mod 2 n P = (P + U * M) >> n if P ≥ M then P=P–M end if // просто оставляем первые n бит // деление на 2 n // результат в пределах 0 ≤ P < 2*M

Умножение по модулю Алгоритм Монтгомери Ключевая идея – заменить деление на M делением на 2 n, которое легко выполняется аппаратно Mont(A, B) = A * B * 2 -n mod M Алгоритм: A, B < M < 2 n , M - нечётное M’ = -M-1 mod 2 n // предвычисленная константа, зависит только от M P=A*B U = P * M’ mod 2 n P = (P + U * M) >> n if P ≥ M then P=P–M end if // просто оставляем первые n бит // деление на 2 n // результат в пределах 0 ≤ P < 2*M

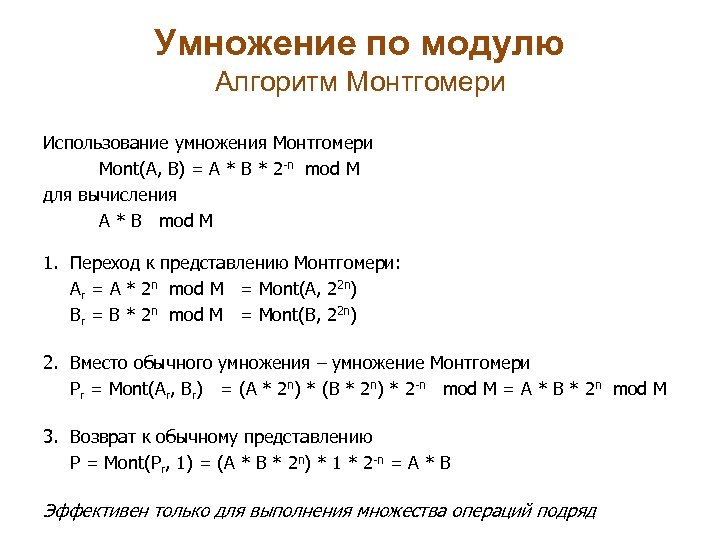

Умножение по модулю Алгоритм Монтгомери Использование умножения Монтгомери Mont(A, B) = A * B * 2 -n mod M для вычисления A * B mod M 1. Переход к представлению Монтгомери: Ar = A * 2 n mod M = Mont(A, 22 n) Br = B * 2 n mod M = Mont(B, 22 n) 2. Вместо обычного умножения – умножение Монтгомери Pr = Mont(Ar, Br) = (A * 2 n) * (B * 2 n) * 2 -n mod M = A * B * 2 n mod M 3. Возврат к обычному представлению P = Mont(Pr, 1) = (A * B * 2 n) * 1 * 2 -n = A * B Эффективен только для выполнения множества операций подряд

Умножение по модулю Алгоритм Монтгомери Использование умножения Монтгомери Mont(A, B) = A * B * 2 -n mod M для вычисления A * B mod M 1. Переход к представлению Монтгомери: Ar = A * 2 n mod M = Mont(A, 22 n) Br = B * 2 n mod M = Mont(B, 22 n) 2. Вместо обычного умножения – умножение Монтгомери Pr = Mont(Ar, Br) = (A * 2 n) * (B * 2 n) * 2 -n mod M = A * B * 2 n mod M 3. Возврат к обычному представлению P = Mont(Pr, 1) = (A * B * 2 n) * 1 * 2 -n = A * B Эффективен только для выполнения множества операций подряд

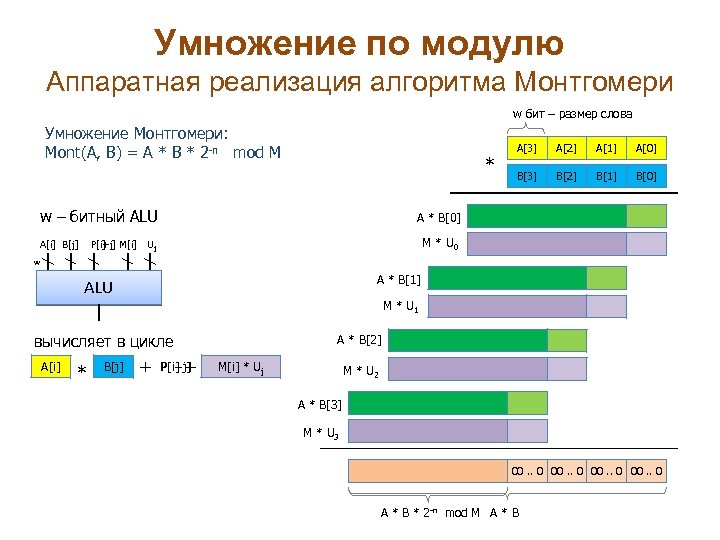

Умножение по модулю Аппаратная реализация алгоритма Монтгомери w бит – размер слова Умножение Монтгомери: Mont(A, B) = A * B * 2 -n mod M * w – битный ALU A[i] B[j] P[i+j] P[i] M[i] A[3] A[2] A[1] A[0] B[3] B[2] B[1] B[0] A * B[0] M * U 0 Uj w A * B[1] ALU M * U 1 вычисляет в цикле A[i] * B[j] + P[i+j] P[i] + A * B[2] M[i] * Uj M * U 2 A * B[3] M * U 3 00. . 0 A * B * 2 -n mod M A * B

Умножение по модулю Аппаратная реализация алгоритма Монтгомери w бит – размер слова Умножение Монтгомери: Mont(A, B) = A * B * 2 -n mod M * w – битный ALU A[i] B[j] P[i+j] P[i] M[i] A[3] A[2] A[1] A[0] B[3] B[2] B[1] B[0] A * B[0] M * U 0 Uj w A * B[1] ALU M * U 1 вычисляет в цикле A[i] * B[j] + P[i+j] P[i] + A * B[2] M[i] * Uj M * U 2 A * B[3] M * U 3 00. . 0 A * B * 2 -n mod M A * B

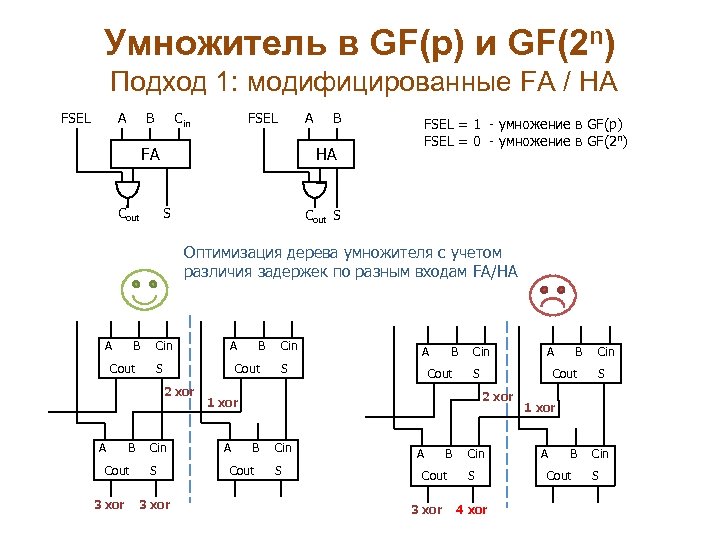

Умножитель в GF(p) и GF(2 n) Подход 1: модифицированные FA / HA FSEL A B Cin FSEL A FA Cout B FSEL = 1 - умножение в GF(p) FSEL = 0 - умножение в GF(2 n) HA S Cout S Оптимизация дерева умножителя с учетом различия задержек по разным входам FA/HA A B Cout Cin B Cout 3 xor B Cout S 2 xor A A Cin S 3 xor Cin A S B Cout Cin S A B Cout 3 xor B Cout 2 xor 1 xor A A Cin S 4 xor Cin S 1 xor A B Cout Cin S

Умножитель в GF(p) и GF(2 n) Подход 1: модифицированные FA / HA FSEL A B Cin FSEL A FA Cout B FSEL = 1 - умножение в GF(p) FSEL = 0 - умножение в GF(2 n) HA S Cout S Оптимизация дерева умножителя с учетом различия задержек по разным входам FA/HA A B Cout Cin B Cout 3 xor B Cout S 2 xor A A Cin S 3 xor Cin A S B Cout Cin S A B Cout 3 xor B Cout 2 xor 1 xor A A Cin S 4 xor Cin S 1 xor A B Cout Cin S

Умножитель в GF(p) и GF(2 n) Подход 2: специальное построение дерева ai * b j w 2 carry FA / HA array sum. . . Wallace tree carry FA / HA array sum Final adder 2 w Результат в GF(p) 2 w - 1 Результат в GF(2 n)

Умножитель в GF(p) и GF(2 n) Подход 2: специальное построение дерева ai * b j w 2 carry FA / HA array sum. . . Wallace tree carry FA / HA array sum Final adder 2 w Результат в GF(p) 2 w - 1 Результат в GF(2 n)

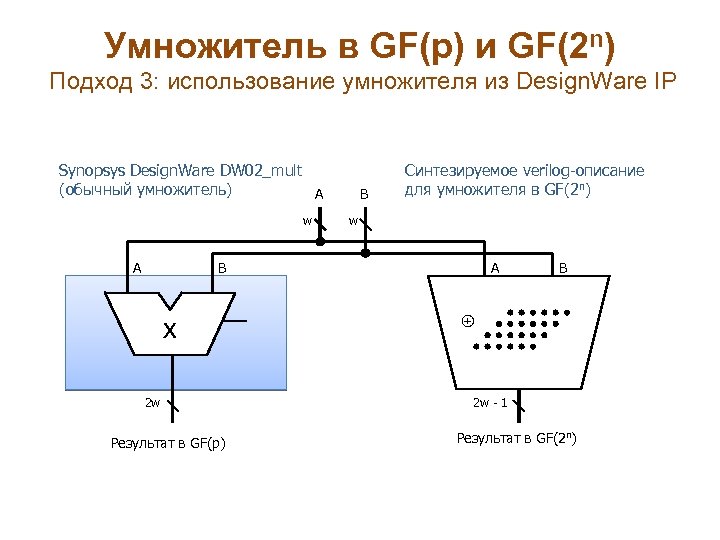

Умножитель в GF(p) и GF(2 n) Подход 3: использование умножителя из Design. Ware IP Synopsys Design. Ware DW 02_mult (обычный умножитель) A w A B B Синтезируемое verilog-описание для умножителя в GF(2 n) w A B x 2 w Результат в GF(p) 2 w - 1 Результат в GF(2 n)

Умножитель в GF(p) и GF(2 n) Подход 3: использование умножителя из Design. Ware IP Synopsys Design. Ware DW 02_mult (обычный умножитель) A w A B B Синтезируемое verilog-описание для умножителя в GF(2 n) w A B x 2 w Результат в GF(p) 2 w - 1 Результат в GF(2 n)

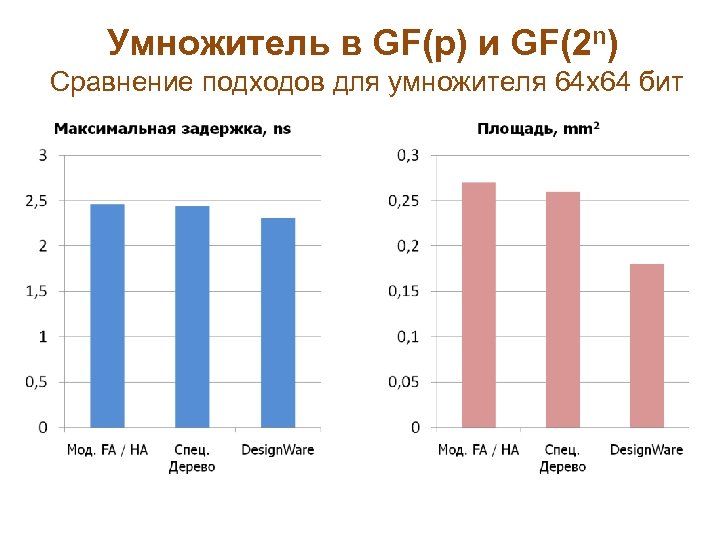

Умножитель в GF(p) и GF(2 n) Сравнение подходов для умножителя 64 x 64 бит

Умножитель в GF(p) и GF(2 n) Сравнение подходов для умножителя 64 x 64 бит

![Умножитель Монтгомери Базовый блок montmul_unit (64 бит) A[i] B[j] P[i] M[i] / M’ 0 Умножитель Монтгомери Базовый блок montmul_unit (64 бит) A[i] B[j] P[i] M[i] / M’ 0](https://present5.com/presentation/79996bc347c87d8d1adcba990c294237/image-15.jpg) Умножитель Монтгомери Базовый блок montmul_unit (64 бит) A[i] B[j] P[i] M[i] / M’ 0 precalc x x U + + C S (C, S) = C + A[i]*B[j] + P[i] + M[i]*U P[i-1]

Умножитель Монтгомери Базовый блок montmul_unit (64 бит) A[i] B[j] P[i] M[i] / M’ 0 precalc x x U + + C S (C, S) = C + A[i]*B[j] + P[i] + M[i]*U P[i-1]

![Умножитель Монтгомери Организация конвейера MEMORY B[j] стадии задержки A[i] M[i] FSM montmul unit FSM Умножитель Монтгомери Организация конвейера MEMORY B[j] стадии задержки A[i] M[i] FSM montmul unit FSM](https://present5.com/presentation/79996bc347c87d8d1adcba990c294237/image-16.jpg) Умножитель Монтгомери Организация конвейера MEMORY B[j] стадии задержки A[i] M[i] FSM montmul unit FSM P[i] montmul unit FSM result

Умножитель Монтгомери Организация конвейера MEMORY B[j] стадии задержки A[i] M[i] FSM montmul unit FSM P[i] montmul unit FSM result

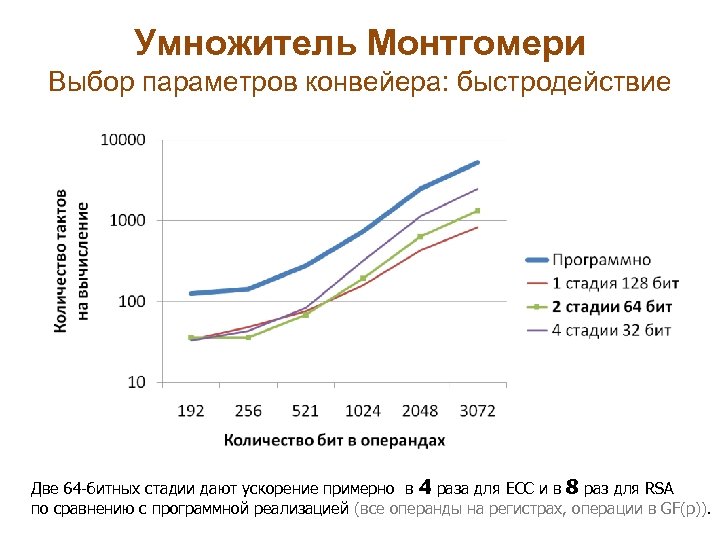

Умножитель Монтгомери Выбор параметров конвейера: быстродействие Две 64 -битных стадии дают ускорение примерно в 4 раза для ECC и в 8 раз для RSA по сравнению с программной реализацией (все операнды на регистрах, операции в GF(p)).

Умножитель Монтгомери Выбор параметров конвейера: быстродействие Две 64 -битных стадии дают ускорение примерно в 4 раза для ECC и в 8 раз для RSA по сравнению с программной реализацией (все операнды на регистрах, операции в GF(p)).

Умножитель Монтгомери Выбор параметров конвейера: площадь

Умножитель Монтгомери Выбор параметров конвейера: площадь

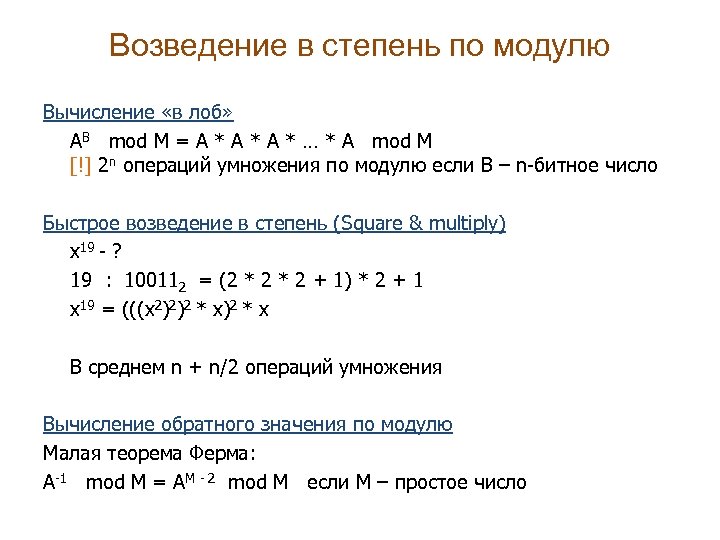

Возведение в степень по модулю Вычисление «в лоб» AB mod M = A * A * … * A mod M [!] 2 n операций умножения по модулю если B – n-битное число Быстрое возведение в степень (Square & multiply) x 19 - ? 19 : 100112 = (2 * 2 + 1) * 2 + 1 x 19 = (((x 2)2)2 * x В среднем n + n/2 операций умножения Вычисление обратного значения по модулю Малая теорема Ферма: A-1 mod M = AM - 2 mod M если M – простое число

Возведение в степень по модулю Вычисление «в лоб» AB mod M = A * A * … * A mod M [!] 2 n операций умножения по модулю если B – n-битное число Быстрое возведение в степень (Square & multiply) x 19 - ? 19 : 100112 = (2 * 2 + 1) * 2 + 1 x 19 = (((x 2)2)2 * x В среднем n + n/2 операций умножения Вычисление обратного значения по модулю Малая теорема Ферма: A-1 mod M = AM - 2 mod M если M – простое число

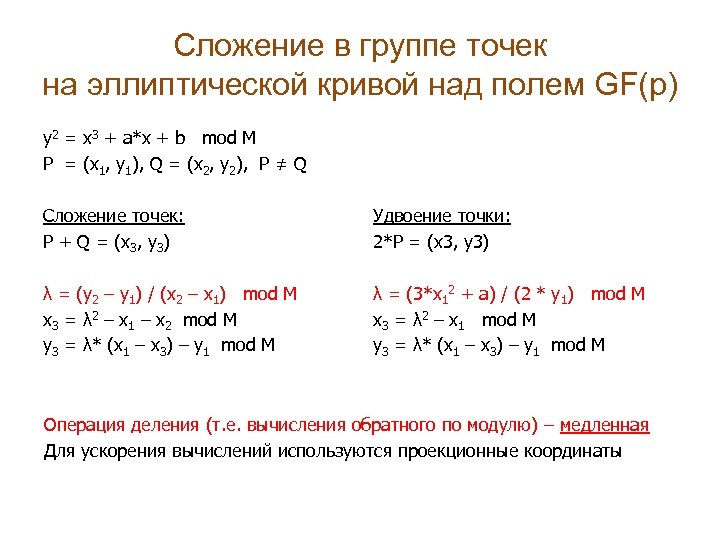

Сложение в группе точек на эллиптической кривой над полем GF(p) y 2 = x 3 + a*x + b mod M P = (x 1, y 1), Q = (x 2, y 2), P ≠ Q Сложение точек: P + Q = (x 3, y 3) Удвоение точки: 2*P = (x 3, y 3) λ = (y 2 – y 1) / (x 2 – x 1) mod M x 3 = λ 2 – x 1 – x 2 mod M y 3 = λ* (x 1 – x 3) – y 1 mod M λ = (3*x 12 + a) / (2 * y 1) mod M x 3 = λ 2 – x 1 mod M y 3 = λ* (x 1 – x 3) – y 1 mod M Операция деления (т. е. вычисления обратного по модулю) – медленная Для ускорения вычислений используются проекционные координаты

Сложение в группе точек на эллиптической кривой над полем GF(p) y 2 = x 3 + a*x + b mod M P = (x 1, y 1), Q = (x 2, y 2), P ≠ Q Сложение точек: P + Q = (x 3, y 3) Удвоение точки: 2*P = (x 3, y 3) λ = (y 2 – y 1) / (x 2 – x 1) mod M x 3 = λ 2 – x 1 – x 2 mod M y 3 = λ* (x 1 – x 3) – y 1 mod M λ = (3*x 12 + a) / (2 * y 1) mod M x 3 = λ 2 – x 1 mod M y 3 = λ* (x 1 – x 3) – y 1 mod M Операция деления (т. е. вычисления обратного по модулю) – медленная Для ускорения вычислений используются проекционные координаты

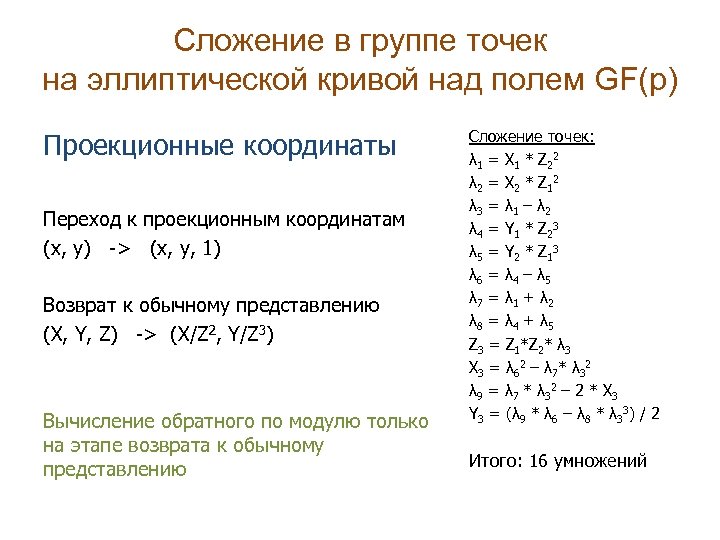

Сложение в группе точек на эллиптической кривой над полем GF(p) Проекционные координаты Переход к проекционным координатам (x, y) -> (x, y, 1) Возврат к обычному представлению (X, Y, Z) -> (X/Z 2, Y/Z 3) Вычисление обратного по модулю только на этапе возврата к обычному представлению Сложение точек: λ 1 = X 1 * Z 22 λ 2 = X 2 * Z 12 λ 3 = λ 1 – λ 2 λ 4 = Y 1 * Z 23 λ 5 = Y 2 * Z 13 λ 6 = λ 4 – λ 5 λ 7 = λ 1 + λ 2 λ 8 = λ 4 + λ 5 Z 3 = Z 1*Z 2* λ 3 X 3 = λ 62 – λ 7* λ 32 λ 9 = λ 7 * λ 32 – 2 * X 3 Y 3 = (λ 9 * λ 6 – λ 8 * λ 33) / 2 Итого: 16 умножений

Сложение в группе точек на эллиптической кривой над полем GF(p) Проекционные координаты Переход к проекционным координатам (x, y) -> (x, y, 1) Возврат к обычному представлению (X, Y, Z) -> (X/Z 2, Y/Z 3) Вычисление обратного по модулю только на этапе возврата к обычному представлению Сложение точек: λ 1 = X 1 * Z 22 λ 2 = X 2 * Z 12 λ 3 = λ 1 – λ 2 λ 4 = Y 1 * Z 23 λ 5 = Y 2 * Z 13 λ 6 = λ 4 – λ 5 λ 7 = λ 1 + λ 2 λ 8 = λ 4 + λ 5 Z 3 = Z 1*Z 2* λ 3 X 3 = λ 62 – λ 7* λ 32 λ 9 = λ 7 * λ 32 – 2 * X 3 Y 3 = (λ 9 * λ 6 – λ 8 * λ 33) / 2 Итого: 16 умножений

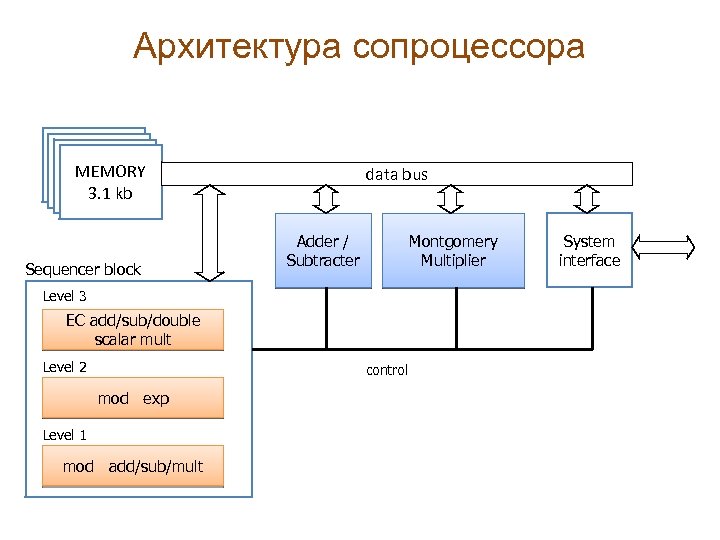

Архитектура сопроцессора MEMORY 3. 1 kb Sequencer block data bus Adder / Subtracter Montgomery Multiplier Level 3 EC add/sub/double scalar mult Level 2 control mod exp Level 1 mod add/sub/mult System interface

Архитектура сопроцессора MEMORY 3. 1 kb Sequencer block data bus Adder / Subtracter Montgomery Multiplier Level 3 EC add/sub/double scalar mult Level 2 control mod exp Level 1 mod add/sub/mult System interface

Результаты работы Разработано verilog-описание и произведён синтез криптографического сопроцессора для микропроцессора «Эльбрус» , позволяющего аппаратно ускорить выполнение алгоритмов шифрования с открытым ключом. Особенности: q Поддержка современных алгоритмов шифрования с открытым ключом, включая алгоритмы на эллиптических кривых q Масштабируемость – размеры операндов ограничены только объёмом памяти. q Эффективность (умножение по модулю в 4 -8 раз быстрее программной реализации) Основные характеристики: q Тактовая частота 500 MHz (90 nm) q 3. 1 kb внутренней памяти – поддержка до 4096 бит RSA и до 571 бит ECC q Площадь ~ 1. 2 мм 2

Результаты работы Разработано verilog-описание и произведён синтез криптографического сопроцессора для микропроцессора «Эльбрус» , позволяющего аппаратно ускорить выполнение алгоритмов шифрования с открытым ключом. Особенности: q Поддержка современных алгоритмов шифрования с открытым ключом, включая алгоритмы на эллиптических кривых q Масштабируемость – размеры операндов ограничены только объёмом памяти. q Эффективность (умножение по модулю в 4 -8 раз быстрее программной реализации) Основные характеристики: q Тактовая частота 500 MHz (90 nm) q 3. 1 kb внутренней памяти – поддержка до 4096 бит RSA и до 571 бит ECC q Площадь ~ 1. 2 мм 2