b8920c9081512fef8a2883e962b6edf0.ppt

- Количество слайдов: 16

Open System. C Initiative (OSCI) Verification Working Group Status Adam Rose, Motorola VWG Chair

Open System. C Initiative (OSCI) Verification Working Group Status Adam Rose, Motorola VWG Chair

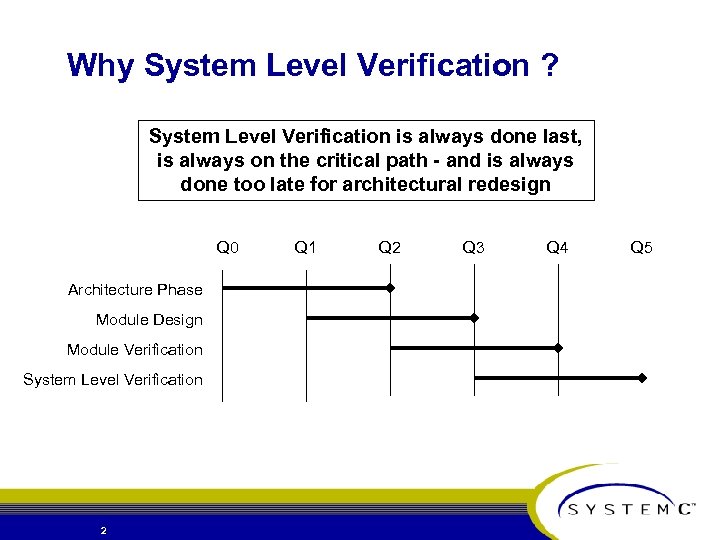

Why System Level Verification ? System Level Verification is always done last, is always on the critical path - and is always done too late for architectural redesign Q 0 Architecture Phase Module Design Module Verification System Level Verification 2 Q 1 Q 2 Q 3 Q 4 Q 5

Why System Level Verification ? System Level Verification is always done last, is always on the critical path - and is always done too late for architectural redesign Q 0 Architecture Phase Module Design Module Verification System Level Verification 2 Q 1 Q 2 Q 3 Q 4 Q 5

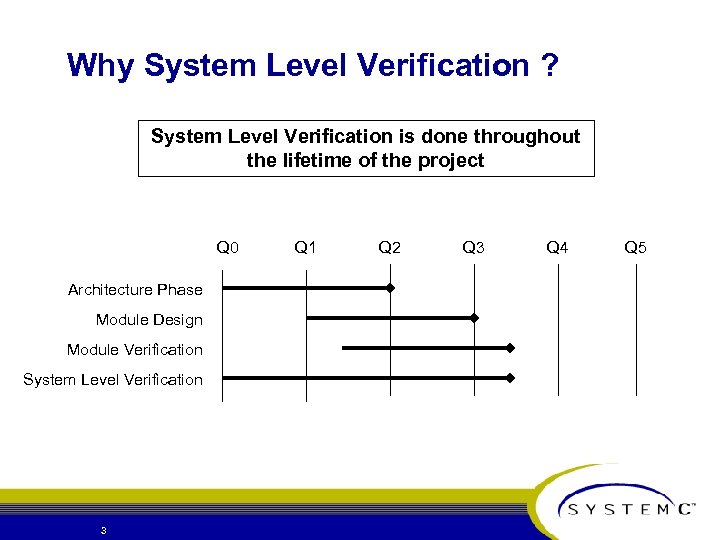

Why System Level Verification ? System Level Verification is done throughout the lifetime of the project Q 0 Architecture Phase Module Design Module Verification System Level Verification 3 Q 1 Q 2 Q 3 Q 4 Q 5

Why System Level Verification ? System Level Verification is done throughout the lifetime of the project Q 0 Architecture Phase Module Design Module Verification System Level Verification 3 Q 1 Q 2 Q 3 Q 4 Q 5

History and Membership § Joint Proposal by Fujitsu, ST and Motorola – System. C 2. 0 provides a platform upon which various design methodologies can be built – System. C should also provide a platform upon which various verification methodologies can be built § Membership – Cadence, Forte, Synopsys, ARM, Fujitsu, Motorola 4

History and Membership § Joint Proposal by Fujitsu, ST and Motorola – System. C 2. 0 provides a platform upon which various design methodologies can be built – System. C should also provide a platform upon which various verification methodologies can be built § Membership – Cadence, Forte, Synopsys, ARM, Fujitsu, Motorola 4

Status § Areas Covered – Data Introspection – Randomisation, Constraints, Weighting – Manual Transaction Recording § Spec has been agreed in VWG – Will be written up and submitted for OSCI review and approval immediately after DAC – Production code expected by end 2002 5

Status § Areas Covered – Data Introspection – Randomisation, Constraints, Weighting – Manual Transaction Recording § Spec has been agreed in VWG – Will be written up and submitted for OSCI review and approval immediately after DAC – Production code expected by end 2002 5

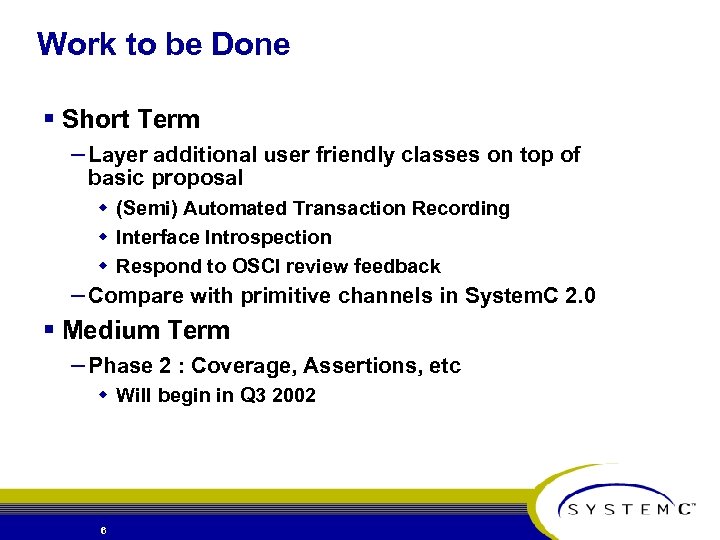

Work to be Done § Short Term – Layer additional user friendly classes on top of basic proposal w (Semi) Automated Transaction Recording w Interface Introspection w Respond to OSCI review feedback – Compare with primitive channels in System. C 2. 0 § Medium Term – Phase 2 : Coverage, Assertions, etc w Will begin in Q 3 2002 6

Work to be Done § Short Term – Layer additional user friendly classes on top of basic proposal w (Semi) Automated Transaction Recording w Interface Introspection w Respond to OSCI review feedback – Compare with primitive channels in System. C 2. 0 § Medium Term – Phase 2 : Coverage, Assertions, etc w Will begin in Q 3 2002 6

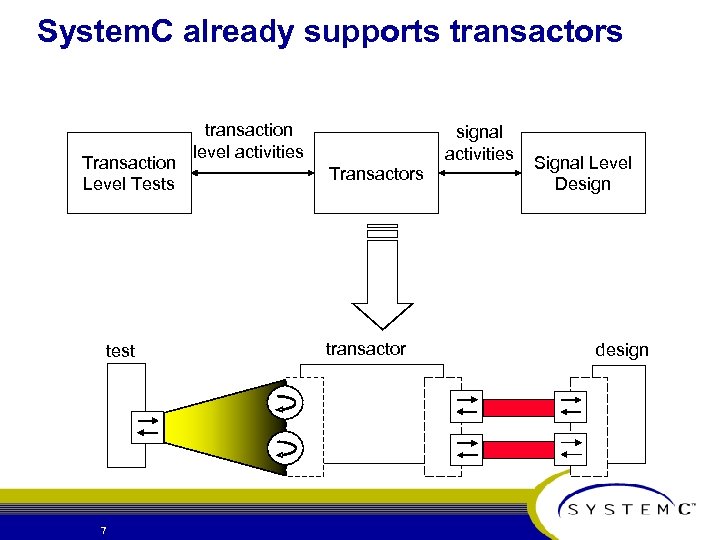

System. C already supports transactors Transaction Level Tests test 7 transaction level activities Transactors transactor signal activities Signal Level Design design

System. C already supports transactors Transaction Level Tests test 7 transaction level activities Transactors transactor signal activities Signal Level Design design

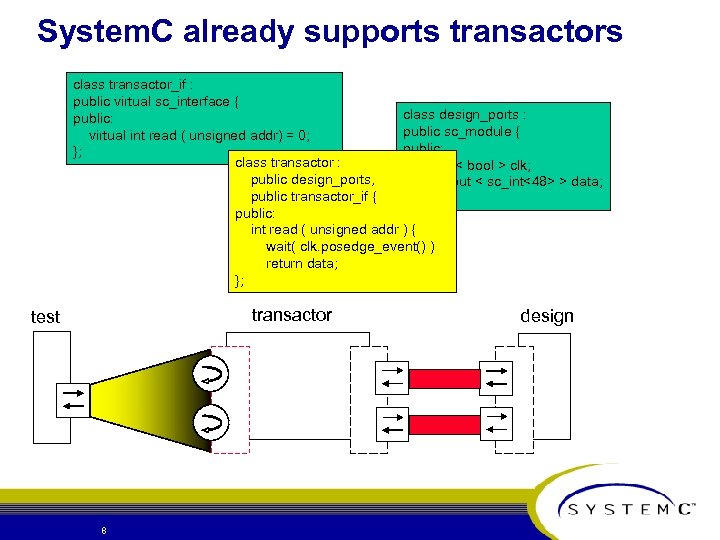

System. C already supports transactors class transactor_if : public virtual sc_interface { class design_ports : public sc_module { virtual int read ( unsigned addr) = 0; public: }; class transactor : sc_in < bool > clk; public design_ports, sc_inout < sc_int<48> > data; public transactor_if { }; public: int read ( unsigned addr ) { wait( clk. posedge_event() ) return data; }; transactor test 8 design

System. C already supports transactors class transactor_if : public virtual sc_interface { class design_ports : public sc_module { virtual int read ( unsigned addr) = 0; public: }; class transactor : sc_in < bool > clk; public design_ports, sc_inout < sc_int<48> > data; public transactor_if { }; public: int read ( unsigned addr ) { wait( clk. posedge_event() ) return data; }; transactor test 8 design

![Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } 9 Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } 9](https://present5.com/presentation/b8920c9081512fef8a2883e962b6edf0/image-9.jpg) Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } 9

Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } 9

![Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize](https://present5.com/presentation/b8920c9081512fef8a2883e962b6edf0/image-10.jpg) Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize whole packet scv_smart_ptr < packet_t > p ; p->next( ); 10

Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize whole packet scv_smart_ptr < packet_t > p ; p->next( ); 10

![Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize](https://present5.com/presentation/b8920c9081512fef8a2883e962b6edf0/image-11.jpg) Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize whole packet scv_smart_ptr < packet_t > p ; p->next( ); // keep src fixed scv_smart_ptr < packet_t > p ; p->src. disable_randomization(); p->next( ); 11

Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize whole packet scv_smart_ptr < packet_t > p ; p->next( ); // keep src fixed scv_smart_ptr < packet_t > p ; p->src. disable_randomization(); p->next( ); 11

![Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize](https://present5.com/presentation/b8920c9081512fef8a2883e962b6edf0/image-12.jpg) Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize whole packet scv_smart_ptr < packet_t > p ; p->next( ); // keep address fixed scv_smart_ptr < packet_t > p ; p->address. disable_randomization(); p->next( ); 12 // basic constraint class my_constraint : public scv_constraint_base { public: scv_smart_ptr < packet_t > p ; SCV_CONSTRAINT_CTOR( my_constraint ) { SCV_CONSTRAINT ( p -> src ( ) != p -> dest ( ) ); for ( int i = 0; i < 8 ; ++ i ) SCV_CONSTRAINT ( p -> data [ i ] < 10 ); } };

Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize whole packet scv_smart_ptr < packet_t > p ; p->next( ); // keep address fixed scv_smart_ptr < packet_t > p ; p->address. disable_randomization(); p->next( ); 12 // basic constraint class my_constraint : public scv_constraint_base { public: scv_smart_ptr < packet_t > p ; SCV_CONSTRAINT_CTOR( my_constraint ) { SCV_CONSTRAINT ( p -> src ( ) != p -> dest ( ) ); for ( int i = 0; i < 8 ; ++ i ) SCV_CONSTRAINT ( p -> data [ i ] < 10 ); } };

![Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize](https://present5.com/presentation/b8920c9081512fef8a2883e962b6edf0/image-13.jpg) Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize whole packet scv_smart_ptr < packet_t > p ; p->next( ); // keep address fixed scv_smart_ptr < packet_t > p ; p->address. disable_randomization(); p->next( ); // constrain packet my_constraint c( “constraint” ); c. p->next( ); 13 // basic constraint class my_constraint : public scv_constraint_base { public: scv_smart_ptr < packet_t > p ; SCV_CONSTRAINT_CTOR( my_constraint ) { SCV_CONSTRAINT ( p -> src ( ) != p -> dest ( ) ); for ( int i = 0; i < 8 ; ++ i ) SCV_CONSTRAINT ( p -> data [ i ] < 10 ); } };

Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize whole packet scv_smart_ptr < packet_t > p ; p->next( ); // keep address fixed scv_smart_ptr < packet_t > p ; p->address. disable_randomization(); p->next( ); // constrain packet my_constraint c( “constraint” ); c. p->next( ); 13 // basic constraint class my_constraint : public scv_constraint_base { public: scv_smart_ptr < packet_t > p ; SCV_CONSTRAINT_CTOR( my_constraint ) { SCV_CONSTRAINT ( p -> src ( ) != p -> dest ( ) ); for ( int i = 0; i < 8 ; ++ i ) SCV_CONSTRAINT ( p -> data [ i ] < 10 ); } };

![Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize](https://present5.com/presentation/b8920c9081512fef8a2883e962b6edf0/image-14.jpg) Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize whole packet scv_smart_ptr < packet_t > p ; p->next( ); // keep address fixed scv_smart_ptr < packet_t > p ; p->address. disable_randomization(); p->next( ); // constrain packet new_constraint c( “constraint” ); c. p->next( ); 14 // basic constraint class my_constraint : public scv_constraint_base { public: scv_smart_ptr < packet_t > p ; SCV_CONSTRAINT_CTOR( my_constraint ) { SCV_CONSTRAINT ( p -> src ( ) != p -> dest ( ) ); for ( int i = 0; i < 8 ; ++ i ) SCV_CONSTRAINT ( p -> data [ i ]() < 10 ); } }; // extended constraint class new_constraint : public my_constraint { public: SCV_CONSTRAINT_CTOR( new_constraint ) { SCV_CONSTRAINT_BASE( my_constraint ) SCV_CONSTRAINT ( p -> data [ 0 ]() != p -> data [ 1 ]() ); } };

Constrained Randomization class packet_t { sc_uint<8> src; sc_uint<8> dest; sc_uint<32> data[8]; } // randomize whole packet scv_smart_ptr < packet_t > p ; p->next( ); // keep address fixed scv_smart_ptr < packet_t > p ; p->address. disable_randomization(); p->next( ); // constrain packet new_constraint c( “constraint” ); c. p->next( ); 14 // basic constraint class my_constraint : public scv_constraint_base { public: scv_smart_ptr < packet_t > p ; SCV_CONSTRAINT_CTOR( my_constraint ) { SCV_CONSTRAINT ( p -> src ( ) != p -> dest ( ) ); for ( int i = 0; i < 8 ; ++ i ) SCV_CONSTRAINT ( p -> data [ i ]() < 10 ); } }; // extended constraint class new_constraint : public my_constraint { public: SCV_CONSTRAINT_CTOR( new_constraint ) { SCV_CONSTRAINT_BASE( my_constraint ) SCV_CONSTRAINT ( p -> data [ 0 ]() != p -> data [ 1 ]() ); } };

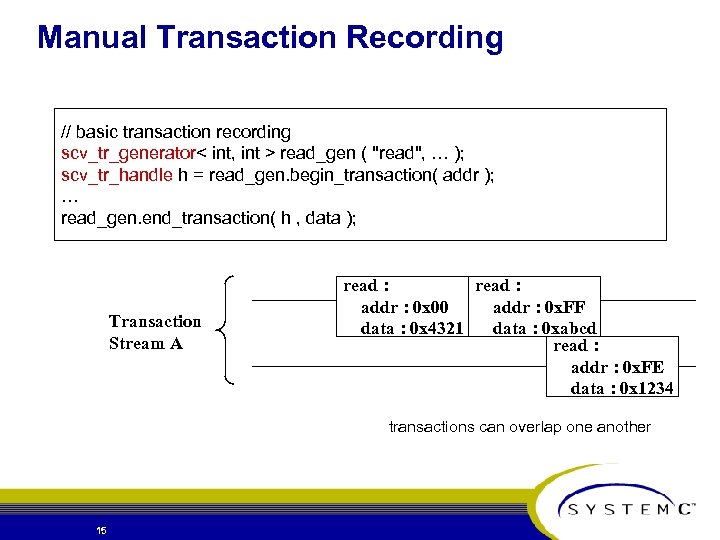

Manual Transaction Recording // basic transaction recording scv_tr_generator< int, int > read_gen ( "read", … ); scv_tr_handle h = read_gen. begin_transaction( addr ); … read_gen. end_transaction( h , data ); Transaction Stream A read : addr : 0 x 00 addr : 0 x. FF data : 0 x 4321 data : 0 xabcd read : addr : 0 x. FE data : 0 x 1234 transactions can overlap one another 15

Manual Transaction Recording // basic transaction recording scv_tr_generator< int, int > read_gen ( "read", … ); scv_tr_handle h = read_gen. begin_transaction( addr ); … read_gen. end_transaction( h , data ); Transaction Stream A read : addr : 0 x 00 addr : 0 x. FF data : 0 x 4321 data : 0 xabcd read : addr : 0 x. FE data : 0 x 1234 transactions can overlap one another 15

Why System. C ? Verification Modelling ü ü Design ü 16

Why System. C ? Verification Modelling ü ü Design ü 16