Вводная лекция ЭВМ.ppt

- Количество слайдов: 98

ОБЩИЕ ПРИНЦИПЫ ЭВМ Классификация , история, архитектура

Вычислительная система • Совокупность устройств, предназначенных для автоматической или автоматизированной обработки данных, называют вычислительной техникой. • Конкретный набор взаимодействующих между собой устройств и программ, предназначенный для обслуживания одного рабочего участка, называют вычислительной системой. • Центральным устройством большинства вычислительных систем является компьютер. • Компьютер - это электронной прибор, предназначенный для автоматизации создания, хранения, обработки и транспортировки данных.

Классификация средств ЭВТ По принципу действия вычислительные машины делятся на три больших класса: аналоговые (АВМ), цифровые (ЦВМ) и гибридные (ГВМ). Критерием деления вычислительных машин на эти три класса является форма представления информации, с которой они работают. АВМ - вычислительные машины, которые работают с информацией, представленной в непрерывной (аналоговой) форме, т. е. в виде непрерывного ряда значений какой-либо физической величины (чаще всего электрического напряжения). ЦВМ - вычислительные машины, предназначенные для работы с информацией, представленной в дискретной, цифровой форме. ГВМ - вычислительные машины комбинированного действия, работают с информацией, представленной в цифровой и в аналоговой форме; они совмещают в себе достоинства АВМ и ЦВМ. Гибридные вычислительные машины целесообразно использовать для решения задач управления сложными быстродействующими техническими комплексами.

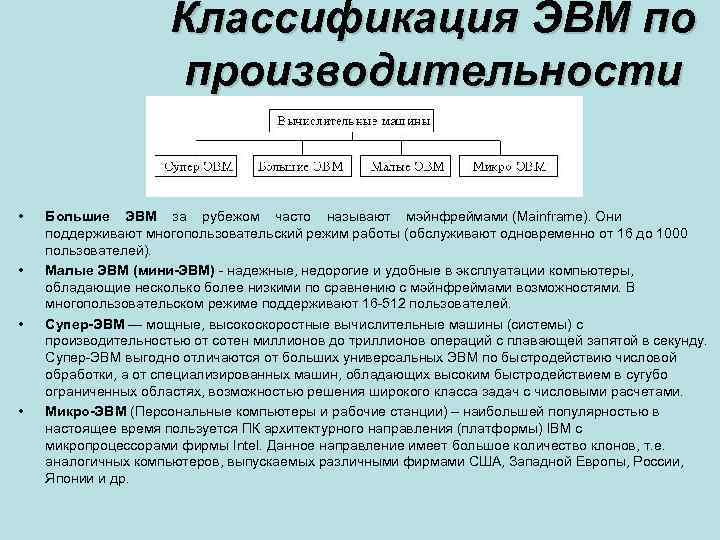

Классификация ЭВМ по производительности • • Большие ЭВМ за рубежом часто называют мэйнфреймами (Mainframe). Они поддерживают многопользовательский режим работы (обслуживают одновременно от 16 до 1000 пользователей). Малые ЭВМ (мини-ЭВМ) - надежные, недорогие и удобные в эксплуатации компьютеры, обладающие несколько более низкими по сравнению с мэйнфреймами возможностями. В многопользовательском режиме поддерживают 16 -512 пользователей. Супер-ЭВМ — мощные, высокоскоростные вычислительные машины (системы) с производительностью от сотен миллионов до триллионов операций с плавающей запятой в секунду. Супер-ЭВМ выгодно отличаются от больших универсальных ЭВМ по быстродействию числовой обработки, а от специализированных машин, обладающих высоким быстродействием в сугубо ограниченных областях, возможностью решения широкого класса задач с числовыми расчетами. Микро-ЭВМ (Персональные компьютеры и рабочие станции) – наибольшей популярностью в настоящее время пользуется ПК архитектурного направления (платформы) IBM с микропроцессорами фирмы Intel. Данное направление имеет большое количество клонов, т. е. аналогичных компьютеров, выпускаемых различными фирмами США, Западной Европы, России, Японии и др.

Электронно-вычислительные машины принято классифицировать по целому ряду признаков, в частности: по функциональным возможностям и характеру решаемых задач, принципу действия, назначению, способам организации вычислительного процесса и вычислительной мощности, конструктивным особенностям. Кроме этого, электронно-вычислительные машины (ЭВМ) классифицируются по поколениям.

Первая ЭВМ Физически первая цифровая ВМ была сконструирована в 1935 году фирмой Белл (США). Такого же вида машина была сконструирована для специальных задач под руководством К. Цузе (1941, Германия). Попытка построения универсальной ЭВМ была предпринята Айтнетом (США). Она получила название “Марк-1”. Спроектирована и изготовлена в Гарвардском университете.

Первые ЭВМ Первая ЭВМ, разработанная на электронных компонентах, изготовлена в 1942 году (“Эниак”). Серийный выпуск в 1945 -1946 годах. Разработана в Пенсельванском университете под руководством Маушли и Энкера. В 1943 году под руководством Тьюринга была разработана ЭВМ “Колос”. После рассекречивания архивов в 70 -х годах оказалось, что первая ЭВМ была разработана в 1939 году выходцем из Германии Антоносовым, которая получила название “ABC”.

Характеристики ВМ (работали с 23 разрядными десятичными цифрами): • Программа вводилась по-командно с перфоленты. • Сложение 2 -х чисел 0. 3 секунды • Умножение 2 -х чисел 6 секунд • Деление 2 -х чисел 11 секунд. Релейная основа была ненадежна. Для ЭВМ были разработаны специальные реле. На которых была разработана ВМ “Марк-2”. Реальный отсчет ВТ ведется с перехода от реле к триггерам. Триггер был изобретен в 1918 году в России Бонч-Бруевичем.

Поколения ЭВМ • Первое (ламповые, начало 50 -х) • Второе (транзисторные 60 -е) • Третье (интегральная системотехника, конец 60 х) • Четвертое (БИС, конец 70 -х) • Пятое (микропроцессорные, конец 80 -х) • Шестое (Оптоэлектронные с массовым параллелизмом и нейронной структурой, наше тысячелетие)

Первое поколение Ламповые ЭВМ, промышленный выпуск начат в начале 50 -х годов. В нашей стране началом выпуска можно считать начало 50 -х годов “МЭСМ”. Разработана под руководством Лебедева. В 1952 -1953 годах на этой основе, под руководством Мельникова и Бурцева была разработана “БЭСМ-1” (Большая электронная счетная машина). А на ее основе был произведен серийный выпуск машины “БЭСМ-2”. В это же время в США выпускают машину “Эдвак”. Технические характеристики машины “БЭСМ-2” были гораздо выше. Это было связано с тем, что в “БЭСМ-2”, использовались два совершенно новых принципа: конвейеризации и стека. Для “БЭСМ-2”, быстродействие АЛУ составляло порядка 10000 операций в секунду. В 1953 году была разработана машина “Стрела” под руководством Василевского. А так же в Московском Энергетическом институте под руководством академика Брука были разработаны ЭВМ получившие название “М”. В Минске был создан завод по производству ЭВМ, серийное производство машин “Минск”. В городе Пензе было создано ОКБ (отдел конструкторского бюро) под руководством академика Рамеева, где разработали и выпускали серийно ЭВМ “Урал”. Структура ЭВМ первого поколения полностью соответствовали машине фон Неймана. Технические характеристики машин были значительно ниже характеристик современных ПК. Программирование велось в машинных кодах. Емкость ОЗУ – 2 тысячи слов. Ввод информации с перфоленты и кинопленки.

Второе поколение Связывают с переходом от ламповых к транзисторным ЭВМ. Транзисторы позволяли обеспечить большую надежность, быстродействие и меньшее энергопотребление (среднее время отказа около 100 часов, тогда как на машинах первого поколение около 10 часов, энергоемкость на два порядка ниже, по сравнению с машинами первого поколения). Переход к печатному монтажу также улучшило надежность.

Архитектура второго поколения

Второе поколение Начинается бурное развитие математического и программного обеспечения. Высшая точка: создание алгоритмических языков (Fortran, ALGOL). Создаются простейшие компиляторы и интерпретаторы. Становится нецелесообразна работа пользователя у пульта управления. Основным режимом становится работа через операторов. Появляются многопрограммные ЭВМ. Многопрограммность достигается за счет программной обработки. Для работы в пакетном режиме создаются первые мониторы и supervisor’ы. Вследствие чего происходит резкое увеличение использование ЭВМ второго поколения.

Третье поколение В конце 60 -х годов появляются первые машины третьего поколения. Переход к третьему поколению ЭВМ связывают с серьезными архитектурными изменениями. Изменение технической базы связано с переходом на интегральную схематехнику. Правда степень интеграции была небольшой. Вследствие чего произошло заметное увеличение надежности. В машинах третьего поколения формируется концепция канала, начинается работа с распараллеливанием процессора, появляется микропрограммное управление, иерархируется память, впервые вводится понятие агрегатирования.

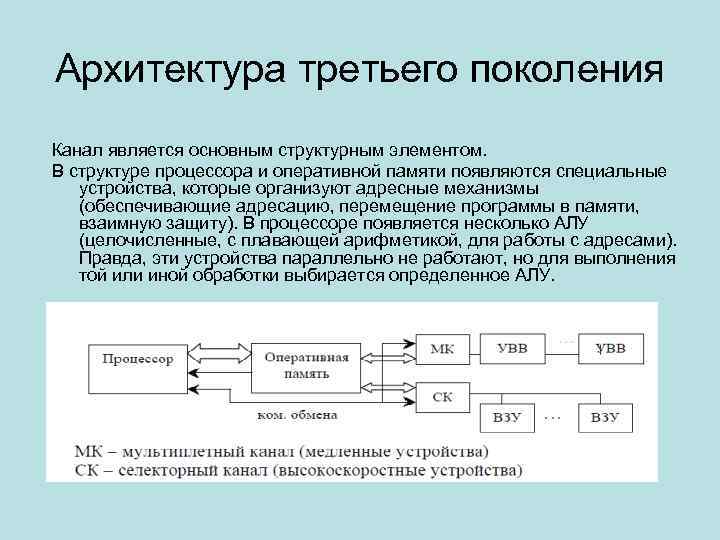

Архитектура третьего поколения Канал является основным структурным элементом. В структуре процессора и оперативной памяти появляются специальные устройства, которые организуют адресные механизмы (обеспечивающие адресацию, перемещение программы в памяти, взаимную защиту). В процессоре появляется несколько АЛУ (целочисленные, с плавающей арифметикой, для работы с адресами). Правда, эти устройства параллельно не работают, но для выполнения той или иной обработки выбирается определенное АЛУ.

Третье поколение • В памяти четко выделяется основная память, к которой процессор обращается непосредственно, и массовая память, емкость которой значительно больше емкости основной памяти, но непосредственно процессору она недоступна. Тем более данные с внешних устройств непосредственно недоступны процессору. Так как память иерархична, то создаются механизмы для управления памятью. Развивается и внутренняя память процессора (создаются предпосылки кэширования). В конце третьего поколения ЭВМ появляется концепция управления виртуальной памяти, развиваются внешние устройства и терминальное оборудование. Самое главное в тот период: унификация ЭВМ по конструктивно - технологическим параметрам. ЭВМ третьего поколения начинают выпускаться сериями или семействами, совместимыми моделями. Дальнейшее развитие математического и программного обеспечения приводит к созданию пакетных программ для решения типовых задач, проблемно - ориентированных программных языков (для решения задач отдельной категории) и впервые создаются уникальные программные комплексы, - операционные системы (разработаны IBM).

Четвертое поколение В конце 70 -х кодов появляются первые ЭВМ четвертого поколения. Связано с переходом на интегральные схемы средней и большой степени интеграции. Характерные свойства ЭВМ четвертого поколения: • Мультипроцессорность • Параллельно – последовательная обработка • Языки высокого уровня • Появляются первые сети ЭВМ

Технические характеристики 4 -го поколения • Средняя задержка сигнала 0. 7 нс. /вентиль (вентиль – типовая схема) • Впервые основная память – полупроводниковая. Время выработки данного из такой памяти 100 -150 нс. Емкость 1012 – 1013 символов. • Впервые применяется аппаратная реализация оперативной системы • Модульное построение стало применяться и для программных средств Основная внимание машин четвертого поколения было направлено на сервис (улучшение общения ЭВМ и человека).

Пятое поколение В конце 80 -х годов появляются первые ЭВМ пятого поколения. Пятое поколение ЭВМ связывают с переходом к микропроцессорам. С точки зрения структурного построения характерна максимальная децентрализация управления. С точки зрения программного и математического обеспечения – переход на работу в программных средах и оболочках. Производительность 108 - 109 операций в секунду. Для пятого и шестого поколения характерны многопроцессорные структуры созданные на упрощенных микропроцессорах, которых очень много (решающие поля или среды). Создаются ЭВМ ориентированные на языки высокого уровня.

Современные тенденции В этот период существуют две диаметрально противоположных тенденции: • Персонификация ресурсов • Коллективизация ресурсов (коллективный доступ – сети)

Шестое поколение Оптоэлектронные ЭВМ с массовым параллелизмом и нейронной структурой — с сетью из большого числа (десятки тысяч) несложных микропроцессоров, моделирующих структуру нейронных биологических систем.

Эволюция ЭВМ и вычислительных систем (ВС) История ВТ отсчитывается с опубликования работы Джона фон Неймана. Впервые возможность построения цифровой ВМ была доказана английским математиком Тьюрингом в 1936 году. Он показал, что любой алгоритм реализуется с помощью его дискретного автомата, который был назван машиной Тьюринга. Независимо это же доказал Пост (машина Поста).

быстродействие

Суперкомпьютеры • 1972. «ILLIAC-IV» (США) – 20 млн. операций в секунду – многопроцессорная система • 1976. «Cray-1» (США) – 166 млн. операций в секунду – память 8 Мб – векторные вычисления • 1980. «Эльбрус-1» (СССР) – 15 млн. операций в секунду – память 64 Мб • 1985. «Эльбрус-2» (СССР) – – 8 процессоров 125 млн. операций в секунду память 144 Мб водяное охлаждение

Суперкомпьютеры • 1985. «Cray-2» – 2 млрд. операций в секунду • 1989. «Cray-3» – 5 млрд. операций в секунду • 1995. «GRAPE-4» (Япония) – 1692 процессора – 1, 08 трлн. операций в секунду • 2002. «Earth Simulator» (NEC) – 5120 процессоров – 36 трлн. операций в секунду • 2007. «Blue. Gene/L» (IBM) – 212 992 процессора – 596 трлн. операций в секунду

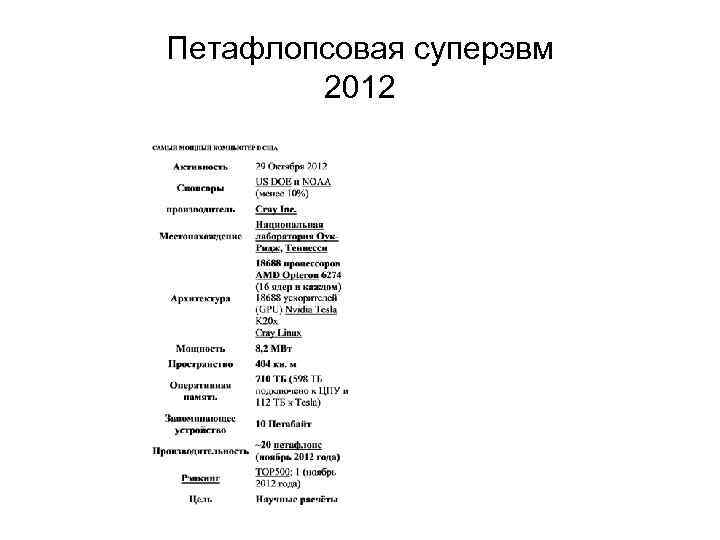

Петафлопсовая суперэвм 2012

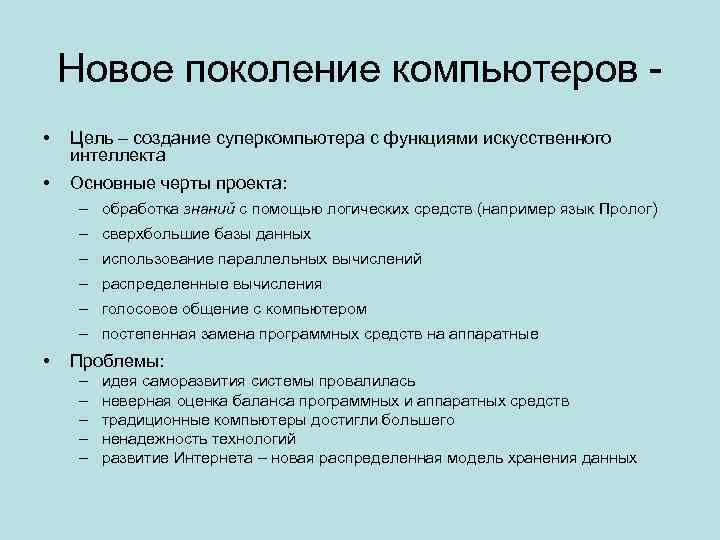

Новое поколение компьютеров • Цель – создание суперкомпьютера с функциями искусственного интеллекта • Основные черты проекта: – обработка знаний с помощью логических средств (например язык Пролог) – сверхбольшие базы данных – использование параллельных вычислений – распределенные вычисления – голосовое общение с компьютером – постепенная замена программных средств на аппаратные • Проблемы: – – – идея саморазвития системы провалилась неверная оценка баланса программных и аппаратных средств традиционные компьютеры достигли большего ненадежность технологий развитие Интернета – новая распределенная модель хранения данных

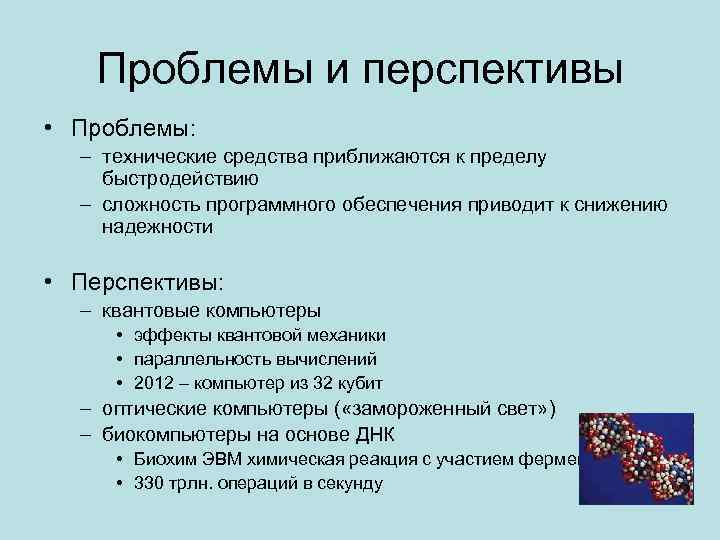

Проблемы и перспективы • Проблемы: – технические средства приближаются к пределу быстродействию – сложность программного обеспечения приводит к снижению надежности • Перспективы: – квантовые компьютеры • эффекты квантовой механики • параллельность вычислений • 2012 – компьютер из 32 кубит – оптические компьютеры ( «замороженный свет» ) – биокомпьютеры на основе ДНК • Биохим ЭВМ химическая реакция с участием ферментов • 330 трлн. операций в секунду

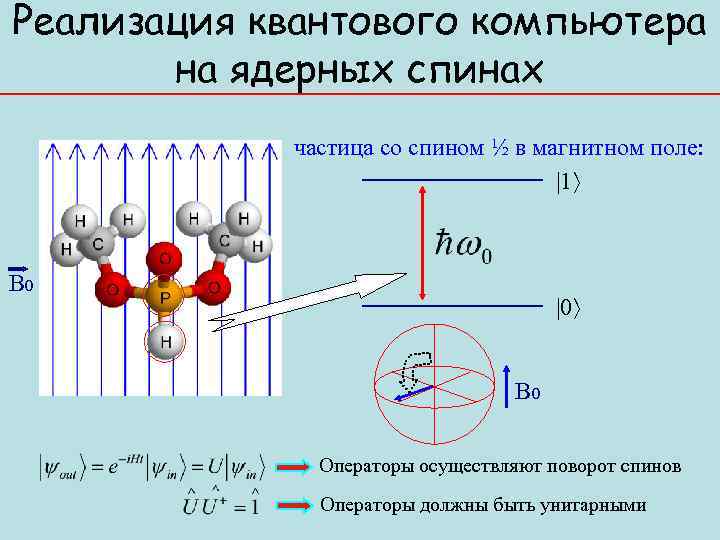

Реализация квантового компьютера на ядерных спинах частица со спином ½ в магнитном поле: |1 B 0 |0 B 0 Операторы осуществляют поворот спинов Операторы должны быть унитарными

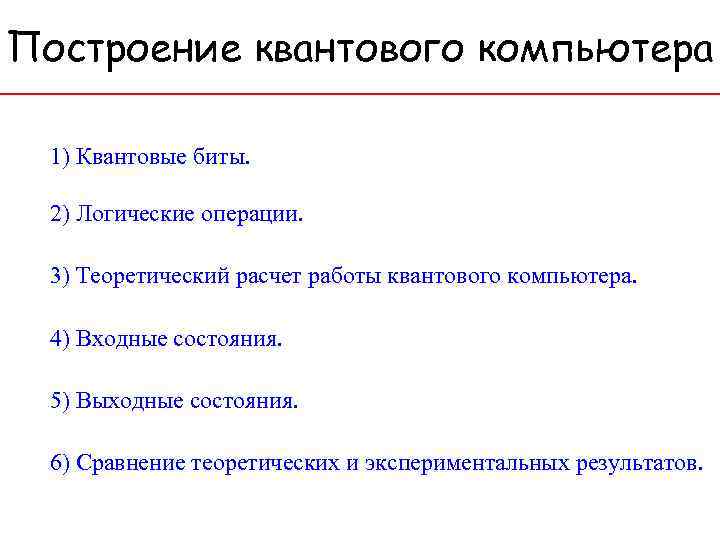

Построение квантового компьютера 1) Квантовые биты. 2) Логические операции. 3) Теоретический расчет работы квантового компьютера. 4) Входные состояния. 5) Выходные состояния. 6) Сравнение теоретических и экспериментальных результатов.

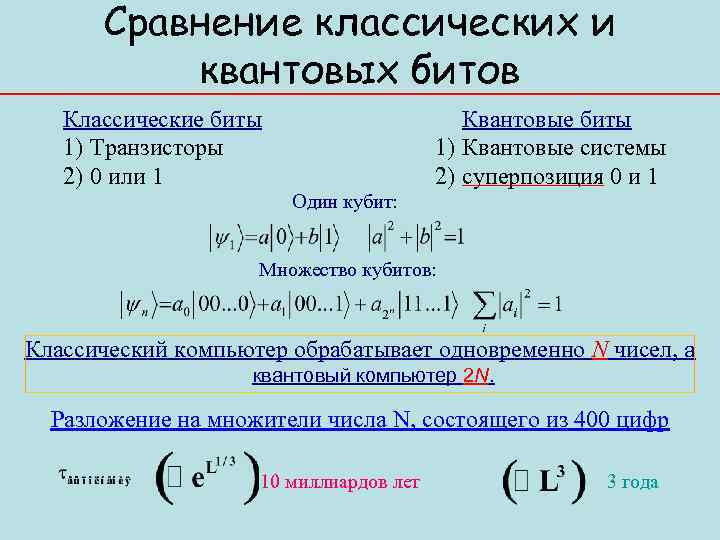

Сравнение классических и квантовых битов Классические биты 1) Транзисторы 2) 0 или 1 Квантовые биты 1) Квантовые системы 2) суперпозиция 0 и 1 Один кубит: Множество кубитов: Классический компьютер обрабатывает одновременно N чисел, а квантовый компьютер 2 N. Разложение на множители числа N, состоящего из 400 цифр 10 миллиардов лет 3 года

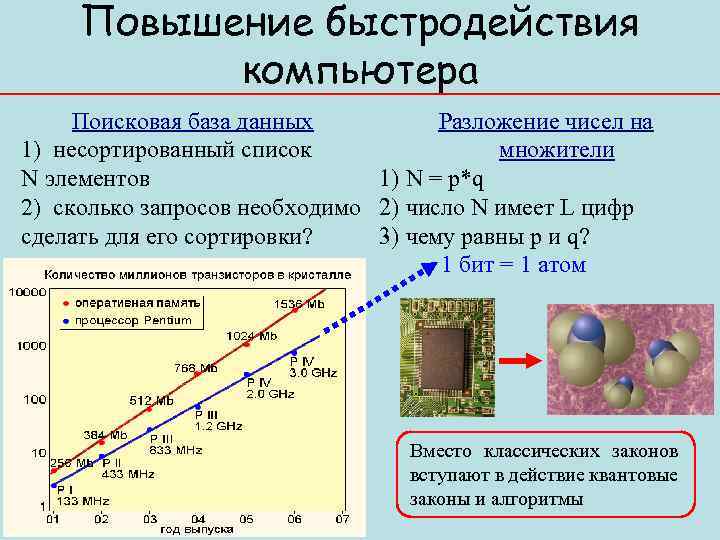

Повышение быстродействия компьютера Поисковая база данных Разложение чисел на 1) несортированный список множители N элементов 1) N = p*q 2) сколько запросов необходимо 2) число N имеет L цифр сделать для его сортировки? 3) чему равны p и q? 1 бит = 1 атом Вместо классических законов вступают в действие квантовые законы и алгоритмы

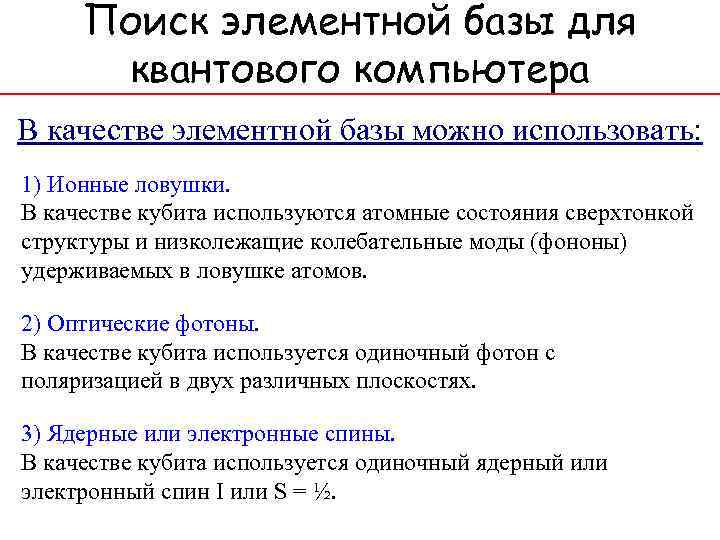

Поиск элементной базы для квантового компьютера В качестве элементной базы можно использовать: 1) Ионные ловушки. В качестве кубита используются атомные состояния сверхтонкой структуры и низколежащие колебательные моды (фононы) удерживаемых в ловушке атомов. 2) Оптические фотоны. В качестве кубита используется одиночный фотон с поляризацией в двух различных плоскостях. 3) Ядерные или электронные спины. В качестве кубита используется одиночный ядерный или электронный спин I или S = ½.

По способу организации вычислительного процесса ЭВМ подразделяются на многопроцессорные и однопроцессорные, а также параллельные и последовательные.

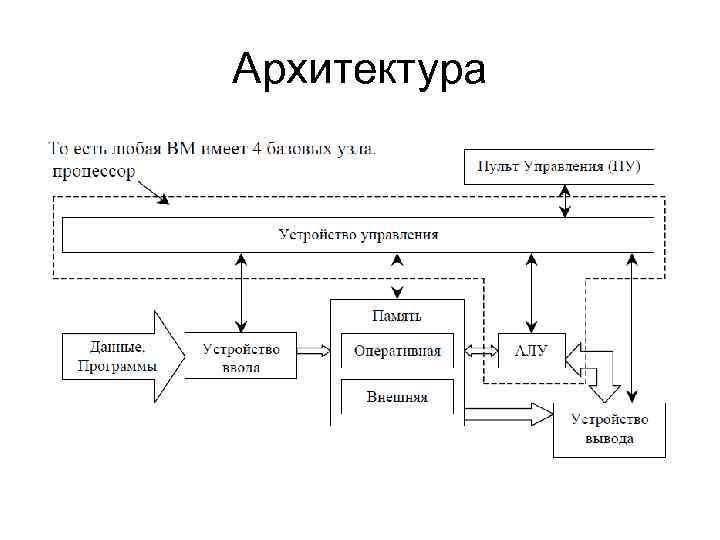

Архитектура

По уровню специализации ЭВМ выделяют: • универсальные (общего назначения) ЭВМ; • проблемно-ориентированные ЭВМ; • специализированные ЭВМ.

Универсальные ЭВМ • предназначены для решения самых разных инженерно-технических задач, отличающихся сложностью алгоритмов и большим объемом обрабатываемых данных.

Проблемно-ориентированные ЭВМ • предназначены для решения более узкого круга задач, связанных с регистрацией, накоплением и обработкой небольших объемов данных.

Специализированные ЭВМ • используются для решения узкого круга задач (микропроцессоры и контроллеры, выполняющие функции управления техническими устройствами).

Персональные компьютеры (ПК) являются наиболее массовыми и широко используемыми ЭВМ. Несмотря на свои небольшие размеры, они вобрали в себя все черты ЭВМ и полностью отражают ее архитектуру и принципы построения. В дальнейшем при рассмотрении аппаратных и программных средств будем вести речь только о персональных компьютерах.

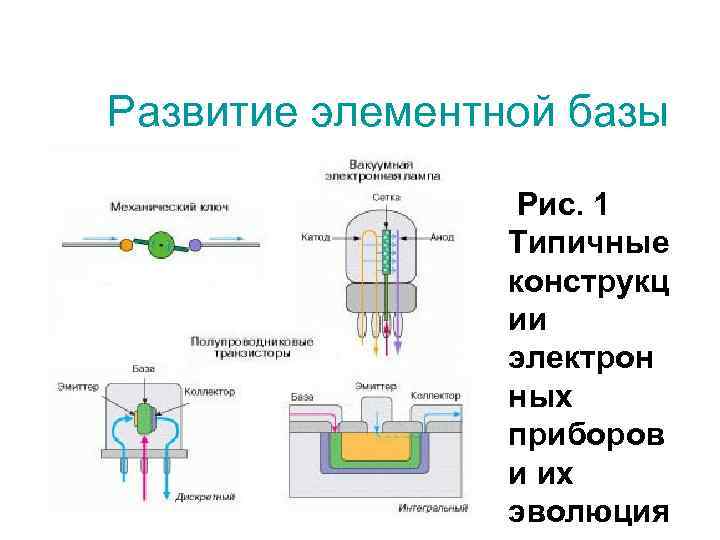

Развитие элементной базы Рис. 1 Типичные конструкц ии электрон ных приборов и их эволюция

Развитие элементной базы начиная с 50 -ых: исторический экскурс Простейшим из приборов является механический ключ. Первым электронным ключом был вакуумный диод, запатентованный в 1904 году англичанином Д. А. Флемингом. Затем был вакуумный триод (1906 год, Л. Де Форест и Р. Либен) и полупроводниковый транзистор (1947 год, У. Браттейн, Дж. Бардин, У. Шокли), а затем интегральные микросхемы на

Прогнозы развития элементной базы Развитие компьютерной техники происходит в геометрической прогрессии. Каждые полтора года производительность компьютеров увеличивается в 2 раза. Предсказывают, что известный эмпирический закон Мура - удвоение элементов на кристалле каждые 18 месяцев, будет действовать и до конца десятилетия. Поэтому только наноэлектроника может обеспечить

Проблемы и поиск путей их решения. Однако прежде чем начать массовое производство, необходимо разработать литографию в глубокой ультрафиолетовой области. Кроме того, необходимо решить проблемы утечки электронов на межсоединениях и чрезмерного теплоотделения. Поэтому

Направления построения новой элементной базы • Усовершенствование традиционной элементной базы. • Микросенсорика: микромеханические электронные устройства. • Опто- и спин-электроника на наногетеростуктурах. • Электроника на квантовых точках и проволоках. • Электроника на нанотрубках. • Электроника, использующая атомное манипулирование.

Организация эвм Структура дисциплины, Понятие вычислительной машины, принципы ф. Неймана

Вычислительная машина • Процессор (АЛУ, УУ) • Память • Устройства вывода и ввода информации • Связи между устройстами

Машинное слово и память • • Разрядность ЭВМ Адресация памяти Представление информации в памяти Система счисления ЭВМ

Регистры ЭВМ • • Универсальные Общего назначения Служебные Управляющие Указательные Счетные Сдвиговые

Команды ЭВМ • Адресность • Последовательность выполнения

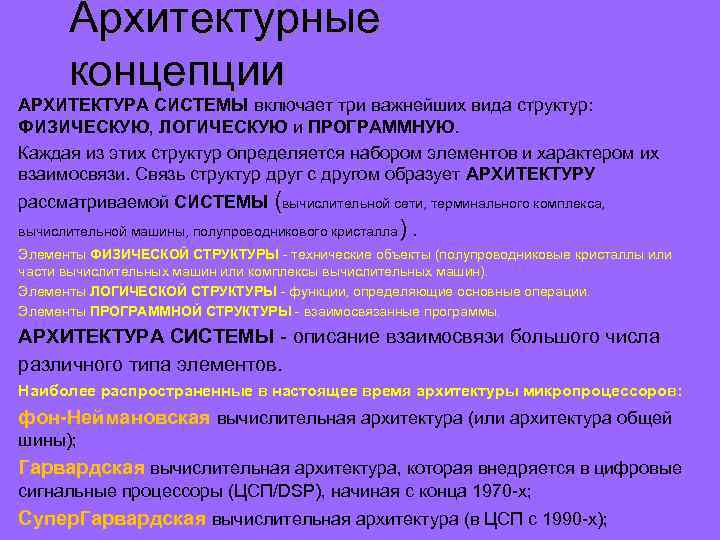

Архитектурные концепции АРХИТЕКТУРА СИСТЕМЫ включает три важнейших вида структур: ФИЗИЧЕСКУЮ, ЛОГИЧЕСКУЮ и ПРОГРАММНУЮ. Каждая из этих структур определяется набором элементов и характером их взаимосвязи. Связь структур друг с другом образует АРХИТЕКТУРУ рассматриваемой СИСТЕМЫ (вычислительной сети, терминального комплекса, вычислительной машины, полупроводникового кристалла ). Элементы ФИЗИЧЕСКОЙ СТРУКТУРЫ - технические объекты (полупроводниковые кристаллы или части вычислительных машин или комплексы вычислительных машин). Элементы ЛОГИЧЕСКОЙ СТРУКТУРЫ - функции, определяющие основные операции. Элементы ПРОГРАММНОЙ СТРУКТУРЫ - взаимосвязанные программы. АРХИТЕКТУРА СИСТЕМЫ - описание взаимосвязи большого числа различного типа элементов. Наиболее распространенные в настоящее время архитектуры микропроцессоров: фон-Неймановская вычислительная архитектура (или архитектура общей шины); Гарвардская вычислительная архитектура, которая внедряется в цифровые сигнальные процессоры (ЦСП/DSP), начиная с конца 1970 -х; Супер. Гарвардская вычислительная архитектура (в ЦСП с 1990 -х);

• Фон-Неймановская архитектура Вычислительное устройство машины с архитектурой фон-Неймана выбирает сначала команду из памяти, затем данные, обрабатывает их, и полученный результат вновь передает в память. Машины фон-Неймана хранят программу и данные в одной и той же области памяти. В машинах этого типа команды содержат указание на то, что выполнить, и адреса данных, подлежащих обработке. Внутри этой машины имеются три основных функциональных блока. Арифметико-логическое устройство (АЛУ) выполняет самые важные операции: умножение, сложение, вычитание и многие другие. Другой блок – память, в которой хранятся команды и обрабатываемые данные. Третий блок - устройство ввода/вывода, которое управляет потоком внешних данных и команд. Эти блоки, реализованные в виде устройств, соединены между собой с помощью трех шин: управления (ШУ), данных (ШД) и адреса (ША).

Гарвардская архитектура Гарвардская машина, как и фон-Неймановская, имеет арифметико-логическое устройство и устройство ввода/вывода. Единственное отличие гарвардской архитектуры состоит в том, что память программ и память данных разделены, и они используют физически разделенные линии передачи. Это позволяет подобной машине пересылать команды и данные одновременно. Есть еще варианты этих архитектур: модифицированная Гарвардская архитектура и Супер. Гарвардская архитектура. Подавляющее большинство современных компьютеров

Связь между функциональной и логической структурой ЭВМ Существуют два взгляда на построение и функционирование ЭВМ: • взгляд пользователя (не интересуется технической реализацией ЭВМ и озабочен только получением некоторого набора функций и услуг, обеспечивающих эффективное решение его задач); • взгляд разработчика ЭВМ (озабочен технической реализацией необходимых пользователю функций). С учетом этого обстоятельства и вводятся понятия "функциональная и логическая

Связь между функциональной и логической структурой ЭВМ Функциональная структура ЭВМ – это реализуемые ей набор функций и услуг. При проектировании ЭВМ создается абстрактная модель, описывающая функциональные возможности машины и предоставляемые ею услуги. Предусматриваемые абстрактной моделью функции ЭВМ реализуются на основе реальных, физических средств (устройств, блоков, узлов, элементов), взаимодействующих между собой. Логическая структура ЭВМ - состав, порядок и принципы взаимодействия основных

Обобщенная структура ЭВМ Основной тенденцией в развитии структуры ЭВМ является разделение функций системы и максимальная специализация подсистем для выполнения этих функций. Обобщенная структура ЭВМ: o. Обрабатывающая подсистема; oподсистема памяти; oподсистема ввода-вывода; oподсистема управления и обслуживания

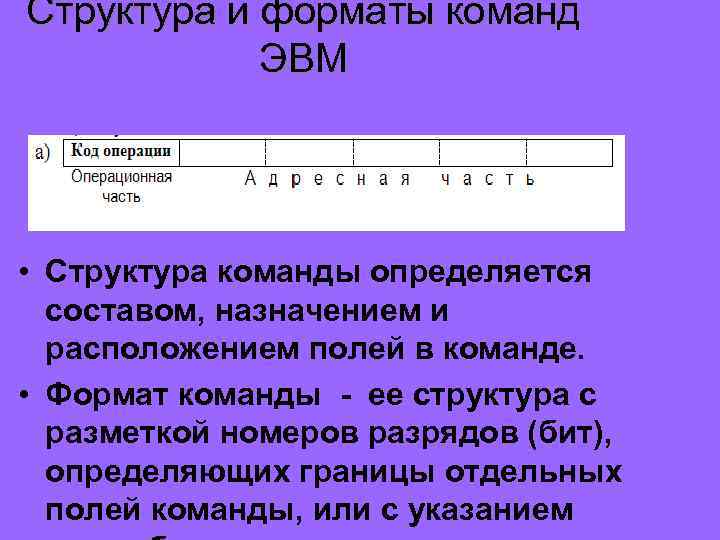

Структура и форматы команд ЭВМ • Структура команды определяется составом, назначением и расположением полей в команде. • Формат команды - ее структура с разметкой номеров разрядов (бит), определяющих границы отдельных полей команды, или с указанием

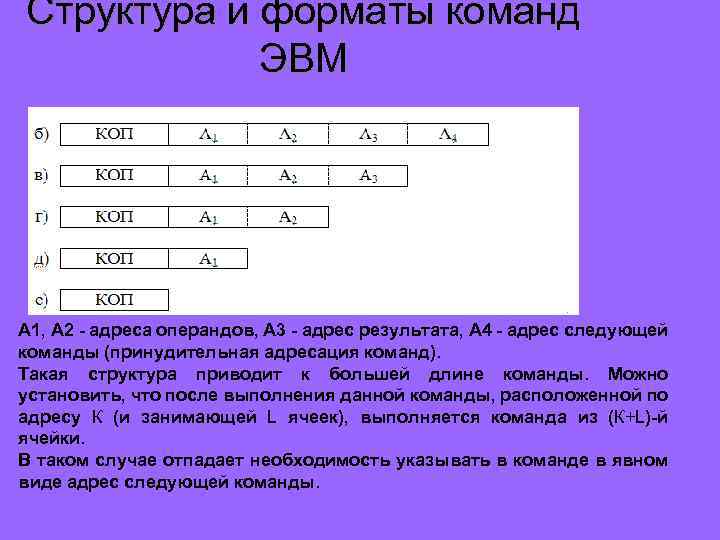

Структура и форматы команд ЭВМ А 1, А 2 - адреса операндов, А 3 - адрес результата, А 4 - адрес следующей команды (принудительная адресация команд). Такая структура приводит к большей длине команды. Можно установить, что после выполнения данной команды, расположенной по адресу К (и занимающей L ячеек), выполняется команда из (К+L)-й ячейки. В таком случае отпадает необходимость указывать в команде в явном виде адрес следующей команды.

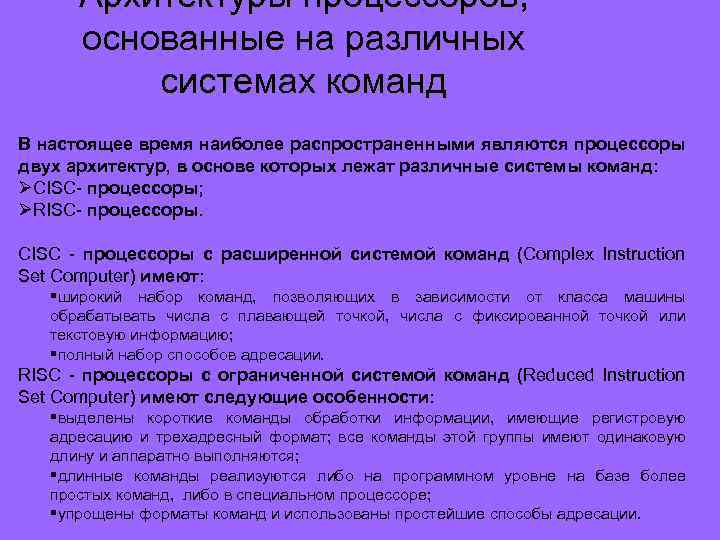

Архитектуры процессоров, основанные на различных системах команд В настоящее время наиболее распространенными являются процессоры двух архитектур, в основе которых лежат различные системы команд: ØCISC- процессоры; ØRISC- процессоры. CISC - процессоры с расширенной системой команд (Complex Instruction Set Computer) имеют: §широкий набор команд, позволяющих в зависимости от класса машины обрабатывать числа с плавающей точкой, числа с фиксированной точкой или текстовую информацию; §полный набор способов адресации. RISC - процессоры с ограниченной системой команд (Reduced Instruction Set Computer) имеют следующие особенности: §выделены короткие команды обработки информации, имеющие регистровую адресацию и трехадресный формат; все команды этой группы имеют одинаковую длину и аппаратно выполняются; §длинные команды реализуются либо на программном уровне на базе более простых команд, либо в специальном процессоре; §упрощены форматы команд и использованы простейшие способы адресации.

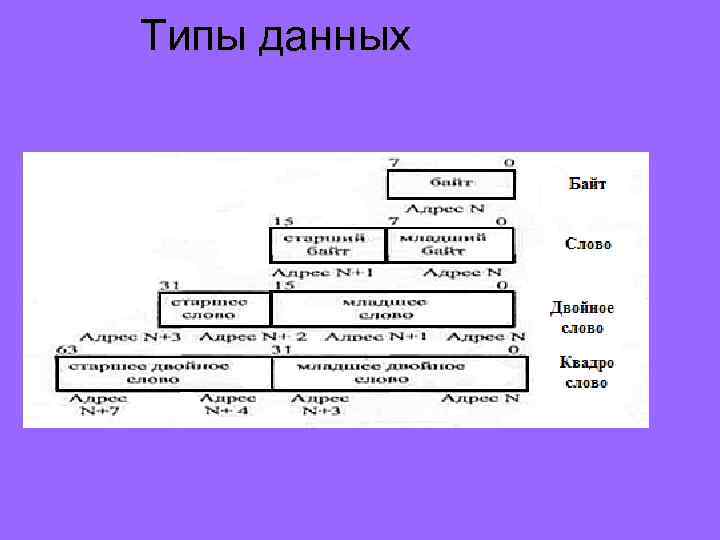

Типы данных

Принципы фон Неймана • Управляющая программа • Произвольный доступ к памяти • Однородность памяти

Машины с архитектурой фон Неймана • • Мэйнфреймы мини. ЭВМ PC RISC Cray SGI Sun …. .

Гарвардская архитектура • Различные адресные пространства • Немодифицируемость кода • Возможно различная реализация памяти команд и памяти данных

Машины с гарвардской архитектурой • Управляющие ЭВМ (станки) • Встроенные в оборудование ЭВМ (контроллеры) • Специализированные ЭВМ (расчетные) • Универсальные ЭВМ (исторические Проминь, Наири, Мир)

Управляющая программа • Из памяти выбираются по очереди команды и выполняются, пока не встретится команда, изменяющая этот порядок обработки

Произвольный доступ к памяти • Память состоит из ячеек • Каждая ячейка имеет свой адрес • Адреса ячеек последовательно возрастают • Время доступа к ячейке памяти не зависит от ее адреса

Однородность памяти • Команды и обрабатываемые данные находятся в одной и той же физической памяти и доступны для обработки • Команды могут обрабатываться как данные

Контроллер гибких дисков Шины: управляющая , адресная , данных Сканер Параллельные порты Принтер Последовательные порты Плоттер Порты ввода/ вывода Модем Дополнительные устройства Схемы Внутреннего управления Мышь Кэш-память Клавиатура Регистры Видеоадаптер Накопитель на гибких магнитных дисках Контроллер накопителя на жёстких магнитных дисках Динамик АЛУ Внутренняя память Схемы управления шиной Микропроцессор Накопитель на жёстких магнитных дисках Дополнительные слоты расширения Rom. Ram Монитор Блок питания Структурная схема микропроцессорной системы Игровой порт Джойстик

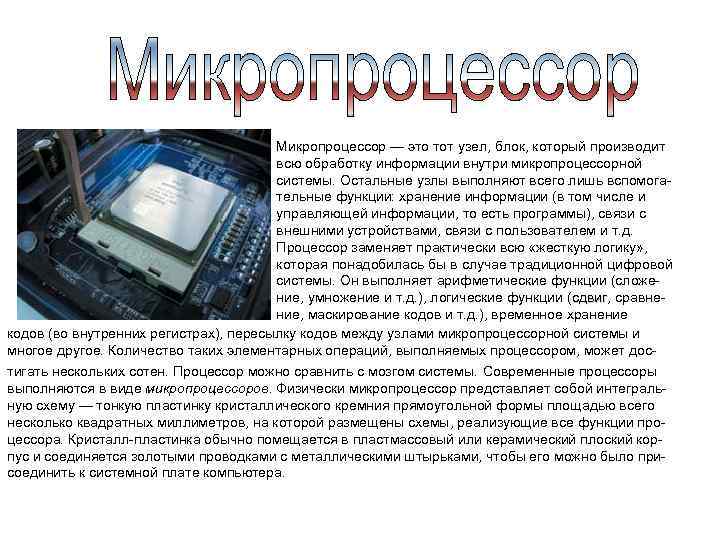

Микропроцессор — это тот узел, блок, который производит всю обработку информации внутри микропроцессорной системы. Остальные узлы выполняют всего лишь вспомогательные функции: хранение информации (в том числе и управляющей информации, то есть программы), связи с внешними устройствами, связи с пользователем и т. д. Процессор заменяет практически всю «жесткую логику» , которая понадобилась бы в случае традиционной цифровой системы. Он выполняет арифметические функции (сложение, умножение и т. д. ), логические функции (сдвиг, сравнесдвиг ние, маскирование кодов и т. д. ), временное хранение кодов (во внутренних регистрах), пересылку кодов между узлами микропроцессорной системы и многое другое. Количество таких элементарных операций, выполняемых процессором, может достигать нескольких сотен. Процессор можно сравнить с мозгом системы. Современные процессоры выполняются в виде микропроцессоров. Физически микропроцессор представляет собой интегральную схему — тонкую пластинку кристаллического кремния прямоугольной формы площадью всего несколько квадратных миллиметров, на которой размещены схемы, реализующие все функции процессора. Кристалл-пластинка обычно помещается в пластмассовый или керамический плоский корпус и соединяется золотыми проводками с металлическими штырьками, чтобы его можно было присоединить к системной плате компьютера.

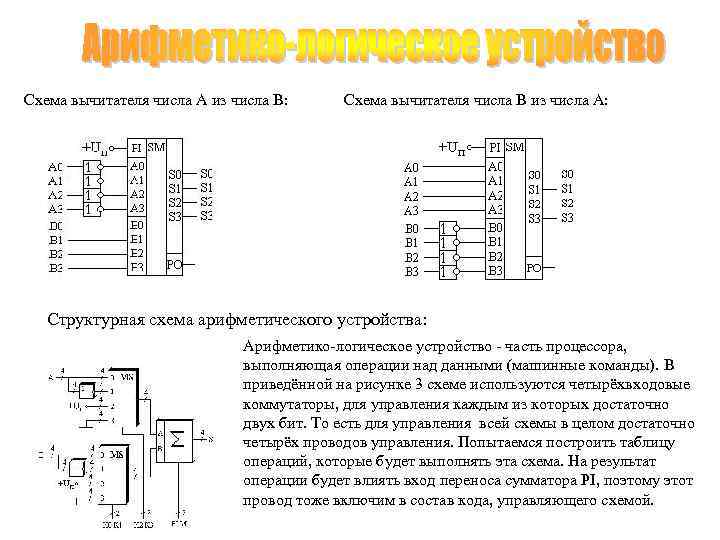

Схема вычитателя числа A из числа B: Схема вычитателя числа B из числа A: Структурная схема арифметического устройства: Арифметико-логическое устройство - часть процессора, выполняющая операции над данными (машинные команды). В приведённой на рисунке 3 схеме используются четырёхвходовые коммутаторы, для управления каждым из которых достаточно двух бит. То есть для управления всей схемы в целом достаточно четырёх проводов управления. Попытаемся построить таблицу операций, которые будет выполнять эта схема. На результат операции будет влиять вход переноса сумматора PI, поэтому этот провод тоже включим в состав кода, управляющего схемой.

Регистры процессора Процессоры имеют регистры, подразделяющиеся на следующие категории: -регистры общего назначения; -указатель инструкций и регистр флагов; -регистры сегментов; -управляющие регистры; -системные адресные регистры; -регистры отладки; -регистры тестирования.

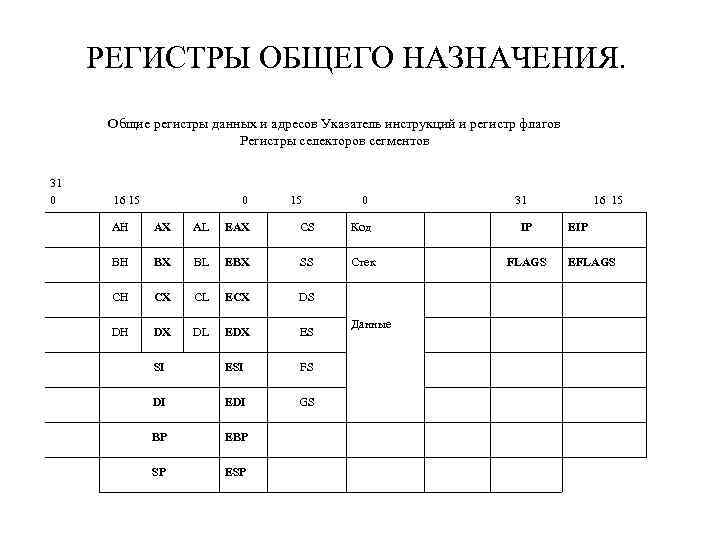

РЕГИСТРЫ ОБЩЕГО НАЗНАЧЕНИЯ. Общие регистры данных и адресов Указатель инструкций и регистр флагов Регистры селекторов сегментов 31 0 16 15 0 15 0 31 16 15 AH AX AL EAX CS Код IP BH BX BL EBX SS Стек FLAGS CH CX CL ECX DS DH DX DL EDX ES Данные EIP EFLAGS SI ESI FS DI EDI GS BP EBP SP ESP

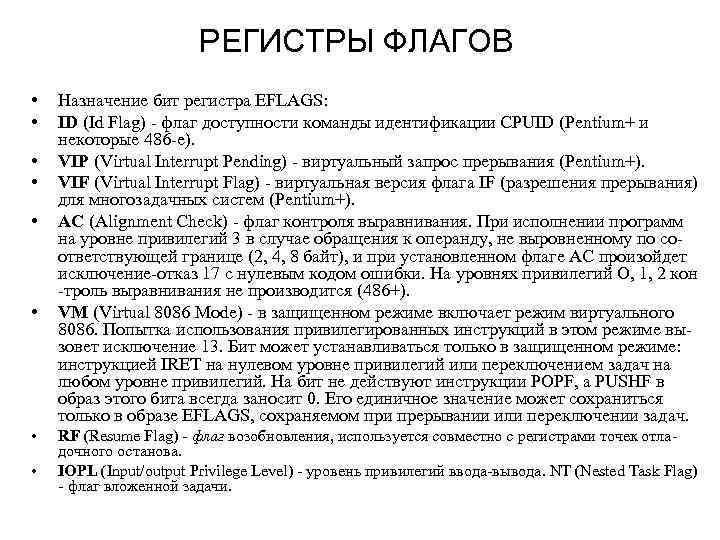

РЕГИСТРЫ ФЛАГОВ • • Назначение бит регистра EFLAGS: ID (Id Flag) - флаг доступности команды идентификации CPUID (Pentium+ и некоторые 486 -е). VIP (Virtual Interrupt Pending) - виртуальный запрос прерывания (Pentium+). VIF (Virtual Interrupt Flag) - виртуальная версия флага IF (разрешения прерывания) для многозадачных систем (Pentium+). AC (Alignment Check) - флаг контроля выравнивания. При исполнении программ на уровне привилегий 3 в случае обращения к операнду, не выровненному по соответствующей границе (2, 4, 8 байт), и при установленном флаге АС произойдет исключение-отказ 17 с нулевым кодом ошибки. На уровнях привилегий О, 1, 2 кон -троль выравнивания не производится (486+). VM (Virtual 8086 Mode) - в защищенном режиме включает режим виртуального 8086. Попытка использования привилегированных инструкций в этом режиме вызовет исключение 13. Бит может устанавливаться только в защищенном режиме: инструкцией IRET на нулевом уровне привилегий или переключением задач на любом уровне привилегий. На бит не действуют инструкции POPF, a PUSHF в образ этого бита всегда заносит 0. Его единичное значение может сохраниться только в образе EFLAGS, сохраняемом при прерывании или переключении задач. RF (Resume Flag) - флаг возобновления, используется совместно с регистрами точек отладочного останова. IOPL (Input/output Privilege Level) - уровень привилегий ввода-вывода. NT (Nested Task Flag) - флаг вложенной задачи.

• • OF (Overflow Flag) - флаг переполнения. Устанавливается, если результат арифметической операции не умещается в операнде назначения. DF (Direction Flag) - флаг управления направлением в строковых операциях. При единичном значении индексные регистры, участвующие в строковых операциях, автоматически декрементируются на количество байт операнда, при нулевом - инкрементируются. IF (Interrupt-enable Flag) - (флаг управления прерываниями. При единичном значении разрешается выполнение маскируемых аппаратных прерываний. TF (Trap Flag) - флаг трассировки (пошагового режима). При его установке после выполнения каждой команды вызывается внутреннее прерывание типа 1 (INT 1). SF (Sign Flag) - флаг знака. Указывает на единичное значение старшего бита результата - признак отрицательного числа. ZF (Zero Flag) - флаг нулевого результата, AF (Auxiliary Flag) - флаг дополнительного переноса (займа) в тетраде для десятичной арифметики. PF (Parity Flag) - флаг паритета, устанавливается при четном числе единиц в результате. CF (Carry Flag) - флаг переноса (заема) старшего бита в арифметических операциях.

РЕГИСТРЫ СЕГМЕНТОВ Содержат 16 -битные указатели (в реальном режиме) или дескрипторы (в защищенном режиме) сегментов CS (Code Segment - сегмент кодов ко-манд); SS (Stack Segment - сегмент стека); DS (Data Segment); ES, FS и GS - дополнительные сегменты. Использование сегментных регистров опре-деляется типом обращения к памяти. Для многих типов обращений возмо-жно применение альтернативных сегментных регистров, которое вводится префиксами команд CS: , SS: , DS: , ES: FS: или GS: (табл. 3. 4). Размер сег-мента - лимит - в реальном режиме фиксирован - 64 Кб, в защищенном мо-жет задаваться в пределах 1 байт - 4 Гб. С каждым из шести сегментных регистров связаны программно-недоступные регистры дескрипторов, автоматически загружаемые при загрузке соответствующих сегментных регистров. В защищенном режиме в регистры дескрипторов загружается 32 -битный базовый адрес, 32 -битный лимит и атрибуты сегментов. В реальном режиме лимит фиксирован, атрибуты не используются, а в качестве базового адреса заносится сдвинутое на 4 бита влево значение сегментного регистра.

УПРАВЛЯЮЩИЕ РЕГИСТРЫ • • CRO, CR 1, CR 2, CR 3 хранят признаки состояния процессора, общие для всех задач. Регистр CRO включает в себя биты регистра MSW процессора 80286. Для обеспечения программной совместимости команды LMSW и SMSW затрагивают только эти младшие 4 бита. Назначение бит регистра CRO: РЕ (Protection Enable) - разрешение защиты. Установка этого флага инструкцией LMSW или LOAD CRO переводит процессор в защищенный режим, возврат в реальный режим (сброс флага) возможен только по инструкции LOAD CRO. Сброс бита РЕ является частью довольно длинной последовательности инструкций, подготавливающих корректное переключение в реальный режим. МР (Monitor Processor Extension) - мониторинг сопроцессора, позволяет вызывать исключение 7 по каждой команде WAIT при TS=1. При исполнении программ для 286/287 и 386/387 на процессорах 486 DX и старте бит МР должен быть установлен. ЕМ (Processor Extension Emulated) - эмуляция сопроцессора. Установка этого флага вызывает появление исключения 7 при каждой команде, относящейся к сопроцессору, что позволяет прозрачно осуществлять его программную эмуляцию. TS (Task Switch) - переключение задач. При установке этого флага следующая команда, относящаяся к сопроцессору, вызовет исключение 7, что позволяет программно определить, относится ли контекст сопроцессора к текущей задаче. Бит сбрасывается инструкцией CLTS. Сочетание МР=0 ЕМ=0 TS=0, устанавливаемое по аппаратному сбросу, обеспечивает полную совместимость с 8086/88 (исключение 7 не вырабатывается). Сочетание МР=1, ЕМ=0 используется при наличии сопроцессора, а МР=0, ЕМ==1 при его программной эмуляции.

• • • • • ЕТ (Extension Type) - индикатор поддержки инструкций математического сопроцессора. Используется в процессорах 486+; для 486 SX ЕТ=0; для остальных процессоров ЕТ=1. NE (Numeric Error) - разрешение стандартного (для Intel, но не для PC) механизма сообщения об ошибке FPU через генерацию исключения (486+). При NE=0 и активном сигнале IGNNE# ошибки FPU игнорируются. При NE=0 и пассивном сигнале IGNNE# при возникновении ошибки FPU процессор останавливается и ждет прерывания, вводимого внешней логикой по сигналу на выходе FERR#. Таким образом эмулируется обработка ошибок FPU, принятая в PC со времен сопроцессоров 80287 и 80387. WP (Write Protect) - разрешение защиты от записи на уровне привилегий супервизора в страницы только для чтения. AM (Alignment Mask) - разрешение контроля выравнивания (контроль выравнивания выполняется только на уровне привилегий 3 при АМ=1 и флаге АС-1). NW (Not Writethrough) - запрет сквозной записи кэша и циклов аннулирования. CD (Cache Disable) - запрет заполнения кэша (кэш-попадания в ранее заполненные строки при этом не запрещаются). PG (Paging Enanable) - включение механизма страничной переадресации памяти. Регистр CR 1 не используется. Регистр CR 2 (Page Fault Linear Address) хранит 32 -битный линейный адрес, по которому был получен последний отказ страницы памяти. Регистр CR 3 (Page Directory Base Register) в старших 20 битах хранит физический базовый адрес таблицы каталога страниц. Из младших 12 бит используются следующие: PCD (Page-Level Cache Disable) - запрет кэширования страницы (один из источников сигнала PCD для управления внешним кэшем), 486+. PWT (Page-Level Writes Transparent) - кэширования страницы со сквозной записью (один из источников сигнала PWT для управления внешним кэшем), 486+. Регистр CR 4 (присутствует в процессорах Pentium и старше) содержит биты разрешения архитектурных расширений. VME (Virtual-8086 Mode Extensions) - разрешение использования виртуального флага прерываний в режиме V 86, что позволяет повысить производительность за счет сокращения излишних вызовов монитора виртуальных машин. PVI (Protected-Mode Virtual Interrupts) - разрешение использования виртуального флага прерываний в защищенном режиме. TSD (Time Stamp Disable) - превращение инструкции RDTSC (read from time stamp counter) в привилегированную. DE (Debugging Extensions) - разрешение точек останова по обращению к портам ввода-вывода.

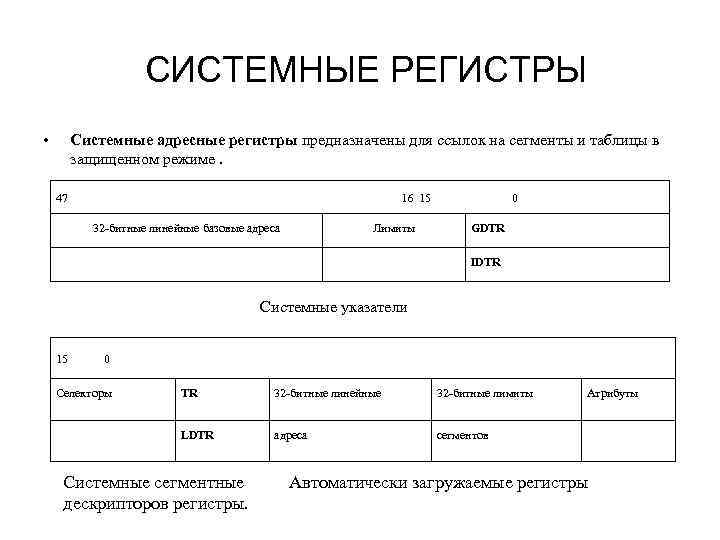

СИСТЕМНЫЕ РЕГИСТРЫ • Системные адресные регистры предназначены для ссылок на сегменты и таблицы в защищенном режиме. 47 16 15 0 32 -битные линейные базовые адреса Лимиты GDTR IDTR Системные указатели 15 0 Селекторы TR 32 -битные линейные 32 -битные лимиты Атрибуты LDTR адреса сегментов Системные сегментные Автоматически загружаемые регистры дескрипторов регистры.

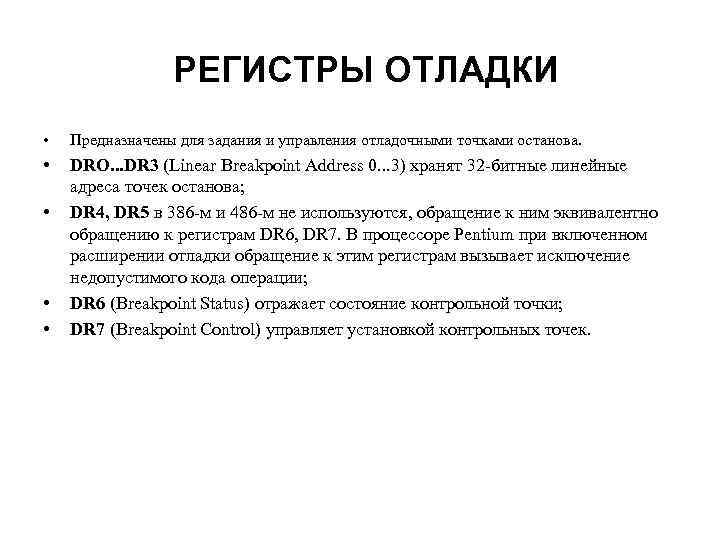

РЕГИСТРЫ ОТЛАДКИ • Предназначены для задания и управления отладочными точками останова. • DRO. . . DR 3 (Linear Breakpoint Address 0. . . 3) хранят 32 -битные линейные адреса точек останова; DR 4, DR 5 в 386 -м и 486 -м не используются, обращение к ним эквивалентно обращению к регистрам DR 6, DR 7. В процессоре Pentium при включенном расширении отладки обращение к этим регистрам вызывает исключение недопустимого кода операции; DR 6 (Breakpoint Status) отражает состояние контрольной точки; DR 7 (Breakpoint Control) управляет установкой контрольных точек. • • •

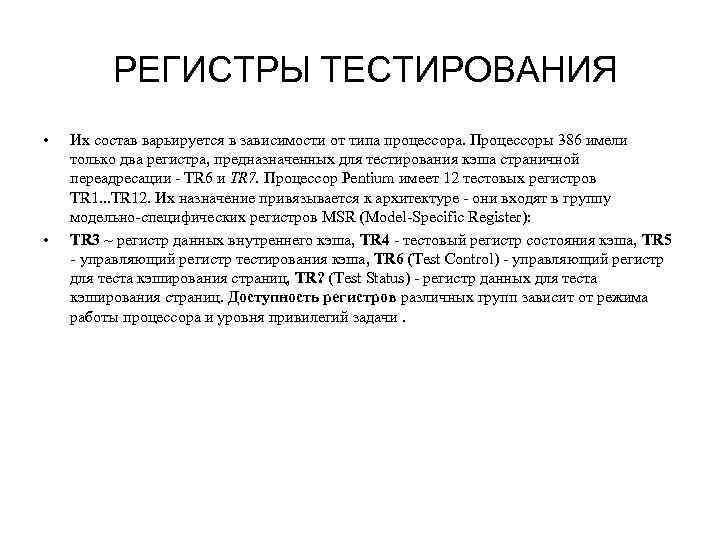

РЕГИСТРЫ ТЕСТИРОВАНИЯ • • Их состав варьируется в зависимости от типа процессора. Процессоры 386 имели только два регистра, предназначенных для тестирования кэша страничной переадресации - TR 6 и TR 7. Процессор Pentium имеет 12 тестовых регистров TR 1. . . TR 12. Их назначение привязывается к архитектуре - они входят в группу модельно-специфических регистров MSR (Model-Specific Register): TR 3 ~ регистр данных внутреннего кэша, TR 4 - тестовый регистр состояния кэша, TR 5 - управляющий регистр тестирования кэша, TR 6 (Test Control) - управляющий регистр для теста кэширования страниц, TR? (Test Status) - регистр данных для теста кэширования страниц. Доступность регистров различных групп зависит от режима работы процессора и уровня привилегий задачи.

Схема внутреннего управления

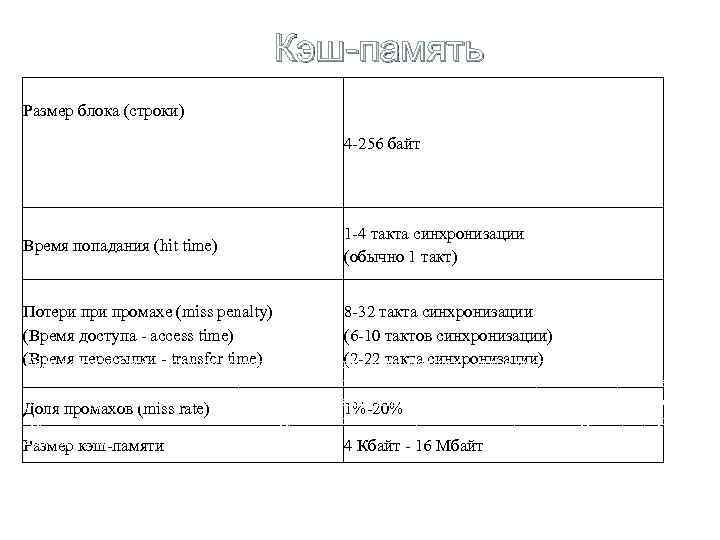

Кэш-память Типовые значения ключевых параметров для кэш-памяти : Размер блока (строки) ения ключевых параметров для кэш-памяти : Время попадания (hit time) 4 -256 байт 1 -4 такта синхронизации (обычно 1 такт) Потери промахе (miss penalty) 8 -32 такта синхронизации (Время доступа - access time) (6 -10 тактов синхронизации) (Время пересылки - transfer time) (2 -22 такта синхронизации) Если каждый блок основной памяти имеет только одно фиксированное место, на котором он может появиться в кэш-памяти, то такая кэш-память называется кэшем с прямым отображением (direct mapped). Это наиболее простая организация кэш-памяти, при которой для отображение Доля промахов (miss rate) 1%-20% адресов блоков основной памяти на адреса кэш-памяти просто используются младшие разряды адреса блока. Размер кэш-памяти 4 Кбайт - 16 Мбайт Если некоторый блок основной памяти может располагаться на любом месте кэш-памяти, то кэш называется полностью ассоциативным (fully associative).

Если некоторый блок основной памяти может располагаться на ограниченном множестве мест в кэш-памяти, то кэш называется множественно-ассоциативным (set associative). Обычно множество представляет собой группу из двух или большего числа блоков в кэше. Если множество состоит из n блоков, то такое размещение называется множественно-ассоциативным с n каналами (n-way set associative). У каждого блока в кэш-памяти имеется адресный тег, указывающий, какой блок в основной памяти данный блок кэш-памяти представляет. Эти теги обычно одновременно сравниваются с выработанным процессором адресом блока памяти. Когда выполняется запись в кэш-память имеются две базовые возможности: сквозная запись (write through, store through) - информация записывается в два места: в блок кэшпамяти и в блок более низкого уровня памяти. запись с обратным копированием (write back, copy back, store in) - информация записывается только в блок кэш-памяти. Модифицированный блок кэш-памяти записывается в основную память только когда он замещается. Для сокращения частоты копирования блоков при замещении обычно с каждым блоком кэш-памяти связывается так называемый бит модификации (dirty bit). Этот бит состояния показывает был ли модифицирован блок, находящийся в кэш-памяти. Если он не модифицировался, то обратное копирование отменяется, поскольку более низкий уровень содержит ту же самую информацию, что и кэш-память. При возникновении промаха, контроллер кэш-памяти должен выбрать подлежащий замещению блок. Как правило для замещения блоков применяются две основных стратегии: случайная и LRU. В первом случае, чтобы иметь равномерное распределение, блоки-кандидаты выбираются случайно. В некоторых системах, чтобы получить воспроизводимое поведение, которое особенно полезно во время отладки аппаратуры, используют псевдослучайный алгоритм замещения. Во втором случае, чтобы уменьшить вероятность выбрасывания информации, которая скоро может потребоваться, все обращения к блокам фиксируются. Заменяется тот блок, который не использовался дольше всех (LRU - Least-Recently Used).

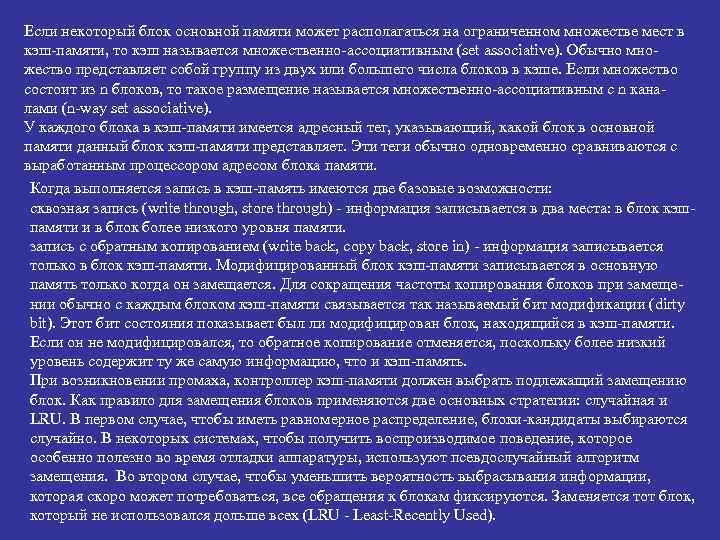

ШИНЫ Интерфейс — это средство сопряжения двух устройств, в котором все физические и логические параметры согласуются между собой. Если интерфейс является общепринятым, например, утверждённым на уровне международных соглашений, то он называется стандартным. Каждый из функциональных элементов (память, монитор или другое устройство) связан с шиной определённого типа — адресной, управляющей или шиной данных. Для согласования интерфейсов периферийные устройства подключаются к шине не напрямую, а через свои контроллеры (адаптеры) и порты примерно по такой схеме: Контроллеры и адаптеры представляют собой наборы электронных цепей, которыми снабжаются устройства компьютера с целью совместимости их интерфейсов. Контроллеры, кроме этого, осуществляют непосредственное управление периферийными устройствами по запросам микропроцессора, т. е. Контроллер это устройство, которое связывает периферийное оборудование или каналы связи с центральным процессором, освобождая процессор от непосредственного управления функционированием данного оборудования. Порты устройств представляют собой некие электронные схемы, содержащие один или несколько регистров ввода-вывода и позволяющие подключать периферийные устройства компьютера к внешним шинам микропроцессора. Портами также называют устройства стандартного интерфейса: последовательный, параллельный и игровой порты (или интерфейсы). Последовательный порт обменивается данными с процессором побайтно, а с внешними устройствами — побитно. Параллельный порт получает и посылает данные побайтно.

Шинные интерфейсы: ISA - Industry Standard Architecture. Позволила связать все устройства системного блока между собой, обеспечила простое подключение новых устройств через стандартные разъемы (слоты). Пропускная способность низкая, но эта шина продолжает использоваться в компьютерах для подключения сравнительно "медленных" внешних устройств, напр. звуковых карт и модемов. PCI -Peripheral Component Interconnect - стандарт подключения внешних компонентов - был введен в ПК, выполненных на базе процессоров Intel Pentium. Интерфейс локальной шины, связывающей процессор с ОП, в которую врезаны разъемы для подключения внешних устройств. Поддерживает режим plug-and-play, в результате которого устройство автоматически получает номер используемого прерывания, адрес порта подключения и номер канала прямого доступа к памяти. FSB. Шина PCI сегодня используется только как шина для подключения ВУ, а для связи процессора и памяти, начиная с процессора Intel Pentium Pro, используется специальная шина, получившая название Front Side Bus. Эта шина работает на очень высокой частоте 100 -125 МГц. В настоящее время внедряются материнские платы с частотой шины 133 МГц и выше. Пропускная способность шины при частоте 100 МГц составляет порядка 800 Мбайт/с. AGP. Видеоадаптер - устройство, требующее особенно высокой скорости передачи данных. Видеоадаптер всегда был первым устройством, врезаемым в новую шину. Для них разработана отдельная шина, получившая название AGP( Advanced Graphic Port - усовершенствованный графический порт). Частота этой шины соответствует частоте шины PCI(33 МГц или 66 МГц), но она имеет более высокую пропускную способность. USB (Universal Serial Bus -универсальная последовательная магистраль). Этот стандарт определяет способ взаимодействия компьютера с периферийным оборудованием. Он позволяет подключать до 256 различных устройств, имеющих последовательный интерфейс. Производительность шины относительно невелика, но для таких устройств, как клавиатура, мышь, модем, джойстик и т. п. , этого достаточно. Она практически исключает конфликты между различным оборудованием, позволяет подключать и отключать устройства в "горячем режиме" (не выключая компьютер) и позволяет объединять несколько компьютеров в простейшую локальную сеть без применения специального оборудования и программного обеспечения.

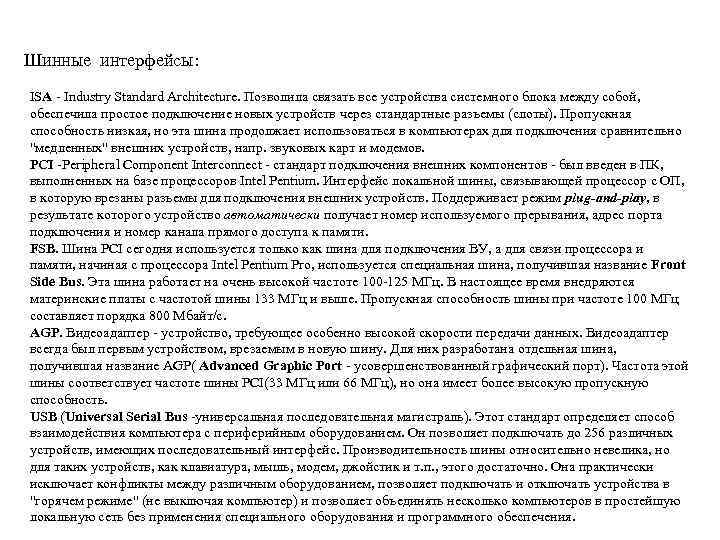

Чипсет: Чипсет (chipset) — это базовый набор микросхем, определяющий архитектуру взаимодействия всех основных подсистем компьютера. Фактически все функциональные возможности материнской платы определяются установленным на ней чипсетом. Выбор чипсетов на сегодняшний день еще более разнообразен, чем выбор процессоров. Чипсеты выпускают такие компании, как AMD, Intel, VIA, Si. S, Intel, n. VIDIA и ATi. Чипсет материнской платы определяет поддерживаемый тип процессора, тип памяти, а также функциональные возможности по подключению периферийных устройств. От чипсета в немалой степени зависит и производи-тельность материнской платы. Большинство чипсетов выпускаются на базе двух микросхем, называемых "Северный мост" и "Южный мост". "Северный мост" управляет взаимосвязью четырех устройств: процессора, оперативной памяти, порта AGP и шины PCI. "Южный мост" выполняет функции контроллера жестких и гибких дисков, функции моста PCIISA, контроллера клавиатуры, мыши, шины USB. Северный мост с кулером: Южный мост:

ВНУТРЕННЯЯ ПАМЯТЬ Под внутренней памятью современного компьютера принято понимать быстродействую-щую электронную память, расположенную на его системной плате. Сейчас такая память изготавливается на базе самых современных полупроводниковых технологий (раньше использовались магнитные устройства на основе ферритовых сердечников – лишнее свиде-тельство тому, что конкретная физические принципы значения не имеют). Наиболее су-щественная часть внутренней памяти называется ОЗУ - оперативное запоминающее устройство. Его главное назначение состоит в том, чтобы хранить данные и программы для решаемых в текущий момент задач. Наверное, каждому пользователю известно, что при выключении питания содержимое ОЗУ полностью теряется. В состав внутренней памяти современного компьютера помимо ОЗУ также входят и некоторые другие разновидности памяти, которые при первом знакомстве можно пропустить. Здесь упомянем только о постоянном запоминающем устройстве (ПЗУ), в котором в частности хранится инфор-мация, необходимая для первоначальной загрузки компьютера в момент включения пита-ния. Как очевидно из названия, информация в ПЗУ не зависит от состояния компью-тера (для лучшего понимания можно указать на некоторую аналогию между информацией в ПЗУ и “врожденными” безусловными рефлексами у живых существ). Раньше содержимое ПЗУ раз и навсегда формировалось на заводе, теперь же современные технологии позволяют в случае необходимости обновлять его даже не извлекая из компьютерной платы.

ВНУТРЕННЯЯ ПАМЯТЬ: ROM К устройствам специальной памяти относятся постоянная память (ROM), перепрограммируемая постоянная память (Flash Memory), память CMOS RAM, питаемая от батарейки, видеопамять и некоторые другие виды памяти. Постоянная память (ПЗУ, англ. ROM, Read Only Memory — память только для чтения) — энергонезависимая память, используется для хранения данных, которые никогда не потребуют изменения. Содержание памяти специальным образом “зашивается” в устройстве при его изготовлении для постоянного хранения. Перепрограммируемая постоянная память (Flash Memory) — энергонезависимая память, допускающая многократную перезапись своего содержимого. Важнейшая микросхема постоянной или Flash-памяти — модуль BIOS. Функции: проверка работоспособности системы управления электропитанием; инициализация системных ресурсов и регистров чипсетов; тестирование оперативной памяти; подключение клавиатуры; тестирование портов; инициализация контроллеров, определение и подключение жестких дисков.

ВНУТРЕННЯЯ ПАМЯТЬ: RAM Оперативная память (ОЗУ, англ. RAM, Random Access Memory — память с произвольным доступом) — это быстрое запоминающее устройство, основанное на триггерах , непосредственно связанное с процессором и предназначенное для записи, считывания и хранения выполняемых программ и данных, обрабатываемых этими программами. Оперативная память используется только для временного хранения данных и программ, так как, когда машина выключается, все, что находилось в ОЗУ, пропадает. Дос -туп к элементам оперативной памяти прямой — это означает, что каждый байт памяти имеет свой индивидуальный адрес.

Система команд процессора

Система команд процессора включает в себя четыре основные группы команд: • • команды пересылки данных; арифметические команды; логические команды; команды переходов.

Команды пересылки данных Выполняют следующие функции: • загрузка (запись) содержимого во внутренние регистры процессора; • сохранение в памяти содержимого внутренних регистров процессора; • копирование содержимого из одной области памяти в другую; • запись в устройства ввода/вывода и чтение из устройств ввода/вывода.

Арифметические команды Рассматривают коды операндов как числовые двоичные или двоично-десятичные коды. Могут быть разделены на пять основных групп: • команды операций с фиксированной запятой (сложение, вычитание, умножение, деление); • команды операций с плавающей запятой (сложение, вычитание, умножение, деление); • команды очистки; • команды инкремента и декремента; • команда сравнения.

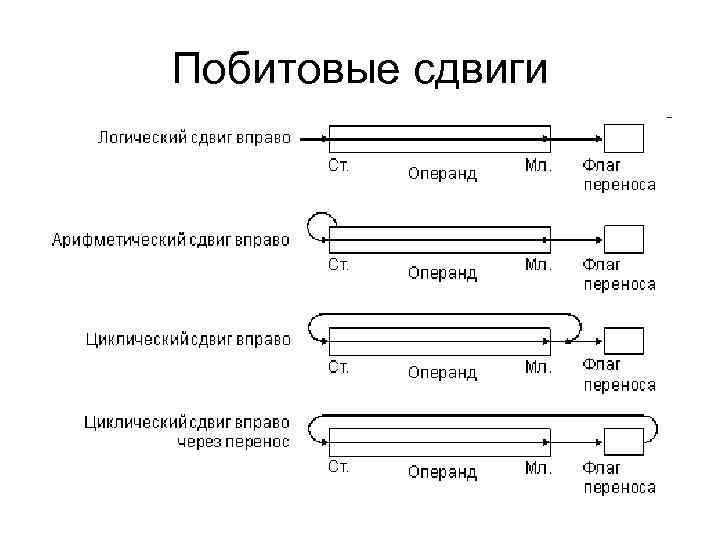

Логические команды Выполняют следующие основные операции: • логическое И, логическое ИЛИ, сложение по модулю 2 (Исключающее ИЛИ); • логические, арифметические и циклические сдвиги; • проверка битов и операндов; • установка и очистка битов (флагов) регистра состояния процессора (PSW).

Побитовые сдвиги

Команды переходов Делятся на две группы: • команды безусловных переходов; • команды условных переходов. Примеры команд условных переходов: • переход, если равно нулю; • переход, если не равно нулю; • переход, если есть переполнение; • переход, если нет переполнения; • переход, если больше нуля; • переход, если меньше или равно нулю.

Реализация ветвления на две ветки

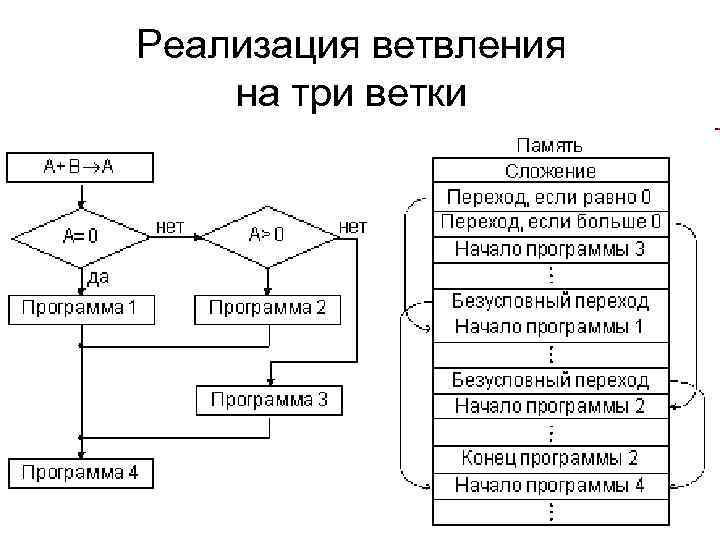

Реализация ветвления на три ветки

Вводная лекция ЭВМ.ppt