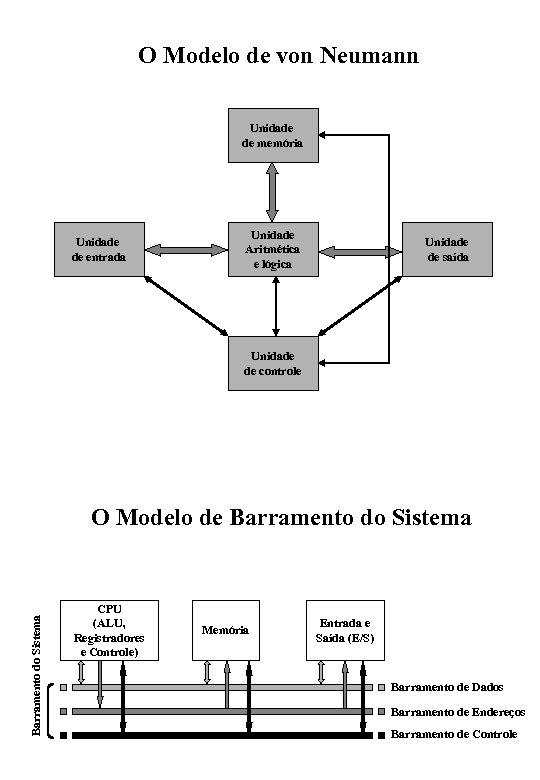

O Modelo de von Neumann Unidade de memória Unidade de entrada Unidade Aritmética e lógica Unidade de saída Unidade de controle Barramento do Sistema O Modelo de Barramento do Sistema CPU (ALU, Registradores e Controle) Memória Entrada e Saída (E/S) Barramento de Dados Barramento de Endereços Barramento de Controle

O Modelo de von Neumann Unidade de memória Unidade de entrada Unidade Aritmética e lógica Unidade de saída Unidade de controle Barramento do Sistema O Modelo de Barramento do Sistema CPU (ALU, Registradores e Controle) Memória Entrada e Saída (E/S) Barramento de Dados Barramento de Endereços Barramento de Controle

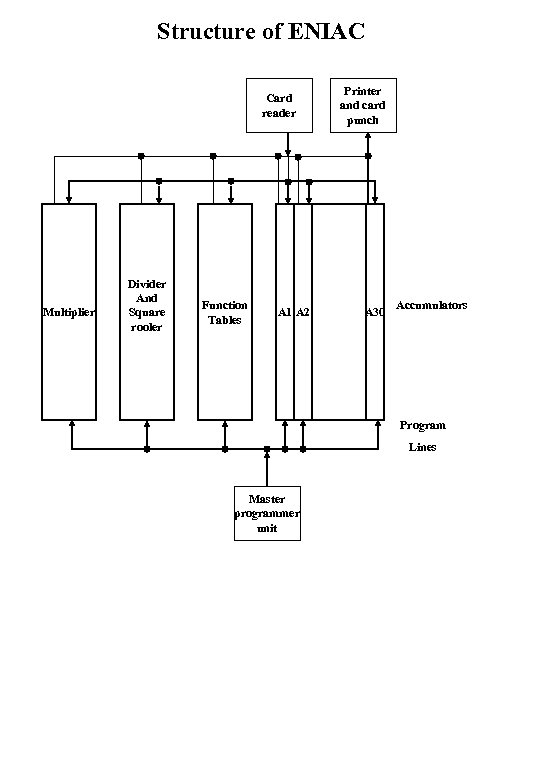

Structure of ENIAC Card reader Multiplier Divider And Square rooler Function Tables A 1 A 2 Printer and card punch A 30 Accumulators Program Lines Master programmer unit

Structure of ENIAC Card reader Multiplier Divider And Square rooler Function Tables A 1 A 2 Printer and card punch A 30 Accumulators Program Lines Master programmer unit

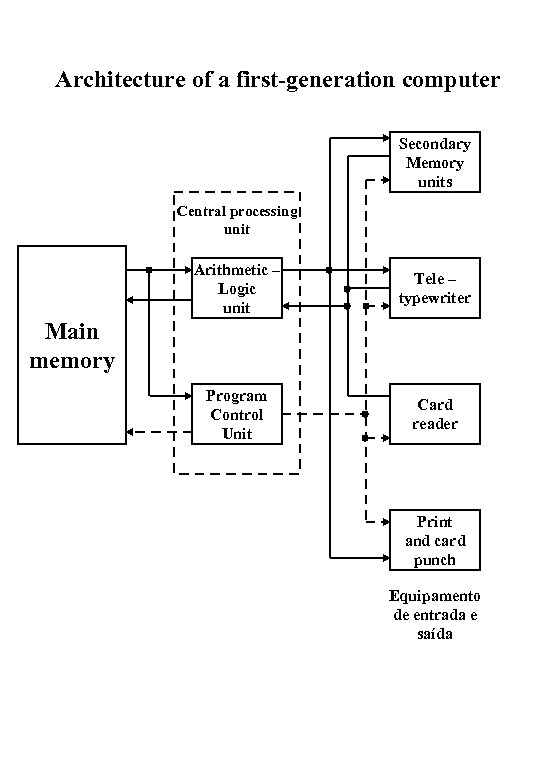

Architecture of a first-generation computer Secondary Memory units Central processing unit Arithmetic – Logic unit Tele – typewriter Program Control Unit Card reader Main memory Print and card punch Equipamento de entrada e saída

Architecture of a first-generation computer Secondary Memory units Central processing unit Arithmetic – Logic unit Tele – typewriter Program Control Unit Card reader Main memory Print and card punch Equipamento de entrada e saída

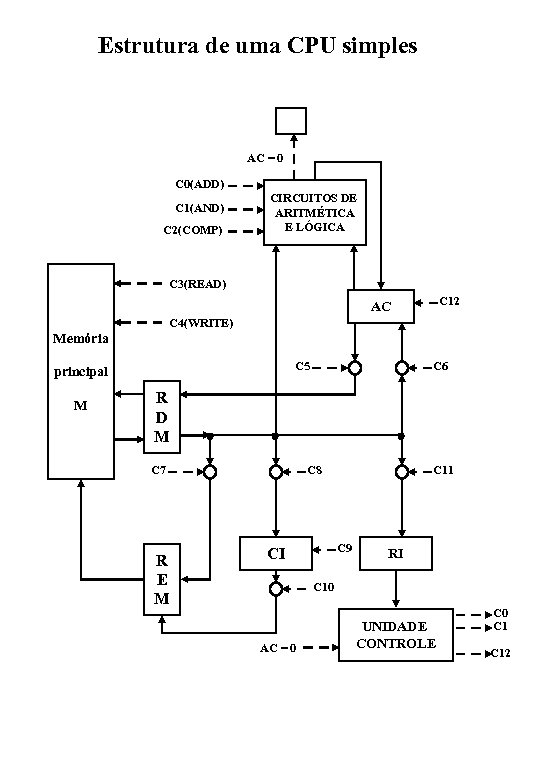

Estrutura de uma CPU simples AC = 0 C 0(ADD) C 1(AND) C 2(COMP) CIRCUITOS DE ARITMÉTICA E LÓGICA C 3(READ) C 12 AC C 4(WRITE) Memória C 5 principal M C 6 R D M C 7 R E M C 8 C 11 C 9 CI RI C 10 AC = 0 UNIDADE CONTROLE C 0 C 12

Estrutura de uma CPU simples AC = 0 C 0(ADD) C 1(AND) C 2(COMP) CIRCUITOS DE ARITMÉTICA E LÓGICA C 3(READ) C 12 AC C 4(WRITE) Memória C 5 principal M C 6 R D M C 7 R E M C 8 C 11 C 9 CI RI C 10 AC = 0 UNIDADE CONTROLE C 0 C 12

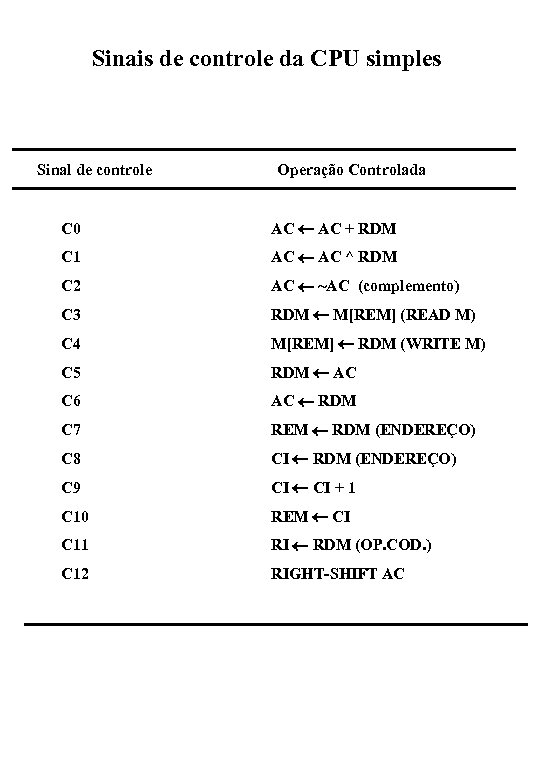

Sinais de controle da CPU simples Sinal de controle Operação Controlada C 0 AC + RDM C 1 AC ^ RDM C 2 AC ~AC (complemento) C 3 RDM M[REM] (READ M) C 4 M[REM] RDM (WRITE M) C 5 RDM AC C 6 AC RDM C 7 REM RDM (ENDEREÇO) C 8 CI RDM (ENDEREÇO) C 9 CI + 1 C 10 REM CI C 11 RI RDM (OP. COD. ) C 12 RIGHT-SHIFT AC

Sinais de controle da CPU simples Sinal de controle Operação Controlada C 0 AC + RDM C 1 AC ^ RDM C 2 AC ~AC (complemento) C 3 RDM M[REM] (READ M) C 4 M[REM] RDM (WRITE M) C 5 RDM AC C 6 AC RDM C 7 REM RDM (ENDEREÇO) C 8 CI RDM (ENDEREÇO) C 9 CI + 1 C 10 REM CI C 11 RI RDM (OP. COD. ) C 12 RIGHT-SHIFT AC

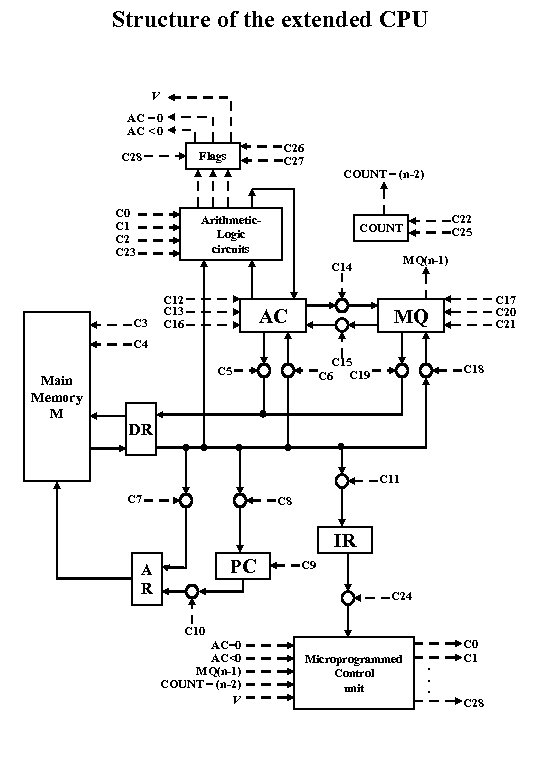

Structure of the extended CPU V AC = 0 AC < 0 C 26 C 27 Flags C 28 C 0 C 1 C 23 COUNT = (n-2) Arithmetic. Logic circuits MQ(n-1) C 14 C 3 C 12 C 13 C 16 C 22 C 25 COUNT AC C 17 C 20 C 21 MQ C 4 Main Memory M C 15 C 6 C 19 C 5 C 18 DR C 11 C 7 C 8 IR PC A R C 9 C 24 C 10 AC=0 AC<0 MQ(n-1) COUNT = (n-2) V Microprogrammed Control unit . . . C 0 C 1 C 28

Structure of the extended CPU V AC = 0 AC < 0 C 26 C 27 Flags C 28 C 0 C 1 C 23 COUNT = (n-2) Arithmetic. Logic circuits MQ(n-1) C 14 C 3 C 12 C 13 C 16 C 22 C 25 COUNT AC C 17 C 20 C 21 MQ C 4 Main Memory M C 15 C 6 C 19 C 5 C 18 DR C 11 C 7 C 8 IR PC A R C 9 C 24 C 10 AC=0 AC<0 MQ(n-1) COUNT = (n-2) V Microprogrammed Control unit . . . C 0 C 1 C 28

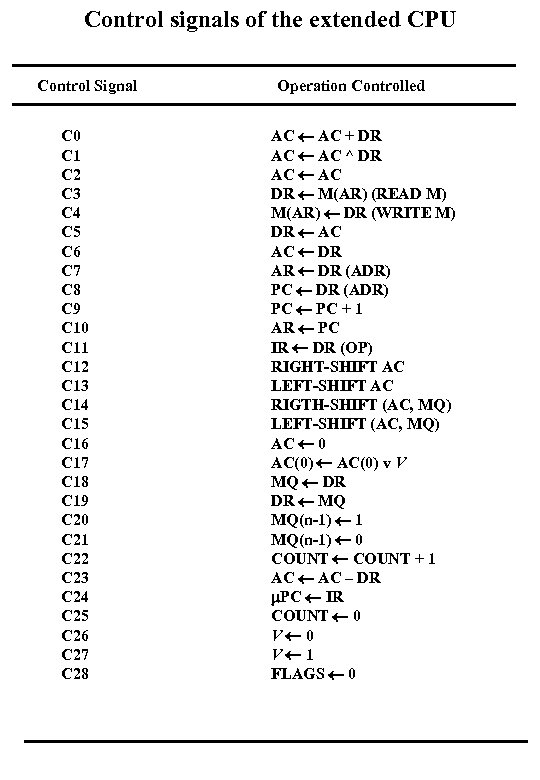

Control signals of the extended CPU Control Signal C 0 C 1 C 2 C 3 C 4 C 5 C 6 C 7 C 8 C 9 C 10 C 11 C 12 C 13 C 14 C 15 C 16 C 17 C 18 C 19 C 20 C 21 C 22 C 23 C 24 C 25 C 26 C 27 C 28 Operation Controlled AC + DR AC ^ DR AC DR M(AR) (READ M) M(AR) DR (WRITE M) DR AC AC DR AR DR (ADR) PC PC + 1 AR PC IR DR (OP) RIGHT-SHIFT AC LEFT-SHIFT AC RIGTH-SHIFT (AC, MQ) LEFT-SHIFT (AC, MQ) AC 0 AC(0) v V MQ DR DR MQ MQ(n-1) 1 MQ(n-1) 0 COUNT + 1 AC – DR PC IR COUNT 0 V 1 FLAGS 0

Control signals of the extended CPU Control Signal C 0 C 1 C 2 C 3 C 4 C 5 C 6 C 7 C 8 C 9 C 10 C 11 C 12 C 13 C 14 C 15 C 16 C 17 C 18 C 19 C 20 C 21 C 22 C 23 C 24 C 25 C 26 C 27 C 28 Operation Controlled AC + DR AC ^ DR AC DR M(AR) (READ M) M(AR) DR (WRITE M) DR AC AC DR AR DR (ADR) PC PC + 1 AR PC IR DR (OP) RIGHT-SHIFT AC LEFT-SHIFT AC RIGTH-SHIFT (AC, MQ) LEFT-SHIFT (AC, MQ) AC 0 AC(0) v V MQ DR DR MQ MQ(n-1) 1 MQ(n-1) 0 COUNT + 1 AC – DR PC IR COUNT 0 V 1 FLAGS 0