3af6d8f8a320c05034404775ea3dcca6.ppt

- Количество слайдов: 78

NSS-MIC 2009 SUMMARY Rafael Ballabriga PH-ESE-ME

NSS Conference • • • • -2 - Photodetectors and Scintillation detectors Semiconductor Detectors Analog and digital circuits Nuclear measurements and monitoring techniques New detector concepts and instrumentation Instrumentation for homeland security Data acquisition and analysis systems Radiation damage effects Computing and software for experiments Trigger and front-end systems Gaseous detectors High energy physics instrumentation Gamma ray imaging Neutron Imaging Accelerators and beam line instrumentation NSS-MIC conference, Orlando (October 2009) R. Ballabriga

MIC Conference • • -3 - X-Ray imaging PET/SPECT instrumentation Simulation and modelling of medical imaging systems Animal imaging and instrumentation techniques Image processing and evaluation Image reconstruction Quantitative imaging techniques NSS-MIC conference, Orlando (October 2009) R. Ballabriga

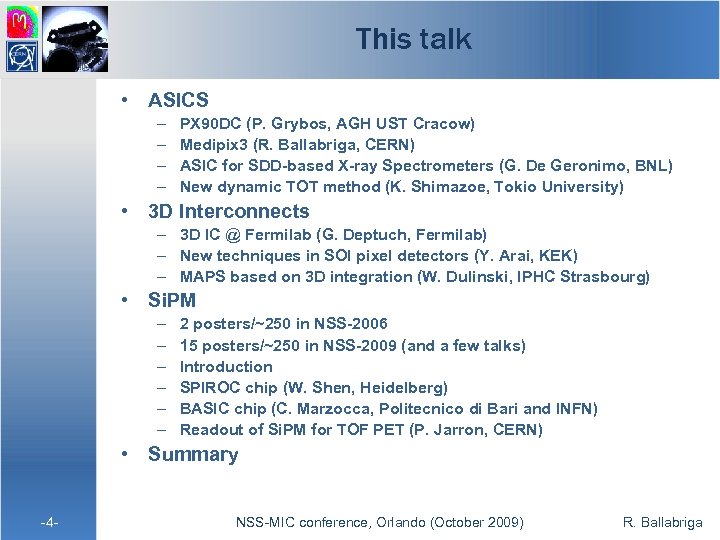

This talk • ASICS – – PX 90 DC (P. Grybos, AGH UST Cracow) Medipix 3 (R. Ballabriga, CERN) ASIC for SDD-based X-ray Spectrometers (G. De Geronimo, BNL) New dynamic TOT method (K. Shimazoe, Tokio University) • 3 D Interconnects – 3 D IC @ Fermilab (G. Deptuch, Fermilab) – New techniques in SOI pixel detectors (Y. Arai, KEK) – MAPS based on 3 D integration (W. Dulinski, IPHC Strasbourg) • Si. PM – – – 2 posters/~250 in NSS-2006 15 posters/~250 in NSS-2009 (and a few talks) Introduction SPIROC chip (W. Shen, Heidelberg) BASIC chip (C. Marzocca, Politecnico di Bari and INFN) Readout of Si. PM for TOF PET (P. Jarron, CERN) • Summary -4 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

ASICs -5 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

-6 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

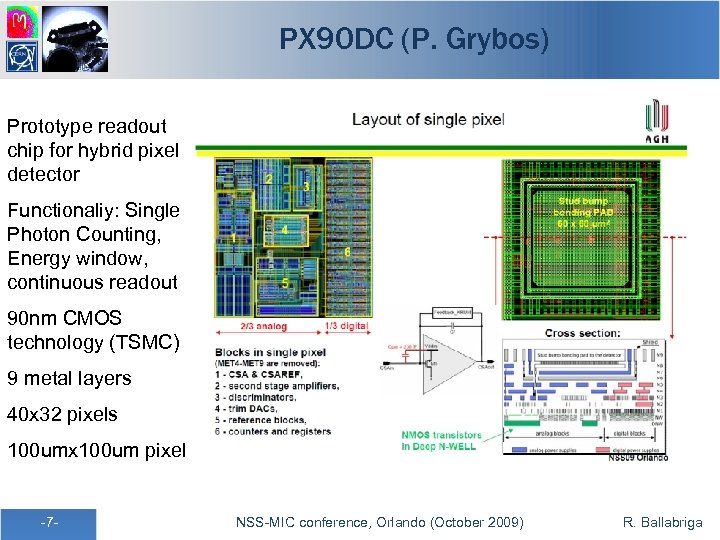

PX 90 DC (P. Grybos) Prototype readout chip for hybrid pixel detector Functionaliy: Single Photon Counting, Energy window, continuous readout 90 nm CMOS technology (TSMC) 9 metal layers 40 x 32 pixels 100 umx 100 um pixel -7 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

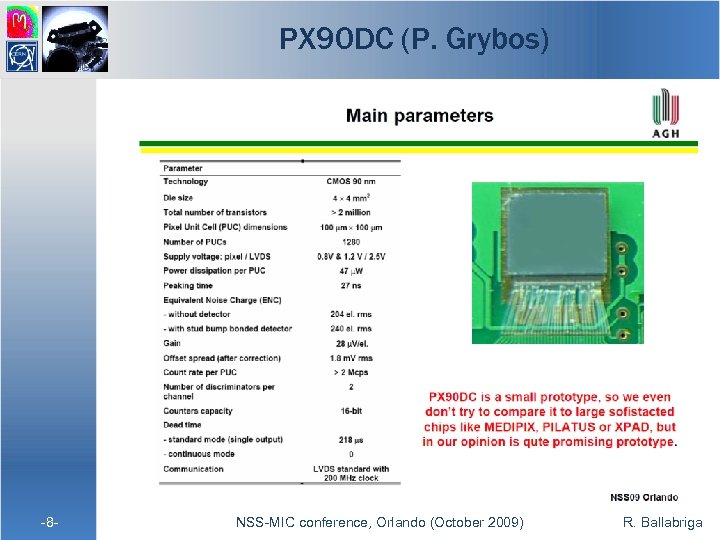

PX 90 DC (P. Grybos) -8 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Characterization of the Medipix 3 Pixel Readout Chip R. Ballabriga, M. Campbell, E. H. M. Heijne, J. Jakubek, X. Llopart, R. Plackett, S. Pospisil, L. Tlustos, Z. Vykydal, W. Wong CERN, PH department -9 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Medipix 3 Introduction • Medipix 3 is a Hybrid Pixel Detector readout chip working in Single Photon Counting Mode • Designed in 130 nm CMOS technology • Highly configurable pixel • Flexible readout scheme (ROI, Configurable output port width) • It implements a novel architecture for improving the system’s spectrometric performance Eliminating the distortion from charge diffusion in the spectrum -10 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

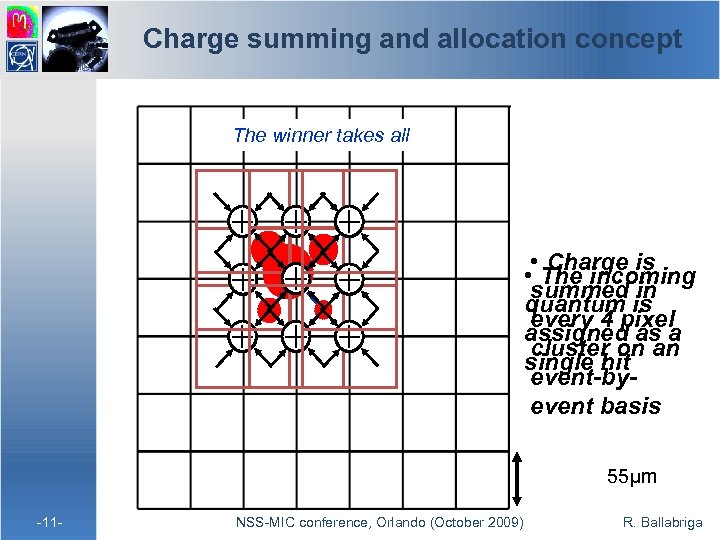

Charge summing and allocation concept The winner takes all • Charge is • The incoming summed in quantum is every 4 pixel assigned as a cluster on an single hit event-byevent basis 55µm -11 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

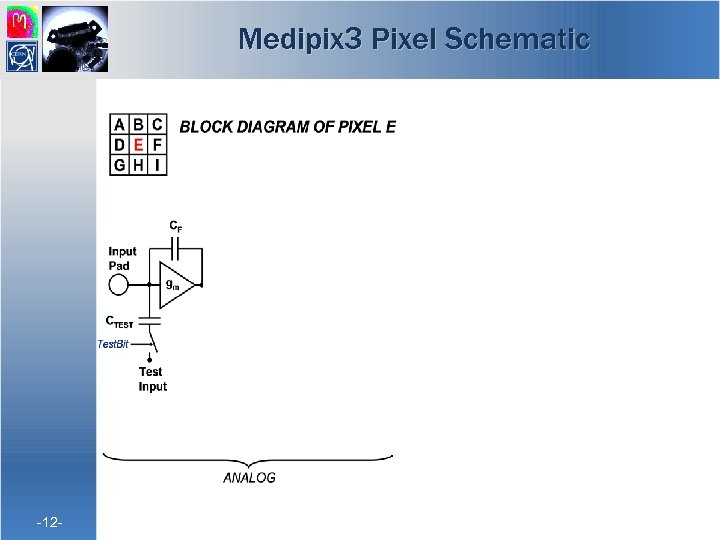

Medipix 3 Pixel Schematic -12 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

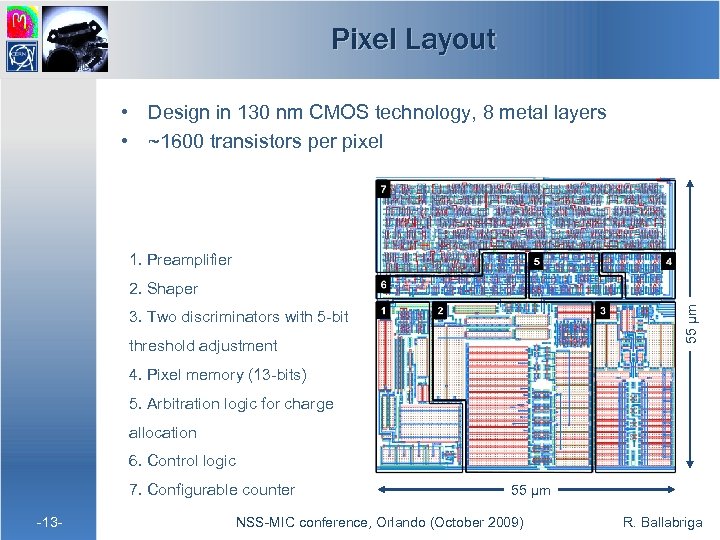

Pixel Layout • Design in 130 nm CMOS technology, 8 metal layers • ~1600 transistors per pixel 1. Preamplifier 55 µm 2. Shaper 3. Two discriminators with 5 -bit threshold adjustment 4. Pixel memory (13 -bits) 5. Arbitration logic for charge allocation 6. Control logic 7. Configurable counter -13 - 55 µm NSS-MIC conference, Orlando (October 2009) R. Ballabriga

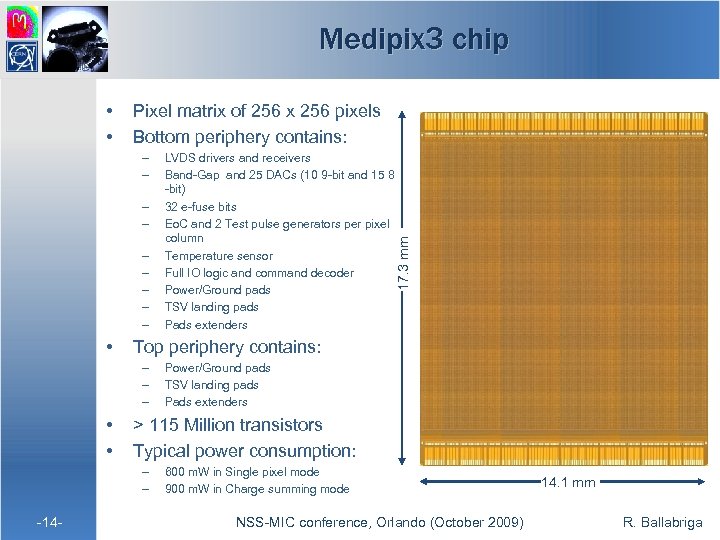

Medipix 3 chip Pixel matrix of 256 x 256 pixels Bottom periphery contains: – – – – – • Top periphery contains: – – – • • Power/Ground pads TSV landing pads Pads extenders > 115 Million transistors Typical power consumption: – – -14 - LVDS drivers and receivers Band-Gap and 25 DACs (10 9 -bit and 15 8 -bit) 32 e-fuse bits Eo. C and 2 Test pulse generators per pixel column Temperature sensor Full IO logic and command decoder Power/Ground pads TSV landing pads Pads extenders 17. 3 mm • • 600 m. W in Single pixel mode 900 m. W in Charge summing mode NSS-MIC conference, Orlando (October 2009) 14. 1 mm R. Ballabriga

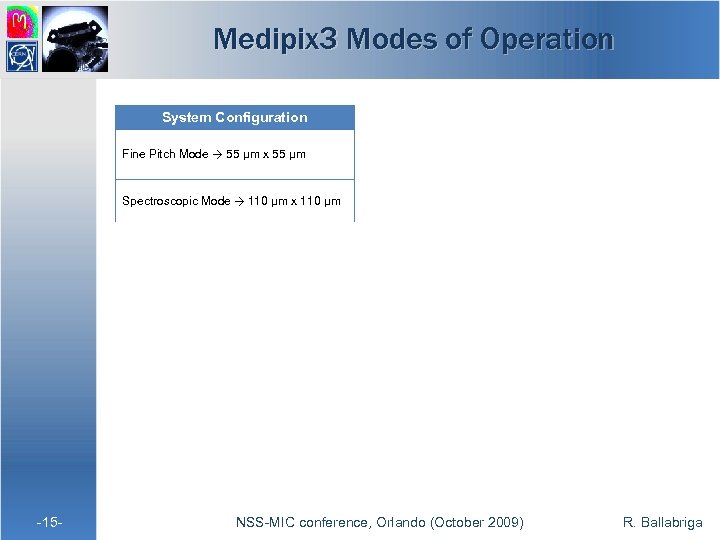

Medipix 3 Modes of Operation System Configuration Pixel Operating Modes # Thresholds Single Pixel Mode Fine Pitch Mode → 55 µm x 55 µm Spectroscopic Mode → 110 µm x 110 µm Front-end Gain Modes Charge Summing Mode Single Cluster Mode Charge Summing Mode Linearity High Gain Mode ~10 ke- Low Gain Mode ~20 ke- Pixel Counter Modes 2 8 # Thresholds 2 Dynamic range # Counters 1 -bit 1 2 4 -bit 15 2 12 -bit 4095 2 24 -bit 16777215 1 # Active Counters Dead Time Sequential Read-Write 2 Yes Continuous Read-Write 1 No Pixel Readout Modes -15 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Electrical Measurements -16 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

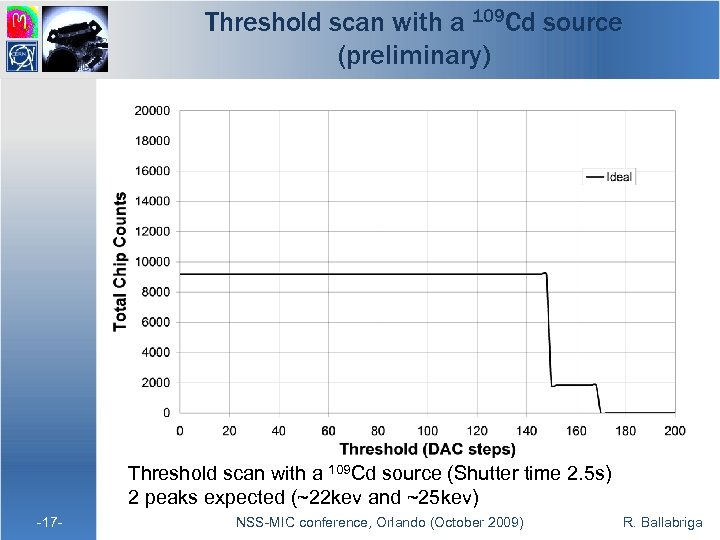

Threshold scan with a 109 Cd source (preliminary) Threshold scan with a 109 Cd source (Shutter time 2. 5 s) 2 peaks expected (~22 kev and ~25 kev) -17 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

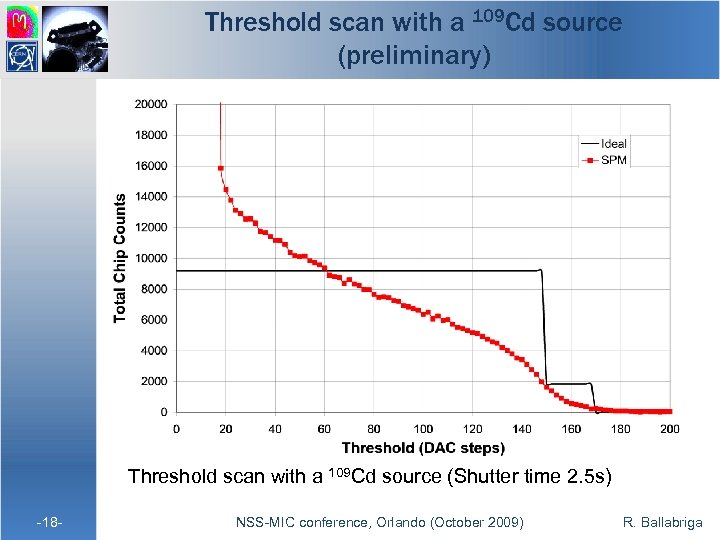

Threshold scan with a 109 Cd source (preliminary) Threshold scan with a 109 Cd source (Shutter time 2. 5 s) -18 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

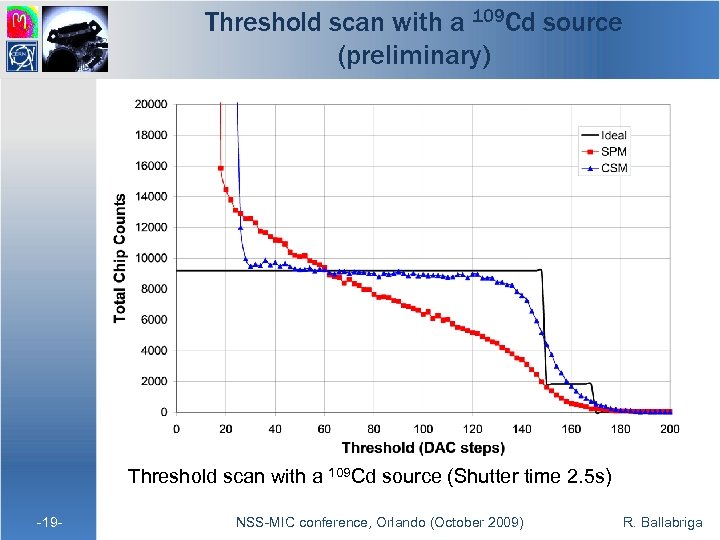

Threshold scan with a 109 Cd source (preliminary) Threshold scan with a 109 Cd source (Shutter time 2. 5 s) -19 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

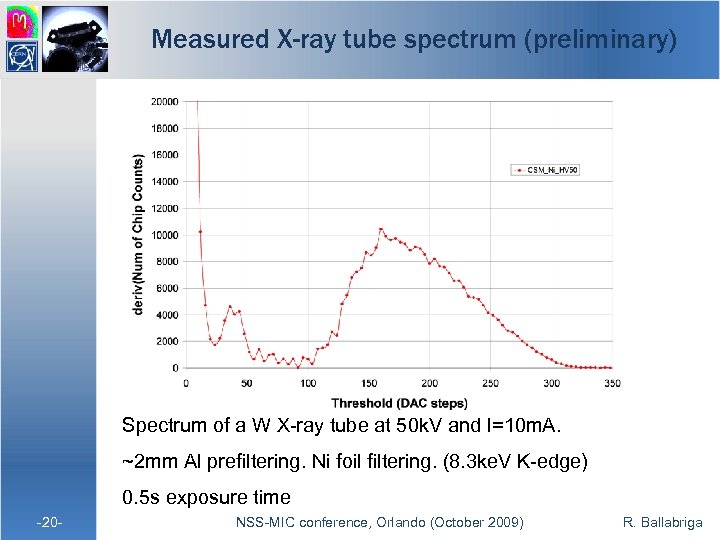

Measured X-ray tube spectrum (preliminary) Spectrum of a W X-ray tube at 50 k. V and I=10 m. A. ~2 mm Al prefiltering. Ni foil filtering. (8. 3 ke. V K-edge) 0. 5 s exposure time -20 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

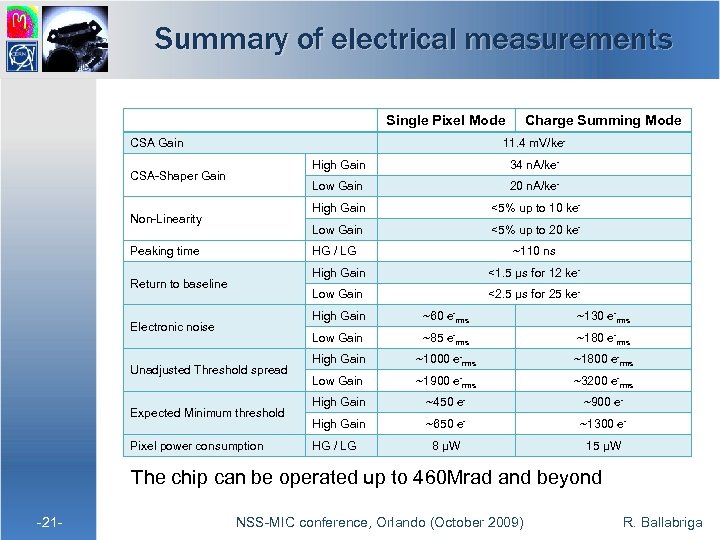

Summary of electrical measurements Single Pixel Mode CSA Gain Charge Summing Mode 11. 4 m. V/ke. High Gain <5% up to 10 ke- Low Gain <5% up to 20 ke- HG / LG Peaking time 20 n. A/ke- High Gain Non-Linearity 34 n. A/ke- Low Gain CSA-Shaper Gain ~110 ns High Gain <1. 5 µs for 12 ke- Low Gain Return to baseline <2. 5 µs for 25 ke- High Gain Unadjusted Threshold spread Expected Minimum threshold Pixel power consumption ~60 e-rms ~130 e-rms Low Gain Electronic noise ~85 e-rms ~180 e-rms High Gain ~1000 e-rms ~1800 e-rms Low Gain ~1900 e-rms ~3200 e-rms High Gain ~450 e- ~900 e- High Gain ~650 e- ~1300 e- 8 µW 15 µW HG / LG The chip can be operated up to 460 Mrad and beyond -21 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

-22 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

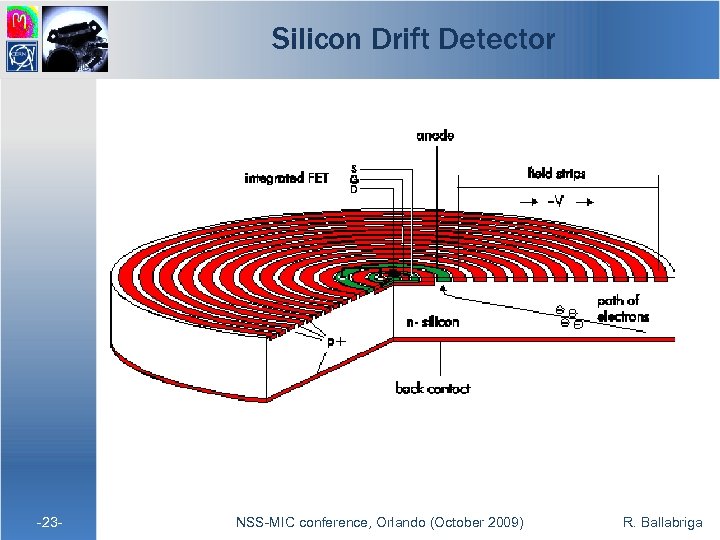

Silicon Drift Detector -23 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

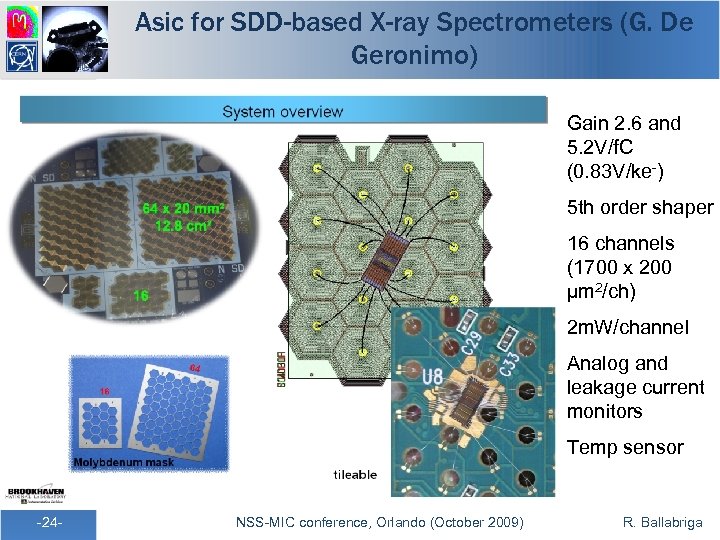

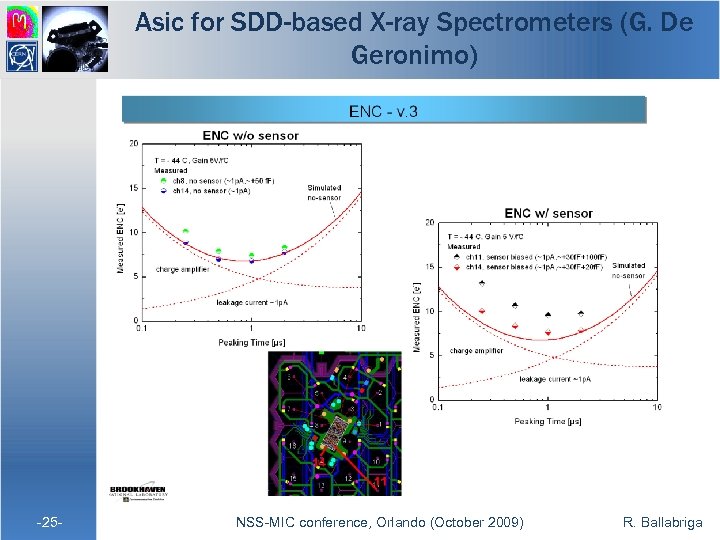

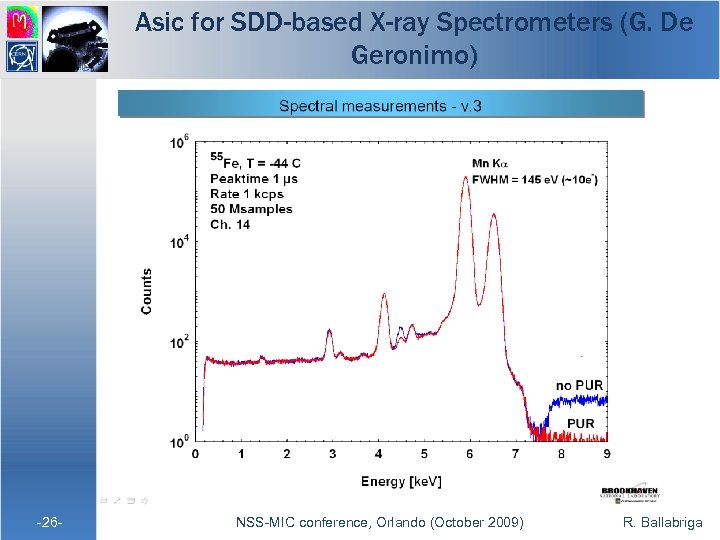

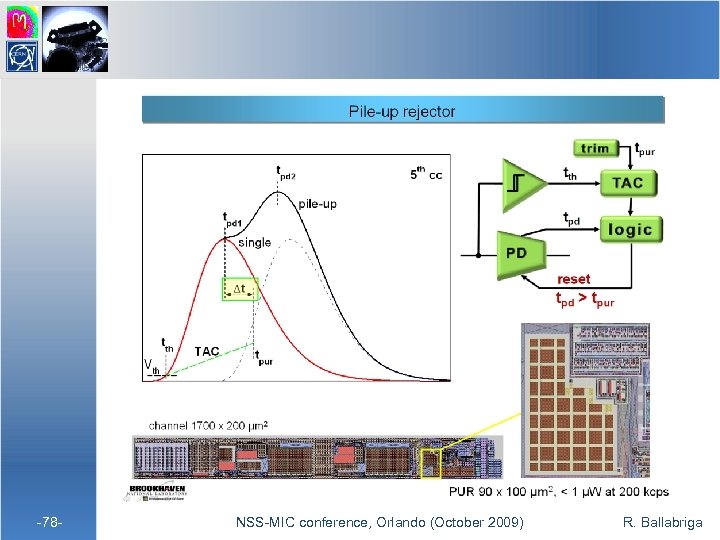

Asic for SDD-based X-ray Spectrometers (G. De Geronimo) Gain 2. 6 and 5. 2 V/f. C (0. 83 V/ke-) 5 th order shaper 16 channels (1700 x 200 µm 2/ch) 2 m. W/channel Analog and leakage current monitors Temp sensor -24 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Asic for SDD-based X-ray Spectrometers (G. De Geronimo) -25 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Asic for SDD-based X-ray Spectrometers (G. De Geronimo) -26 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

A New Dynamic Time over Threshold Method K. Shimazoe 1, H. Takahashi 1, T. Fujiwara 2, T. Furumiya 3, J. Ohi 3, Y. Kumazawa 3 1 Bioengineering, The University of Tokyo, Bunkyo-ku, Japan 2 Nuclear Engineering and Management, The University of Tokyo, Bunkyo-ku, Japan 3 Shimadzu Corporation, Kyoto, Japan -27 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

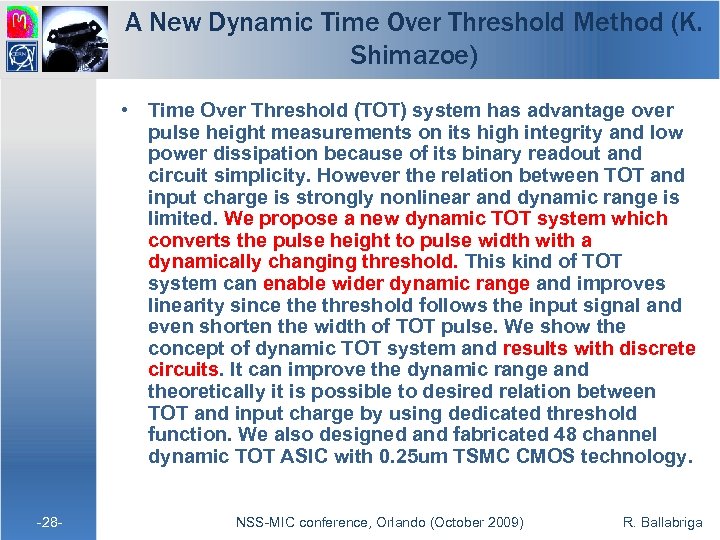

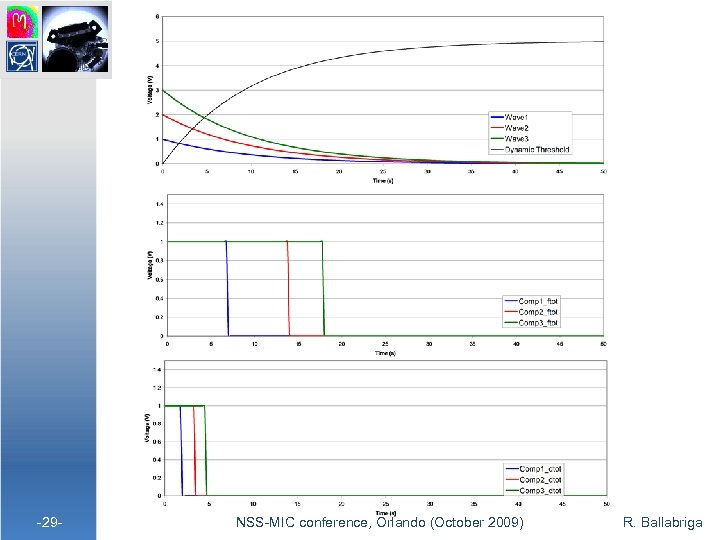

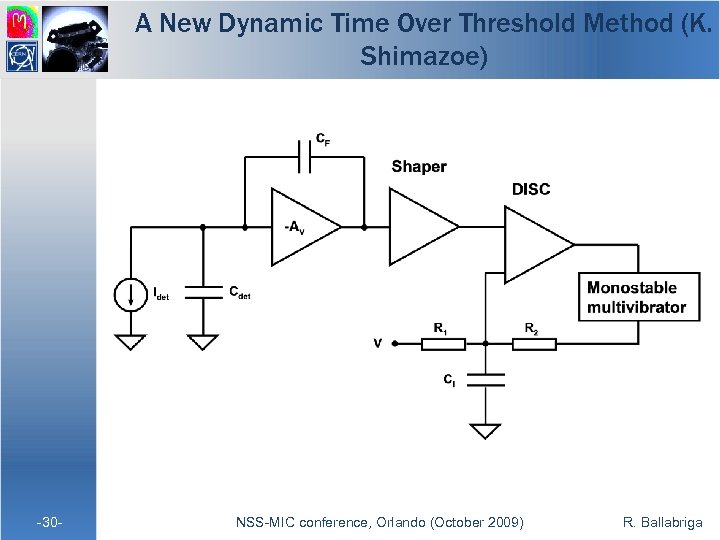

A New Dynamic Time Over Threshold Method (K. Shimazoe) • Time Over Threshold (TOT) system has advantage over pulse height measurements on its high integrity and low power dissipation because of its binary readout and circuit simplicity. However the relation between TOT and input charge is strongly nonlinear and dynamic range is limited. We propose a new dynamic TOT system which converts the pulse height to pulse width with a dynamically changing threshold. This kind of TOT system can enable wider dynamic range and improves linearity since threshold follows the input signal and even shorten the width of TOT pulse. We show the concept of dynamic TOT system and results with discrete circuits. It can improve the dynamic range and theoretically it is possible to desired relation between TOT and input charge by using dedicated threshold function. We also designed and fabricated 48 channel dynamic TOT ASIC with 0. 25 um TSMC CMOS technology. -28 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

-29 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

A New Dynamic Time Over Threshold Method (K. Shimazoe) -30 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

3 D interconnects -31 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

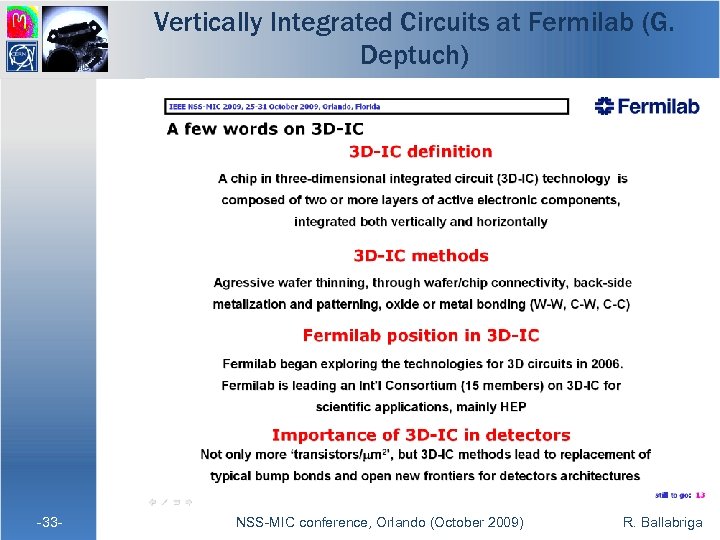

Vertically Integrated Circuits at Fermilab (G. Deptuch) -32 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Vertically Integrated Circuits at Fermilab (G. Deptuch) -33 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

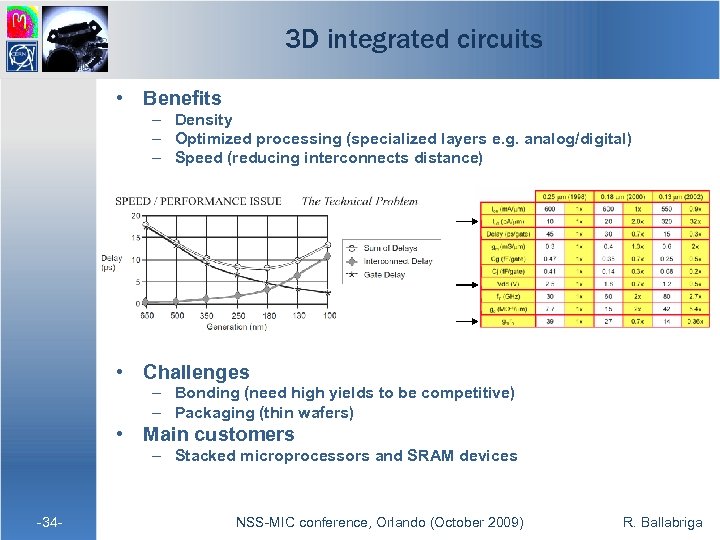

3 D integrated circuits • Benefits – Density – Optimized processing (specialized layers e. g. analog/digital) – Speed (reducing interconnects distance) • Challenges – Bonding (need high yields to be competitive) – Packaging (thin wafers) • Main customers – Stacked microprocessors and SRAM devices -34 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

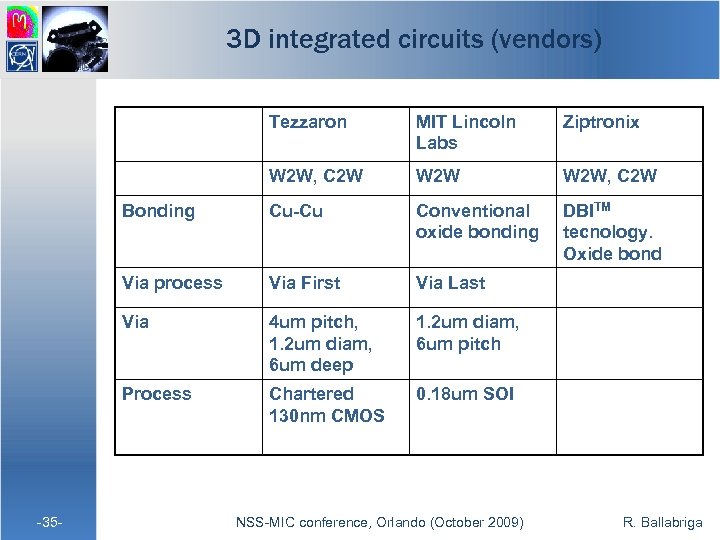

3 D integrated circuits (vendors) Tezzaron Ziptronix W 2 W, C 2 W Bonding Cu-Cu Conventional oxide bonding DBITM tecnology. Oxide bond Via process Via First Via Last Via 4 um pitch, 1. 2 um diam, 6 um deep 1. 2 um diam, 6 um pitch Process -35 - MIT Lincoln Labs Chartered 130 nm CMOS 0. 18 um SOI NSS-MIC conference, Orlando (October 2009) R. Ballabriga

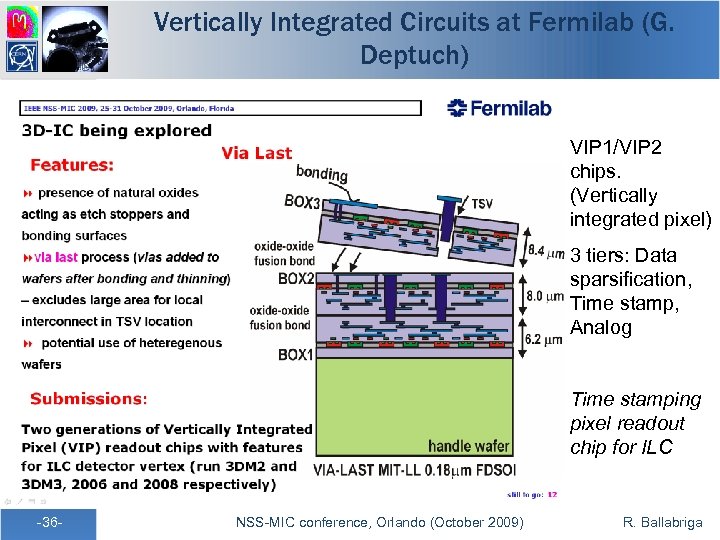

Vertically Integrated Circuits at Fermilab (G. Deptuch) VIP 1/VIP 2 chips. (Vertically integrated pixel) 3 tiers: Data sparsification, Time stamp, Analog Time stamping pixel readout chip for ILC -36 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

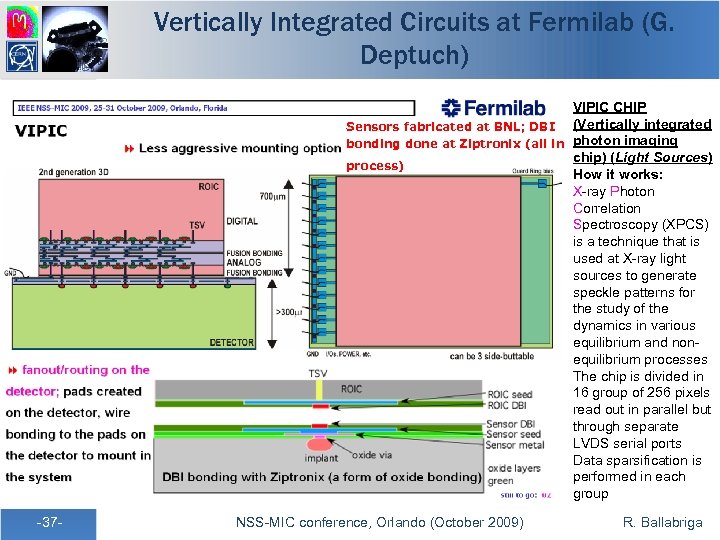

Vertically Integrated Circuits at Fermilab (G. Deptuch) VIPIC CHIP Sensors fabricated at BNL; DBI (Vertically integrated bonding done at Ziptronix (all in photon imaging chip) (Light Sources) process) How it works: X-ray Photon Correlation Spectroscopy (XPCS) is a technique that is used at X-ray light sources to generate speckle patterns for the study of the dynamics in various equilibrium and nonequilibrium processes The chip is divided in 16 group of 256 pixels read out in parallel but through separate LVDS serial ports Data sparsification is performed in each group -37 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

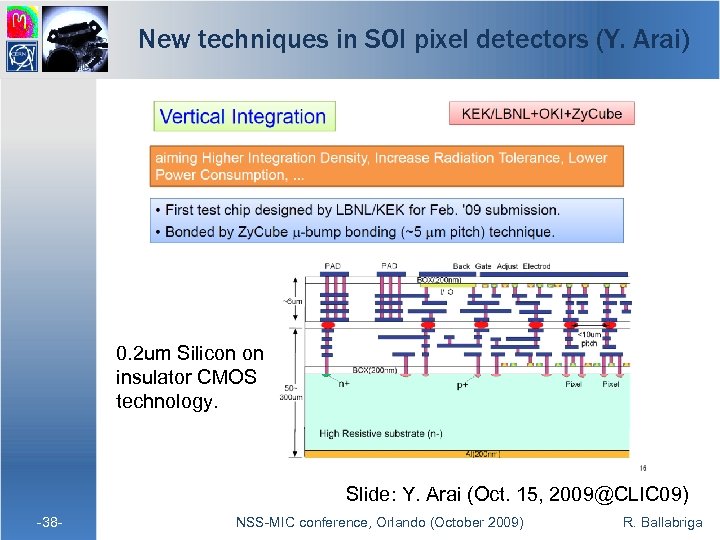

New techniques in SOI pixel detectors (Y. Arai) 0. 2 um Silicon on insulator CMOS technology. Slide: Y. Arai (Oct. 15, 2009@CLIC 09) -38 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

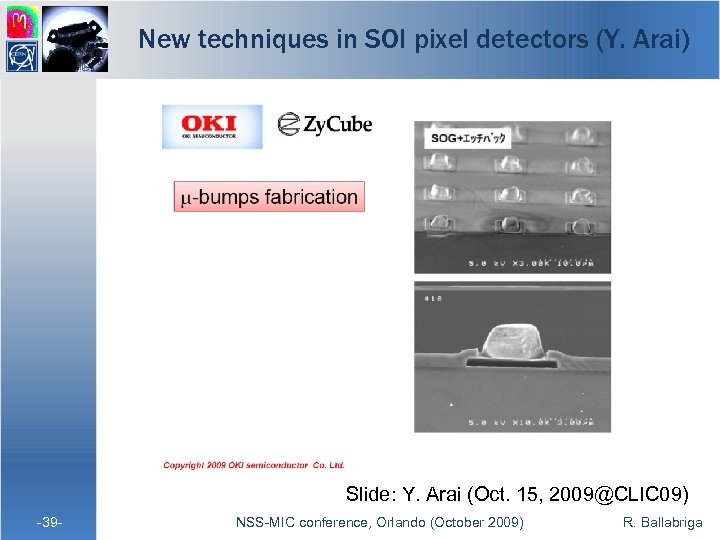

New techniques in SOI pixel detectors (Y. Arai) Slide: Y. Arai (Oct. 15, 2009@CLIC 09) -39 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Ultra Thin, Fully depleted MAPS based on 3 D integration of Heterogeneous CMOS layers (Wojciech Dulinski, Strasbourg) -40 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

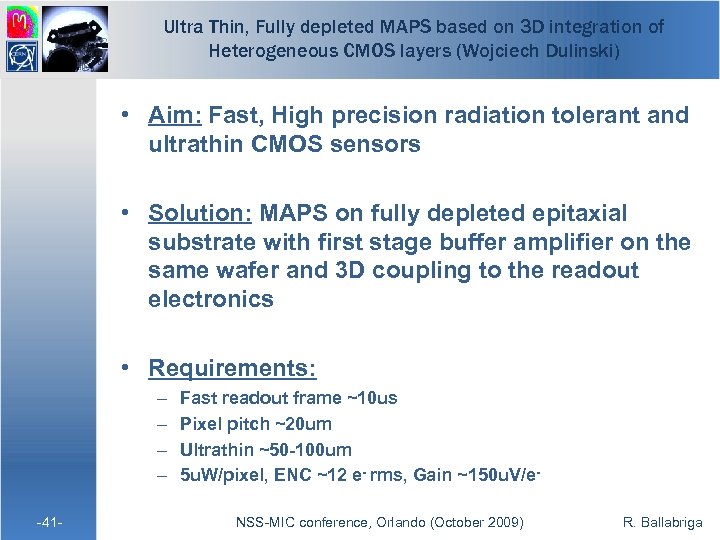

Ultra Thin, Fully depleted MAPS based on 3 D integration of Heterogeneous CMOS layers (Wojciech Dulinski) • Aim: Fast, High precision radiation tolerant and ultrathin CMOS sensors • Solution: MAPS on fully depleted epitaxial substrate with first stage buffer amplifier on the same wafer and 3 D coupling to the readout electronics • Requirements: – – -41 - Fast readout frame ~10 us Pixel pitch ~20 um Ultrathin ~50 -100 um 5 u. W/pixel, ENC ~12 e- rms, Gain ~150 u. V/e. NSS-MIC conference, Orlando (October 2009) R. Ballabriga

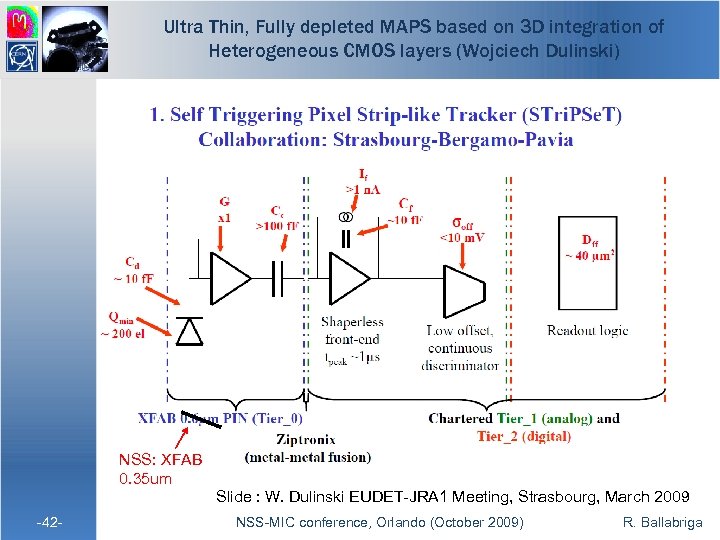

Ultra Thin, Fully depleted MAPS based on 3 D integration of Heterogeneous CMOS layers (Wojciech Dulinski) NSS: XFAB 0. 35 um -42 - Slide : W. Dulinski EUDET-JRA 1 Meeting, Strasbourg, March 2009 NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Si. PM -43 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

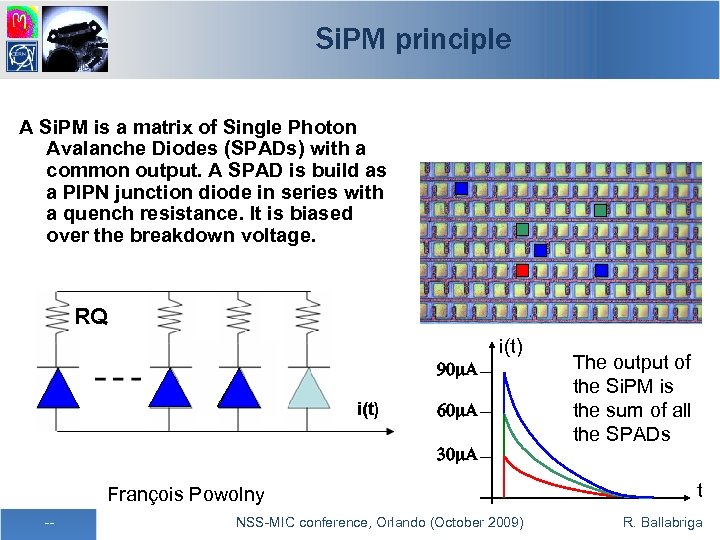

Si. PM principle A Si. PM is a matrix of Single Photon Avalanche Diodes (SPADs) with a common output. A SPAD is build as a PIPN junction diode in series with a quench resistance. It is biased over the breakdown voltage. 90 m. A i(t) 60 m. A 30 m. A François Powolny -- NSS-MIC conference, Orlando (October 2009) The output of the Si. PM is the sum of all the SPADs t R. Ballabriga

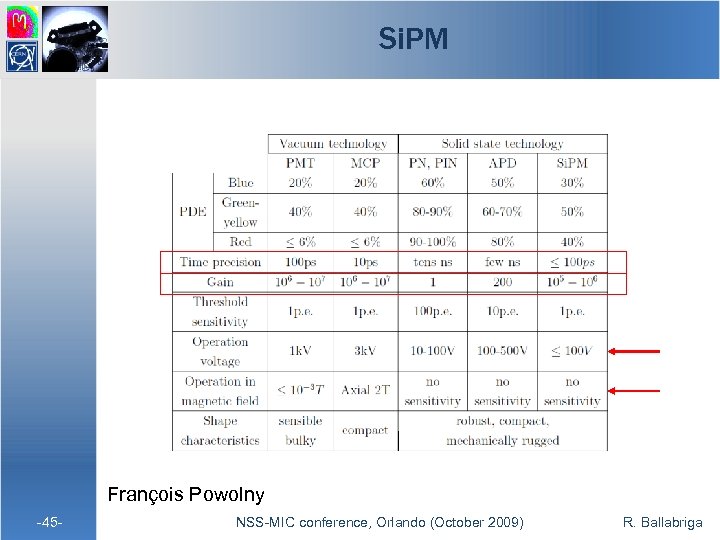

Si. PM François Powolny -45 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

-46 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

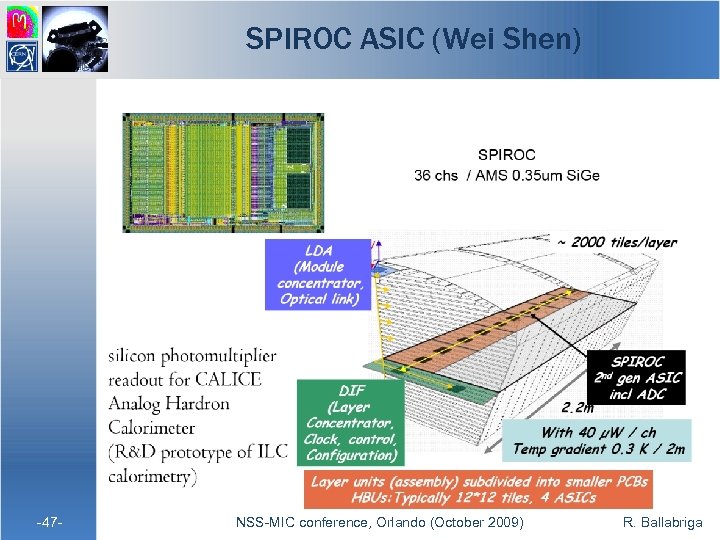

SPIROC ASIC (Wei Shen) -47 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

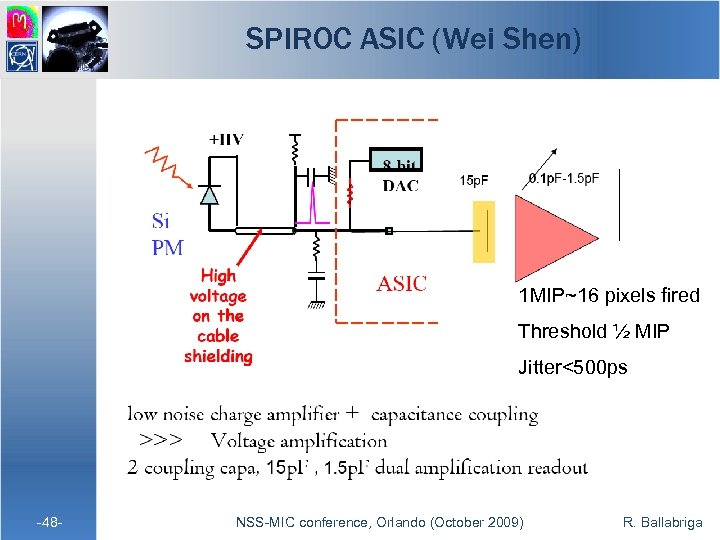

SPIROC ASIC (Wei Shen) 1 MIP~16 pixels fired Threshold ½ MIP Jitter<500 ps -48 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

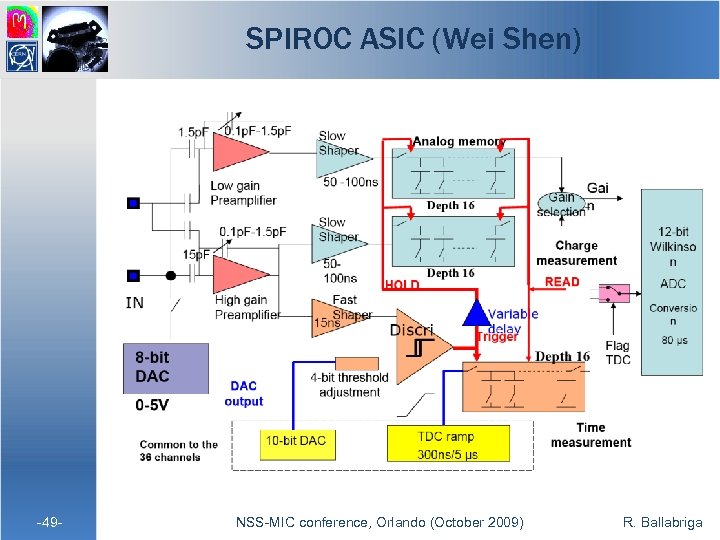

SPIROC ASIC (Wei Shen) -49 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

-50 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

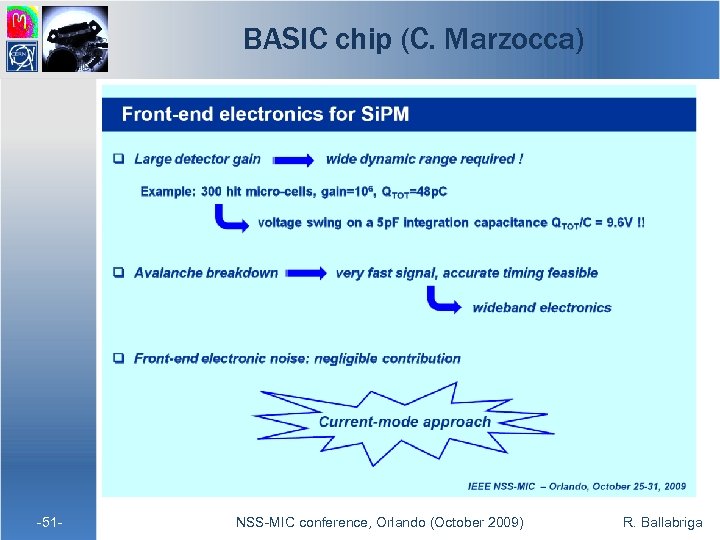

BASIC chip (C. Marzocca) -51 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

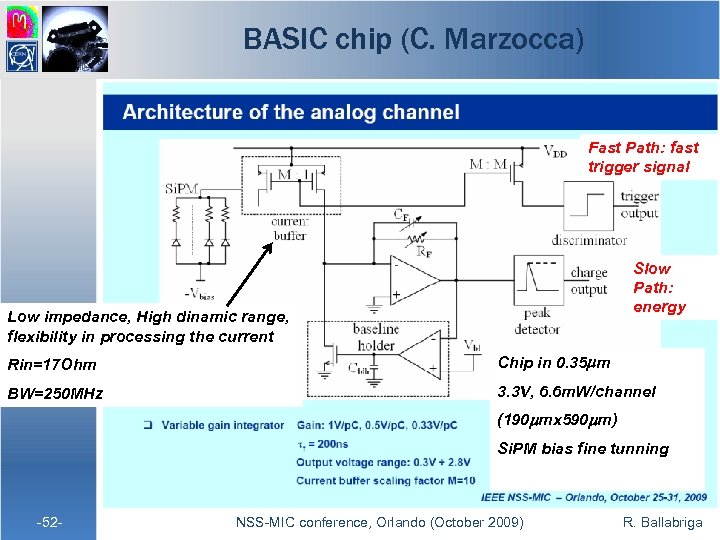

BASIC chip (C. Marzocca) Fast Path: fast trigger signal Slow Path: energy Low impedance, High dinamic range, flexibility in processing the current Rin=17 Ohm Chip in 0. 35 mm BW=250 MHz 3. 3 V, 6. 6 m. W/channel (190 mmx 590 mm) Si. PM bias fine tunning -52 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

-53 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

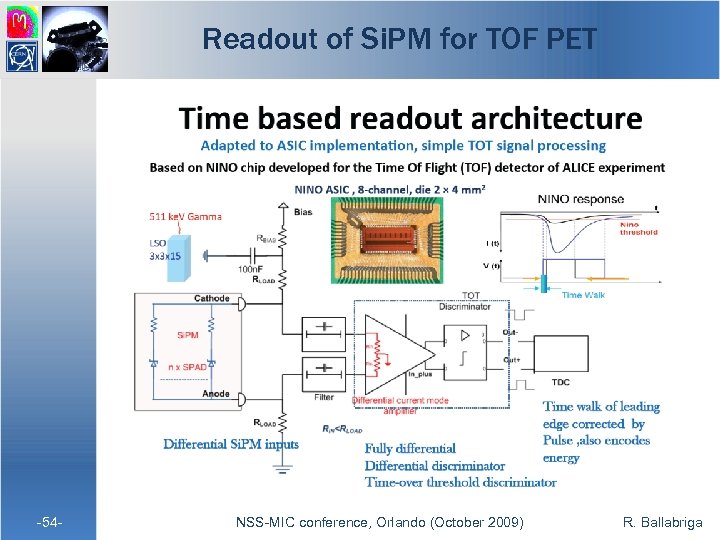

Readout of Si. PM for TOF PET -54 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

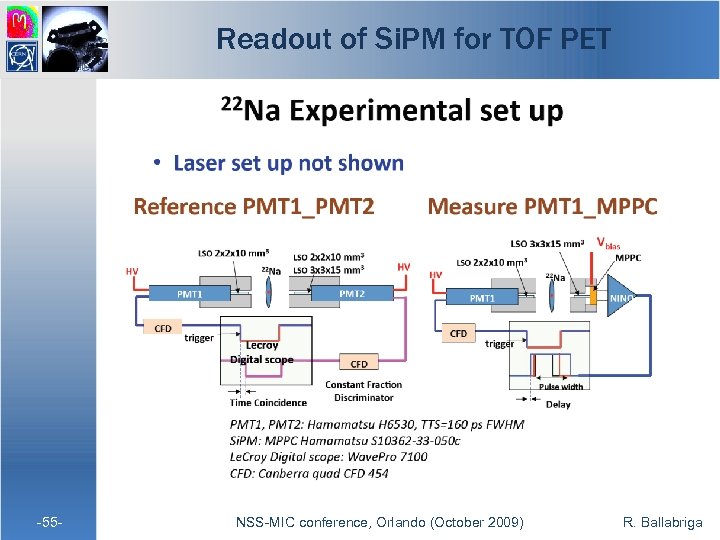

Readout of Si. PM for TOF PET -55 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

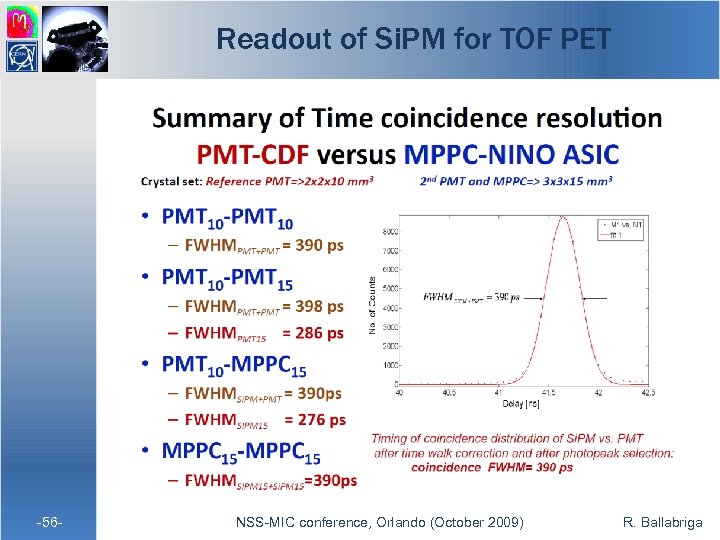

Readout of Si. PM for TOF PET -56 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Summary -57 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Summary • Some ASICs that were presented at NSS have been presented in this presentation. • An international collaboration in the field of 3 D IC for HEP was created. 3 D IC brings benefits and challenges and seems a direction industry is taking. • Si. PMs are emerging as candidates to replace Photomultiplier tubes, specially in medical imaging due to insensitivity to magnetic fields and operating « low voltage » . They were chosen in HEP for the Hadron Calorimeter for the ILC. -58 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Other designs of interest (for completeness) • A Pixel Front-End ASIC in 0. 13 μm CMOS for the NA 62 Experiment with on Pixel 100 ps Time-to-Digital Conversion • FE-I 4: the New ATLAS Pixel Chip for Upgraded LHC Luminosities • PARISROC, a Photomultiplier Array Integrated Read Out Chip • FREDA: a Programmable Mixed Signal ASIC for Gas Micro-Strip Detectors Having a Wide Range of Input Capacitance • Design and Performance of the ABCN-25 Readout Chip for the ATLAS Inner Detector Upgrade • Low Noise 64 -Channel ASIC for Si, Ga. As and Cd. Te Strip Detectors -59 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Additional Slides -60 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Medipix 3 Dicing options -61 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

![Multiple dicing options Y [µm] Active Area Medipix 2 and Timepix 14111 16120 87. Multiple dicing options Y [µm] Active Area Medipix 2 and Timepix 14111 16120 87.](https://present5.com/presentation/3af6d8f8a320c05034404775ea3dcca6/image-62.jpg)

Multiple dicing options Y [µm] Active Area Medipix 2 and Timepix 14111 16120 87. 1% Medipix 3 top and bottom WB 14100 17300 81. 2% Medipix 3 bottom WB 14100 15900 88. 4% Medipix 3 top and bottom TVS 14100 15300 91. 9% Medipix 3 bottom TVS 14100 14900 94. 3% 15. 3 mm 15. 9 mm 14. 9 mm 17. 3 mm X [µm] 14. 1 mm -62 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Equalization procedure -63 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

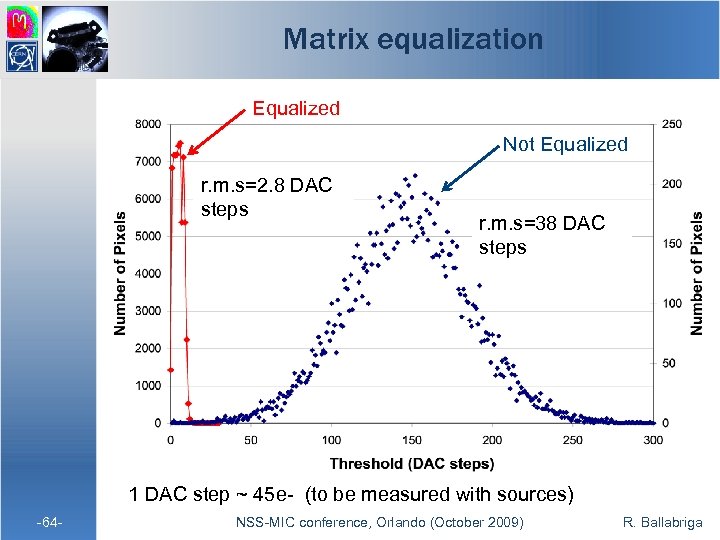

Matrix equalization Equalized Not Equalized r. m. s=2. 8 DAC steps r. m. s=38 DAC steps 1 DAC step ~ 45 e- (to be measured with sources) -64 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Chip power consumption -65 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

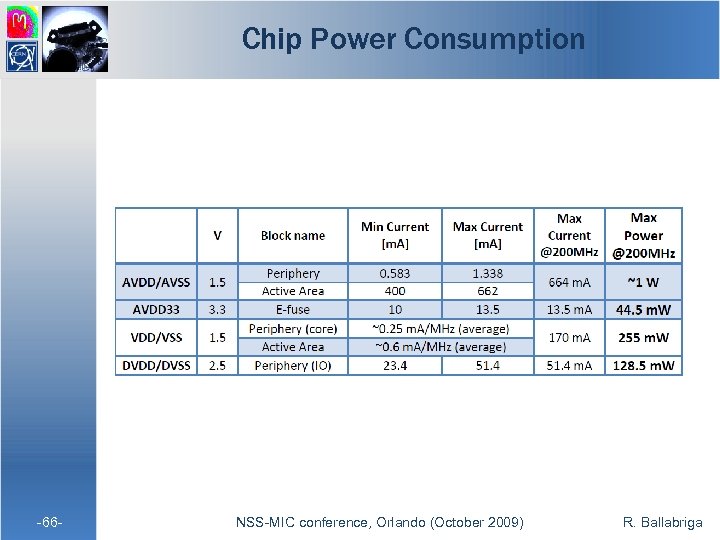

Chip Power Consumption -66 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

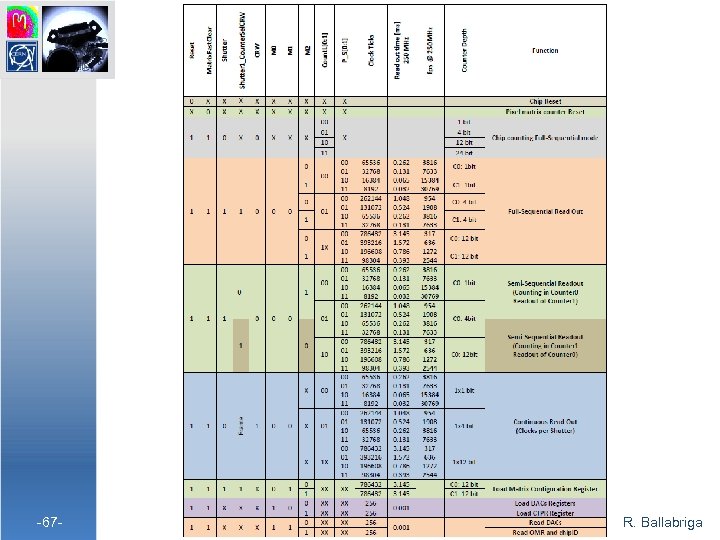

-67 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

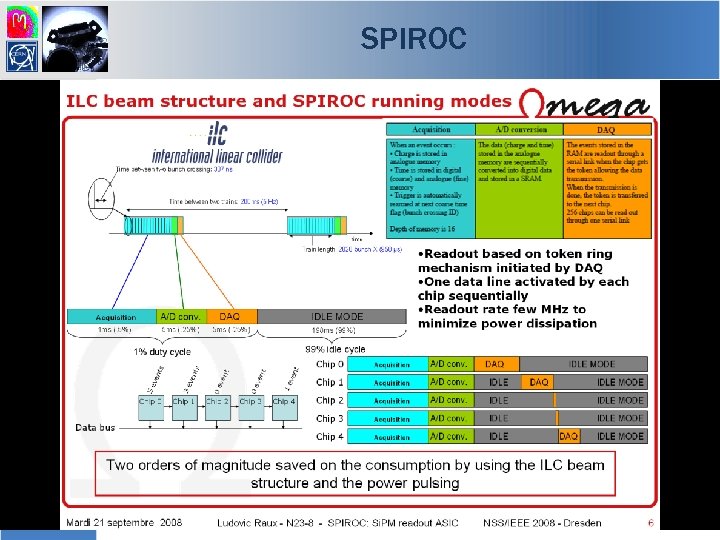

SPIROC -68 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

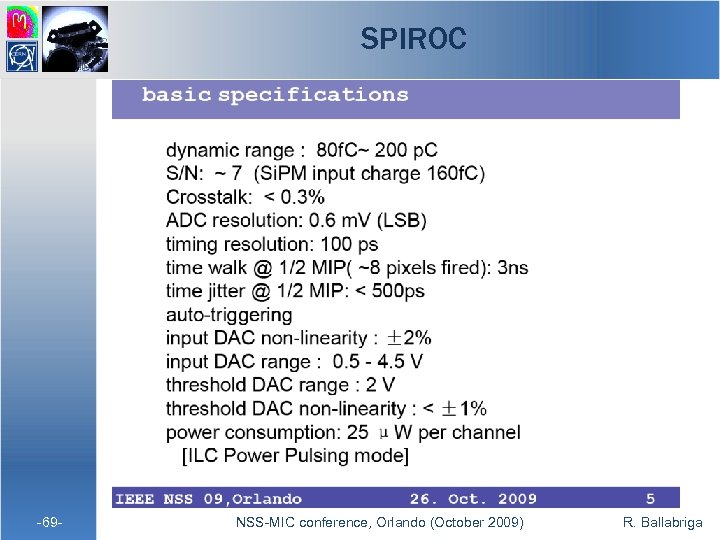

SPIROC -69 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

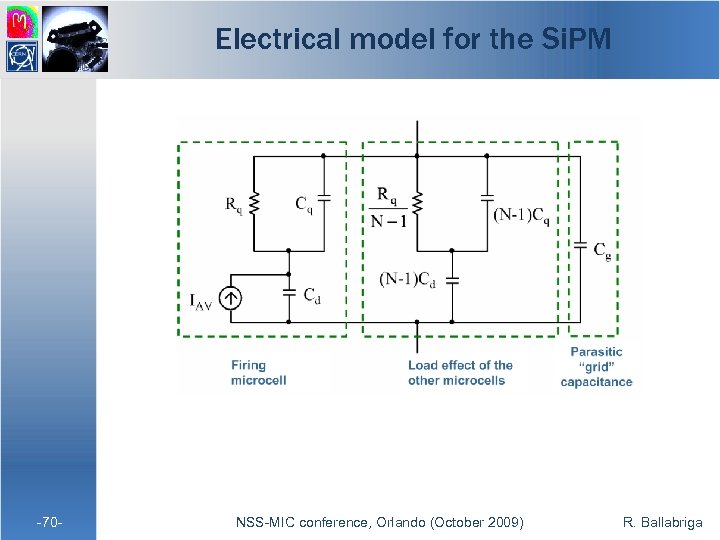

Electrical model for the Si. PM -70 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

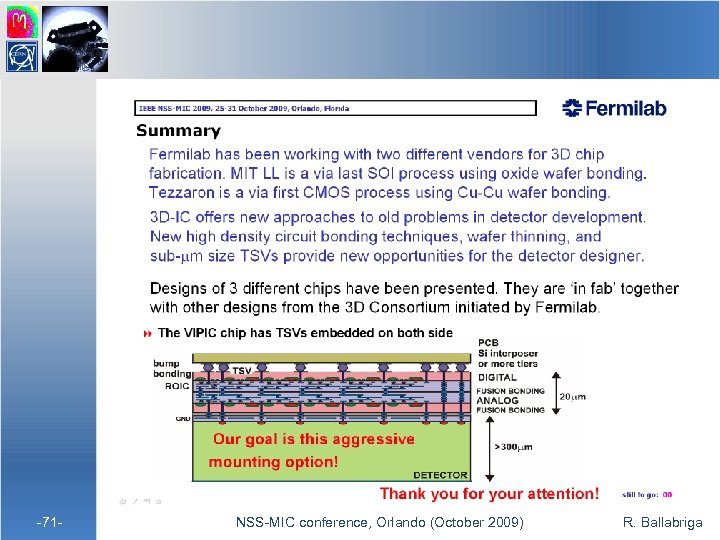

-71 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

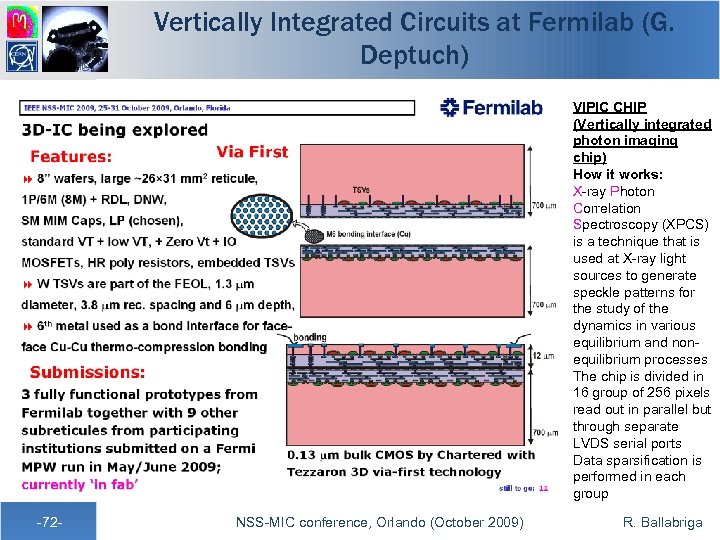

Vertically Integrated Circuits at Fermilab (G. Deptuch) VIPIC CHIP (Vertically integrated photon imaging chip) How it works: X-ray Photon Correlation Spectroscopy (XPCS) is a technique that is used at X-ray light sources to generate speckle patterns for the study of the dynamics in various equilibrium and nonequilibrium processes The chip is divided in 16 group of 256 pixels read out in parallel but through separate LVDS serial ports Data sparsification is performed in each group -72 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

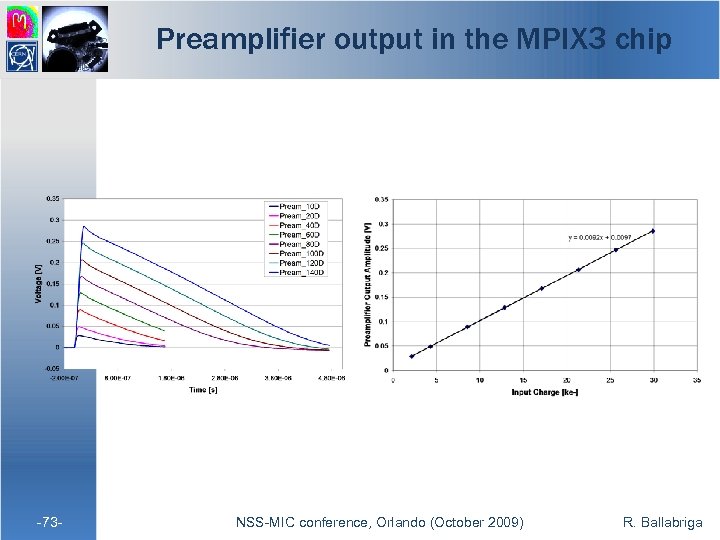

Preamplifier output in the MPIX 3 chip -73 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Stud Bonding -74 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Stud bonding (http: //www. flipchips. com/tutorial 03. html) • The gold stud bump flip chip assembly process creates conductive gold bumps on the die bond pads, and connects the die to the circuit board or substrate with adhesive or ultrasonic assembly. Stud bumping requires no underbump metallization (UBM), and thus does not require wafer processing; individual die can be stud bumped as easily as they can be wire bonded. -75 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Stud bonding (http: //www. flipchips. com/tutorial 03. html) • • • -76 - ADVANTAGES AND LIMITATIONS Gold stud bump flip chip offers several advantages. The bumping equipment, a wire bonder or dedicated stud bumper, is widely available and well characterized. Since stud bumps are formed by wire bonders, they can be placed anywhere a wire bond might be placed. They can easily achieve pitches of less than 100 microns and be placed on pads of less than 75 microns. Since stud bumping can be done on a wire bonder, it does not require wafers or under-bump metallization (UBM). Single, off-the-shelf die can be bumped and flipped without pre-processing. This makes stud bump flip chip fast, efficient, and flexible for product development, prototyping and low to medium volume production, while easy to scale up to high volume wafer-based production with automated equipment. Because stud bumping is a serial process, the bumping time required increases with the number of bumps. However, high speed equipment now can place as many as 12 bumps per second. Stud bump assemblies demand more precise die placement equipment and are less tolerant of placement errors than self-aligning solder assemblies. Each of the stud bump assembly processes has advantages and limitations that suit it for specific applications. Stud bump assembly has been successful in a wide range of applications. Selecting the most appropriate assembly process depends on the application, the die size and number of bumps, the substrate, equipment availability, cost, and other considerations. Choosing the proper process is the best assurance of success. NSS-MIC conference, Orlando (October 2009) R. Ballabriga

Pile-up rejector block (de Geronimo) -77 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

-78 - NSS-MIC conference, Orlando (October 2009) R. Ballabriga

3af6d8f8a320c05034404775ea3dcca6.ppt