lection-parallel-computers.ppt

- Количество слайдов: 16

Новосибирский государственный университет Факультет информационных технологий Кафедра Параллельных вычислений АРХИТЕКТУРА ПАРАЛЛЕЛЬНЫХ КОМПЬЮТЕРОВ Калгин Константин Викторович kalgin@ssd. sscc. ru

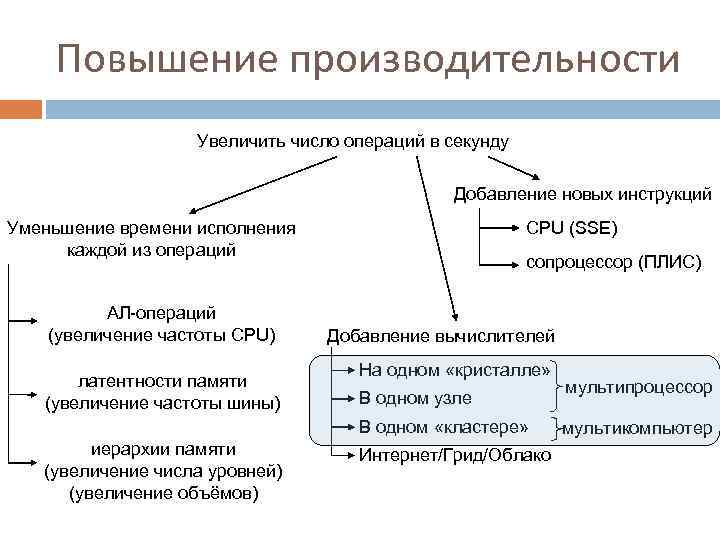

Повышение производительности Увеличить число операций в секунду Добавление новых инструкций Уменьшение времени исполнения каждой из операций АЛ-операций (увеличение частоты CPU) латентности памяти (увеличение частоты шины) CPU (SSE) сопроцессор (ПЛИС) Добавление вычислителей На одном «кристалле» В одном узле В одном «кластере» иерархии памяти (увеличение числа уровней) (увеличение объёмов) Интернет/Грид/Облако мультипроцессор мультикомпьютер

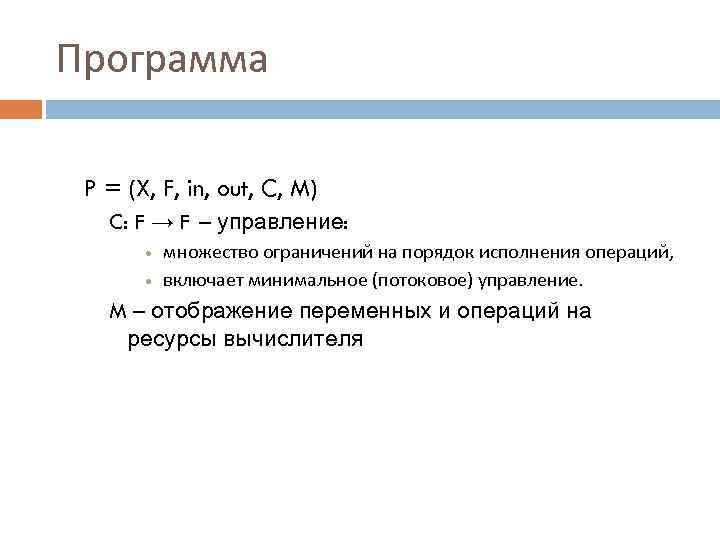

Программа P = (X, F, in, out, C, M) C: F → F – управление: • • множество ограничений на порядок исполнения операций, включает минимальное (потоковое) управление. M – отображение переменных и операций на ресурсы вычислителя

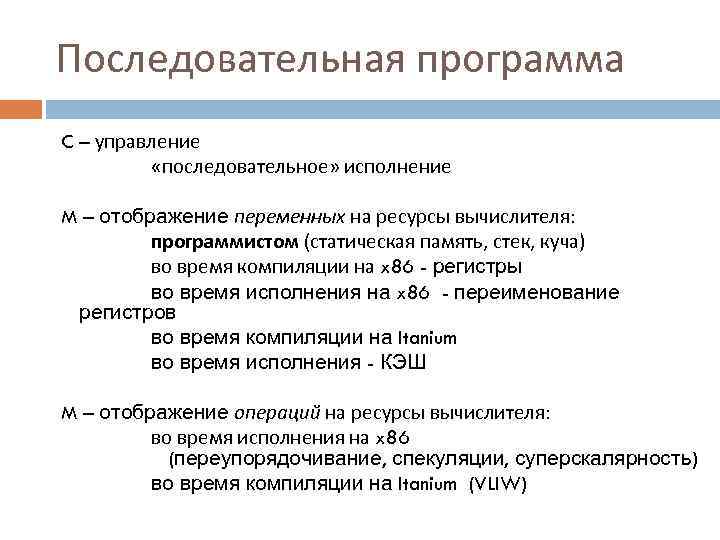

Последовательная программа C – управление «последовательное» исполнение M – отображение переменных на ресурсы вычислителя: программистом (статическая память, стек, куча) во время компиляции на x 86 - регистры во время исполнения на x 86 - переименование регистров во время компиляции на Itanium во время исполнения - КЭШ M – отображение операций на ресурсы вычислителя: во время исполнения на x 86 (переупорядочивание, спекуляции, суперскалярность) во время компиляции на Itanium (VLIW)

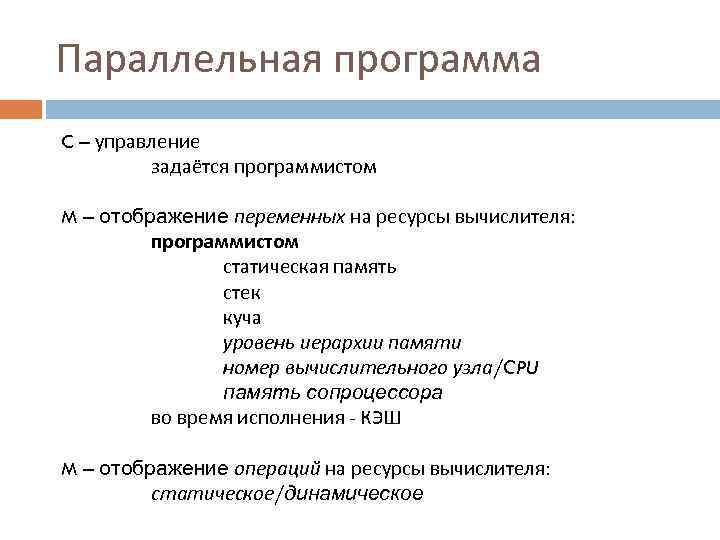

Параллельная программа C – управление задаётся программистом M – отображение переменных на ресурсы вычислителя: программистом статическая память стек куча уровень иерархии памяти номер вычислительного узла/CPU память сопроцессора во время исполнения - КЭШ M – отображение операций на ресурсы вычислителя: статическое/динамическое

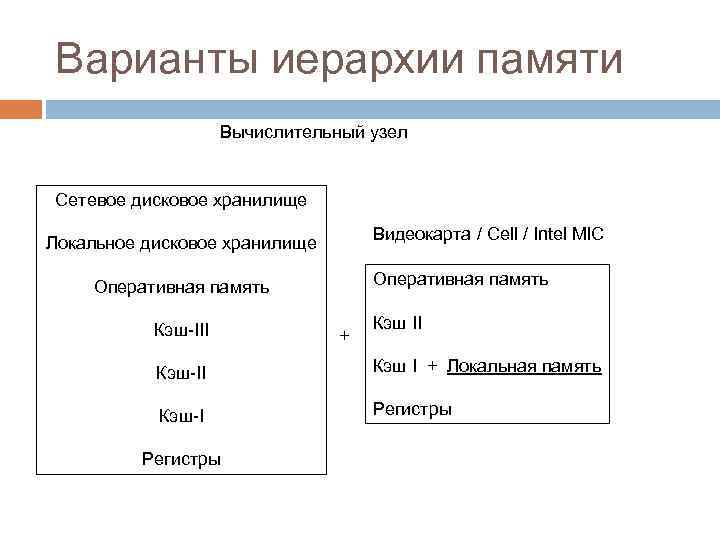

Варианты иерархии памяти Вычислительный узел Сетевое дисковое хранилище Видеокарта / Cell / Intel MIC Локальное дисковое хранилище Оперативная память Кэш-III + Кэш II Кэш-II Кэш I + Локальная память Кэш-I Регистры

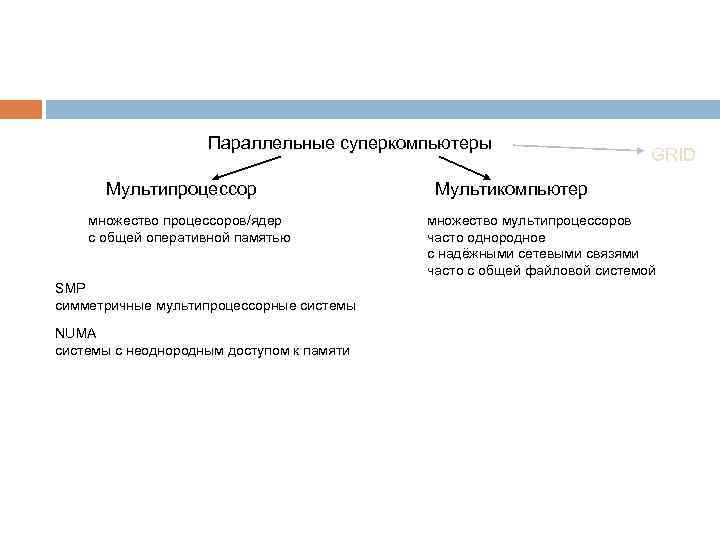

Параллельные суперкомпьютеры Мультипроцессор множество процессоров/ядер с общей оперативной памятью SMP симметричные мультипроцессорные системы NUMA системы с неоднородным доступом к памяти GRID Мультикомпьютер множество мультипроцессоров часто однородное с надёжными сетевыми связями часто с общей файловой системой

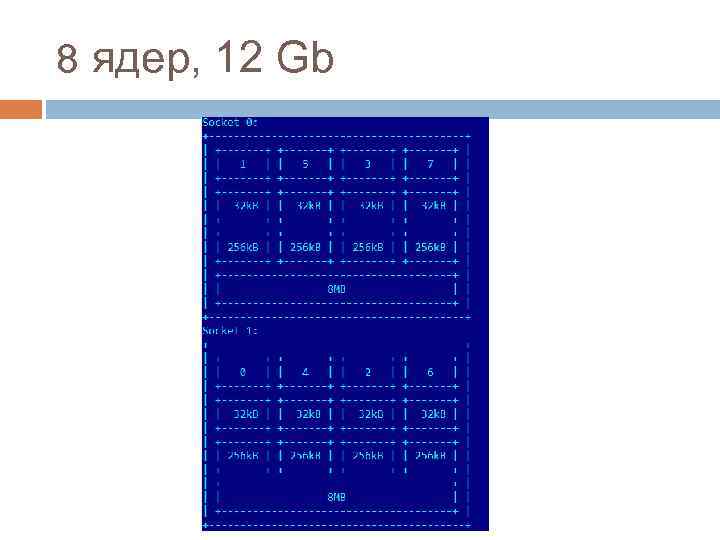

8 ядер, 12 Gb

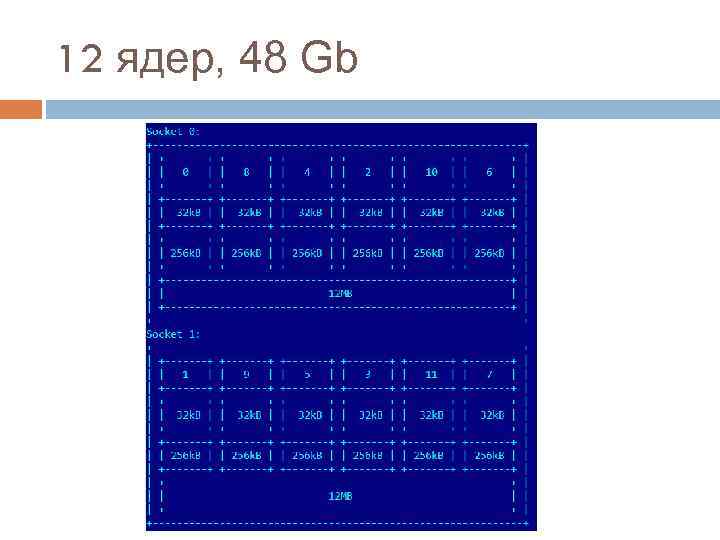

12 ядер, 48 Gb

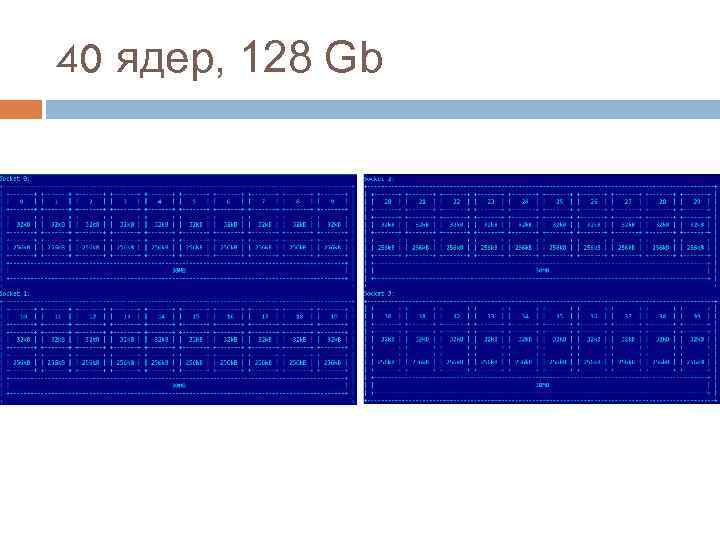

40 ядер, 128 Gb

lection-parallel-computers.ppt