e53334da94fd9766f75182cf2741bed7.ppt

- Количество слайдов: 12

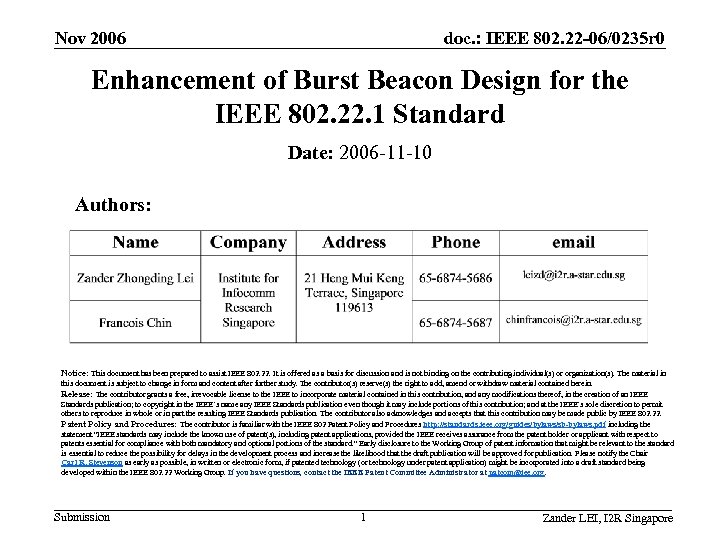

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Enhancement of Burst Beacon Design for the IEEE 802. 22. 1 Standard Date: 2006 -11 -10 Authors: Notice: This document has been prepared to assist IEEE 802. 22. It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or withdraw material contained herein. Release: The contributor grants a free, irrevocable license to the IEEE to incorporate material contained in this contribution, and any modifications thereof, in the creation of an IEEE Standards publication; to copyright in the IEEE’s name any IEEE Standards publication even though it may include portions of this contribution; and at the IEEE’s sole discretion to permit others to reproduce in whole or in part the resulting IEEE Standards publication. The contributor also acknowledges and accepts that this contribution may be made public by IEEE 802. 22. Patent Policy and Procedures: The contributor is familiar with the IEEE 802 Patent Policy and Procedures http: //standards. ieee. org/guides/bylaws/sb-bylaws. pdf including the statement "IEEE standards may include the known use of patent(s), including patent applications, provided the IEEE receives assurance from the patent holder or applicant with respect to patents essential for compliance with both mandatory and optional portions of the standard. " Early disclosure to the Working Group of patent information that might be relevant to the standard is essential to reduce the possibility for delays in the development process and increase the likelihood that the draft publication will be approved for publication. Please notify the Chair Carl R. Stevenson as early as possible, in written or electronic form, if patented technology (or technology under patent application) might be incorporated into a draft standard being developed within the IEEE 802. 22 Working Group. If you have questions, contact the IEEE Patent Committee Administrator at patcom@iee. org. Submission 1 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Enhancement of Burst Beacon Design for the IEEE 802. 22. 1 Standard Date: 2006 -11 -10 Authors: Notice: This document has been prepared to assist IEEE 802. 22. It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or withdraw material contained herein. Release: The contributor grants a free, irrevocable license to the IEEE to incorporate material contained in this contribution, and any modifications thereof, in the creation of an IEEE Standards publication; to copyright in the IEEE’s name any IEEE Standards publication even though it may include portions of this contribution; and at the IEEE’s sole discretion to permit others to reproduce in whole or in part the resulting IEEE Standards publication. The contributor also acknowledges and accepts that this contribution may be made public by IEEE 802. 22. Patent Policy and Procedures: The contributor is familiar with the IEEE 802 Patent Policy and Procedures http: //standards. ieee. org/guides/bylaws/sb-bylaws. pdf including the statement "IEEE standards may include the known use of patent(s), including patent applications, provided the IEEE receives assurance from the patent holder or applicant with respect to patents essential for compliance with both mandatory and optional portions of the standard. " Early disclosure to the Working Group of patent information that might be relevant to the standard is essential to reduce the possibility for delays in the development process and increase the likelihood that the draft publication will be approved for publication. Please notify the Chair Carl R. Stevenson as early as possible, in written or electronic form, if patented technology (or technology under patent application) might be incorporated into a draft standard being developed within the IEEE 802. 22 Working Group. If you have questions, contact the IEEE Patent Committee Administrator at patcom@iee. org. Submission 1 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Abstract We propose an enhanced burst beacon transmission for the IEEE 802. 22. 1 Enhanced Detection of Part 74 Devices standard. Submission 2 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Abstract We propose an enhanced burst beacon transmission for the IEEE 802. 22. 1 Enhanced Detection of Part 74 Devices standard. Submission 2 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Background • IEEE 802. 22. 1 Standard – Enhance harmful interference protection for low-power licensed as secondary devices operating in TV Broadcast Bands (under Title 47 of the Code of Federal Regulations (CFR) in the USA and equivalent devices in other regulatory domains) – Target technologies for signalling the presence of low-power licensed devices that different from the sensing and cognitive radio technologies that are being considered elsewhere in 802. 22 • Status – Motorola’s proposal has been selected as baseline in Sept. meeting – Samsung introduced I/Q transmission Submission 3 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Background • IEEE 802. 22. 1 Standard – Enhance harmful interference protection for low-power licensed as secondary devices operating in TV Broadcast Bands (under Title 47 of the Code of Federal Regulations (CFR) in the USA and equivalent devices in other regulatory domains) – Target technologies for signalling the presence of low-power licensed devices that different from the sensing and cognitive radio technologies that are being considered elsewhere in 802. 22 • Status – Motorola’s proposal has been selected as baseline in Sept. meeting – Samsung introduced I/Q transmission Submission 3 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Baseline PHY • Beacon design is critical in the 802. 22. 1 – Sending 50 bytes in 5 ms requires a data rate of 80 kb/s, or a bit length of 12. 5 ms. – Available spectrum bandwidth (< 200 k. Hz) – Required sensitivity (as good as possible) – Path loss aside, a path of even 10 km has a propagation delay of 33 ms, so multipath is a significant issue. – Multipath mitigation methods, such as equalization and OFDM, add undesirable complexity Submission 4 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Baseline PHY • Beacon design is critical in the 802. 22. 1 – Sending 50 bytes in 5 ms requires a data rate of 80 kb/s, or a bit length of 12. 5 ms. – Available spectrum bandwidth (< 200 k. Hz) – Required sensitivity (as good as possible) – Path loss aside, a path of even 10 km has a propagation delay of 33 ms, so multipath is a significant issue. – Multipath mitigation methods, such as equalization and OFDM, add undesirable complexity Submission 4 Zander LEI, I 2 R Singapore

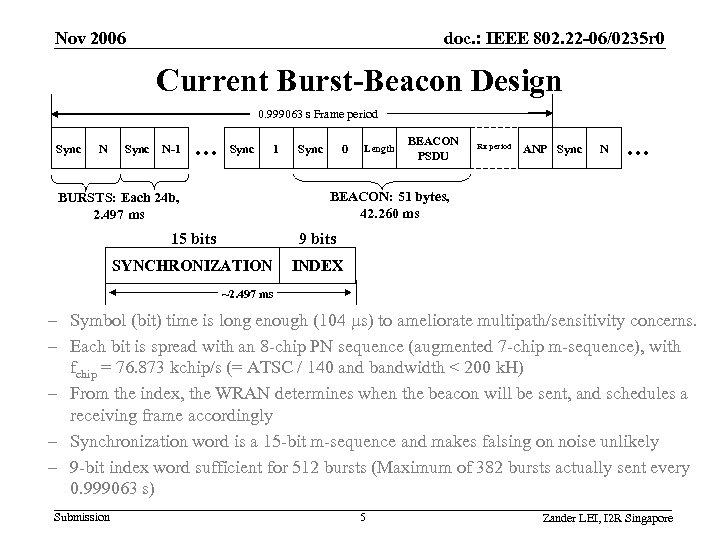

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Current Burst-Beacon Design 0. 999063 s Frame period Sync N-1 … Sync 1 Sync 0 Length BEACON PSDU Rx period ANP Sync N … BEACON: 51 bytes, 42. 260 ms BURSTS: Each 24 b, 2. 497 ms 15 bits 9 bits SYNCHRONIZATION INDEX ~2. 497 ms – Symbol (bit) time is long enough (104 ms) to ameliorate multipath/sensitivity concerns. – Each bit is spread with an 8 -chip PN sequence (augmented 7 -chip m-sequence), with fchip = 76. 873 kchip/s (= ATSC / 140 and bandwidth < 200 k. H) – From the index, the WRAN determines when the beacon will be sent, and schedules a receiving frame accordingly – Synchronization word is a 15 -bit m-sequence and makes falsing on noise unlikely – 9 -bit index word sufficient for 512 bursts (Maximum of 382 bursts actually sent every 0. 999063 s) Submission 5 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Current Burst-Beacon Design 0. 999063 s Frame period Sync N-1 … Sync 1 Sync 0 Length BEACON PSDU Rx period ANP Sync N … BEACON: 51 bytes, 42. 260 ms BURSTS: Each 24 b, 2. 497 ms 15 bits 9 bits SYNCHRONIZATION INDEX ~2. 497 ms – Symbol (bit) time is long enough (104 ms) to ameliorate multipath/sensitivity concerns. – Each bit is spread with an 8 -chip PN sequence (augmented 7 -chip m-sequence), with fchip = 76. 873 kchip/s (= ATSC / 140 and bandwidth < 200 k. H) – From the index, the WRAN determines when the beacon will be sent, and schedules a receiving frame accordingly – Synchronization word is a 15 -bit m-sequence and makes falsing on noise unlikely – 9 -bit index word sufficient for 512 bursts (Maximum of 382 bursts actually sent every 0. 999063 s) Submission 5 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Merits and Problems • Merits J Fairly simple design w/ low complexity demodulator J Fast burst detection w/ index facilitating scheduling J… • Index / Beacon could be vulnerable – Less protection • Bits are protected only by 8 chip spreading – Unbalanced error protection • Sync word is further protected by 15 -bit sequence to minimize miss alarm rate • Get synced but w/ wrong index or beacon errors • Objective √ Improve bit protection performance and keep most (if not all) merits Submission 6 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Merits and Problems • Merits J Fairly simple design w/ low complexity demodulator J Fast burst detection w/ index facilitating scheduling J… • Index / Beacon could be vulnerable – Less protection • Bits are protected only by 8 chip spreading – Unbalanced error protection • Sync word is further protected by 15 -bit sequence to minimize miss alarm rate • Get synced but w/ wrong index or beacon errors • Objective √ Improve bit protection performance and keep most (if not all) merits Submission 6 Zander LEI, I 2 R Singapore

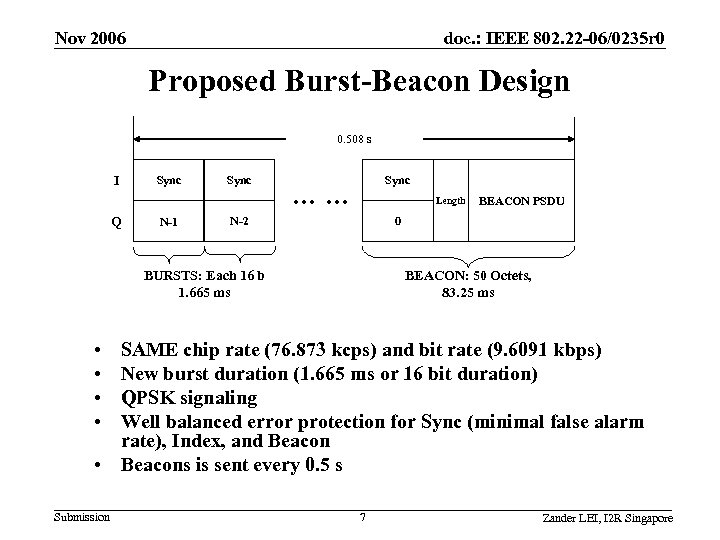

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Proposed Burst-Beacon Design 0. 508 s I Q Sync N-1 Sync …… Length BEACON PSDU 0 N-2 BURSTS: Each 16 b 1. 665 ms BEACON: 50 Octets, 83. 25 ms • • SAME chip rate (76. 873 kcps) and bit rate (9. 6091 kbps) New burst duration (1. 665 ms or 16 bit duration) QPSK signaling Well balanced error protection for Sync (minimal false alarm rate), Index, and Beacon • Beacons is sent every 0. 5 s Submission 7 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Proposed Burst-Beacon Design 0. 508 s I Q Sync N-1 Sync …… Length BEACON PSDU 0 N-2 BURSTS: Each 16 b 1. 665 ms BEACON: 50 Octets, 83. 25 ms • • SAME chip rate (76. 873 kcps) and bit rate (9. 6091 kbps) New burst duration (1. 665 ms or 16 bit duration) QPSK signaling Well balanced error protection for Sync (minimal false alarm rate), Index, and Beacon • Beacons is sent every 0. 5 s Submission 7 Zander LEI, I 2 R Singapore

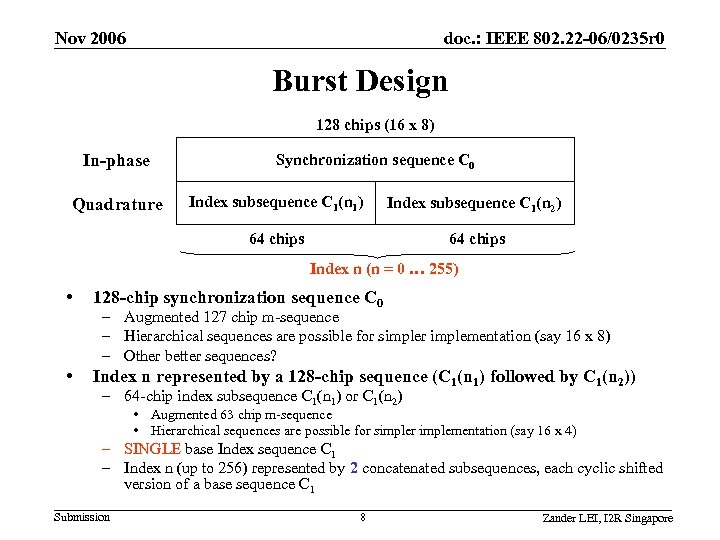

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Burst Design 128 chips (16 x 8) In-phase Synchronization sequence C 0 Index subsequence C 1(n 1) Index subsequence C 1(n 2) 64 chips Quadrature 64 chips Index n (n = 0 … 255) • 128 -chip synchronization sequence C 0 – Augmented 127 chip m-sequence – Hierarchical sequences are possible for simpler implementation (say 16 x 8) – Other better sequences? • Index n represented by a 128 -chip sequence (C 1(n 1) followed by C 1(n 2)) – 64 -chip index subsequence C 1(n 1) or C 1(n 2) • Augmented 63 chip m-sequence • Hierarchical sequences are possible for simpler implementation (say 16 x 4) – SINGLE base Index sequence C 1 – Index n (up to 256) represented by 2 concatenated subsequences, each cyclic shifted version of a base sequence C 1 Submission 8 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Burst Design 128 chips (16 x 8) In-phase Synchronization sequence C 0 Index subsequence C 1(n 1) Index subsequence C 1(n 2) 64 chips Quadrature 64 chips Index n (n = 0 … 255) • 128 -chip synchronization sequence C 0 – Augmented 127 chip m-sequence – Hierarchical sequences are possible for simpler implementation (say 16 x 8) – Other better sequences? • Index n represented by a 128 -chip sequence (C 1(n 1) followed by C 1(n 2)) – 64 -chip index subsequence C 1(n 1) or C 1(n 2) • Augmented 63 chip m-sequence • Hierarchical sequences are possible for simpler implementation (say 16 x 4) – SINGLE base Index sequence C 1 – Index n (up to 256) represented by 2 concatenated subsequences, each cyclic shifted version of a base sequence C 1 Submission 8 Zander LEI, I 2 R Singapore

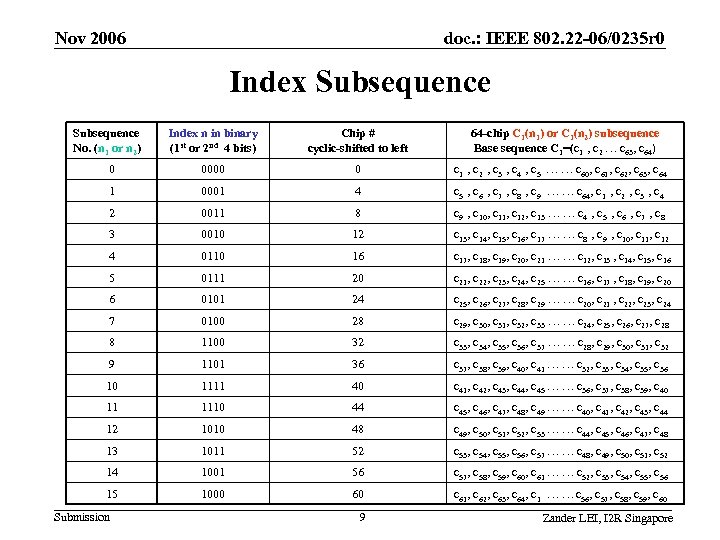

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Index Subsequence No. (n 1 or n 2) Index n in binary (1 st or 2 nd 4 bits) Chip # cyclic-shifted to left 0 0000 0 c 1 , c 2 , c 3 , c 4 , c 5 … … c 60, c 61, c 62, c 63, c 64 1 0001 4 c 5 , c 6 , c 7 , c 8 , c 9 … … c 64, c 1 , c 2 , c 3 , c 4 2 0011 8 c 9 , c 10, c 11, c 12, c 13 … … c 4 , c 5 , c 6 , c 7 , c 8 3 0010 12 c 13, c 14, c 15, c 16, c 17 … … c 8 , c 9 , c 10, c 11, c 12 4 0110 16 c 17, c 18, c 19, c 20, c 21 … … c 12, c 13 , c 14, c 15, c 16 5 0111 20 c 21, c 22, c 23, c 24, c 25 … … c 16, c 17 , c 18, c 19, c 20 6 0101 24 c 25, c 26, c 27, c 28, c 29 … … c 20, c 21 , c 22, c 23, c 24 7 0100 28 c 29, c 30, c 31, c 32, c 33 … … c 24, c 25, c 26, c 27, c 28 8 1100 32 c 33, c 34, c 35, c 36, c 37 … … c 28, c 29, c 30, c 31, c 32 9 1101 36 c 37, c 38, c 39, c 40, c 41 … … c 32, c 33, c 34, c 35, c 36 10 1111 40 c 41, c 42, c 43, c 44, c 45 … … c 36, c 37, c 38, c 39, c 40 11 1110 44 c 45, c 46, c 47, c 48, c 49 … … c 40, c 41, c 42, c 43, c 44 12 1010 48 c 49, c 50, c 51, c 52, c 53 … … c 44, c 45, c 46, c 47, c 48 13 1011 52 c 53, c 54, c 55, c 56, c 57 … … c 48, c 49, c 50, c 51, c 52 14 1001 56 c 57, c 58, c 59, c 60, c 61 … … c 52, c 53, c 54, c 55, c 56 15 1000 60 c 61, c 62, c 63, c 64, c 1 … … c 56, c 57, c 58, c 59, c 60 Submission 9 64 -chip C 1(n 1) or C 1(n 2) subsequence Base sequence C 1=(c 1 , c 2 … c 63, c 64) Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Index Subsequence No. (n 1 or n 2) Index n in binary (1 st or 2 nd 4 bits) Chip # cyclic-shifted to left 0 0000 0 c 1 , c 2 , c 3 , c 4 , c 5 … … c 60, c 61, c 62, c 63, c 64 1 0001 4 c 5 , c 6 , c 7 , c 8 , c 9 … … c 64, c 1 , c 2 , c 3 , c 4 2 0011 8 c 9 , c 10, c 11, c 12, c 13 … … c 4 , c 5 , c 6 , c 7 , c 8 3 0010 12 c 13, c 14, c 15, c 16, c 17 … … c 8 , c 9 , c 10, c 11, c 12 4 0110 16 c 17, c 18, c 19, c 20, c 21 … … c 12, c 13 , c 14, c 15, c 16 5 0111 20 c 21, c 22, c 23, c 24, c 25 … … c 16, c 17 , c 18, c 19, c 20 6 0101 24 c 25, c 26, c 27, c 28, c 29 … … c 20, c 21 , c 22, c 23, c 24 7 0100 28 c 29, c 30, c 31, c 32, c 33 … … c 24, c 25, c 26, c 27, c 28 8 1100 32 c 33, c 34, c 35, c 36, c 37 … … c 28, c 29, c 30, c 31, c 32 9 1101 36 c 37, c 38, c 39, c 40, c 41 … … c 32, c 33, c 34, c 35, c 36 10 1111 40 c 41, c 42, c 43, c 44, c 45 … … c 36, c 37, c 38, c 39, c 40 11 1110 44 c 45, c 46, c 47, c 48, c 49 … … c 40, c 41, c 42, c 43, c 44 12 1010 48 c 49, c 50, c 51, c 52, c 53 … … c 44, c 45, c 46, c 47, c 48 13 1011 52 c 53, c 54, c 55, c 56, c 57 … … c 48, c 49, c 50, c 51, c 52 14 1001 56 c 57, c 58, c 59, c 60, c 61 … … c 52, c 53, c 54, c 55, c 56 15 1000 60 c 61, c 62, c 63, c 64, c 1 … … c 56, c 57, c 58, c 59, c 60 Submission 9 64 -chip C 1(n 1) or C 1(n 2) subsequence Base sequence C 1=(c 1 , c 2 … c 63, c 64) Zander LEI, I 2 R Singapore

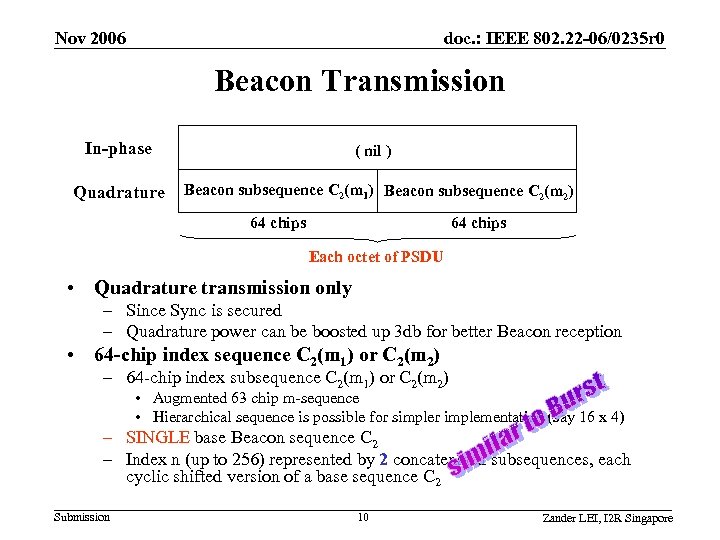

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Beacon Transmission In-phase Quadrature ( nil ) Beacon subsequence C 2(m 1) Beacon subsequence C 2(m 2) 64 chips Each octet of PSDU • Quadrature transmission only – Since Sync is secured – Quadrature power can be boosted up 3 db for better Beacon reception • 64 -chip index sequence C 2(m 1) or C 2(m 2) – 64 -chip index subsequence C 2(m 1) or C 2(m 2) • Augmented 63 chip m-sequence • Hierarchical sequence is possible for simpler implementation (say 16 x 4) – SINGLE base Beacon sequence C 2 – Index n (up to 256) represented by 2 concatenated subsequences, each cyclic shifted version of a base sequence C 2 Submission 10 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Beacon Transmission In-phase Quadrature ( nil ) Beacon subsequence C 2(m 1) Beacon subsequence C 2(m 2) 64 chips Each octet of PSDU • Quadrature transmission only – Since Sync is secured – Quadrature power can be boosted up 3 db for better Beacon reception • 64 -chip index sequence C 2(m 1) or C 2(m 2) – 64 -chip index subsequence C 2(m 1) or C 2(m 2) • Augmented 63 chip m-sequence • Hierarchical sequence is possible for simpler implementation (say 16 x 4) – SINGLE base Beacon sequence C 2 – Index n (up to 256) represented by 2 concatenated subsequences, each cyclic shifted version of a base sequence C 2 Submission 10 Zander LEI, I 2 R Singapore

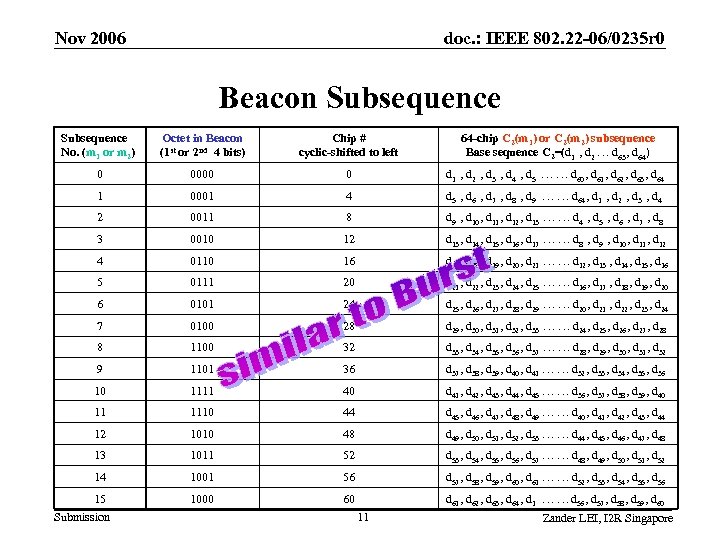

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Beacon Subsequence No. (m 1 or m 2) Octet in Beacon (1 st or 2 nd 4 bits) Chip # cyclic-shifted to left 64 -chip C 2(m 1) or C 2(m 2) subsequence Base sequence C 2=(d 1 , d 2 … d 63, d 64) 0 0000 0 d 1 , d 2 , d 3 , d 4 , d 5 … … d 60, d 61, d 62, d 63, d 64 1 0001 4 d 5 , d 6 , d 7 , d 8 , d 9 … … d 64, d 1 , d 2 , d 3 , d 4 2 0011 8 d 9 , d 10, d 11, d 12, d 13 … … d 4 , d 5 , d 6 , d 7 , d 8 3 0010 12 d 13, d 14, d 15, d 16, d 17 … … d 8 , d 9 , d 10, d 11, d 12 4 0110 16 d 17, d 18, d 19, d 20, d 21 … … d 12, d 13 , d 14, d 15, d 16 5 0111 20 d 21, d 22, d 23, d 24, d 25 … … d 16, d 17 , d 18, d 19, d 20 6 0101 24 d 25, d 26, d 27, d 28, d 29 … … d 20, d 21 , d 22, d 23, d 24 7 0100 28 d 29, d 30, d 31, d 32, d 33 … … d 24, d 25, d 26, d 27, d 28 8 1100 32 d 33, d 34, d 35, d 36, d 37 … … d 28, d 29, d 30, d 31, d 32 9 1101 36 d 37, d 38, d 39, d 40, d 41 … … d 32, d 33, d 34, d 35, d 36 10 1111 40 d 41, d 42, d 43, d 44, d 45 … … d 36, d 37, d 38, d 39, d 40 11 1110 44 d 45, d 46, d 47, d 48, d 49 … … d 40, d 41, d 42, d 43, d 44 12 1010 48 d 49, d 50, d 51, d 52, d 53 … … d 44, d 45, d 46, d 47, d 48 13 1011 52 d 53, d 54, d 55, d 56, d 57 … … d 48, d 49, d 50, d 51, d 52 14 1001 56 d 57, d 58, d 59, d 60, d 61 … … d 52, d 53, d 54, d 55, d 56 15 1000 60 d 61, d 62, d 63, d 64, d 1 … … d 56, d 57, d 58, d 59, d 60 Submission 11 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Beacon Subsequence No. (m 1 or m 2) Octet in Beacon (1 st or 2 nd 4 bits) Chip # cyclic-shifted to left 64 -chip C 2(m 1) or C 2(m 2) subsequence Base sequence C 2=(d 1 , d 2 … d 63, d 64) 0 0000 0 d 1 , d 2 , d 3 , d 4 , d 5 … … d 60, d 61, d 62, d 63, d 64 1 0001 4 d 5 , d 6 , d 7 , d 8 , d 9 … … d 64, d 1 , d 2 , d 3 , d 4 2 0011 8 d 9 , d 10, d 11, d 12, d 13 … … d 4 , d 5 , d 6 , d 7 , d 8 3 0010 12 d 13, d 14, d 15, d 16, d 17 … … d 8 , d 9 , d 10, d 11, d 12 4 0110 16 d 17, d 18, d 19, d 20, d 21 … … d 12, d 13 , d 14, d 15, d 16 5 0111 20 d 21, d 22, d 23, d 24, d 25 … … d 16, d 17 , d 18, d 19, d 20 6 0101 24 d 25, d 26, d 27, d 28, d 29 … … d 20, d 21 , d 22, d 23, d 24 7 0100 28 d 29, d 30, d 31, d 32, d 33 … … d 24, d 25, d 26, d 27, d 28 8 1100 32 d 33, d 34, d 35, d 36, d 37 … … d 28, d 29, d 30, d 31, d 32 9 1101 36 d 37, d 38, d 39, d 40, d 41 … … d 32, d 33, d 34, d 35, d 36 10 1111 40 d 41, d 42, d 43, d 44, d 45 … … d 36, d 37, d 38, d 39, d 40 11 1110 44 d 45, d 46, d 47, d 48, d 49 … … d 40, d 41, d 42, d 43, d 44 12 1010 48 d 49, d 50, d 51, d 52, d 53 … … d 44, d 45, d 46, d 47, d 48 13 1011 52 d 53, d 54, d 55, d 56, d 57 … … d 48, d 49, d 50, d 51, d 52 14 1001 56 d 57, d 58, d 59, d 60, d 61 … … d 52, d 53, d 54, d 55, d 56 15 1000 60 d 61, d 62, d 63, d 64, d 1 … … d 56, d 57, d 58, d 59, d 60 Submission 11 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Summary • Enhancement for Burst Beacon Transmission is proposed – QPSK signaling • In phase: One PN sequence for Sync • Quadrature: One 64 -chip base subsequence each for Index and Beacon – Balanced and better error protection • Sync word: 128 -chip sequence • Index / Beacon octet: 128 -chip sequence – Comprises of two 64 -chip subsequences – Each subsequence is cyclic shifted version of base sequence – Low complexity implementation Submission 12 Zander LEI, I 2 R Singapore

Nov 2006 doc. : IEEE 802. 22 -06/0235 r 0 Summary • Enhancement for Burst Beacon Transmission is proposed – QPSK signaling • In phase: One PN sequence for Sync • Quadrature: One 64 -chip base subsequence each for Index and Beacon – Balanced and better error protection • Sync word: 128 -chip sequence • Index / Beacon octet: 128 -chip sequence – Comprises of two 64 -chip subsequences – Each subsequence is cyclic shifted version of base sequence – Low complexity implementation Submission 12 Zander LEI, I 2 R Singapore