0c22a7860c8ab8c0918202d27b2776ef.ppt

- Количество слайдов: 56

Нижегородский Государственный Университет им. Н. И. Лобачевского Оптимизация программ Программная оптимизация Зимняя школа ITLab-2010 1 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

Содержание § Введение § Некоторые особенности архитектуры IA-32 § Оптимизация основных алгоритмических конструкций (условия, циклы, множественный выбор) - различные приемы оптимизация расчетных участков: – – – 2 исключение повторяющихся вычислений встраивание функций замена операций (напр. , деление на умножение) развертка циклов выравнивание данных учет многоуровневости системы памяти (ОП, кэши, регистры) © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

1. Введение 3 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

1. Введение § Программная оптимизация вступает в дело, когда алгоритм выбран, реализован и отлажен. § Вспомним установки: – Выигрыш должен быть существенным. – Рассматриваем оптимизацию на ЯП C/C++. – C++ как правило вредит программной оптимизации. – Приветствуем понятность кода после оптимизации. § Без понимания принципов работы архитектуры программная оптимизация сильно затруднена. 4 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 5 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Немного истории § Направления разработки аппаратуры: – рост производительности; – миниатюризация. § 1978 г. Intel 8086 – 8 МГц, 29 000 транзисторов. § Intel Pentium – первый инструкции за такт. процессор, исполняющий >1 § Intel Pentium Pro – out-of-order execution. § 2000 г. Intel Pentium 4 – 1, 5 ГГц, 42 000 транзисторов. § Есть физические пределы, которые вызывают развитие не только экстенсивных, но и интенсивных технологий повышения производительности. 6 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Механизмы, приводящие к ускорению § 2 ключевых механизма: – уменьшение латентности – времени от начала операции до ее завершения; (как команд, так и памяти) – увеличение пропускной способности – количества данных, которое может быть передано по шине за единицу времени. § Латентность операций уменьшается реализации «тяжелых» операций. за счет аппаратной § Латентность памяти уменьшается за счет многоуровневой организации памяти (регистры, кэши, ОЗУ, диск). § Пропускная способность повышается за счет конвейеризации и репликации. 7 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

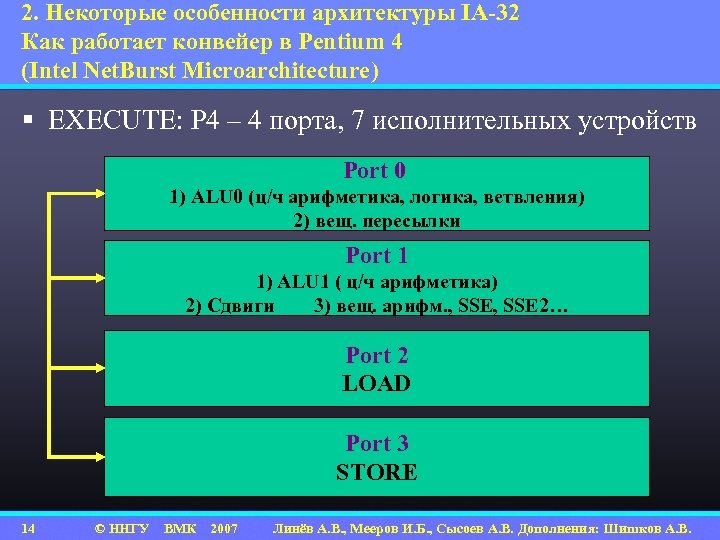

2. Некоторые особенности архитектуры IA-32 Конвейеры… § Конвейеризация – разбиение процесса выполнения инструкции на несколько стадий с целью их выполнения в едином потоке. § Конвейер Pentium 4 – 20 стадий (Prescott – 31). § Конвейер Core 2 Duo – 14 стадий. § 4 типа стадий: – FETCH (выборка команд) – DECODE (декодирование – преобразование в набор элементарных операций u. Ops) – EXECUTE (выполнение) – WRITE (завершение). Иногда применяется термин RETIREMENT 8 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Конвейеры 4 стадии, нет конвейера 4 стадии, конвейер Картинки взяты с сайта http: //arstechnica. com/articles/paedia/cpu 9 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

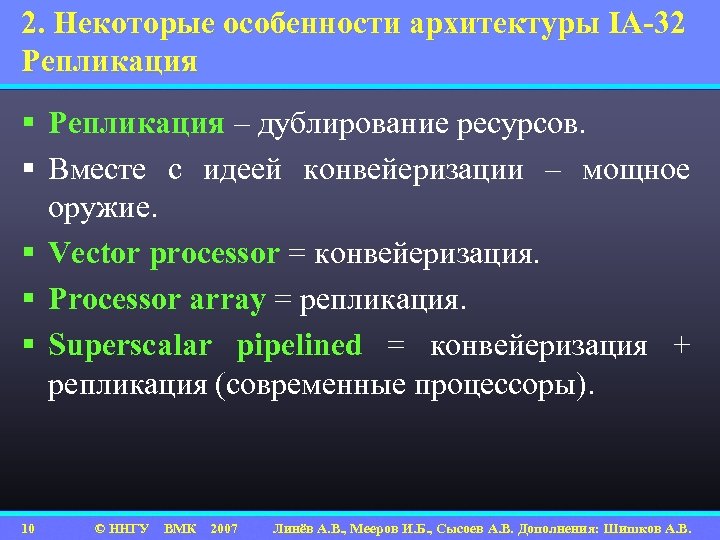

2. Некоторые особенности архитектуры IA-32 Репликация § Репликация – дублирование ресурсов. § Вместе с идеей конвейеризации – мощное оружие. § Vector processor = конвейеризация. § Processor array = репликация. § Superscalar pipelined = конвейеризация + репликация (современные процессоры). 10 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Репликация + конвейеризация Картинка взята с сайта http: //arstechnica. com/articles/paedia/cpu 11 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

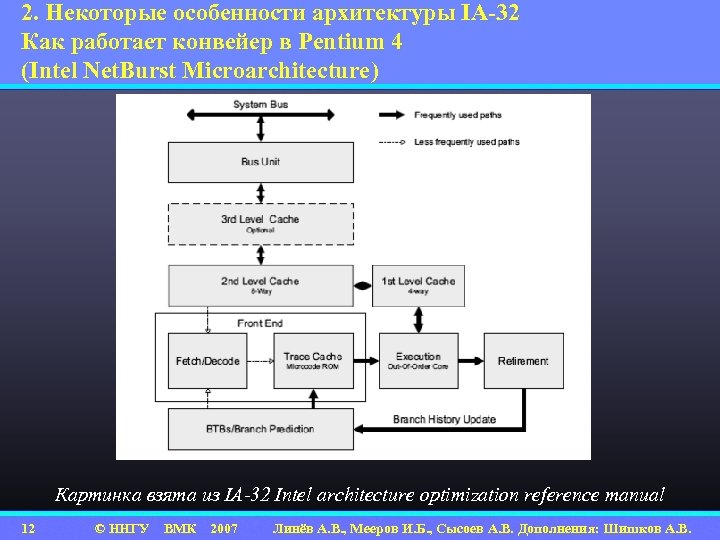

2. Некоторые особенности архитектуры IA-32 Как работает конвейер в Pentium 4 (Intel Net. Burst Microarchitecture) Картинка взята из IA-32 Intel architecture optimization reference manual 12 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Как работает конвейер в Pentium 4 (Intel Net. Burst Microarchitecture) § Front-end (FETCH+DECODE): – FETCH инструкции из памяти – DECODE в программном порядке (1 инстр. = 1 -4 u. Ops) – оправка исполнительному ядру § Execution (EXECUTE): – выборка декодированных инструкций (u. Ops) – исполнение в максимально быстром порядке (out-of-order) § Write (Retirement) – завершение выполнения инструкций – приведение в соответствие с порядком в программе 13 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

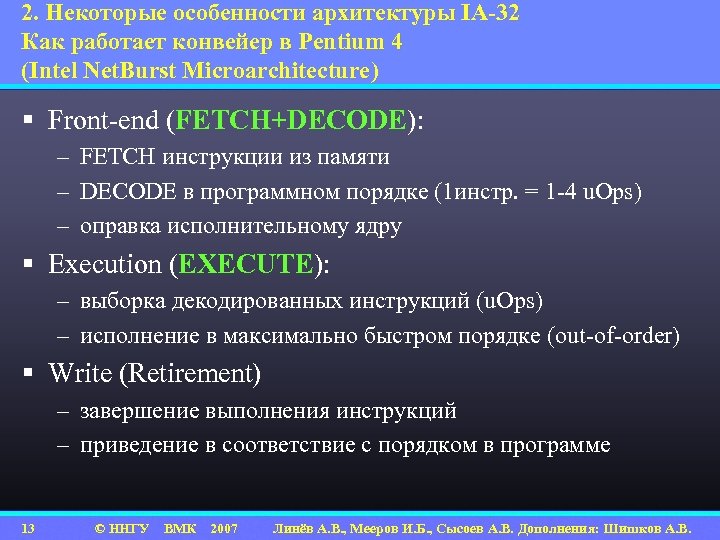

2. Некоторые особенности архитектуры IA-32 Как работает конвейер в Pentium 4 (Intel Net. Burst Microarchitecture) § EXECUTE: P 4 – 4 порта, 7 исполнительных устройств Port 0 1) ALU 0 (ц/ч арифметика, логика, ветвления) 2) вещ. пересылки Port 1 1) ALU 1 ( ц/ч арифметика) 2) Сдвиги 3) вещ. арифм. , SSE 2… Port 2 LOAD Port 3 STORE 14 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

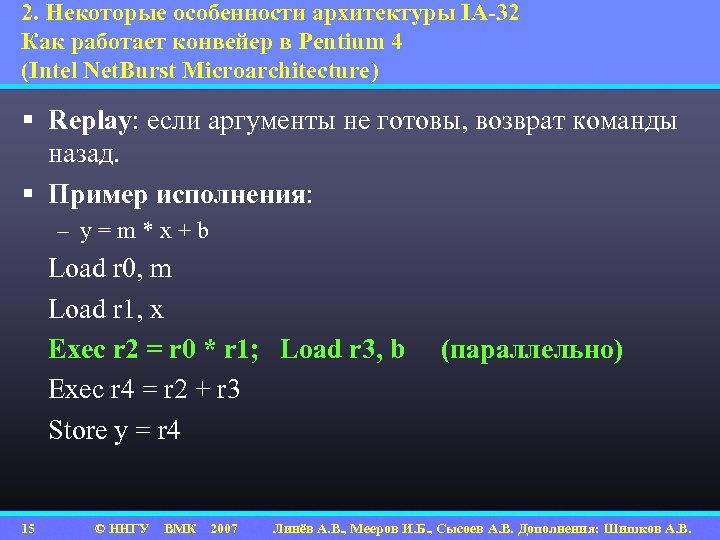

2. Некоторые особенности архитектуры IA-32 Как работает конвейер в Pentium 4 (Intel Net. Burst Microarchitecture) § Replay: если аргументы не готовы, возврат команды назад. § Пример исполнения: – y=m*x+b Load r 0, m Load r 1, x Exec r 2 = r 0 * r 1; Load r 3, b Exec r 4 = r 2 + r 3 Store y = r 4 15 © ННГУ ВМК 2007 (параллельно) Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Как работает конвейер в Pentium 4 § Нужно избегать простоев конвейера. § Из-за чего они возникают? 16 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Простои конвейера Вопрос: § Из-за чего возникает простой конвейера? Ответ: § Из-за ветвлений и зависимостей между инструкциями. 17 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Простои конвейера § Ветвление может привести к необходимости перезагрузки конвейера – очень большая потеря производительности. § Решение проблемы – механизм прогноза ветвлений. 18 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Прогноз ветвлений § Прогноз ветвлений специальную таблицу (branch – prediction) BTB (branch опирается target на buffer), содержащую 4096 записей (P 4) о предыдущих переходах с информацией о том, был переход или нет. § BP = Static prediction + Dynamic prediction. – Dynamic prediction – использует BTB. – Static prediction – прогнозирует, что ветвления вперед нет, а назад – есть. § В Pentium 4 вероятность правильного прогноза более 90%, а алгоритм – один из охраняемых секретов компании. 19 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

![2. Некоторые особенности архитектуры IA-32 Зависимости между инструкциями for (i=1; i<=100; i=i+1) { A[i] 2. Некоторые особенности архитектуры IA-32 Зависимости между инструкциями for (i=1; i<=100; i=i+1) { A[i]](https://present5.com/presentation/0c22a7860c8ab8c0918202d27b2776ef/image-20.jpg)

2. Некоторые особенности архитектуры IA-32 Зависимости между инструкциями for (i=1; i<=100; i=i+1) { A[i] = A[i] + B[i]; /* S 1 */ B[i+1] = C[i] + D[i]; } /* S 2 */ Исходный цикл: Итерация 1 S 1 A[1] = A[1] + B[1]; S 2 Итерация 99 B[2] = C[1] + D[1]; A[2] = A[2] + B[2]; . . . A[99] = A[99] + B[99]; B[3] = C[2] + D[2]; Межитерационная B[100] = C[99] + D[99]; зависимость A[1] = A[1] + B[1]; Модифицированный for (i=1; i<=99; i=i+1) { распараллеленный B[i+1] = C[i] + D[i]; A[i+1] = A[i+1] + B[i+1]; } цикл: (на одну итерацию меньше) B[101] = C[100] + D[100]; Итерация 1 Код инициализации цикла A[1] = A[1] + B[1]; A[2] = A[2] + B[2]; B[2] = C[1] + D[1]; B[3] = C[2] + D[2]; . . Итерация 98 A[99] = A[99] + B[99]; Не B[100] = C[99] + D[99]; межитерационная зависимость Итерация 100 A[100] = A[100] + B[100]; B[101] = C[100] + D[100]; Итерация 99 A[100] = A[100] + B[100]; B[101] = C[100] + D[100]; Код завершения цикла Пример взят из учебного курса Intel Studio по архитектуре ЭВМ 20 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

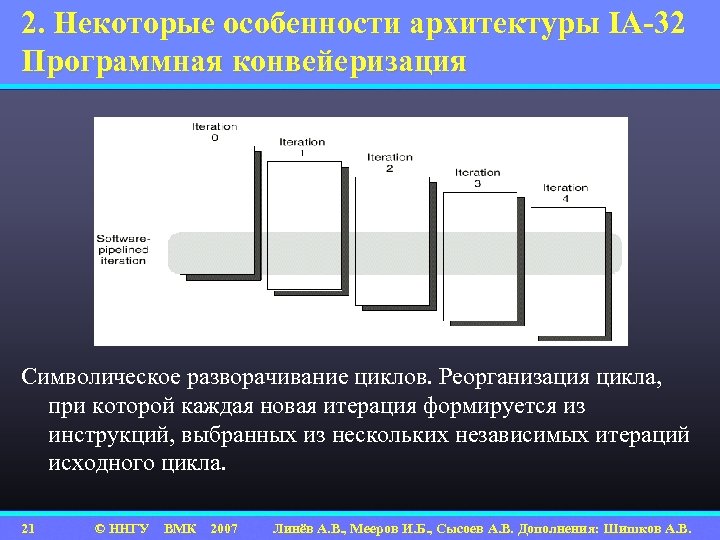

2. Некоторые особенности архитектуры IA-32 Программная конвейеризация Символическое разворачивание циклов. Реорганизация цикла, при которой каждая новая итерация формируется из инструкций, выбранных из нескольких независимых итераций исходного цикла. 21 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Команды SIMD § SIMD – Single instruction – multiple data – технология, которая подразумевает одновременное выполнение нескольких однотипных команд. § Специальные регистры и команды SIMD. § Наборы команд: – MMX (Pentium 166 MMX) – SSEIII (P 4 Prescott) – SSSEIII – SSEIV (Core 2 Duo (ядро Penryn и более новые )) 22 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

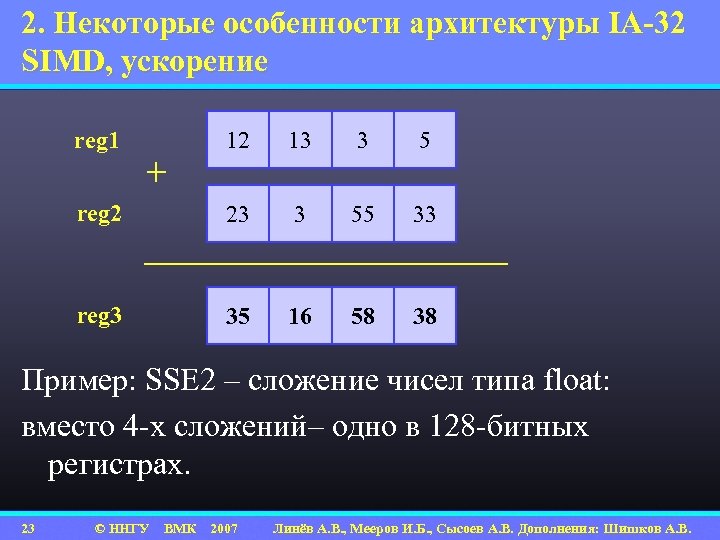

2. Некоторые особенности архитектуры IA-32 SIMD, ускорение reg 1 12 13 3 5 reg 2 23 3 55 33 reg 3 35 16 58 38 + Пример: SSE 2 – сложение чисел типа float: вместо 4 -х сложений– одно в 128 -битных регистрах. 23 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Команды SIMD § SSE 4: – ускорение компенсации движения в видеокодеках – обработка строк 8/16 битных символов – вычисление CRC 32 – вычисление popcnt (подсчет числа единичных бит) – увеличение производительности взаимодействия CPU c GPU 24 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Многоуровневая организация памяти § Кеш-память – специальный вид памяти, реализующий буферизацию данных в более быстрой памяти. § Уровни памяти в Intel Pentium 4: – регистры процессора – L 1 -кэш (инструкций, данных) – L 2 -кэш – L 3 -кэш (не везде) – ОЗУ – Жесткий диск 25 © ННГУ ВМК 2007 Дешевле Медленнее Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Характеристика кеш-памяти § Размер кеш-памяти << размера основной оперативной памяти. § Кеш-память состоит из линеек кеш-памяти (непрерывная область памяти фиксированного размера). Для архитектуры IA 32 типичный размер линейки кеш-памяти составляет 64 байта. § Кеш-память ассоциативна. 26 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

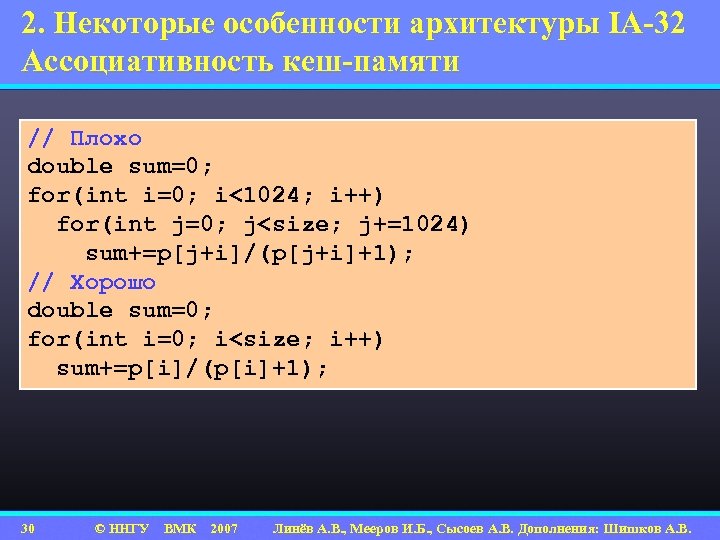

2. Некоторые особенности архитектуры IA-32 Ассоциативность кеш-памяти § Кеш-память с N-канальной ассоциативностью (N-way set associative), характеризует, что информация, размещённая по некоторому адресу ОП, может быть размещена только в N местах. 27 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Ассоциативность кеш-памяти § Кеш-память с 1 -канальной ассоциативностью § Кеш-память с 2 -канальной ассоциативностью 28 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Ассоциативность кеш-памяти 29 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

2. Некоторые особенности архитектуры IA-32 Ассоциативность кеш-памяти // Плохо double sum=0; for(int i=0; i<1024; i++) for(int j=0; j<size; j+=1024) sum+=p[j+i]/(p[j+i]+1); // Хорошо double sum=0; for(int i=0; i<size; i++) sum+=p[i]/(p[i]+1); 30 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

3. Некоторые приемы оптимизации под IA-32 31 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

3. Некоторые приемы оптимизации под IA-32 Введение Для того, чтобы программа работала быстро, она должна обеспечивать: § Отсутствие лишних вычислений. § Хороший прогноз ветвлений. § Быструю работу с памятью. § Производительность вещественных операций. § Использование SIMD-команд (векторизация). § Удачную смесь инструкций. 32 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

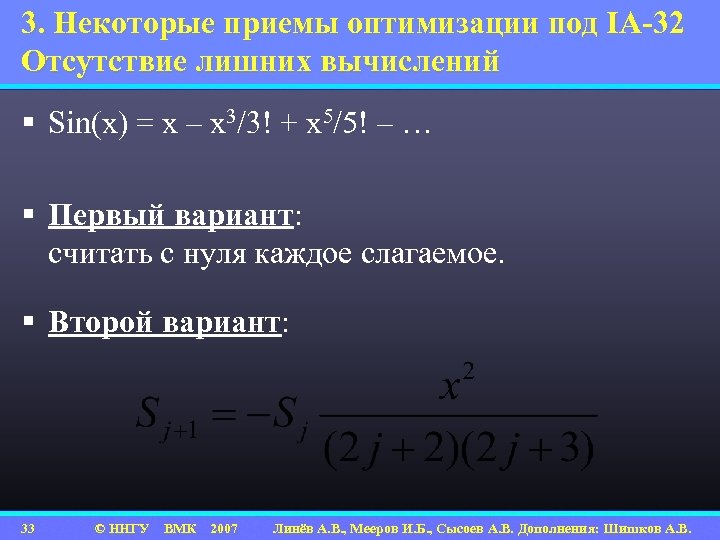

3. Некоторые приемы оптимизации под IA-32 Отсутствие лишних вычислений § Sin(x) = x – x 3/3! + x 5/5! – … § Первый вариант: считать с нуля каждое слагаемое. § Второй вариант: 33 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

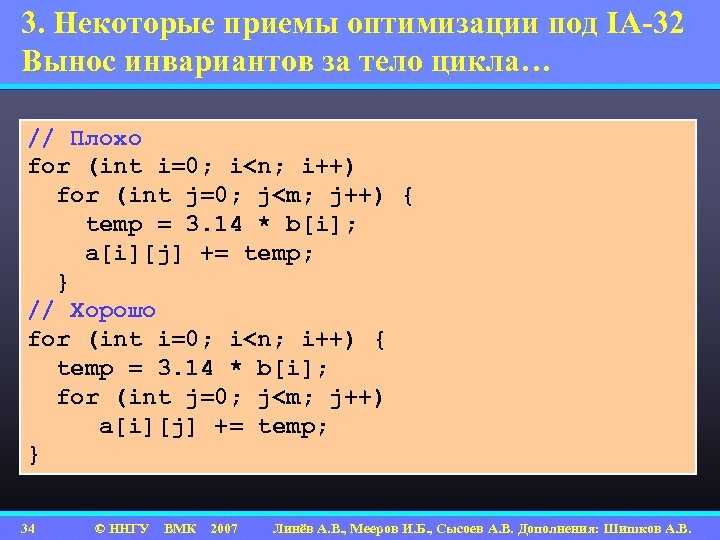

3. Некоторые приемы оптимизации под IA-32 Вынос инвариантов за тело цикла… // Плохо for (int i=0; i<n; i++) for (int j=0; j<m; j++) { temp = 3. 14 * b[i]; a[i][j] += temp; } // Хорошо for (int i=0; i<n; i++) { temp = 3. 14 * b[i]; for (int j=0; j<m; j++) a[i][j] += temp; } 34 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

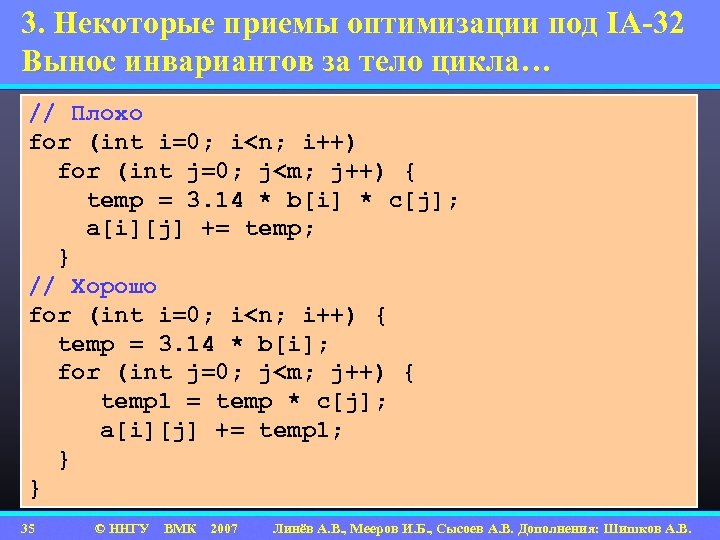

3. Некоторые приемы оптимизации под IA-32 Вынос инвариантов за тело цикла… // Плохо for (int i=0; i<n; i++) for (int j=0; j<m; j++) { temp = 3. 14 * b[i] * c[j]; a[i][j] += temp; } // Хорошо for (int i=0; i<n; i++) { temp = 3. 14 * b[i]; for (int j=0; j<m; j++) { temp 1 = temp * c[j]; a[i][j] += temp 1; } } 35 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

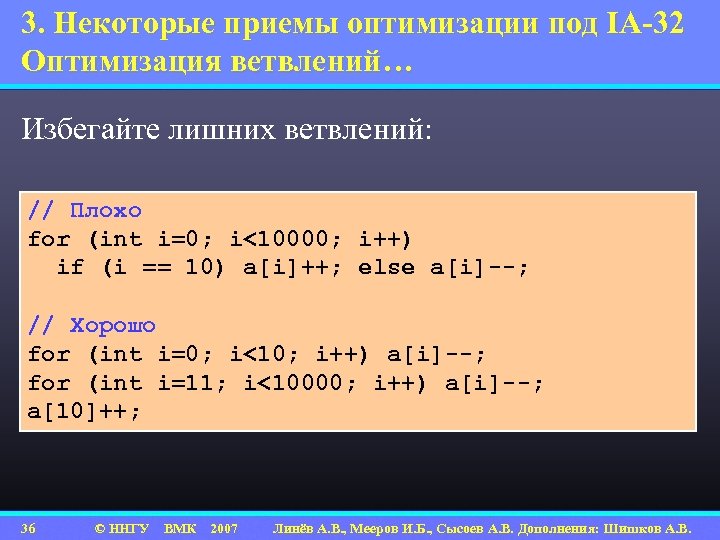

3. Некоторые приемы оптимизации под IA-32 Оптимизация ветвлений… Избегайте лишних ветвлений: // Плохо for (int i=0; i<10000; i++) if (i == 10) a[i]++; else a[i]--; // Хорошо for (int i=0; i<10; i++) a[i]--; for (int i=11; i<10000; i++) a[i]--; a[10]++; 36 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

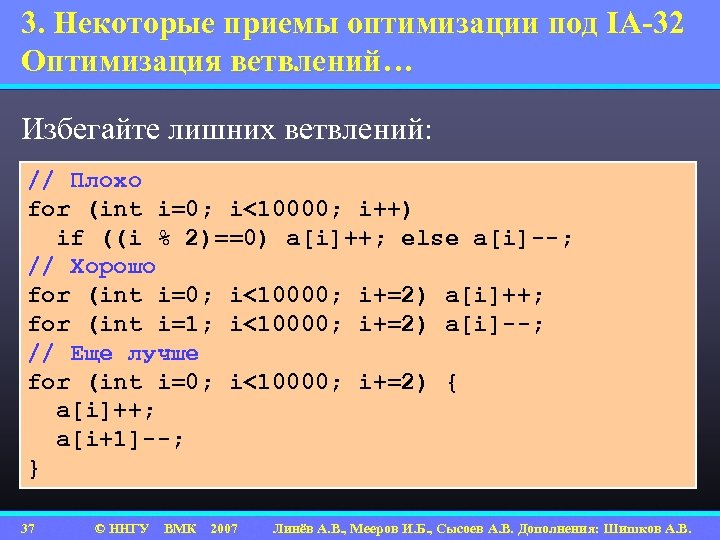

3. Некоторые приемы оптимизации под IA-32 Оптимизация ветвлений… Избегайте лишних ветвлений: // Плохо for (int i=0; i<10000; i++) if ((i % 2)==0) a[i]++; else a[i]--; // Хорошо for (int i=0; i<10000; i+=2) a[i]++; for (int i=1; i<10000; i+=2) a[i]--; // Еще лучше for (int i=0; i<10000; i+=2) { a[i]++; a[i+1]--; } 37 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

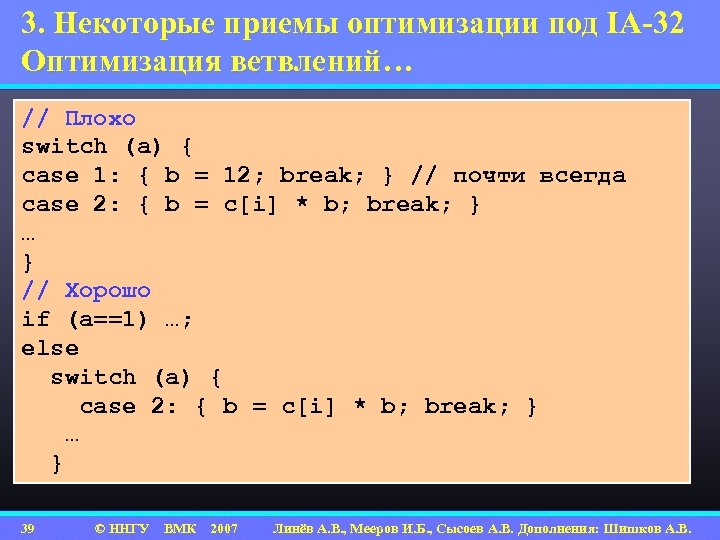

3. Некоторые приемы оптимизации под IA-32 Оптимизация ветвлений… § Размещайте наиболее часто реализующиеся ветвления в начале цепочки вложенных проверок. 38 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

3. Некоторые приемы оптимизации под IA-32 Оптимизация ветвлений… // Плохо § Размещайте наиболее часто реализующиеся switch (a) { case 1: { b = в начале } // почти вложенных ветвления 12; break; цепочки всегда case 2: { b = c[i] * b; break; } … проверок. } // Хорошо if (a==1) …; else switch (a) { case 2: { b = c[i] * b; break; } … } 39 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

3. Некоторые приемы оптимизации под IA-32 Оптимизация ветвлений § Главная беда – непрогнозируемые ветвления (random). § Branch prediction ищет «шаблон» (pattern) – закономерность, которой нет. 40 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

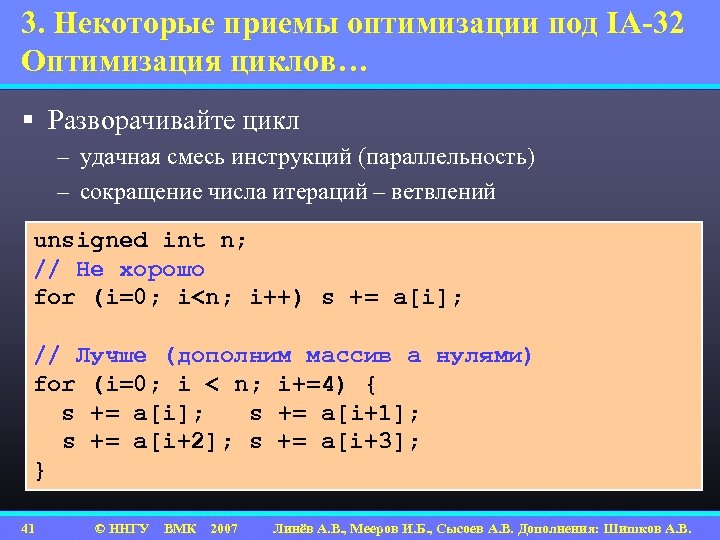

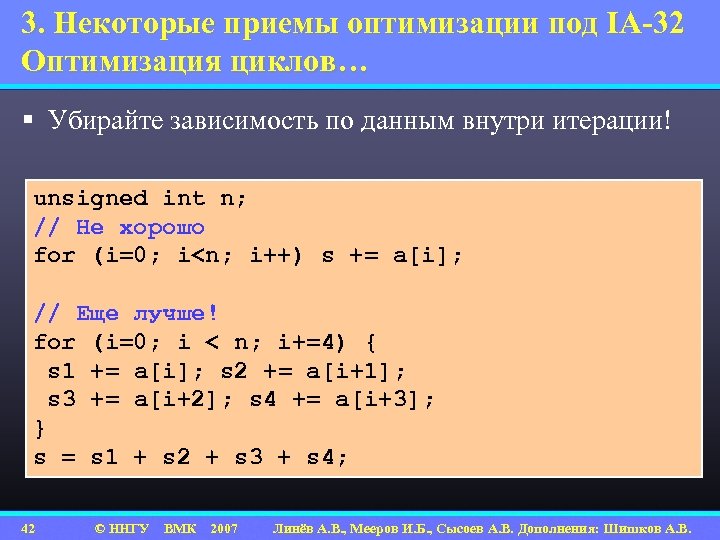

3. Некоторые приемы оптимизации под IA-32 Оптимизация циклов… § Разворачивайте цикл – удачная смесь инструкций (параллельность) – сокращение числа итераций – ветвлений unsigned int n; // Не хорошо for (i=0; i<n; i++) s += a[i]; // Лучше (дополним массив a нулями) for (i=0; i < n; i+=4) { s += a[i]; s += a[i+1]; s += a[i+2]; s += a[i+3]; } 41 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

3. Некоторые приемы оптимизации под IA-32 Оптимизация циклов… § Убирайте зависимость по данным внутри итерации! unsigned int n; // Не хорошо for (i=0; i<n; i++) s += a[i]; // Еще лучше! for (i=0; i < n; i+=4) { s 1 += a[i]; s 2 += a[i+1]; s 3 += a[i+2]; s 4 += a[i+3]; } s = s 1 + s 2 + s 3 + s 4; 42 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

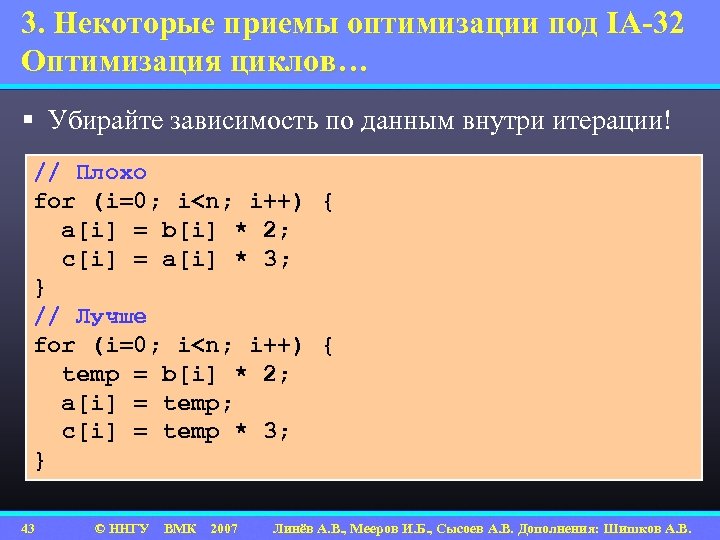

3. Некоторые приемы оптимизации под IA-32 Оптимизация циклов… § Убирайте зависимость по данным внутри итерации! // Плохо for (i=0; i<n; i++) { a[i] = b[i] * 2; c[i] = a[i] * 3; } // Лучше for (i=0; i<n; i++) { temp = b[i] * 2; a[i] = temp; c[i] = temp * 3; } 43 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

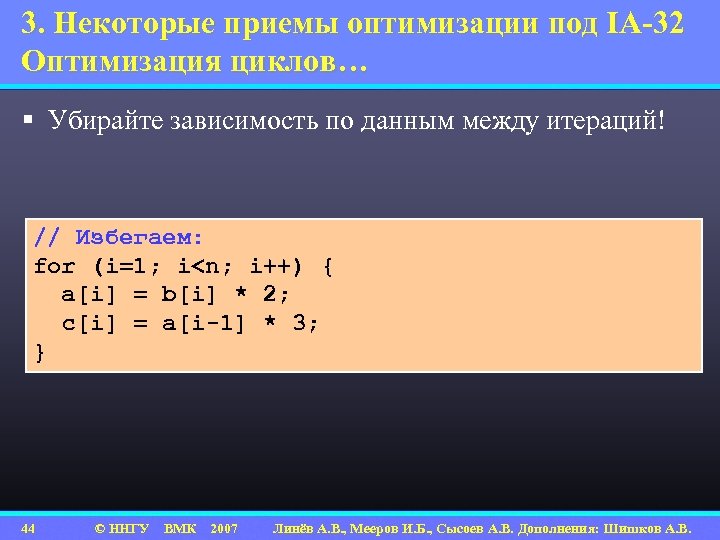

3. Некоторые приемы оптимизации под IA-32 Оптимизация циклов… § Убирайте зависимость по данным между итераций! // Избегаем: for (i=1; i<n; i++) { a[i] = b[i] * 2; c[i] = a[i-1] * 3; } 44 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

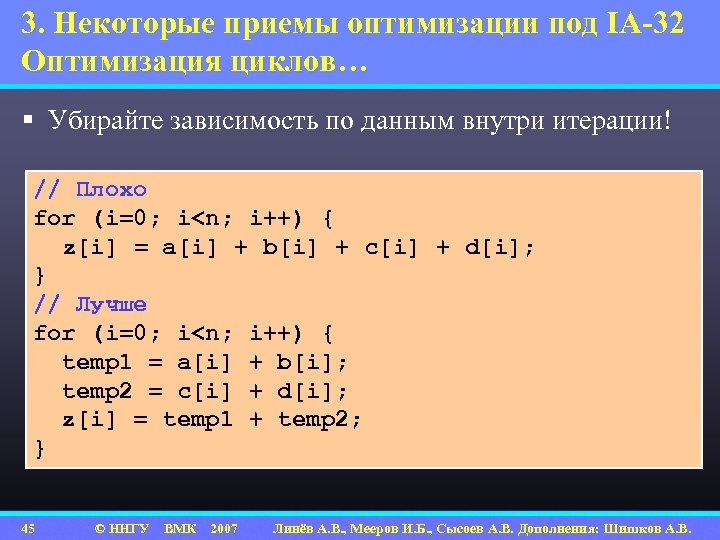

3. Некоторые приемы оптимизации под IA-32 Оптимизация циклов… § Убирайте зависимость по данным внутри итерации! // Плохо for (i=0; i<n; i++) { z[i] = a[i] + b[i] + c[i] + d[i]; } // Лучше for (i=0; i<n; i++) { temp 1 = a[i] + b[i]; temp 2 = c[i] + d[i]; z[i] = temp 1 + temp 2; } 45 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

3. Некоторые приемы оптимизации под IA-32 Векторизация § Если у вас: – простой внутренний цикл; – вы обрабатываете массивы; – нет зависимости между итерациями и внутри итерации; – нет смеси типов данных; – правильный компилятор, включены опции; – выполняются еще некоторые условия, то: Ваш внутренний цикл будет векторизован (использование SIMD)! 46 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

3. Некоторые приемы оптимизации под IA-32 Операции с вещественными числами § Перестраивайте алгоритм, чтобы не работать с очень малыми числами (avoid denormals). § По возможности понизьте точность используемых типов данных (float вместо double). 47 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

3. Некоторые приемы оптимизации под IA-32 Оптимизация работы с памятью § Выравнивание: избегаем невыравненного доступа к данным – избегаем штрафов. § Располагаем в структурах поля от большего к меньшему. Дополняем до 16, 32. . . § Локальность: стремимся программировать так, чтобы нужные данные находились в кэш-памяти. – – 48 разбиваем циклы на 2 (работа с разными массивами); перестановка циклов; блочные алгоритмы (умножение матриц); массивы структур и структуры массивов – в зависимости от задачи. © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

![3. Некоторые приемы оптимизации под IA-32 Пример слияния массивов // Вариант 1 int val[SIZE]; 3. Некоторые приемы оптимизации под IA-32 Пример слияния массивов // Вариант 1 int val[SIZE];](https://present5.com/presentation/0c22a7860c8ab8c0918202d27b2776ef/image-49.jpg)

3. Некоторые приемы оптимизации под IA-32 Пример слияния массивов // Вариант 1 int val[SIZE]; int key[SIZE]; // Вариант 2 struct merge { int val; int key; }; struct merged_array[SIZE]; Пример взят из учебного курса Intel Studio по архитектуре ЭВМ 49 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

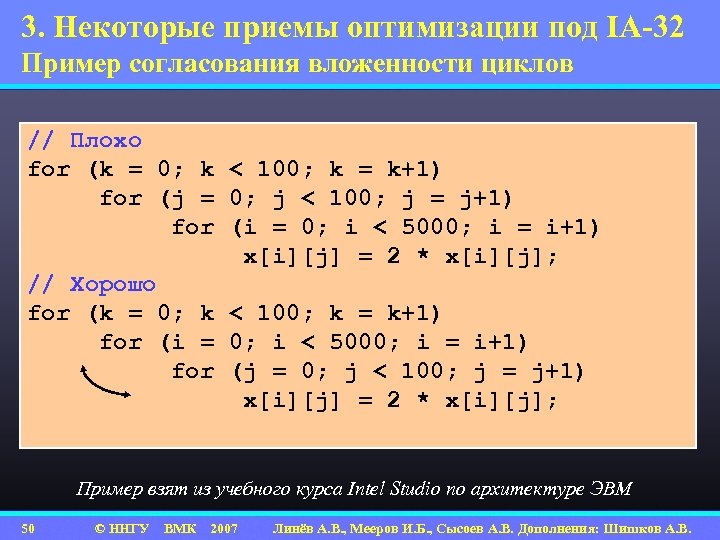

3. Некоторые приемы оптимизации под IA-32 Пример согласования вложенности циклов // Плохо for (k = 0; k < 100; k = k+1) for (j = 0; j < 100; j = j+1) for (i = 0; i < 5000; i = i+1) x[i][j] = 2 * x[i][j]; // Хорошо for (k = 0; k < 100; k = k+1) for (i = 0; i < 5000; i = i+1) for (j = 0; j < 100; j = j+1) x[i][j] = 2 * x[i][j]; Пример взят из учебного курса Intel Studio по архитектуре ЭВМ 50 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

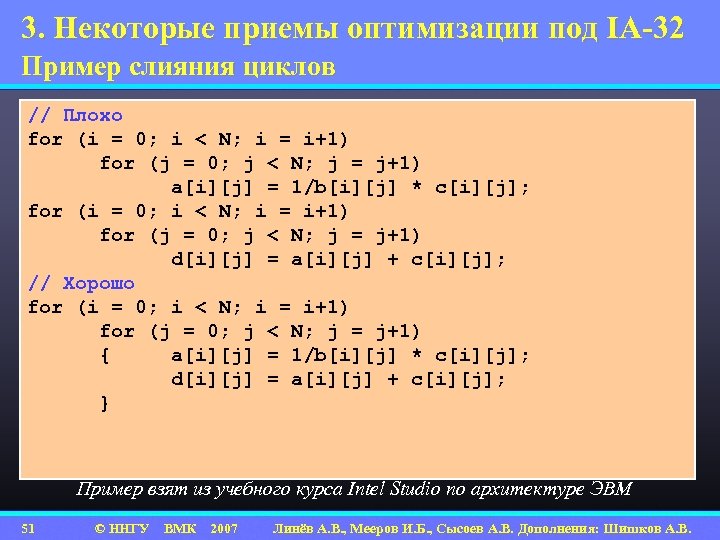

3. Некоторые приемы оптимизации под IA-32 Пример слияния циклов // Плохо for (i = 0; i < N; i = i+1) for (j = 0; j < N; j = j+1) a[i][j] = 1/b[i][j] * c[i][j]; for (i = 0; i < N; i = i+1) for (j = 0; j < N; j = j+1) d[i][j] = a[i][j] + c[i][j]; // Хорошо for (i = 0; i < N; i = i+1) for (j = 0; j < N; j = j+1) { a[i][j] = 1/b[i][j] * c[i][j]; d[i][j] = a[i][j] + c[i][j]; } Пример взят из учебного курса Intel Studio по архитектуре ЭВМ 51 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

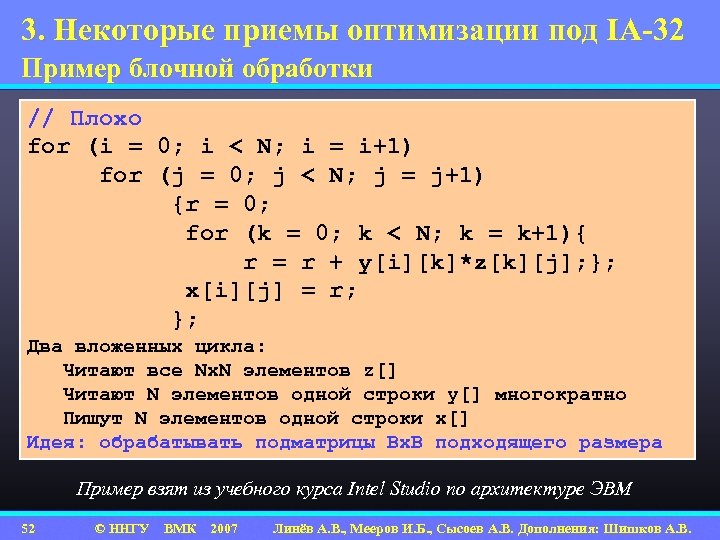

3. Некоторые приемы оптимизации под IA-32 Пример блочной обработки // Плохо for (i = 0; i < N; i = i+1) for (j = 0; j < N; j = j+1) {r = 0; for (k = 0; k < N; k = k+1){ r = r + y[i][k]*z[k][j]; }; x[i][j] = r; }; Два вложенных цикла: Читают все Nx. N элементов z[] Читают N элементов одной строки y[] многократно Пишут N элементов одной строки x[] Идея: обрабатывать подматрицы Bx. B подходящего размера Пример взят из учебного курса Intel Studio по архитектуре ЭВМ 52 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

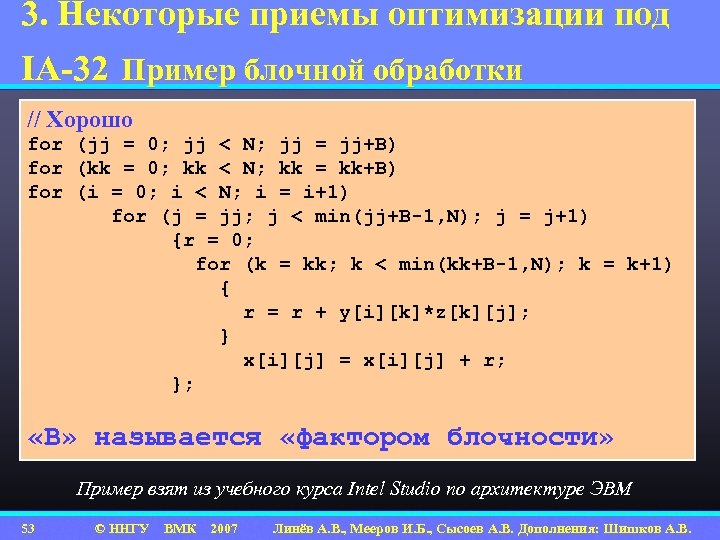

3. Некоторые приемы оптимизации под IA-32 Пример блочной обработки // Хорошо for (jj = 0; jj < N; jj = jj+B) for (kk = 0; kk < N; kk = kk+B) for (i = 0; i < N; i = i+1) for (j = jj; j < min(jj+B-1, N); j = j+1) {r = 0; for (k = kk; k < min(kk+B-1, N); k = k+1) { r = r + y[i][k]*z[k][j]; } x[i][j] = x[i][j] + r; }; «B» называется «фактором блочности» Пример взят из учебного курса Intel Studio по архитектуре ЭВМ 53 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

Вывод “Я также знал, но забыл афоризм Хоара о том, что преждевременная оптимизация – корень всех зол в программирования” Дональд Кнут. The errors of Te. X 54 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

Использованные источники При создании презентации активно использовались материалы книг: § Крис Касперски. Техника оптимизации программ. Эффективное использование памяти. – Санкт. Петербург: БХВ-Петербург, 2003. § Intel IA-32 Architecture optimization reference manual. § A. J. C. Bik. The software vectorization handbook. Intel. Press, 2004. 55 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

Вопросы § ? ? ? 56 © ННГУ ВМК 2007 Линёв А. В. , Мееров И. Б. , Сысоев А. В. Дополнения: Шишков А. В.

0c22a7860c8ab8c0918202d27b2776ef.ppt