bba92e921f10e653e0294272bac3b6b5.ppt

- Количество слайдов: 32

Networking and the Internet (4) l Last Week: » » » l Task Management revision Online Computing (Interactive versus Transactional) e-commerce issues – what do we need for B 2 C? HTML introduction HTML Practical Week 4 Focus » Network Architecture » Computer Memory – Virtual and Real » CPU design and Performance (Coope chapter 6 Willis, chapters 6, 7 and 8) » HTML Practical » HTML tables BS 2911 Week 4 1

Networking and the Internet (4) l Last Week: » » » l Task Management revision Online Computing (Interactive versus Transactional) e-commerce issues – what do we need for B 2 C? HTML introduction HTML Practical Week 4 Focus » Network Architecture » Computer Memory – Virtual and Real » CPU design and Performance (Coope chapter 6 Willis, chapters 6, 7 and 8) » HTML Practical » HTML tables BS 2911 Week 4 1

Network Architecture Last week we looked at networks in various ways: Physical, logical, data, meaning of data Will now consider “Packet Switching” BS 2911 Week 4 2

Network Architecture Last week we looked at networks in various ways: Physical, logical, data, meaning of data Will now consider “Packet Switching” BS 2911 Week 4 2

Early Computer Networks l Initially had two distinct purposes: » to connect terminals to mainframe computers » to link computers together l And two ranges: » Local – low errors, wiring under enterprise control » Wide-area – wiring regulated by PTTs (was error-prone) l And two topologies: l Network architectures developed to share connections, based on packet-switching concept: Telephone companies » Point-to point » Concentrated (multiple devices sharing a connection) » Systems Network Architecture led through 70 s and 80 s » Internet Architecture now taken over (even in IBM shops) BS 2911 Week 4 3

Early Computer Networks l Initially had two distinct purposes: » to connect terminals to mainframe computers » to link computers together l And two ranges: » Local – low errors, wiring under enterprise control » Wide-area – wiring regulated by PTTs (was error-prone) l And two topologies: l Network architectures developed to share connections, based on packet-switching concept: Telephone companies » Point-to point » Concentrated (multiple devices sharing a connection) » Systems Network Architecture led through 70 s and 80 s » Internet Architecture now taken over (even in IBM shops) BS 2911 Week 4 3

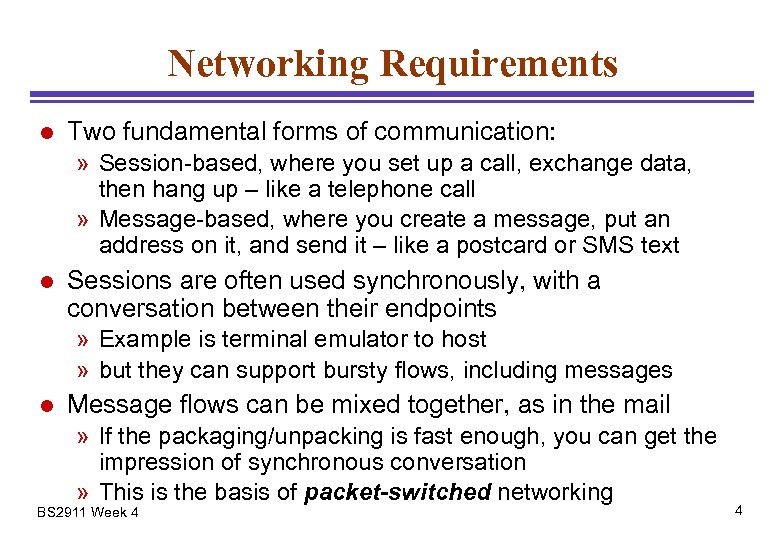

Networking Requirements l Two fundamental forms of communication: » Session-based, where you set up a call, exchange data, then hang up – like a telephone call » Message-based, where you create a message, put an address on it, and send it – like a postcard or SMS text l Sessions are often used synchronously, with a conversation between their endpoints » Example is terminal emulator to host » but they can support bursty flows, including messages l Message flows can be mixed together, as in the mail » If the packaging/unpacking is fast enough, you can get the impression of synchronous conversation » This is the basis of packet-switched networking BS 2911 Week 4 4

Networking Requirements l Two fundamental forms of communication: » Session-based, where you set up a call, exchange data, then hang up – like a telephone call » Message-based, where you create a message, put an address on it, and send it – like a postcard or SMS text l Sessions are often used synchronously, with a conversation between their endpoints » Example is terminal emulator to host » but they can support bursty flows, including messages l Message flows can be mixed together, as in the mail » If the packaging/unpacking is fast enough, you can get the impression of synchronous conversation » This is the basis of packet-switched networking BS 2911 Week 4 4

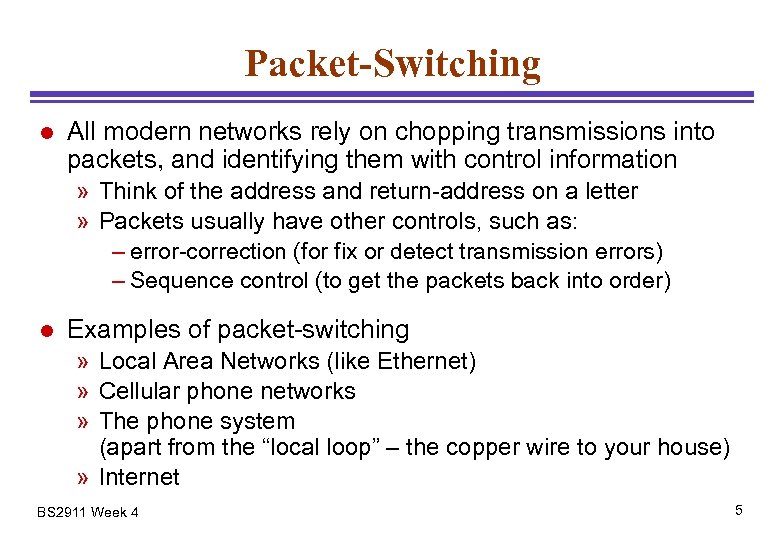

Packet-Switching l All modern networks rely on chopping transmissions into packets, and identifying them with control information » Think of the address and return-address on a letter » Packets usually have other controls, such as: – error-correction (for fix or detect transmission errors) – Sequence control (to get the packets back into order) l Examples of packet-switching » Local Area Networks (like Ethernet) » Cellular phone networks » The phone system (apart from the “local loop” – the copper wire to your house) » Internet BS 2911 Week 4 5

Packet-Switching l All modern networks rely on chopping transmissions into packets, and identifying them with control information » Think of the address and return-address on a letter » Packets usually have other controls, such as: – error-correction (for fix or detect transmission errors) – Sequence control (to get the packets back into order) l Examples of packet-switching » Local Area Networks (like Ethernet) » Cellular phone networks » The phone system (apart from the “local loop” – the copper wire to your house) » Internet BS 2911 Week 4 5

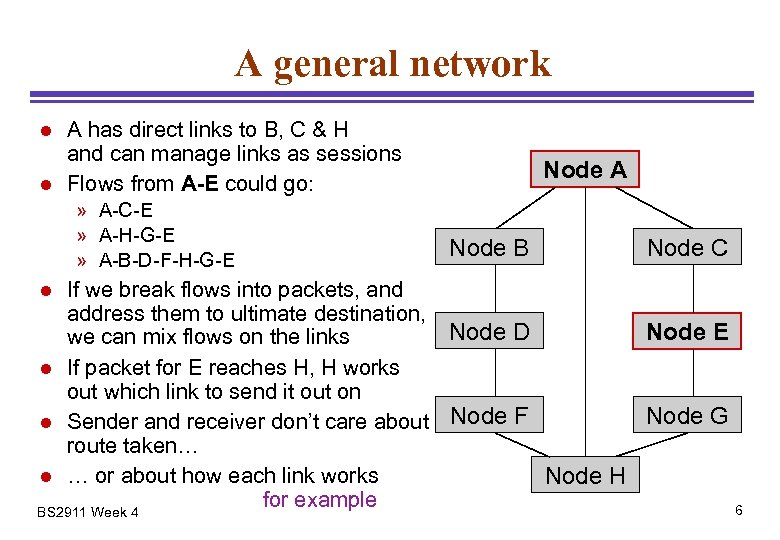

A general network l l A has direct links to B, C & H and can manage links as sessions Flows from A-E could go: » A-C-E » A-H-G-E » A-B-D-F-H-G-E Node A Node B Node C If we break flows into packets, and address them to ultimate destination, Node D Node E we can mix flows on the links l If packet for E reaches H, H works out which link to send it out on Node G l Sender and receiver don’t care about Node F route taken… l … or about how each link works Node H for example 6 BS 2911 Week 4 l

A general network l l A has direct links to B, C & H and can manage links as sessions Flows from A-E could go: » A-C-E » A-H-G-E » A-B-D-F-H-G-E Node A Node B Node C If we break flows into packets, and address them to ultimate destination, Node D Node E we can mix flows on the links l If packet for E reaches H, H works out which link to send it out on Node G l Sender and receiver don’t care about Node F route taken… l … or about how each link works Node H for example 6 BS 2911 Week 4 l

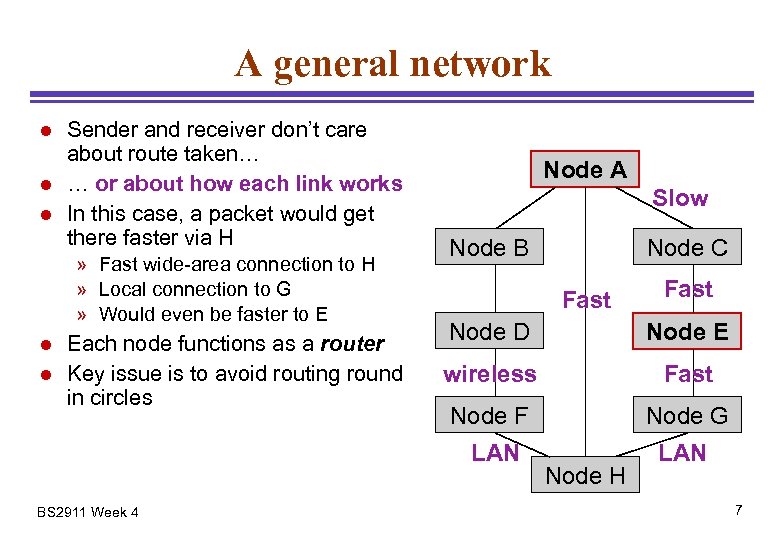

A general network l l l Sender and receiver don’t care about route taken… … or about how each link works In this case, a packet would get there faster via H » Fast wide-area connection to H » Local connection to G » Would even be faster to E Node A Slow Node B Node C Fast l Each node functions as a router Key issue is to avoid routing round in circles BS 2911 Week 4 Node D Node E wireless Fast Node F Node G LAN l LAN Node H 7

A general network l l l Sender and receiver don’t care about route taken… … or about how each link works In this case, a packet would get there faster via H » Fast wide-area connection to H » Local connection to G » Would even be faster to E Node A Slow Node B Node C Fast l Each node functions as a router Key issue is to avoid routing round in circles BS 2911 Week 4 Node D Node E wireless Fast Node F Node G LAN l LAN Node H 7

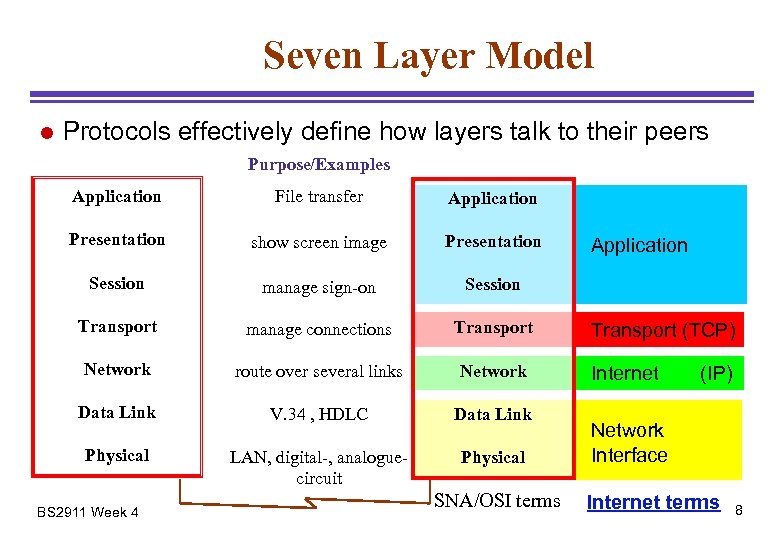

Seven Layer Model l Protocols effectively define how layers talk to their peers Purpose/Examples Application File transfer Application Presentation show screen image Presentation Session manage sign-on Session Transport manage connections Transport Network route over several links Network Data Link V. 34 , HDLC Data Link Physical LAN, digital-, analoguecircuit Physical BS 2911 Week 4 SNA/OSI terms Application Transport (TCP) Internet (IP) Network Interface Internet terms 8

Seven Layer Model l Protocols effectively define how layers talk to their peers Purpose/Examples Application File transfer Application Presentation show screen image Presentation Session manage sign-on Session Transport manage connections Transport Network route over several links Network Data Link V. 34 , HDLC Data Link Physical LAN, digital-, analoguecircuit Physical BS 2911 Week 4 SNA/OSI terms Application Transport (TCP) Internet (IP) Network Interface Internet terms 8

TCP/IP has superseded SNA l l l The World of e-Commerce is built on LANs and TCP/IP We’ll cover Ethernet and other LAN technology later; they provide the links to carry Internet Protocol data Every location on the Internet has an IP address » To send data to a location, system applies its address to every “packet” to be transmitted » Also attaches a return address for replies l Sender works out which link to send the packet down » Routes it when there’s no direct link – » for example, at home, any non-local Internet address is down the Talk connection from my home network » Other end of link works out onward routing BS 2911 Week 4 9

TCP/IP has superseded SNA l l l The World of e-Commerce is built on LANs and TCP/IP We’ll cover Ethernet and other LAN technology later; they provide the links to carry Internet Protocol data Every location on the Internet has an IP address » To send data to a location, system applies its address to every “packet” to be transmitted » Also attaches a return address for replies l Sender works out which link to send the packet down » Routes it when there’s no direct link – » for example, at home, any non-local Internet address is down the Talk connection from my home network » Other end of link works out onward routing BS 2911 Week 4 9

Memory Concepts Virtual and Real Memory: we’ll start with Real BS 2911 Week 4 10

Memory Concepts Virtual and Real Memory: we’ll start with Real BS 2911 Week 4 10

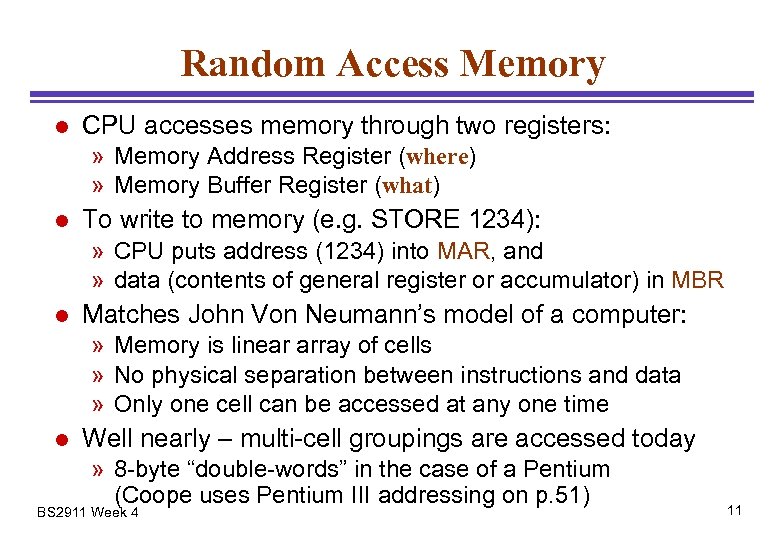

Random Access Memory l CPU accesses memory through two registers: » Memory Address Register (where) » Memory Buffer Register (what) l To write to memory (e. g. STORE 1234): » CPU puts address (1234) into MAR, and » data (contents of general register or accumulator) in MBR l Matches John Von Neumann’s model of a computer: » Memory is linear array of cells » No physical separation between instructions and data » Only one cell can be accessed at any one time l Well nearly – multi-cell groupings are accessed today » 8 -byte “double-words” in the case of a Pentium (Coope uses Pentium III addressing on p. 51) BS 2911 Week 4 11

Random Access Memory l CPU accesses memory through two registers: » Memory Address Register (where) » Memory Buffer Register (what) l To write to memory (e. g. STORE 1234): » CPU puts address (1234) into MAR, and » data (contents of general register or accumulator) in MBR l Matches John Von Neumann’s model of a computer: » Memory is linear array of cells » No physical separation between instructions and data » Only one cell can be accessed at any one time l Well nearly – multi-cell groupings are accessed today » 8 -byte “double-words” in the case of a Pentium (Coope uses Pentium III addressing on p. 51) BS 2911 Week 4 11

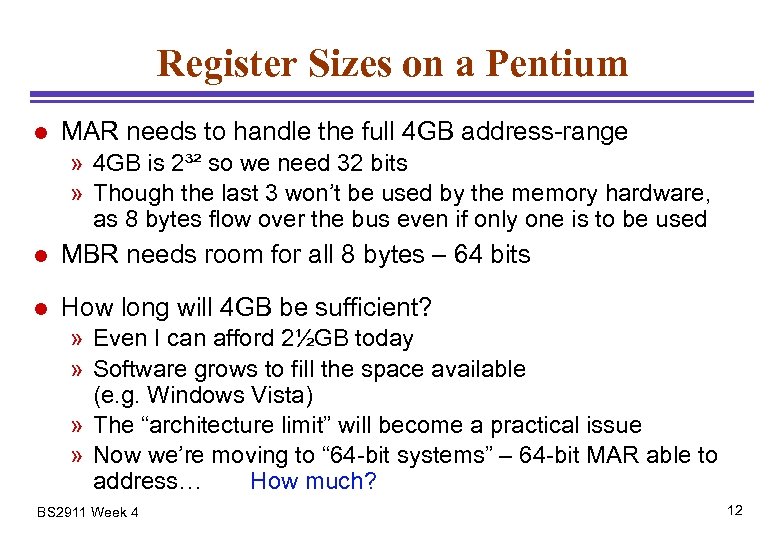

Register Sizes on a Pentium l MAR needs to handle the full 4 GB address-range » 4 GB is 2³² so we need 32 bits » Though the last 3 won’t be used by the memory hardware, as 8 bytes flow over the bus even if only one is to be used l MBR needs room for all 8 bytes – 64 bits l How long will 4 GB be sufficient? » Even I can afford 2½GB today » Software grows to fill the space available (e. g. Windows Vista) » The “architecture limit” will become a practical issue » Now we’re moving to “ 64 -bit systems” – 64 -bit MAR able to address… How much? BS 2911 Week 4 12

Register Sizes on a Pentium l MAR needs to handle the full 4 GB address-range » 4 GB is 2³² so we need 32 bits » Though the last 3 won’t be used by the memory hardware, as 8 bytes flow over the bus even if only one is to be used l MBR needs room for all 8 bytes – 64 bits l How long will 4 GB be sufficient? » Even I can afford 2½GB today » Software grows to fill the space available (e. g. Windows Vista) » The “architecture limit” will become a practical issue » Now we’re moving to “ 64 -bit systems” – 64 -bit MAR able to address… How much? BS 2911 Week 4 12

Associative Memory l l l l Memory is read by content, not by address Essentially you get locations matching a given key Place key in interrogate register Interrogate Register Filter matches with a mask Mask Register Parallel memory electronics flag all locations that match Associative Registers Expensive – Little used for ordinary data Valuable for paging systems » As we shall see l Gordon Scarrott’s CAFS* was never a commercial success BS 2911 Week 4 * Content Addressable File Store 13

Associative Memory l l l l Memory is read by content, not by address Essentially you get locations matching a given key Place key in interrogate register Interrogate Register Filter matches with a mask Mask Register Parallel memory electronics flag all locations that match Associative Registers Expensive – Little used for ordinary data Valuable for paging systems » As we shall see l Gordon Scarrott’s CAFS* was never a commercial success BS 2911 Week 4 * Content Addressable File Store 13

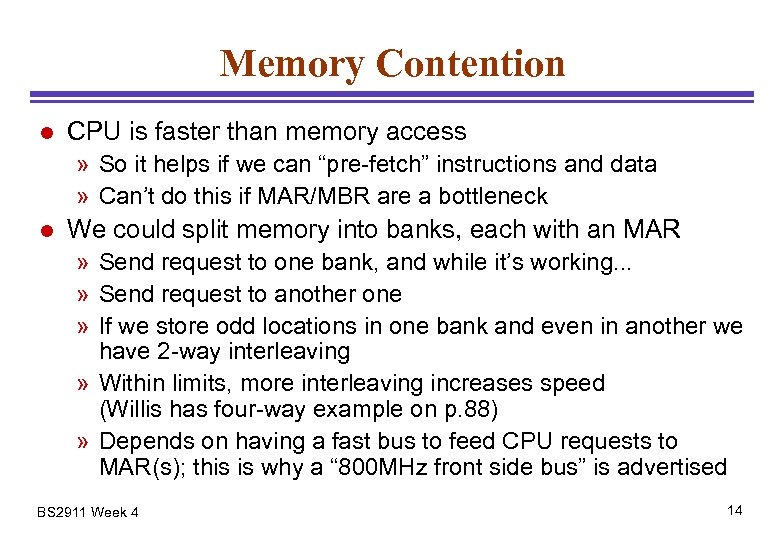

Memory Contention l CPU is faster than memory access » So it helps if we can “pre-fetch” instructions and data » Can’t do this if MAR/MBR are a bottleneck l We could split memory into banks, each with an MAR » Send request to one bank, and while it’s working. . . » Send request to another one » If we store odd locations in one bank and even in another we have 2 -way interleaving » Within limits, more interleaving increases speed (Willis has four-way example on p. 88) » Depends on having a fast bus to feed CPU requests to MAR(s); this is why a “ 800 MHz front side bus” is advertised BS 2911 Week 4 14

Memory Contention l CPU is faster than memory access » So it helps if we can “pre-fetch” instructions and data » Can’t do this if MAR/MBR are a bottleneck l We could split memory into banks, each with an MAR » Send request to one bank, and while it’s working. . . » Send request to another one » If we store odd locations in one bank and even in another we have 2 -way interleaving » Within limits, more interleaving increases speed (Willis has four-way example on p. 88) » Depends on having a fast bus to feed CPU requests to MAR(s); this is why a “ 800 MHz front side bus” is advertised BS 2911 Week 4 14

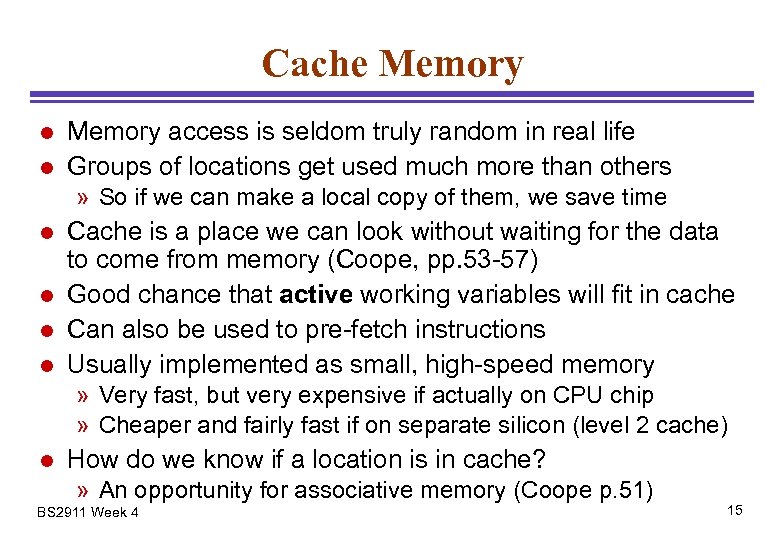

Cache Memory l l Memory access is seldom truly random in real life Groups of locations get used much more than others » So if we can make a local copy of them, we save time l l Cache is a place we can look without waiting for the data to come from memory (Coope, pp. 53 -57) Good chance that active working variables will fit in cache Can also be used to pre-fetch instructions Usually implemented as small, high-speed memory » Very fast, but very expensive if actually on CPU chip » Cheaper and fairly fast if on separate silicon (level 2 cache) l How do we know if a location is in cache? » An opportunity for associative memory (Coope p. 51) BS 2911 Week 4 15

Cache Memory l l Memory access is seldom truly random in real life Groups of locations get used much more than others » So if we can make a local copy of them, we save time l l Cache is a place we can look without waiting for the data to come from memory (Coope, pp. 53 -57) Good chance that active working variables will fit in cache Can also be used to pre-fetch instructions Usually implemented as small, high-speed memory » Very fast, but very expensive if actually on CPU chip » Cheaper and fairly fast if on separate silicon (level 2 cache) l How do we know if a location is in cache? » An opportunity for associative memory (Coope p. 51) BS 2911 Week 4 15

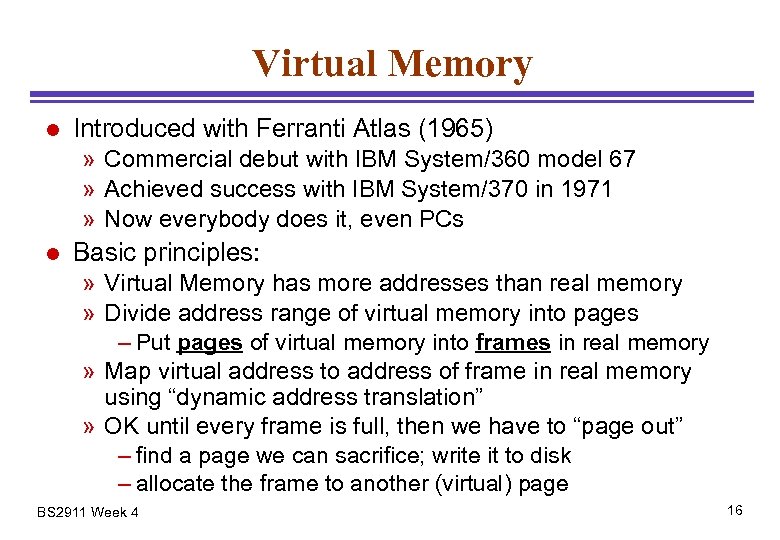

Virtual Memory l Introduced with Ferranti Atlas (1965) » Commercial debut with IBM System/360 model 67 » Achieved success with IBM System/370 in 1971 » Now everybody does it, even PCs l Basic principles: » Virtual Memory has more addresses than real memory » Divide address range of virtual memory into pages – Put pages of virtual memory into frames in real memory » Map virtual address to address of frame in real memory using “dynamic address translation” » OK until every frame is full, then we have to “page out” – find a page we can sacrifice; write it to disk – allocate the frame to another (virtual) page BS 2911 Week 4 16

Virtual Memory l Introduced with Ferranti Atlas (1965) » Commercial debut with IBM System/360 model 67 » Achieved success with IBM System/370 in 1971 » Now everybody does it, even PCs l Basic principles: » Virtual Memory has more addresses than real memory » Divide address range of virtual memory into pages – Put pages of virtual memory into frames in real memory » Map virtual address to address of frame in real memory using “dynamic address translation” » OK until every frame is full, then we have to “page out” – find a page we can sacrifice; write it to disk – allocate the frame to another (virtual) page BS 2911 Week 4 16

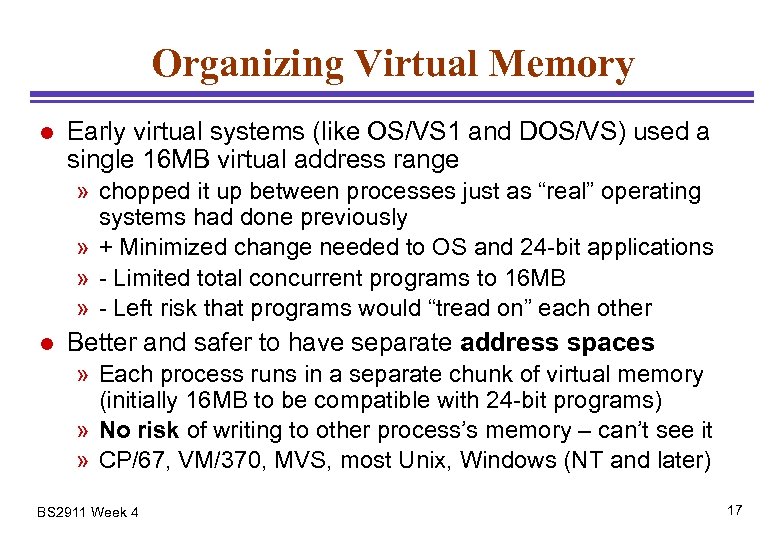

Organizing Virtual Memory l Early virtual systems (like OS/VS 1 and DOS/VS) used a single 16 MB virtual address range » chopped it up between processes just as “real” operating systems had done previously » + Minimized change needed to OS and 24 -bit applications » - Limited total concurrent programs to 16 MB » - Left risk that programs would “tread on” each other l Better and safer to have separate address spaces » Each process runs in a separate chunk of virtual memory (initially 16 MB to be compatible with 24 -bit programs) » No risk of writing to other process’s memory – can’t see it » CP/67, VM/370, MVS, most Unix, Windows (NT and later) BS 2911 Week 4 17

Organizing Virtual Memory l Early virtual systems (like OS/VS 1 and DOS/VS) used a single 16 MB virtual address range » chopped it up between processes just as “real” operating systems had done previously » + Minimized change needed to OS and 24 -bit applications » - Limited total concurrent programs to 16 MB » - Left risk that programs would “tread on” each other l Better and safer to have separate address spaces » Each process runs in a separate chunk of virtual memory (initially 16 MB to be compatible with 24 -bit programs) » No risk of writing to other process’s memory – can’t see it » CP/67, VM/370, MVS, most Unix, Windows (NT and later) BS 2911 Week 4 17

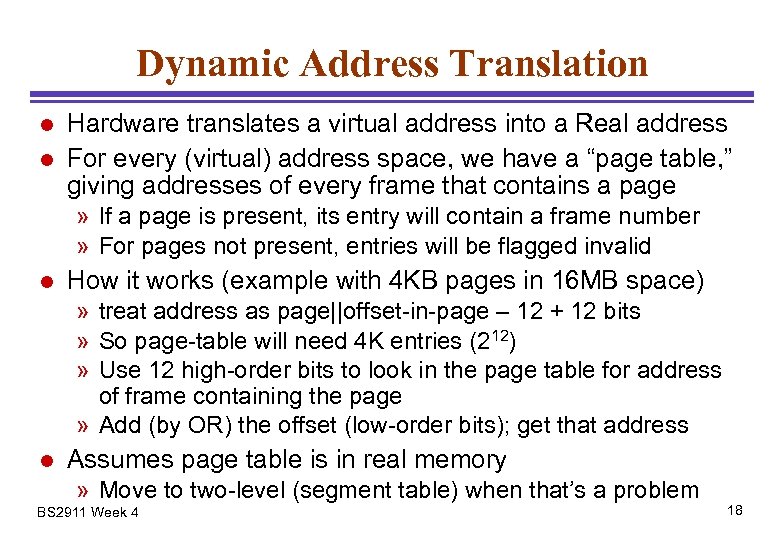

Dynamic Address Translation l l Hardware translates a virtual address into a Real address For every (virtual) address space, we have a “page table, ” giving addresses of every frame that contains a page » If a page is present, its entry will contain a frame number » For pages not present, entries will be flagged invalid l How it works (example with 4 KB pages in 16 MB space) » treat address as page||offset-in-page – 12 + 12 bits » So page-table will need 4 K entries (212) » Use 12 high-order bits to look in the page table for address of frame containing the page » Add (by OR) the offset (low-order bits); get that address l Assumes page table is in real memory » Move to two-level (segment table) when that’s a problem BS 2911 Week 4 18

Dynamic Address Translation l l Hardware translates a virtual address into a Real address For every (virtual) address space, we have a “page table, ” giving addresses of every frame that contains a page » If a page is present, its entry will contain a frame number » For pages not present, entries will be flagged invalid l How it works (example with 4 KB pages in 16 MB space) » treat address as page||offset-in-page – 12 + 12 bits » So page-table will need 4 K entries (212) » Use 12 high-order bits to look in the page table for address of frame containing the page » Add (by OR) the offset (low-order bits); get that address l Assumes page table is in real memory » Move to two-level (segment table) when that’s a problem BS 2911 Week 4 18

Getting to a byte in real memory 8 F 4 A 10 Page number Offset in page Virtual address A 10 Relevant page frame Page table 8 F 4 Addressed byte contains real address Real memory BS 2911 Week 4 19

Getting to a byte in real memory 8 F 4 A 10 Page number Offset in page Virtual address A 10 Relevant page frame Page table 8 F 4 Addressed byte contains real address Real memory BS 2911 Week 4 19

Machine code & CPU structure l Some of Coope chapter 5 (Willis 7 -8) will be familiar to you » » l Instruction sets for Machine code Optional detail Register instructions (you’ll not be examined on anything Stacks beyond simple Virtual Memory) Components of the CPU Base & Displacement addressing may not be » IBM System/360 instructions use 16 -bit address, but memory needs a 24 -bit address (31 -bit from S/370) » So have a register to hold a base address (<32 -bits) » add displacement to decide which location to access » Displacement can be literal* or held in a register » Can also add contents of another (Index) register – great for stepping along an array * inside the instruction BS 2911 Week 4 20

Machine code & CPU structure l Some of Coope chapter 5 (Willis 7 -8) will be familiar to you » » l Instruction sets for Machine code Optional detail Register instructions (you’ll not be examined on anything Stacks beyond simple Virtual Memory) Components of the CPU Base & Displacement addressing may not be » IBM System/360 instructions use 16 -bit address, but memory needs a 24 -bit address (31 -bit from S/370) » So have a register to hold a base address (<32 -bits) » add displacement to decide which location to access » Displacement can be literal* or held in a register » Can also add contents of another (Index) register – great for stepping along an array * inside the instruction BS 2911 Week 4 20

World Wide Web Publishing Writing HTML Some recommended references: http: //www. web-nation. com/lessons/html-pri. htm http: //www. w 3 schools. com/ BS 2911 Week 4 21

World Wide Web Publishing Writing HTML Some recommended references: http: //www. web-nation. com/lessons/html-pri. htm http: //www. w 3 schools. com/ BS 2911 Week 4 21

World Wide Web Publishing l How confident are you about: » » Basic structure of an HTML document Headings, Paragraphs and Lists Including Images Making Hyperlinks ? l Did you do the exercise last week? See document and zip file of samples on Learning Network l Main structures still to study are: » Tables (this week) » Frames BS 2911 Week 4 22

World Wide Web Publishing l How confident are you about: » » Basic structure of an HTML document Headings, Paragraphs and Lists Including Images Making Hyperlinks ? l Did you do the exercise last week? See document and zip file of samples on Learning Network l Main structures still to study are: » Tables (this week) » Frames BS 2911 Week 4 22

Reminder: Creating Hyperlinks l l Any hyperlink reference needs to say what it is linking to In HTML, we use an Anchor tag with the HREF attribute » Quick Univ » Local reference l l You can reference any resource on the Internet – Just give its URL Any lack of specificity means “look locally, ” so missing out the domain means it is in the local file system » Always leave out as much as you can Important in Assignment » Makes it much easier to move the site » Can also use relative references, e. g. to a sub-folder relative reference BS 2911 Week 4 23

Reminder: Creating Hyperlinks l l Any hyperlink reference needs to say what it is linking to In HTML, we use an Anchor tag with the HREF attribute » Quick Univ » Local reference l l You can reference any resource on the Internet – Just give its URL Any lack of specificity means “look locally, ” so missing out the domain means it is in the local file system » Always leave out as much as you can Important in Assignment » Makes it much easier to move the site » Can also use relative references, e. g. to a sub-folder relative reference BS 2911 Week 4 23

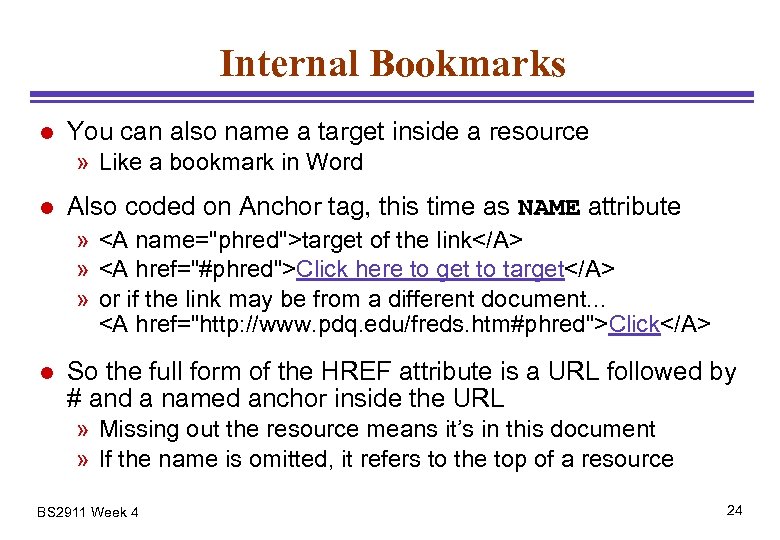

Internal Bookmarks l You can also name a target inside a resource » Like a bookmark in Word l Also coded on Anchor tag, this time as NAME attribute » target of the link » Click here to get to target » or if the link may be from a different document. . . Click l So the full form of the HREF attribute is a URL followed by # and a named anchor inside the URL » Missing out the resource means it’s in this document » If the name is omitted, it refers to the top of a resource BS 2911 Week 4 24

Internal Bookmarks l You can also name a target inside a resource » Like a bookmark in Word l Also coded on Anchor tag, this time as NAME attribute » target of the link » Click here to get to target » or if the link may be from a different document. . . Click l So the full form of the HREF attribute is a URL followed by # and a named anchor inside the URL » Missing out the resource means it’s in this document » If the name is omitted, it refers to the top of a resource BS 2911 Week 4 24

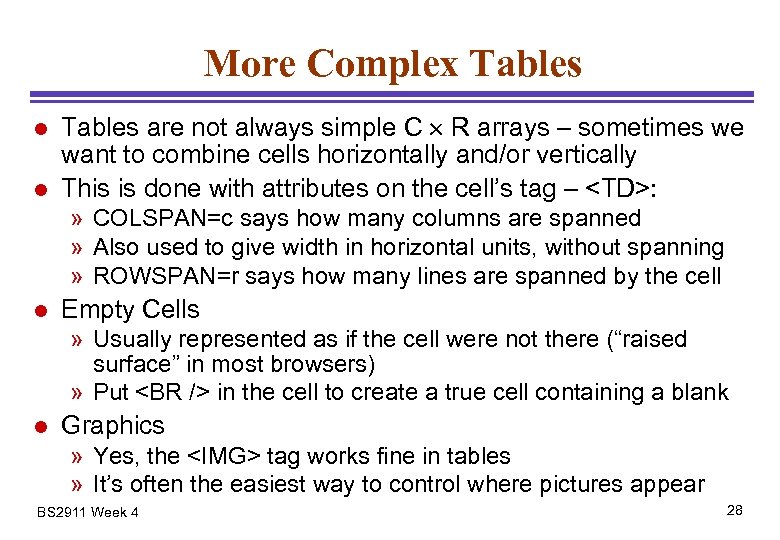

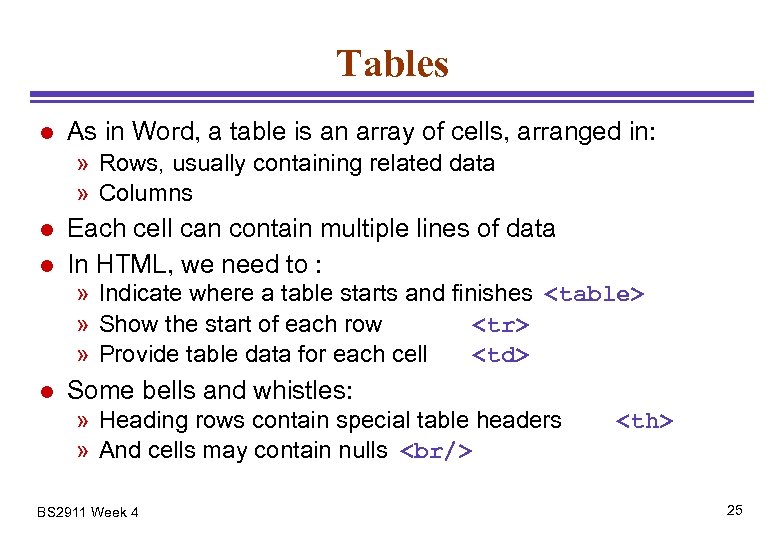

Tables l As in Word, a table is an array of cells, arranged in: » Rows, usually containing related data » Columns l l Each cell can contain multiple lines of data In HTML, we need to : » Indicate where a table starts and finishes

Tables l As in Word, a table is an array of cells, arranged in: » Rows, usually containing related data » Columns l l Each cell can contain multiple lines of data In HTML, we need to : » Indicate where a table starts and finishes

| l Some bells and whistles: » Heading rows contain special table headers » And cells may contain nulls BS 2911 Week 4 | 25

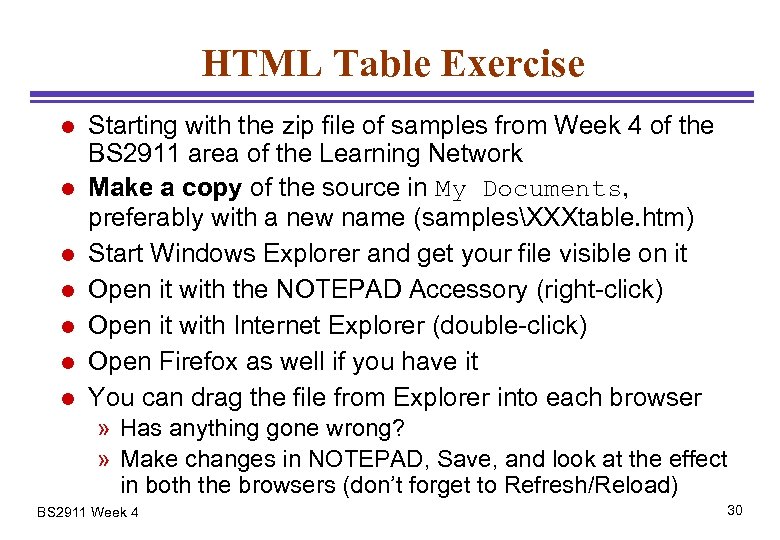

: » COLSPAN=c says how many columns are spanned » Also used to give width in horizontal units, without spanning » ROWSPAN=r says how many lines are spanned by the cell l Empty Cells » Usually represented as if the cell were not there (“raised surface” in most browsers) » Put | in the cell to create a true cell containing a blank l Graphics » Yes, the

, | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|