3c05760808abdd383c4a48ea85fd0747.ppt

- Количество слайдов: 25

Nanoelectronic Memory Devices: Space-Time-Energy Trade-offs Ralph Cavin and Victor Zhirnov Semiconductor Research Corporation

Nanoelectronic Memory Devices: Space-Time-Energy Trade-offs Ralph Cavin and Victor Zhirnov Semiconductor Research Corporation

Main Points q Many candidates for beyond-CMOS nano-electronics have been proposed for memory, but no clear successor has been identified. q q Methodology for system-level analysis How is maximum performance related to device physics? SRC/NSF A*STAR Forum on 2020 Semiconductor Memory Strategies: Processes, Devices, and Architectures, Singapore, October 20 -21, 2009 http: //grc. src. org/member/event/e 003676_Meeting. Results. asp 2

Main Points q Many candidates for beyond-CMOS nano-electronics have been proposed for memory, but no clear successor has been identified. q q Methodology for system-level analysis How is maximum performance related to device physics? SRC/NSF A*STAR Forum on 2020 Semiconductor Memory Strategies: Processes, Devices, and Architectures, Singapore, October 20 -21, 2009 http: //grc. src. org/member/event/e 003676_Meeting. Results. asp 2

Space-Time-Energy Metrics q Essential parameters of the memory element are: q q q cell size/density, retention time, access time/speed operating voltage/energy. None of known memory technologies, perform well across all of these parameters At the most basic level, for all memory elements, there is interdependence between operational voltage, the speed of operation and the retention time. Cell dimensions are also part of the trade-off, hence the Space-Time-Energy compromise 3

Space-Time-Energy Metrics q Essential parameters of the memory element are: q q q cell size/density, retention time, access time/speed operating voltage/energy. None of known memory technologies, perform well across all of these parameters At the most basic level, for all memory elements, there is interdependence between operational voltage, the speed of operation and the retention time. Cell dimensions are also part of the trade-off, hence the Space-Time-Energy compromise 3

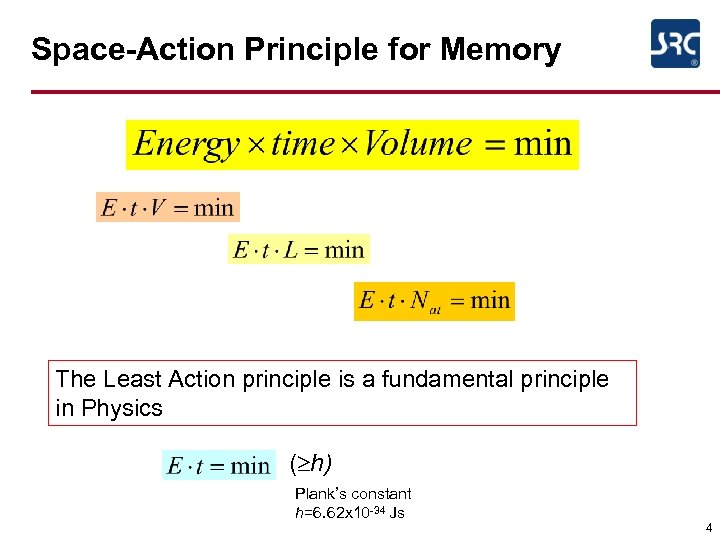

Space-Action Principle for Memory The Least Action principle is a fundamental principle in Physics ( h) Plank’s constant h=6. 62 x 10 -34 Js 4

Space-Action Principle for Memory The Least Action principle is a fundamental principle in Physics ( h) Plank’s constant h=6. 62 x 10 -34 Js 4

Three essential components of a Memory Device: q 1) ‘Storage node’ q q 2) ‘Sensor’ which reads the state q q e. g. transistor 3) ‘Selector’ which allows a memory cell in an array to be addressed q q q physics of memory operation transistor diode All three components impact scaling limits for all memory devices 5

Three essential components of a Memory Device: q 1) ‘Storage node’ q q 2) ‘Sensor’ which reads the state q q e. g. transistor 3) ‘Selector’ which allows a memory cell in an array to be addressed q q q physics of memory operation transistor diode All three components impact scaling limits for all memory devices 5

Three Major Memory State Variables q Electron Charge (‘moving electrons’) q q Electron Spin (‘moving spins’) q q e. g. DRAM, Flash (STT-) MRAM Massive particle(s) (‘moving atoms’) q e. g. Re. RAM, PCM, Nanomechanical, etc. Note: Electrical I/O always wanted 6

Three Major Memory State Variables q Electron Charge (‘moving electrons’) q q Electron Spin (‘moving spins’) q q e. g. DRAM, Flash (STT-) MRAM Massive particle(s) (‘moving atoms’) q e. g. Re. RAM, PCM, Nanomechanical, etc. Note: Electrical I/O always wanted 6

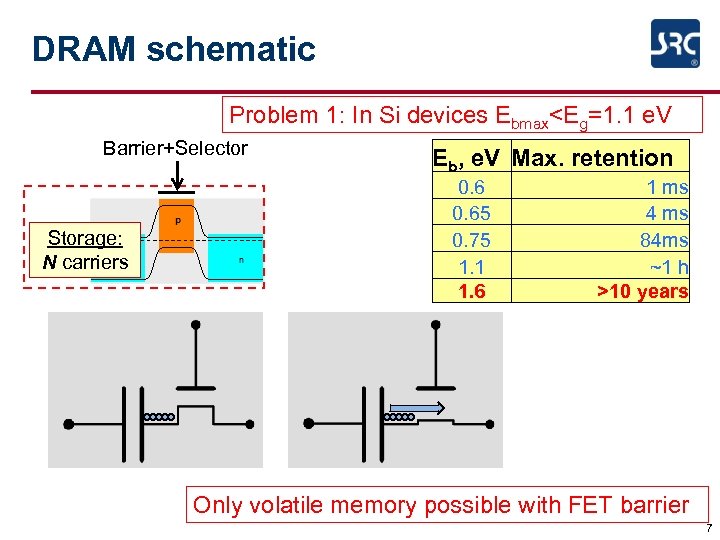

DRAM schematic Problem 1: In Si devices Ebmax

DRAM schematic Problem 1: In Si devices Ebmax

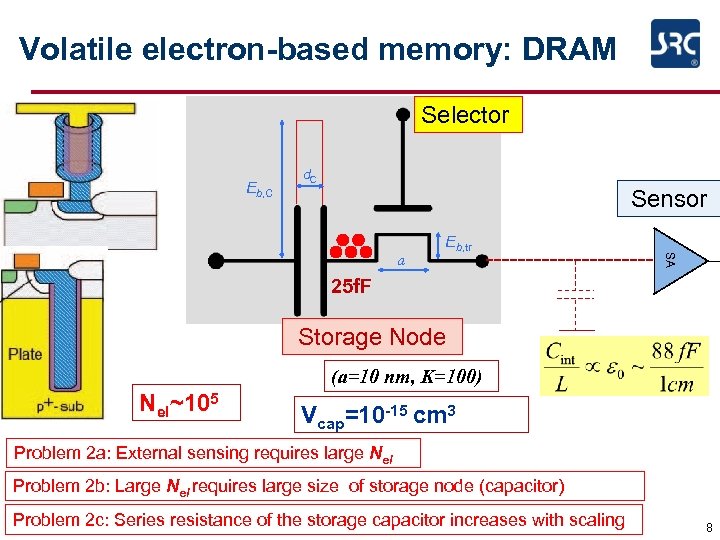

Volatile electron-based memory: DRAM Selector Eb, C d. C Sensor SA a Eb, tr 25 f. F Storage Node (a=10 nm, K=100) Nel~105 Vcap=10 -15 cm 3 Problem 2 a: External sensing requires large Nel Problem 2 b: Large Nel requires large size of storage node (capacitor) Problem 2 c: Series resistance of the storage capacitor increases with scaling 8

Volatile electron-based memory: DRAM Selector Eb, C d. C Sensor SA a Eb, tr 25 f. F Storage Node (a=10 nm, K=100) Nel~105 Vcap=10 -15 cm 3 Problem 2 a: External sensing requires large Nel Problem 2 b: Large Nel requires large size of storage node (capacitor) Problem 2 c: Series resistance of the storage capacitor increases with scaling 8

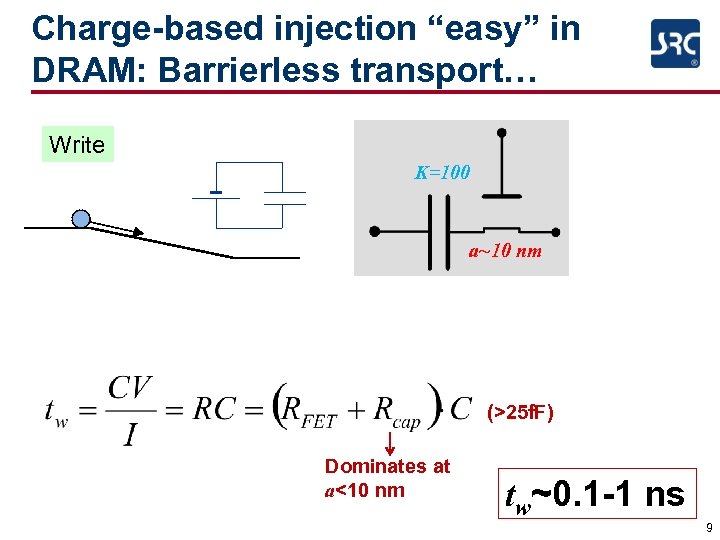

Charge-based injection “easy” in DRAM: Barrierless transport… Write K=100 a~10 nm (>25 f. F) Dominates at a<10 nm tw~0. 1 -1 ns 9

Charge-based injection “easy” in DRAM: Barrierless transport… Write K=100 a~10 nm (>25 f. F) Dominates at a<10 nm tw~0. 1 -1 ns 9

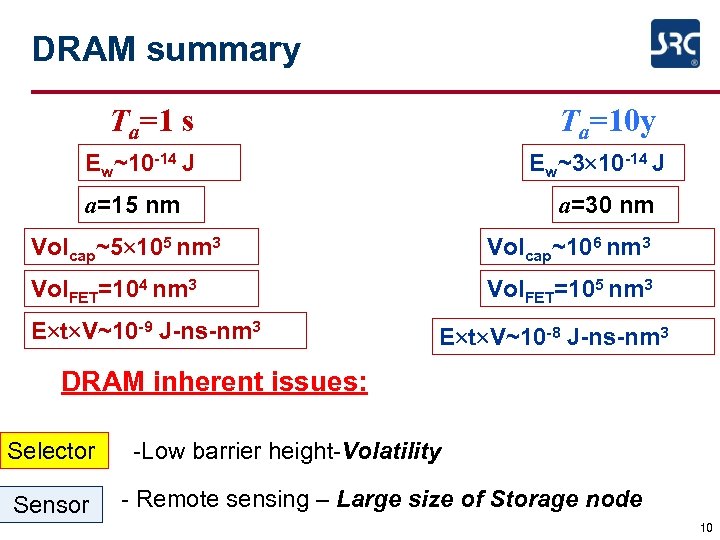

DRAM summary Ta=1 s Ta=10 y Ew~10 -14 J Ew~3 10 -14 J a=15 nm a=30 nm Volcap~5 105 nm 3 Volcap~106 nm 3 Vol. FET=104 nm 3 Vol. FET=105 nm 3 E t V~10 -9 J-ns-nm 3 E t V~10 -8 J-ns-nm 3 DRAM inherent issues: Selector Sensor -Low barrier height-Volatility - Remote sensing – Large size of Storage node 10

DRAM summary Ta=1 s Ta=10 y Ew~10 -14 J Ew~3 10 -14 J a=15 nm a=30 nm Volcap~5 105 nm 3 Volcap~106 nm 3 Vol. FET=104 nm 3 Vol. FET=105 nm 3 E t V~10 -9 J-ns-nm 3 E t V~10 -8 J-ns-nm 3 DRAM inherent issues: Selector Sensor -Low barrier height-Volatility - Remote sensing – Large size of Storage node 10

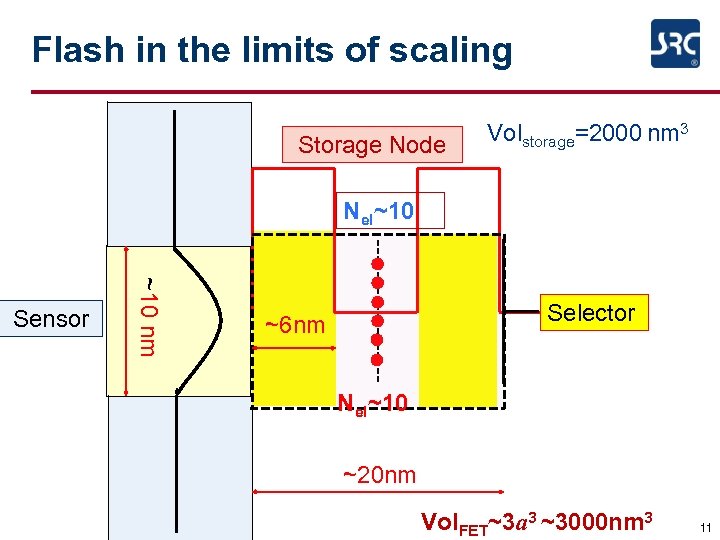

Flash in the limits of scaling Storage Node Volstorage=2000 nm 3 Nel~10 nm Sensor Selector ~6 nm Nel~10 ~20 nm Vol. FET~3 a 3 ~3000 nm 3 11

Flash in the limits of scaling Storage Node Volstorage=2000 nm 3 Nel~10 nm Sensor Selector ~6 nm Nel~10 ~20 nm Vol. FET~3 a 3 ~3000 nm 3 11

Voltage-Time Dilemma u For an arbitrary electron-charge based memory element, there is interdependence between operational voltage, the speed of operation and the retention time. u Specifically, the nonvolatile electron-based memory, suffers from the “barrier” issue: v v High barriers needed for long retention do not allow fast charge injection It is difficult (impossible? ) to match their speed and voltages to logic 12

Voltage-Time Dilemma u For an arbitrary electron-charge based memory element, there is interdependence between operational voltage, the speed of operation and the retention time. u Specifically, the nonvolatile electron-based memory, suffers from the “barrier” issue: v v High barriers needed for long retention do not allow fast charge injection It is difficult (impossible? ) to match their speed and voltages to logic 12

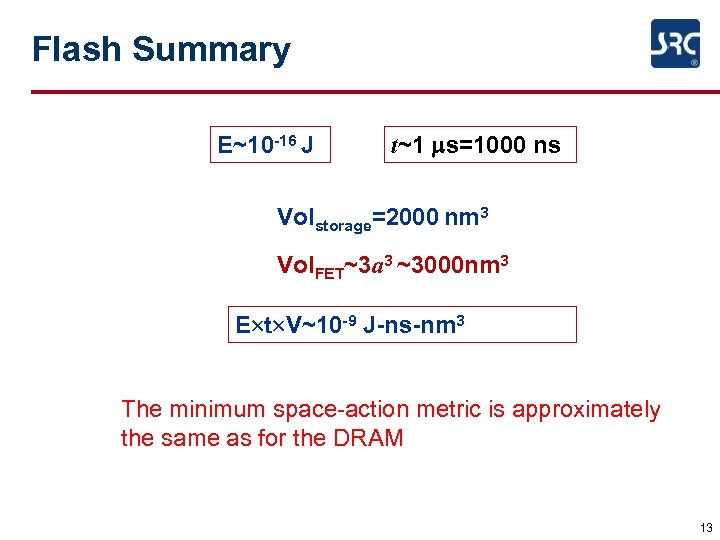

Flash Summary E~10 -16 J t~1 ms=1000 ns Volstorage=2000 nm 3 Vol. FET~3 a 3 ~3000 nm 3 E t V~10 -9 J-ns-nm 3 The minimum space-action metric is approximately the same as for the DRAM 13

Flash Summary E~10 -16 J t~1 ms=1000 ns Volstorage=2000 nm 3 Vol. FET~3 a 3 ~3000 nm 3 E t V~10 -9 J-ns-nm 3 The minimum space-action metric is approximately the same as for the DRAM 13

Conclusion on ultimate chargebased memories u All charge-based memories suffer from the “barrier” issue: v v High barriers needed for long retention do not allow fast charge injection It is difficult (impossible? ) to match their speed and voltages to logic n Voltage-Time Dilemma Non-charge-based NVMs? The Choice of Information Carrier 14

Conclusion on ultimate chargebased memories u All charge-based memories suffer from the “barrier” issue: v v High barriers needed for long retention do not allow fast charge injection It is difficult (impossible? ) to match their speed and voltages to logic n Voltage-Time Dilemma Non-charge-based NVMs? The Choice of Information Carrier 14

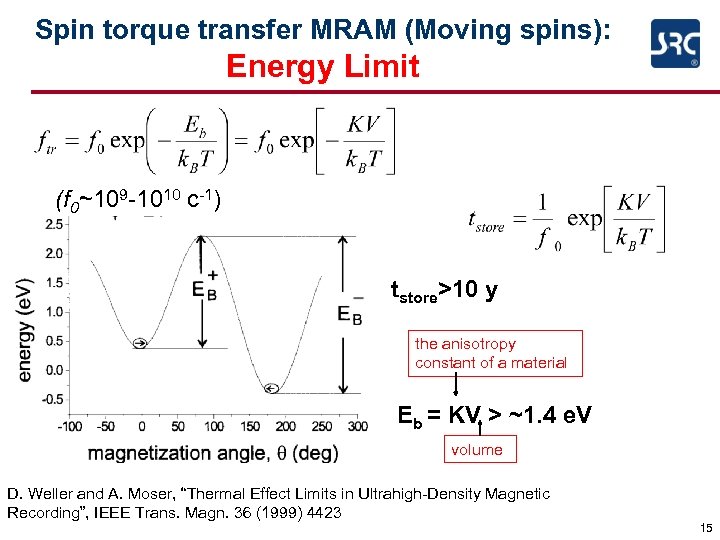

Spin torque transfer MRAM (Moving spins): Energy Limit (f 0~109 -1010 c-1) tstore>10 y the anisotropy constant of a material Eb = KV > ~1. 4 e. V volume D. Weller and A. Moser, “Thermal Effect Limits in Ultrahigh-Density Magnetic Recording”, IEEE Trans. Magn. 36 (1999) 4423 15

Spin torque transfer MRAM (Moving spins): Energy Limit (f 0~109 -1010 c-1) tstore>10 y the anisotropy constant of a material Eb = KV > ~1. 4 e. V volume D. Weller and A. Moser, “Thermal Effect Limits in Ultrahigh-Density Magnetic Recording”, IEEE Trans. Magn. 36 (1999) 4423 15

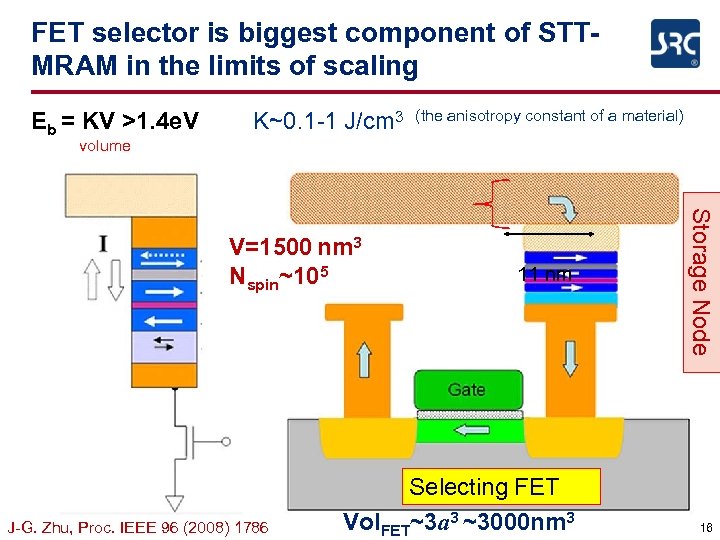

FET selector is biggest component of STTMRAM in the limits of scaling Eb = KV >1. 4 e. V K~0. 1 -1 J/cm 3 (the anisotropy constant of a material) volume J-G. Zhu, Proc. IEEE 96 (2008) 1786 11 nm Selecting FET Vol. FET~3 a 3 ~3000 nm 3 Storage Node V=1500 nm 3 Nspin~105 16

FET selector is biggest component of STTMRAM in the limits of scaling Eb = KV >1. 4 e. V K~0. 1 -1 J/cm 3 (the anisotropy constant of a material) volume J-G. Zhu, Proc. IEEE 96 (2008) 1786 11 nm Selecting FET Vol. FET~3 a 3 ~3000 nm 3 Storage Node V=1500 nm 3 Nspin~105 16

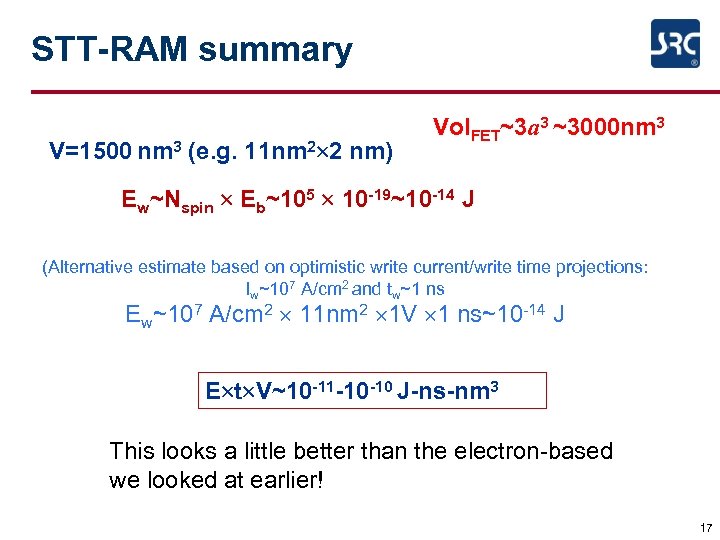

STT-RAM summary V=1500 nm 3 (e. g. 11 nm 2 2 nm) Vol. FET~3 a 3 ~3000 nm 3 Ew~Nspin Eb~105 10 -19~10 -14 J (Alternative estimate based on optimistic write current/write time projections: Iw~107 A/cm 2 and tw~1 ns Ew~107 A/cm 2 11 nm 2 1 V 1 ns~10 -14 J E t V~10 -11 -10 -10 J-ns-nm 3 This looks a little better than the electron-based we looked at earlier! 17

STT-RAM summary V=1500 nm 3 (e. g. 11 nm 2 2 nm) Vol. FET~3 a 3 ~3000 nm 3 Ew~Nspin Eb~105 10 -19~10 -14 J (Alternative estimate based on optimistic write current/write time projections: Iw~107 A/cm 2 and tw~1 ns Ew~107 A/cm 2 11 nm 2 1 V 1 ns~10 -14 J E t V~10 -11 -10 -10 J-ns-nm 3 This looks a little better than the electron-based we looked at earlier! 17

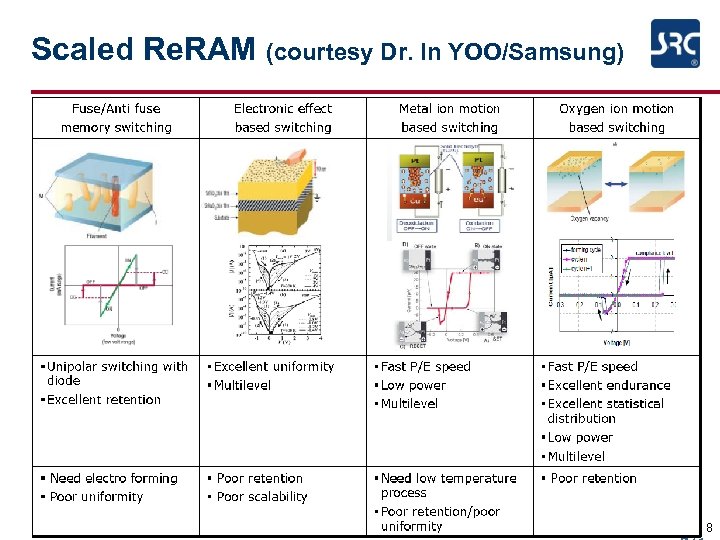

Scaled Re. RAM (courtesy Dr. In YOO/Samsung) 18

Scaled Re. RAM (courtesy Dr. In YOO/Samsung) 18

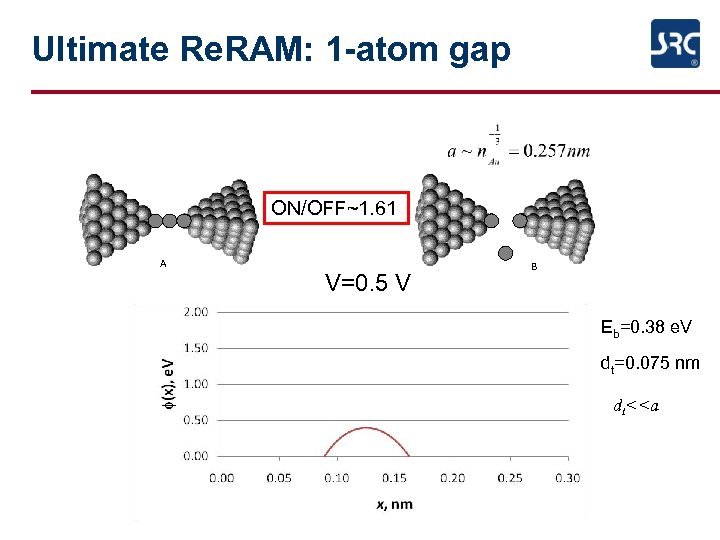

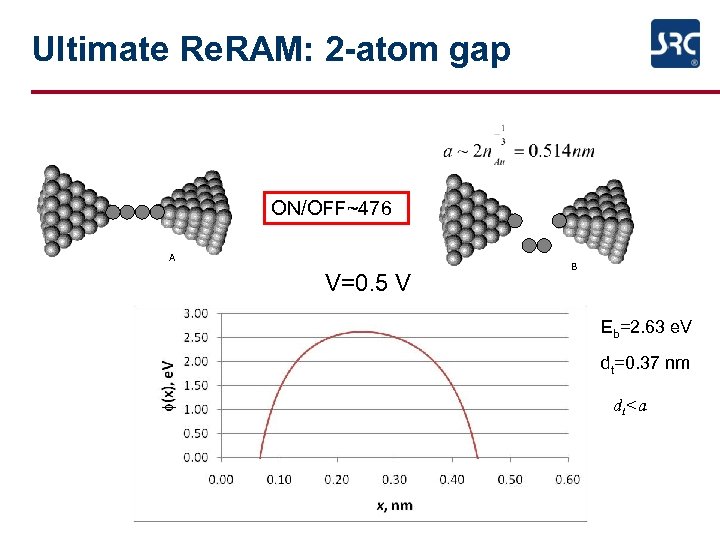

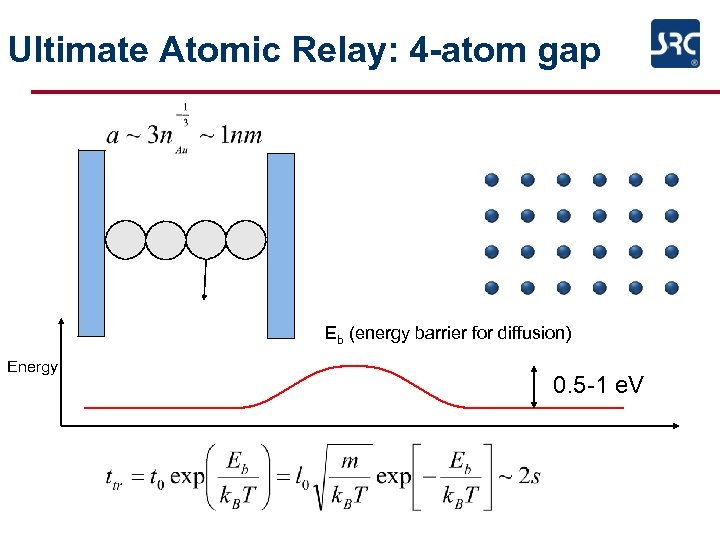

Ultimate Atomic Relay: 4 -atom gap Eb (energy barrier for diffusion) Energy 0. 5 -1 e. V

Ultimate Atomic Relay: 4 -atom gap Eb (energy barrier for diffusion) Energy 0. 5 -1 e. V

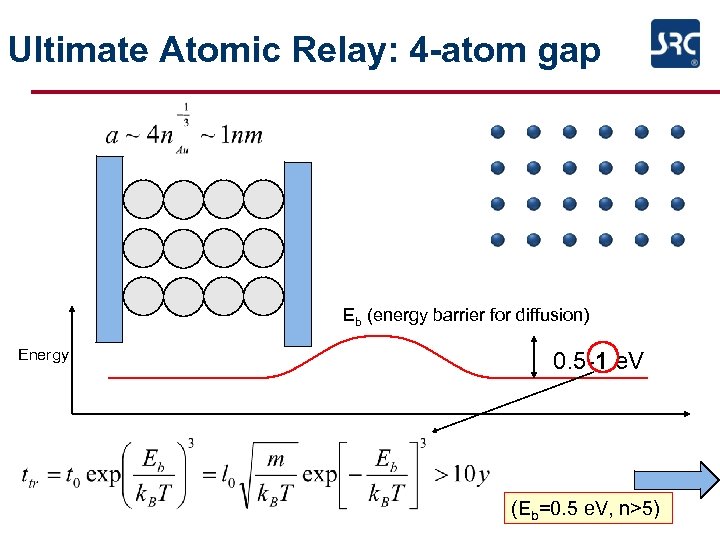

Ultimate Atomic Relay: 4 -atom gap Eb (energy barrier for diffusion) Energy 0. 5 -1 e. V (Eb=0. 5 e. V, n>5)

Ultimate Atomic Relay: 4 -atom gap Eb (energy barrier for diffusion) Energy 0. 5 -1 e. V (Eb=0. 5 e. V, n>5)

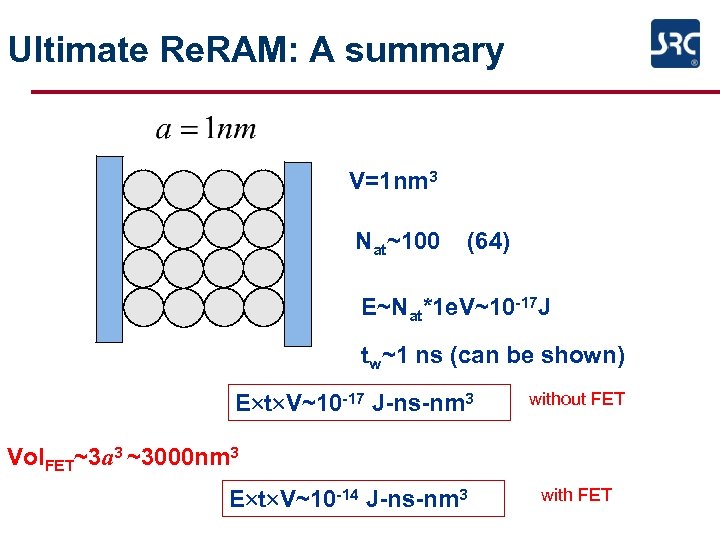

Ultimate Re. RAM: A summary V=1 nm 3 Nat~100 (64) E~Nat*1 e. V~10 -17 J tw~1 ns (can be shown) E t V~10 -17 J-ns-nm 3 without FET Vol. FET~3 a 3 ~3000 nm 3 E t V~10 -14 J-ns-nm 3 with FET

Ultimate Re. RAM: A summary V=1 nm 3 Nat~100 (64) E~Nat*1 e. V~10 -17 J tw~1 ns (can be shown) E t V~10 -17 J-ns-nm 3 without FET Vol. FET~3 a 3 ~3000 nm 3 E t V~10 -14 J-ns-nm 3 with FET

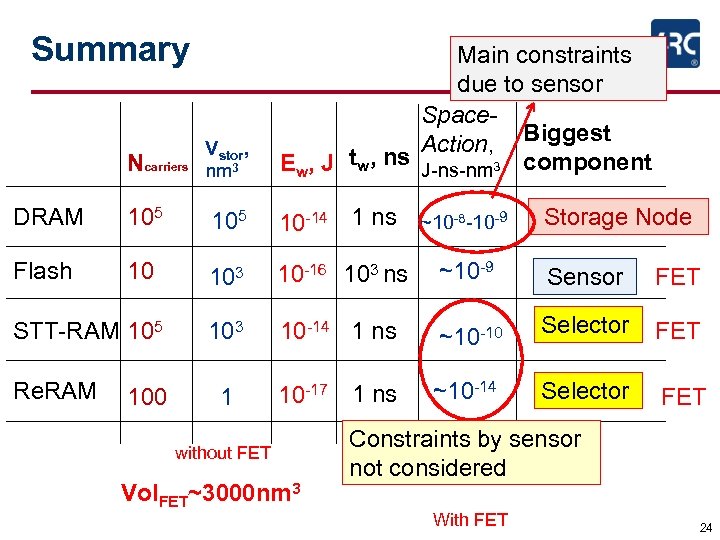

Summary Ncarriers Vstor, nm 3 Main constraints due to sensor Space. Action, Biggest Ew, J tw, ns J-ns-nm 3 component DRAM 105 10 -14 1 ns ~10 -8 -10 -9 Flash 10 103 10 -16 103 ns ~10 -9 Sensor FET 103 10 -14 1 ns ~10 -10 Selector FET 1 ns ~10 -14 Selector FET STT-RAM 105 Re. RAM 100 1 10 -17 without FET Vol. FET~3000 nm 3 Storage Node Constraints by sensor not considered With FET 24

Summary Ncarriers Vstor, nm 3 Main constraints due to sensor Space. Action, Biggest Ew, J tw, ns J-ns-nm 3 component DRAM 105 10 -14 1 ns ~10 -8 -10 -9 Flash 10 103 10 -16 103 ns ~10 -9 Sensor FET 103 10 -14 1 ns ~10 -10 Selector FET 1 ns ~10 -14 Selector FET STT-RAM 105 Re. RAM 100 1 10 -17 without FET Vol. FET~3000 nm 3 Storage Node Constraints by sensor not considered With FET 24

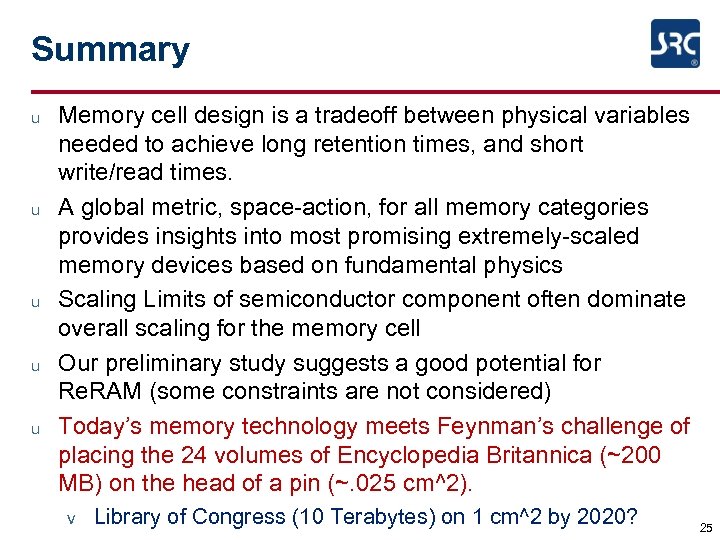

Summary u u u Memory cell design is a tradeoff between physical variables needed to achieve long retention times, and short write/read times. A global metric, space-action, for all memory categories provides insights into most promising extremely-scaled memory devices based on fundamental physics Scaling Limits of semiconductor component often dominate overall scaling for the memory cell Our preliminary study suggests a good potential for Re. RAM (some constraints are not considered) Today’s memory technology meets Feynman’s challenge of placing the 24 volumes of Encyclopedia Britannica (~200 MB) on the head of a pin (~. 025 cm^2). v Library of Congress (10 Terabytes) on 1 cm^2 by 2020? 25

Summary u u u Memory cell design is a tradeoff between physical variables needed to achieve long retention times, and short write/read times. A global metric, space-action, for all memory categories provides insights into most promising extremely-scaled memory devices based on fundamental physics Scaling Limits of semiconductor component often dominate overall scaling for the memory cell Our preliminary study suggests a good potential for Re. RAM (some constraints are not considered) Today’s memory technology meets Feynman’s challenge of placing the 24 volumes of Encyclopedia Britannica (~200 MB) on the head of a pin (~. 025 cm^2). v Library of Congress (10 Terabytes) on 1 cm^2 by 2020? 25