® Multi-Port SRAM Overview 8/9/99 09100 - Overview - Multi-Port SRAM Slide

® Multi-Port SRAM Overview 8/9/99 09100 - Overview - Multi-Port SRAM Slide

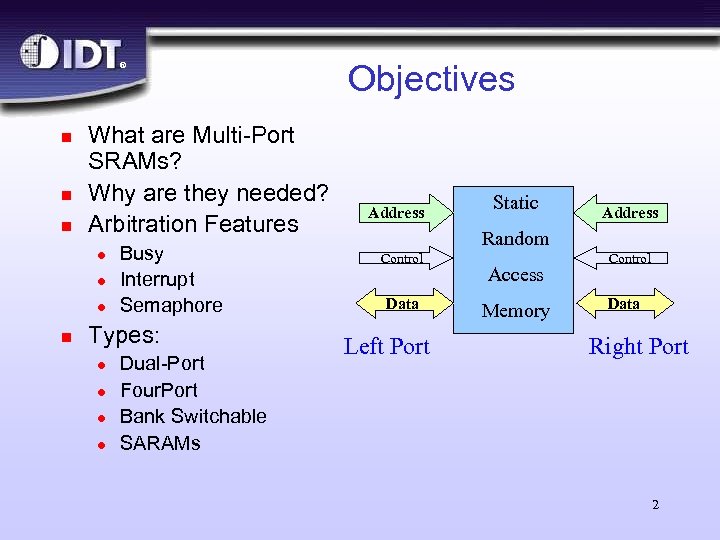

® n n n What are Multi-Port SRAMs? Why are they needed? Arbitration Features l l l n Busy Interrupt Semaphore Types: l l Dual-Port Four. Port Bank Switchable SARAMs Objectives Address Static Address Random Control Data Left Port Access Memory Control Data Right Port 2

® n n n What are Multi-Port SRAMs? Why are they needed? Arbitration Features l l l n Busy Interrupt Semaphore Types: l l Dual-Port Four. Port Bank Switchable SARAMs Objectives Address Static Address Random Control Data Left Port Access Memory Control Data Right Port 2

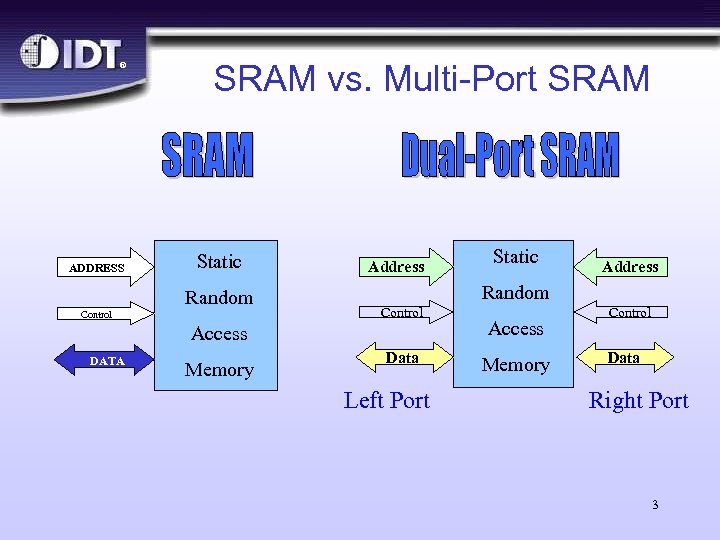

® ADDRESS Control SRAM vs. Multi-Port SRAM Static Random Address Memory Address Random Control Access DATA Static Data Left Port Access Memory Control Data Right Port 3

® ADDRESS Control SRAM vs. Multi-Port SRAM Static Random Address Memory Address Random Control Access DATA Static Data Left Port Access Memory Control Data Right Port 3

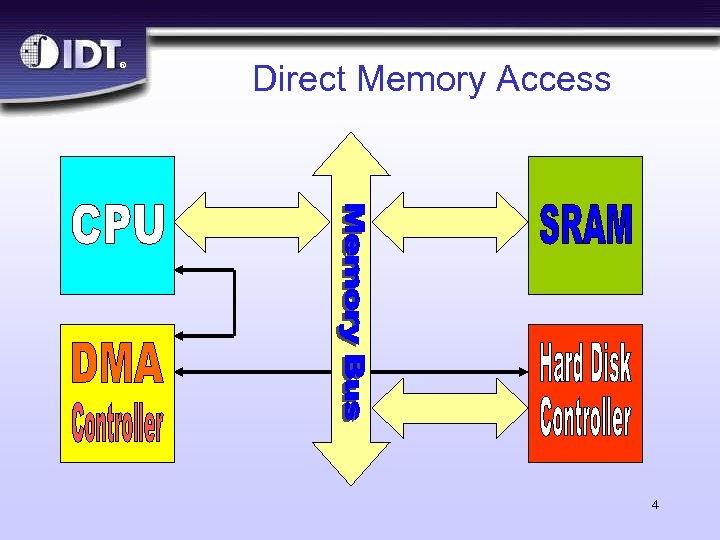

® Direct Memory Access 4

® Direct Memory Access 4

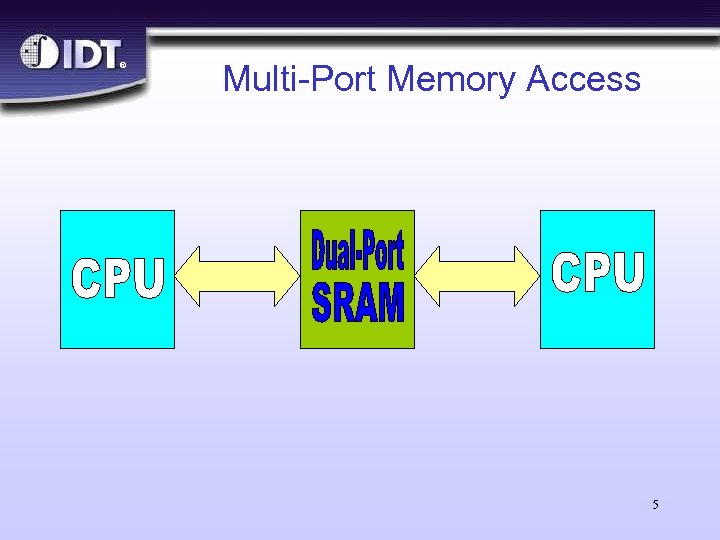

® Multi-Port Memory Access 5

® Multi-Port Memory Access 5

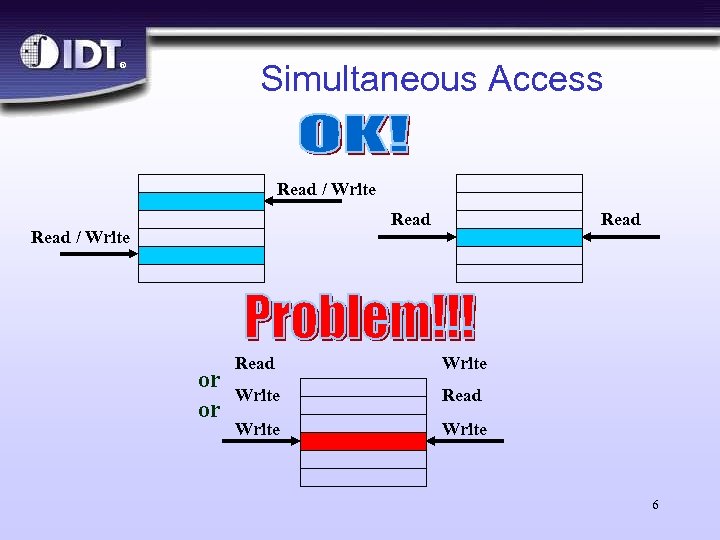

Simultaneous Access ® Read / Write or or Read Write 6

Simultaneous Access ® Read / Write or or Read Write 6

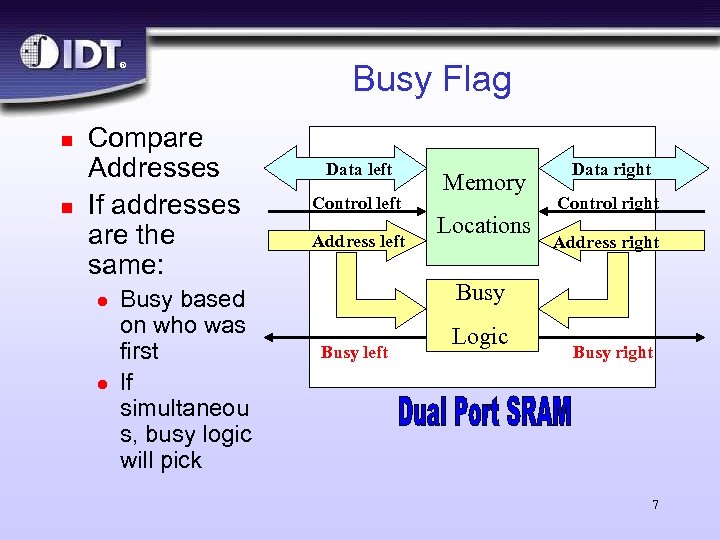

® n n Compare Addresses If addresses are the same: l l Busy based on who was first If simultaneou s, busy logic will pick Busy Flag Data left Control left Address left Memory Locations Data right Control right Address right Busy left Logic Busy right 7

® n n Compare Addresses If addresses are the same: l l Busy based on who was first If simultaneou s, busy logic will pick Busy Flag Data left Control left Address left Memory Locations Data right Control right Address right Busy left Logic Busy right 7

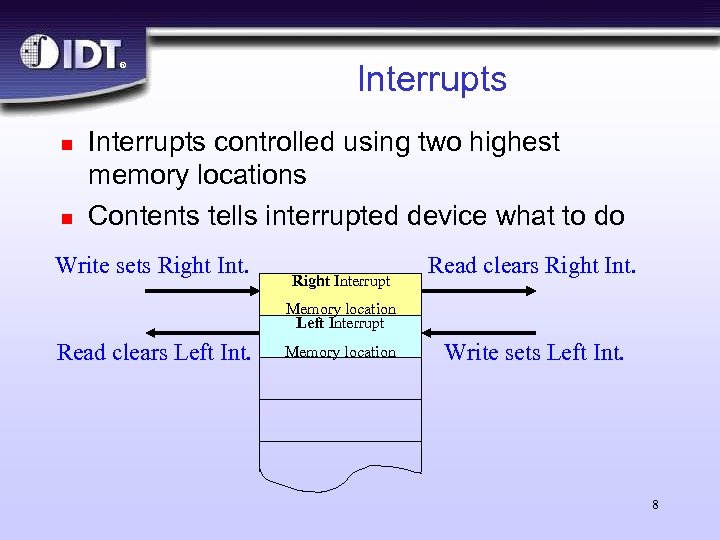

® n n Interrupts controlled using two highest memory locations Contents tells interrupted device what to do Write sets Right Interrupt Read clears Right Int. Memory location Left Interrupt Read clears Left Int. Memory location Write sets Left Int. 8

® n n Interrupts controlled using two highest memory locations Contents tells interrupted device what to do Write sets Right Interrupt Read clears Right Int. Memory location Left Interrupt Read clears Left Int. Memory location Write sets Left Int. 8

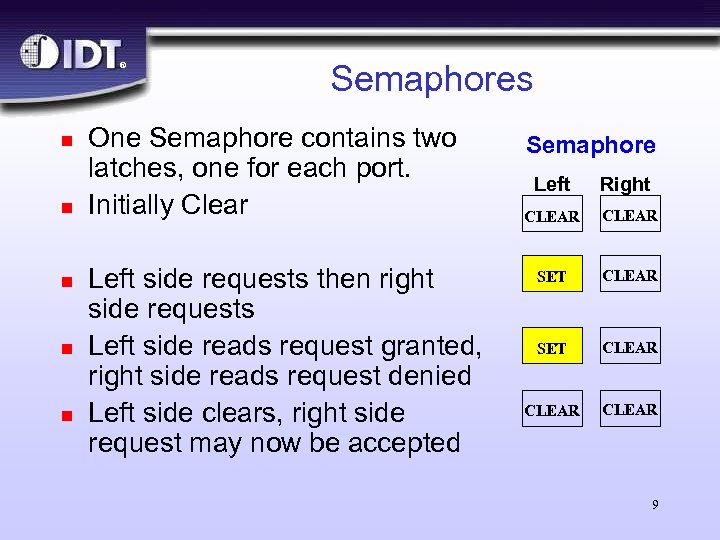

® n n n Semaphores One Semaphore contains two latches, one for each port. Initially Clear Left side requests then right side requests Left side reads request granted, right side reads request denied Left side clears, right side request may now be accepted Semaphore Left Right CLEAR SET CLEAR 9

® n n n Semaphores One Semaphore contains two latches, one for each port. Initially Clear Left side requests then right side requests Left side reads request granted, right side reads request denied Left side clears, right side request may now be accepted Semaphore Left Right CLEAR SET CLEAR 9

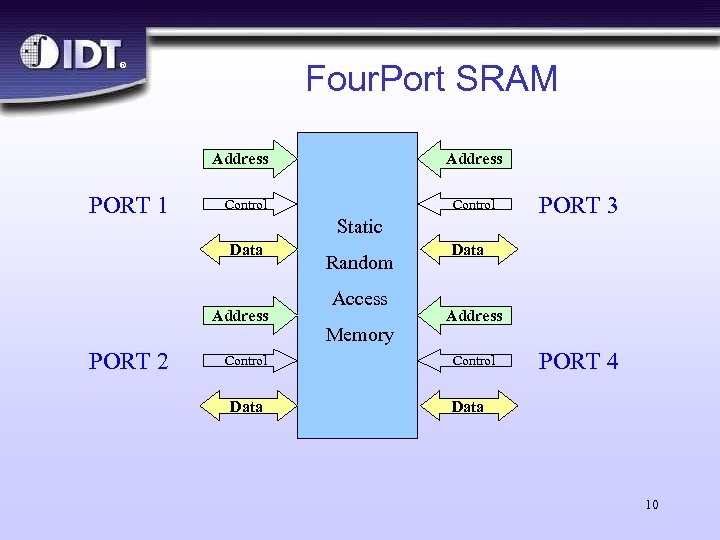

Four. Port SRAM ® Address PORT 1 Control Static Data Address PORT 2 Address Control Data Random Access Memory PORT 3 Data Address Control PORT 4 Data 10

Four. Port SRAM ® Address PORT 1 Control Static Data Address PORT 2 Address Control Data Random Access Memory PORT 3 Data Address Control PORT 4 Data 10

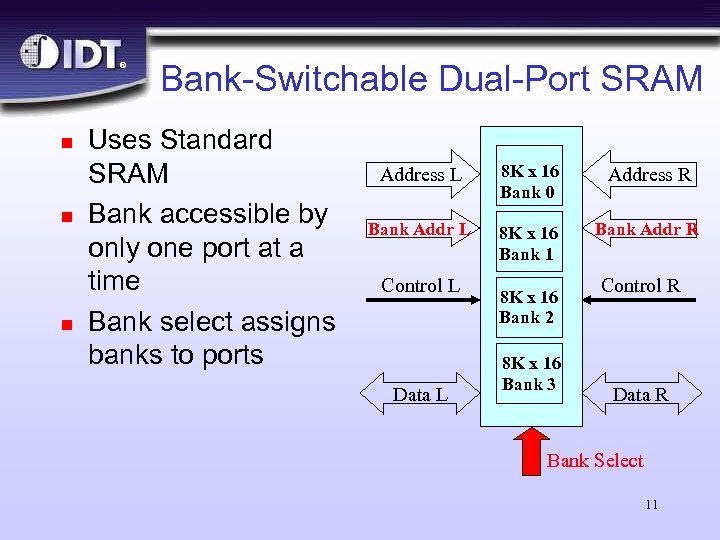

® n n n Bank-Switchable Dual-Port SRAM Uses Standard SRAM Bank accessible by only one port at a time Bank select assigns banks to ports Address L 8 K x 16 Bank 0 Address R Bank Addr L 8 K x 16 Bank 1 Bank Addr R Control L Data L 8 K x 16 Bank 2 8 K x 16 Bank 3 Control R Data R Bank Select 11

® n n n Bank-Switchable Dual-Port SRAM Uses Standard SRAM Bank accessible by only one port at a time Bank select assigns banks to ports Address L 8 K x 16 Bank 0 Address R Bank Addr L 8 K x 16 Bank 1 Bank Addr R Control L Data L 8 K x 16 Bank 2 8 K x 16 Bank 3 Control R Data R Bank Select 11

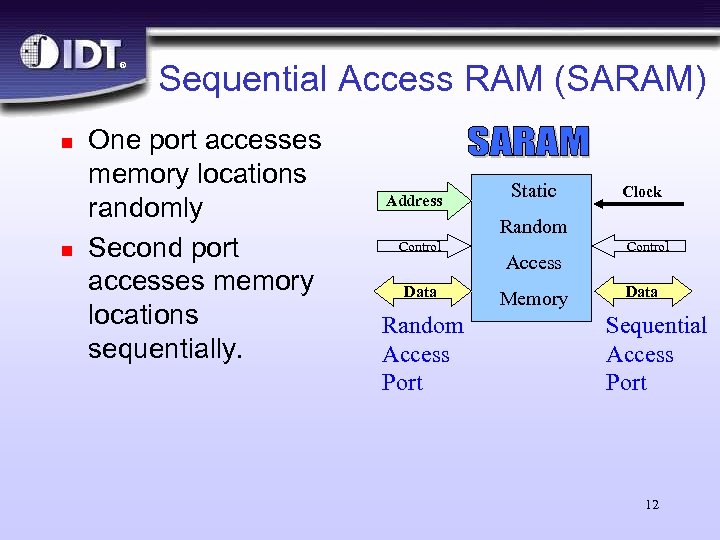

® n n Sequential Access RAM (SARAM) One port accesses memory locations randomly Second port accesses memory locations sequentially. Address Static Clock Random Control Data Random Access Port Access Memory Control Data Sequential Access Port 12

® n n Sequential Access RAM (SARAM) One port accesses memory locations randomly Second port accesses memory locations sequentially. Address Static Clock Random Control Data Random Access Port Access Memory Control Data Sequential Access Port 12

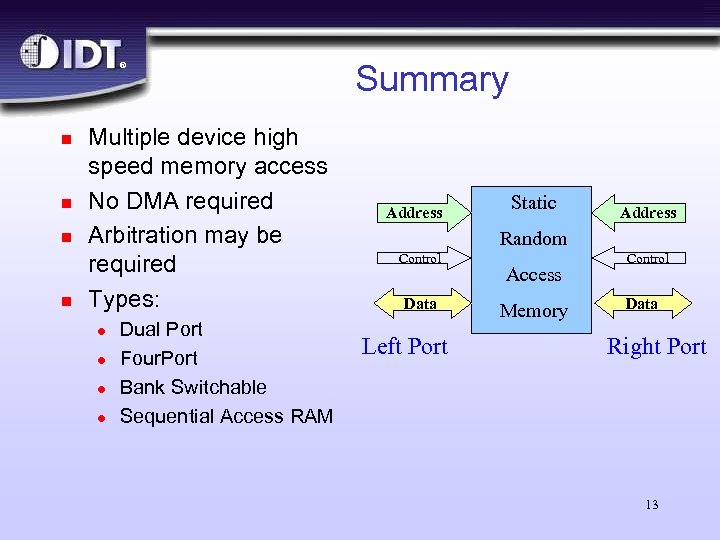

® n n Multiple device high speed memory access No DMA required Arbitration may be required Types: l l Dual Port Four. Port Bank Switchable Sequential Access RAM Summary Address Static Address Random Control Data Left Port Access Memory Control Data Right Port 13

® n n Multiple device high speed memory access No DMA required Arbitration may be required Types: l l Dual Port Four. Port Bank Switchable Sequential Access RAM Summary Address Static Address Random Control Data Left Port Access Memory Control Data Right Port 13