80e2dd74fb4425869330620fdeaa173b.ppt

- Количество слайдов: 44

Module 1: So. C System Specification, Languages, Model 최해욱 (ICU, 공학부)

Module 1: So. C System Specification, Languages, Model 최해욱 (ICU, 공학부)

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model (모듈1: System Specification/Model/Analysis) 목차 n Introduction n So. C Specification n Specification Languages n So. C Model Copyrightⓒ 2003 2

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model (모듈1: System Specification/Model/Analysis) 목차 n Introduction n So. C Specification n Specification Languages n So. C Model Copyrightⓒ 2003 2

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model So. C: System-On-Chip Definition A complex IC that integrates the major functional elements of a complete end-product into a single chip. General So. C Organization: hardware - at least one programmable processor - on-chip memory - accelerating function units implemented in hardware. - interfaces to peripheral devices - interfaces to real world (analog & O/MEMS components) software - Real time OS - Device Drivers O/MEMS: opto/microelectronic mechanical system Copyrightⓒ 2003 3

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model So. C: System-On-Chip Definition A complex IC that integrates the major functional elements of a complete end-product into a single chip. General So. C Organization: hardware - at least one programmable processor - on-chip memory - accelerating function units implemented in hardware. - interfaces to peripheral devices - interfaces to real world (analog & O/MEMS components) software - Real time OS - Device Drivers O/MEMS: opto/microelectronic mechanical system Copyrightⓒ 2003 3

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model So. C: System-On-Chip (Cont’d) System Viewpoint A collection of all kinds of components and/or subsystems that are appropriately interconnected to perform the specified functions for end users. An So. C design is a “product creation process” which Starts at identifying the end-user needs Ends at delivering a product with enough functional satisfaction to overcome the payment from the end-user Copyrightⓒ 2003 4

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model So. C: System-On-Chip (Cont’d) System Viewpoint A collection of all kinds of components and/or subsystems that are appropriately interconnected to perform the specified functions for end users. An So. C design is a “product creation process” which Starts at identifying the end-user needs Ends at delivering a product with enough functional satisfaction to overcome the payment from the end-user Copyrightⓒ 2003 4

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model So. C Applications Communication Digital cellular phone Networking Computer PC/Workstation Chipsets Consumer Game box Digital Camera Copyrightⓒ 2003 5

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model So. C Applications Communication Digital cellular phone Networking Computer PC/Workstation Chipsets Consumer Game box Digital Camera Copyrightⓒ 2003 5

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Benefits of Using So. C Reduced size Reduced overall system cost Lower power consumption Increased performance Copyrightⓒ 2003 6

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Benefits of Using So. C Reduced size Reduced overall system cost Lower power consumption Increased performance Copyrightⓒ 2003 6

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Success So. Cs or Platforms ■ The Philips Nexperia Digital Video Platform ■ The TI OMAP Platform Copyrightⓒ 2003 7

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Success So. Cs or Platforms ■ The Philips Nexperia Digital Video Platform ■ The TI OMAP Platform Copyrightⓒ 2003 7

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Characteristics of Philips Nexperia Platform Approach ■ Flexibility for easy differentiation and product upgradeability (through programmability and extensive S/W & H/W IP choice) ■ Innovation – addressing new, exciting, consumer applications ■ Future-proof via S/W upgrade ability and a roadmap of compatible platform instances ■ The use of an architecture framework and IP blocks to flesh out designs Copyrightⓒ 2003 8

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Characteristics of Philips Nexperia Platform Approach ■ Flexibility for easy differentiation and product upgradeability (through programmability and extensive S/W & H/W IP choice) ■ Innovation – addressing new, exciting, consumer applications ■ Future-proof via S/W upgrade ability and a roadmap of compatible platform instances ■ The use of an architecture framework and IP blocks to flesh out designs Copyrightⓒ 2003 8

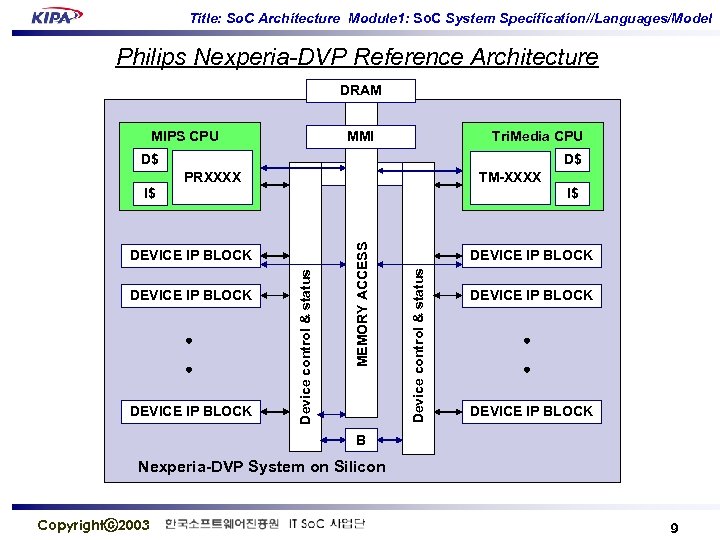

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Philips Nexperia-DVP Reference Architecture DRAM MMI MIPS CPU Tri. Media CPU D$ D$ PRXXXX TM-XXXX I$ DEVICE IP BLOCK Device control & status DEVICE IP BLOCK MEMORY ACCESS I$ DEVICE IP BLOCK B Nexperia-DVP System on Silicon Copyrightⓒ 2003 9

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Philips Nexperia-DVP Reference Architecture DRAM MMI MIPS CPU Tri. Media CPU D$ D$ PRXXXX TM-XXXX I$ DEVICE IP BLOCK Device control & status DEVICE IP BLOCK MEMORY ACCESS I$ DEVICE IP BLOCK B Nexperia-DVP System on Silicon Copyrightⓒ 2003 9

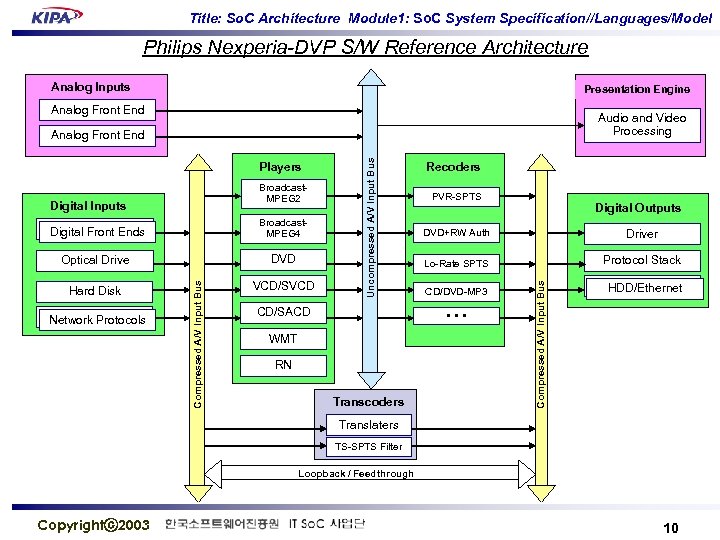

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Philips Nexperia-DVP S/W Reference Architecture Analog Inputs Presentation Engine Analog Front End Audio and Video Processing Broadcast. MPEG 2 Digital Inputs Optical Drive DVD Hard Disk VCD/SVCD Network Protocols Compressed A/V Input Bus Analog Front Ends Digital Front End Broadcast. MPEG 4 CD/SACD Recoders PVR-SPTS DVD+RW Auth Driver Lo-Rate SPTS Protocol Stack CD/DVD-MP 3 Network Protocols HDD/Ethernet WMT RN Transcoders Digital Outputs Compressed A/V Input Bus Players Uncompressed A/V Input Bus Analog Front End Translaters TS-SPTS Filter Loopback / Feedthrough Copyrightⓒ 2003 10

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Philips Nexperia-DVP S/W Reference Architecture Analog Inputs Presentation Engine Analog Front End Audio and Video Processing Broadcast. MPEG 2 Digital Inputs Optical Drive DVD Hard Disk VCD/SVCD Network Protocols Compressed A/V Input Bus Analog Front Ends Digital Front End Broadcast. MPEG 4 CD/SACD Recoders PVR-SPTS DVD+RW Auth Driver Lo-Rate SPTS Protocol Stack CD/DVD-MP 3 Network Protocols HDD/Ethernet WMT RN Transcoders Digital Outputs Compressed A/V Input Bus Players Uncompressed A/V Input Bus Analog Front End Translaters TS-SPTS Filter Loopback / Feedthrough Copyrightⓒ 2003 10

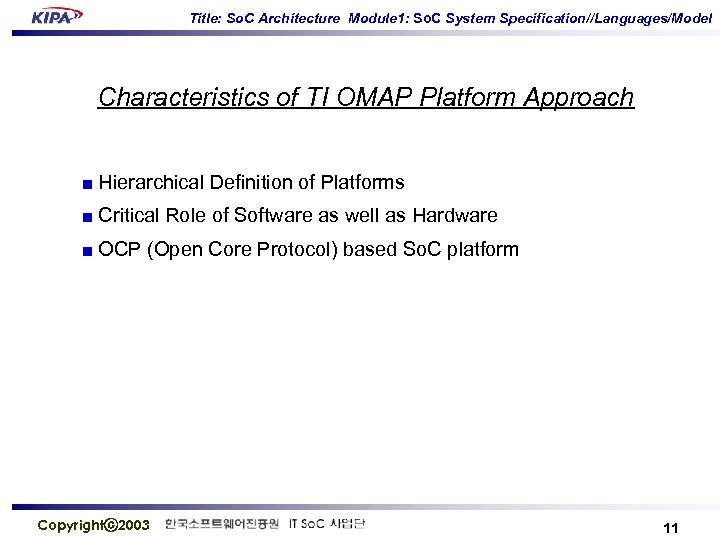

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Characteristics of TI OMAP Platform Approach ■ Hierarchical Definition of Platforms ■ Critical Role of Software as well as Hardware ■ OCP (Open Core Protocol) based So. C platform Copyrightⓒ 2003 11

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Characteristics of TI OMAP Platform Approach ■ Hierarchical Definition of Platforms ■ Critical Role of Software as well as Hardware ■ OCP (Open Core Protocol) based So. C platform Copyrightⓒ 2003 11

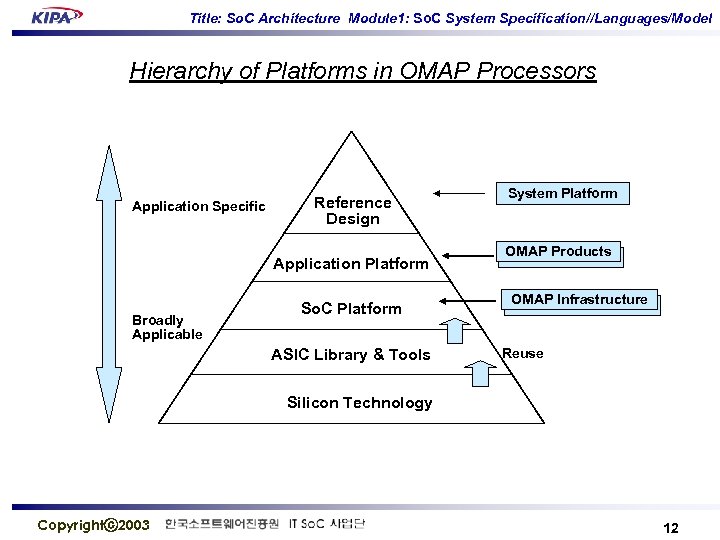

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Hierarchy of Platforms in OMAP Processors Application Specific Reference Design Application Platform Broadly Applicable So. C Platform ASIC Library & Tools System Platform OMAP Products OMAP Infrastructure Reuse Silicon Technology Copyrightⓒ 2003 12

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Hierarchy of Platforms in OMAP Processors Application Specific Reference Design Application Platform Broadly Applicable So. C Platform ASIC Library & Tools System Platform OMAP Products OMAP Infrastructure Reuse Silicon Technology Copyrightⓒ 2003 12

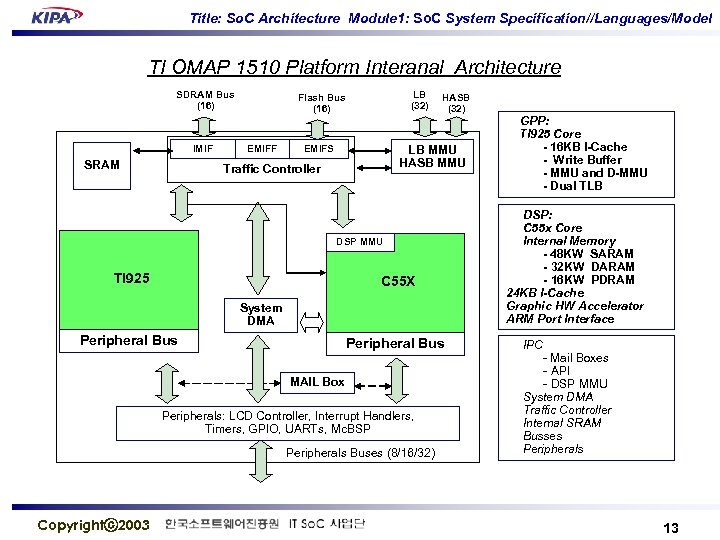

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model TI OMAP 1510 Platform Interanal Architecture SDRAM Bus (16) IMIF SRAM LB (32) Flash Bus (16) EMIFF EMIFS HASB (32) LB MMU HASB MMU Traffic Controller DSP MMU TI 925 C 55 X System DMA Peripheral Bus MAIL Box Peripherals: LCD Controller, Interrupt Handlers, Timers, GPIO, UARTs, Mc. BSP Peripherals Buses (8/16/32) Copyrightⓒ 2003 GPP: TI 925 Core - 16 KB I-Cache - Write Buffer - MMU and D-MMU - Dual TLB DSP: C 55 x Core Internal Memory - 48 KW SARAM - 32 KW DARAM - 16 KW PDRAM 24 KB I-Cache Graphic HW Accelerator ARM Port Interface IPC - Mail Boxes - API - DSP MMU System DMA Traffic Controller Internal SRAM Busses Peripherals 13

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model TI OMAP 1510 Platform Interanal Architecture SDRAM Bus (16) IMIF SRAM LB (32) Flash Bus (16) EMIFF EMIFS HASB (32) LB MMU HASB MMU Traffic Controller DSP MMU TI 925 C 55 X System DMA Peripheral Bus MAIL Box Peripherals: LCD Controller, Interrupt Handlers, Timers, GPIO, UARTs, Mc. BSP Peripherals Buses (8/16/32) Copyrightⓒ 2003 GPP: TI 925 Core - 16 KB I-Cache - Write Buffer - MMU and D-MMU - Dual TLB DSP: C 55 x Core Internal Memory - 48 KW SARAM - 32 KW DARAM - 16 KW PDRAM 24 KB I-Cache Graphic HW Accelerator ARM Port Interface IPC - Mail Boxes - API - DSP MMU System DMA Traffic Controller Internal SRAM Busses Peripherals 13

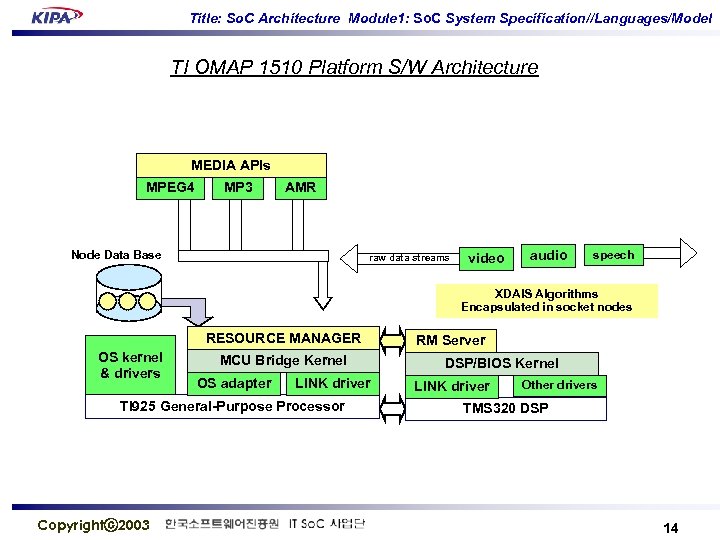

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model TI OMAP 1510 Platform S/W Architecture MEDIA APIs MPEG 4 MP 3 AMR Node Data Base raw data streams video audio speech XDAIS Algorithms Encapsulated in socket nodes RESOURCE MANAGER OS kernel & drivers MCU Bridge Kernel OS adapter LINK driver TI 925 General-Purpose Processor Copyrightⓒ 2003 RM Server DSP/BIOS Kernel LINK driver Other drivers TMS 320 DSP 14

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model TI OMAP 1510 Platform S/W Architecture MEDIA APIs MPEG 4 MP 3 AMR Node Data Base raw data streams video audio speech XDAIS Algorithms Encapsulated in socket nodes RESOURCE MANAGER OS kernel & drivers MCU Bridge Kernel OS adapter LINK driver TI 925 General-Purpose Processor Copyrightⓒ 2003 RM Server DSP/BIOS Kernel LINK driver Other drivers TMS 320 DSP 14

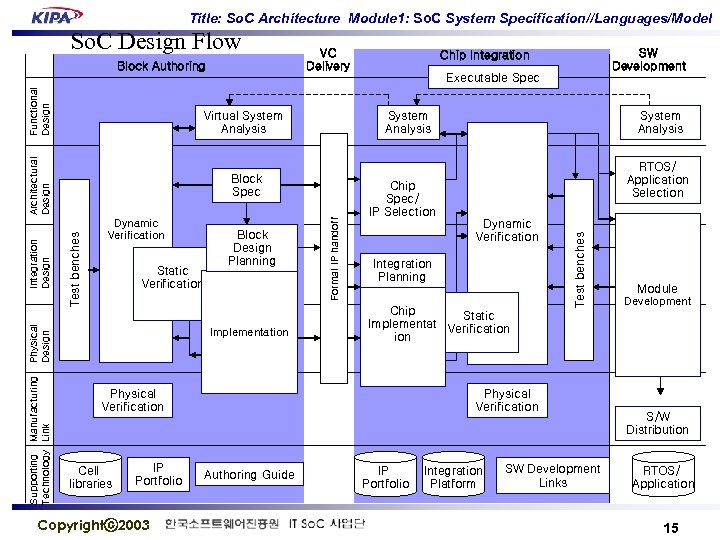

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Functional Design Block Authoring Static Verification Block Design Planning Implementation Formal IP handoff Dynamic Verification Executable Spec IP Portfolio Copyrightⓒ 2003 System Analysis RTOS/ Application Selection Chip Spec/ IP Selection Dynamic Verification Integration Planning Chip Static Implementat Verification Physical Verification Cell libraries SW Development Chip Integration System Analysis Block Spec Test benches Integration Design Architectural Design Virtual System Analysis Physical Design Supporting Manufacturing Technology Link VC Delivery Test benches So. C Design Flow Physical Verification Authoring Guide IP Portfolio Integration Platform SW Development Links Module Development S/W Distribution RTOS/ Application 15

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Functional Design Block Authoring Static Verification Block Design Planning Implementation Formal IP handoff Dynamic Verification Executable Spec IP Portfolio Copyrightⓒ 2003 System Analysis RTOS/ Application Selection Chip Spec/ IP Selection Dynamic Verification Integration Planning Chip Static Implementat Verification Physical Verification Cell libraries SW Development Chip Integration System Analysis Block Spec Test benches Integration Design Architectural Design Virtual System Analysis Physical Design Supporting Manufacturing Technology Link VC Delivery Test benches So. C Design Flow Physical Verification Authoring Guide IP Portfolio Integration Platform SW Development Links Module Development S/W Distribution RTOS/ Application 15

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model The History of the So. C n The History of the System-on-Chip o The Glorious Hope (1995 -1999) o The Reign of Terror: Reality & disappointment (1999 -2001) o Thermidor: Platform transformation (2000 -2002) o L’Avenir: The radiant future? Copyrightⓒ 2003 16

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model The History of the So. C n The History of the System-on-Chip o The Glorious Hope (1995 -1999) o The Reign of Terror: Reality & disappointment (1999 -2001) o Thermidor: Platform transformation (2000 -2002) o L’Avenir: The radiant future? Copyrightⓒ 2003 16

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model n The Glorious Hope (1995 -1999) o Productivity Gap vs. IP based design o 3 Seminal Events o VSIA (1996) : Virtual Socket Interface Association, aiming to reduce the confusion & design bottlenecks involved with IP reuse at the hard, firm & soft levels through the identification of de facto standards in use for IP development, exchange & integration, & the creation of new standards. o RMM (1998 & 1999) : Reuse Methodology Manual by Michael Keating & Pierre Bricaud, describing a series of guidelines and rules for effective creation and reuse of individual soft & hard IP blocks, system level integration and verification, etc. o ALBA (1996~ Present): Scotland government sponsored academicindustry-government collaborative project to support, enhance and attract So. C design activities by establishing of 3 key pillars, the institute for system level integration (ISLI), a business infrastructure, the Virtual Component Exchange or VCX, a dedicated ALBA center for So. C companies. Copyrightⓒ 2003 17

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model n The Glorious Hope (1995 -1999) o Productivity Gap vs. IP based design o 3 Seminal Events o VSIA (1996) : Virtual Socket Interface Association, aiming to reduce the confusion & design bottlenecks involved with IP reuse at the hard, firm & soft levels through the identification of de facto standards in use for IP development, exchange & integration, & the creation of new standards. o RMM (1998 & 1999) : Reuse Methodology Manual by Michael Keating & Pierre Bricaud, describing a series of guidelines and rules for effective creation and reuse of individual soft & hard IP blocks, system level integration and verification, etc. o ALBA (1996~ Present): Scotland government sponsored academicindustry-government collaborative project to support, enhance and attract So. C design activities by establishing of 3 key pillars, the institute for system level integration (ISLI), a business infrastructure, the Virtual Component Exchange or VCX, a dedicated ALBA center for So. C companies. Copyrightⓒ 2003 17

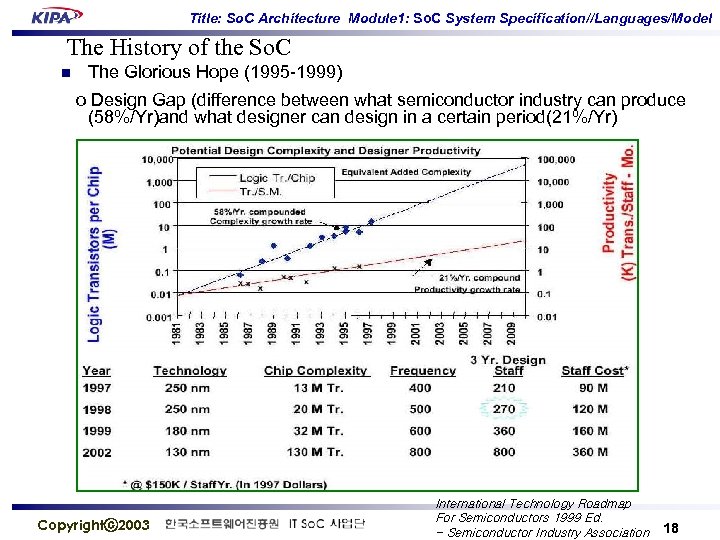

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model The History of the So. C n The Glorious Hope (1995 -1999) o Design Gap (difference between what semiconductor industry can produce (58%/Yr)and what designer can design in a certain period(21%/Yr) Copyrightⓒ 2003 International Technology Roadmap For Semiconductors 1999 Ed. - Semiconductor Industry Association 18

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model The History of the So. C n The Glorious Hope (1995 -1999) o Design Gap (difference between what semiconductor industry can produce (58%/Yr)and what designer can design in a certain period(21%/Yr) Copyrightⓒ 2003 International Technology Roadmap For Semiconductors 1999 Ed. - Semiconductor Industry Association 18

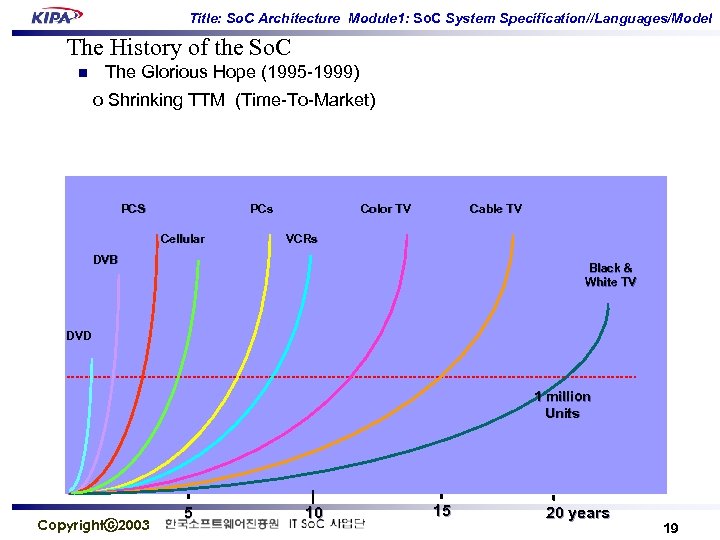

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model The History of the So. C n The Glorious Hope (1995 -1999) o Shrinking TTM (Time-To-Market) PCS PCs Cellular Color TV Cable TV VCRs DVB Black & White TV DVD 1 million Units Copyrightⓒ 2003 5 10 15 20 years 19

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model The History of the So. C n The Glorious Hope (1995 -1999) o Shrinking TTM (Time-To-Market) PCS PCs Cellular Color TV Cable TV VCRs DVB Black & White TV DVD 1 million Units Copyrightⓒ 2003 5 10 15 20 years 19

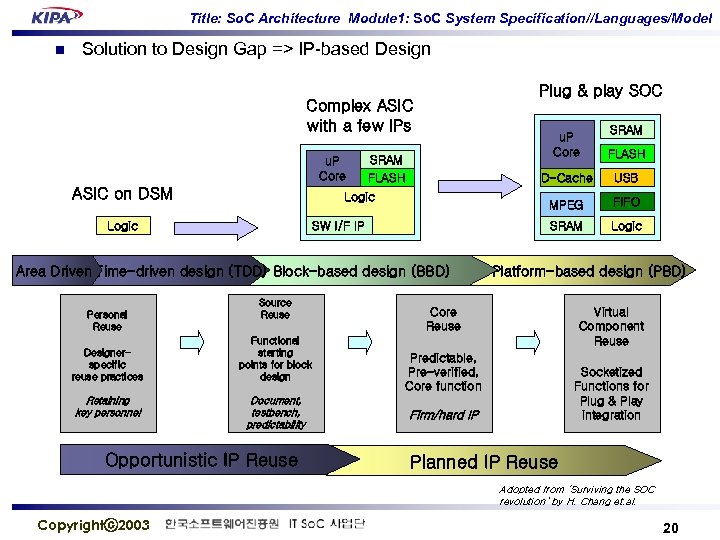

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model n Solution to Design Gap => IP-based Design Plug & play SOC Complex ASIC with a few IPs u. P Core ASIC on DSM Personal Reuse Designerspecific reuse practices Retaining key personnel Source Reuse Functional starting points for block design Document, testbench, predictability Opportunistic IP Reuse FIFO SRAM Area Driven Time-driven design (TDD) Block-based design (BBD) USB MPEG SW I/F IP FLASH D-Cache SRAM FLASH Logic SRAM u. P Core Logic Platform-based design (PBD) Core Reuse Virtual Component Reuse Predictable, Pre-verified, Core function Socketized Functions for Plug & Play integration Firm/hard IP Planned IP Reuse Adopted from ‘Surviving the SOC revolution’ by H. Chang et. al. Copyrightⓒ 2003 20

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model n Solution to Design Gap => IP-based Design Plug & play SOC Complex ASIC with a few IPs u. P Core ASIC on DSM Personal Reuse Designerspecific reuse practices Retaining key personnel Source Reuse Functional starting points for block design Document, testbench, predictability Opportunistic IP Reuse FIFO SRAM Area Driven Time-driven design (TDD) Block-based design (BBD) USB MPEG SW I/F IP FLASH D-Cache SRAM FLASH Logic SRAM u. P Core Logic Platform-based design (PBD) Core Reuse Virtual Component Reuse Predictable, Pre-verified, Core function Socketized Functions for Plug & Play integration Firm/hard IP Planned IP Reuse Adopted from ‘Surviving the SOC revolution’ by H. Chang et. al. Copyrightⓒ 2003 20

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model The History of the So. C n The Reign of Terror: Reality & disappointment (1999 -2001) - Overheated IT economy starting in 1999 => collapse of the industry o Thermidor: Platform transformation (2000 -2002) o L’Avenir: The radiant future? Copyrightⓒ 2003 21

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model The History of the So. C n The Reign of Terror: Reality & disappointment (1999 -2001) - Overheated IT economy starting in 1999 => collapse of the industry o Thermidor: Platform transformation (2000 -2002) o L’Avenir: The radiant future? Copyrightⓒ 2003 21

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Challenges in So. C Epoch Time-to-market Process roadmap acceleration Consumerization of electronic devices Silicon Complexity Heterogeneous processes Billion Transistors, Deep submicron effects : crosstalk, wire delays, electromigration, mask costs Copyrightⓒ 2003 22

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Challenges in So. C Epoch Time-to-market Process roadmap acceleration Consumerization of electronic devices Silicon Complexity Heterogeneous processes Billion Transistors, Deep submicron effects : crosstalk, wire delays, electromigration, mask costs Copyrightⓒ 2003 22

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Challenges in So. C Epoch (Cont’d) Design Complexity µCs, DSPs, HW/SW, SW protocol stacks, RTOS’s, digital/analog IPs, On-chips buses System-level architecture Life-in-market Performance/Energy/Cost tradeoff Scalable architecture with unified design environment Copyrightⓒ 2003 23

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Challenges in So. C Epoch (Cont’d) Design Complexity µCs, DSPs, HW/SW, SW protocol stacks, RTOS’s, digital/analog IPs, On-chips buses System-level architecture Life-in-market Performance/Energy/Cost tradeoff Scalable architecture with unified design environment Copyrightⓒ 2003 23

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model How to Solve the Complexity? Use a known real entity A pre-designed component (IP reuse) A platform (architecture reuse) Partition Based on functionality Hardware and software Modeling At different level Consistent and accurate Copyrightⓒ 2003 24

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model How to Solve the Complexity? Use a known real entity A pre-designed component (IP reuse) A platform (architecture reuse) Partition Based on functionality Hardware and software Modeling At different level Consistent and accurate Copyrightⓒ 2003 24

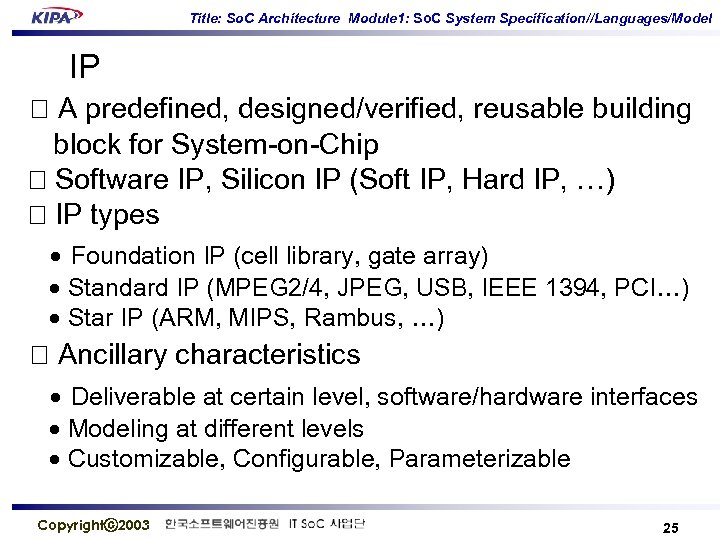

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model IP A predefined, designed/verified, reusable building block for System-on-Chip Software IP, Silicon IP (Soft IP, Hard IP, …) IP types Foundation IP (cell library, gate array) Standard IP (MPEG 2/4, JPEG, USB, IEEE 1394, PCI…) Star IP (ARM, MIPS, Rambus, …) Ancillary characteristics Deliverable at certain level, software/hardware interfaces Modeling at different levels Customizable, Configurable, Parameterizable Copyrightⓒ 2003 25

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model IP A predefined, designed/verified, reusable building block for System-on-Chip Software IP, Silicon IP (Soft IP, Hard IP, …) IP types Foundation IP (cell library, gate array) Standard IP (MPEG 2/4, JPEG, USB, IEEE 1394, PCI…) Star IP (ARM, MIPS, Rambus, …) Ancillary characteristics Deliverable at certain level, software/hardware interfaces Modeling at different levels Customizable, Configurable, Parameterizable Copyrightⓒ 2003 25

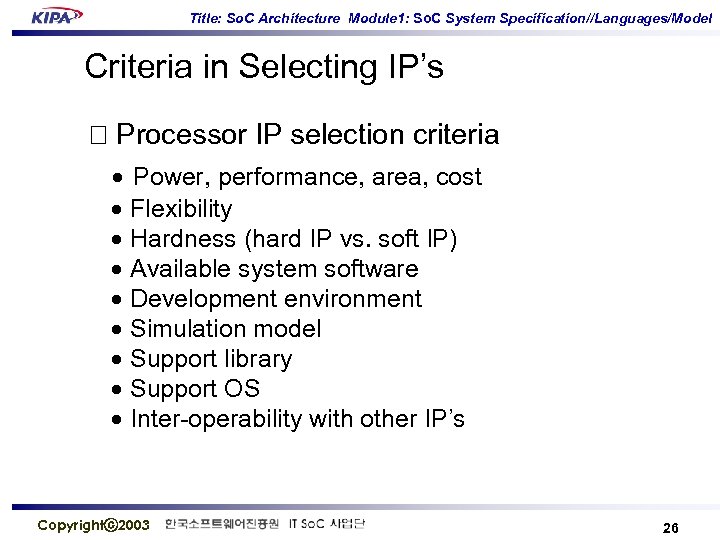

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Criteria in Selecting IP’s Processor IP selection criteria Power, performance, area, cost Flexibility Hardness (hard IP vs. soft IP) Available system software Development environment Simulation model Support library Support OS Inter-operability with other IP’s Copyrightⓒ 2003 26

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Criteria in Selecting IP’s Processor IP selection criteria Power, performance, area, cost Flexibility Hardness (hard IP vs. soft IP) Available system software Development environment Simulation model Support library Support OS Inter-operability with other IP’s Copyrightⓒ 2003 26

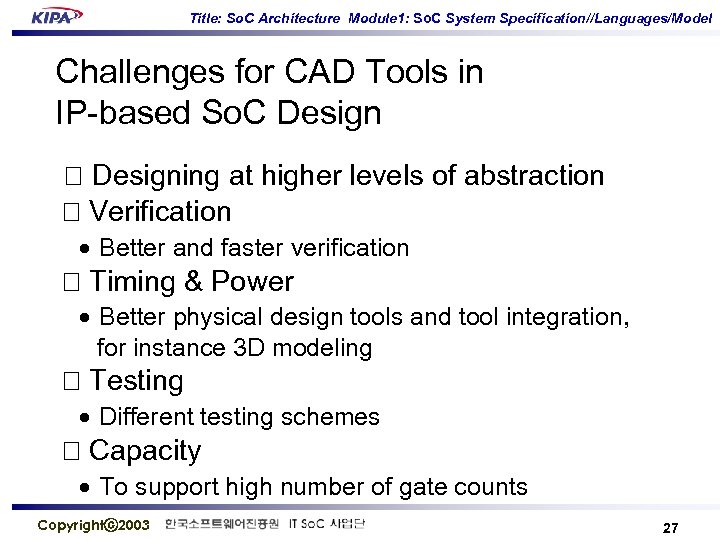

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Challenges for CAD Tools in IP-based So. C Designing at higher levels of abstraction Verification Better and faster verification Timing & Power Better physical design tools and tool integration, for instance 3 D modeling Testing Different testing schemes Capacity To support high number of gate counts Copyrightⓒ 2003 27

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Challenges for CAD Tools in IP-based So. C Designing at higher levels of abstraction Verification Better and faster verification Timing & Power Better physical design tools and tool integration, for instance 3 D modeling Testing Different testing schemes Capacity To support high number of gate counts Copyrightⓒ 2003 27

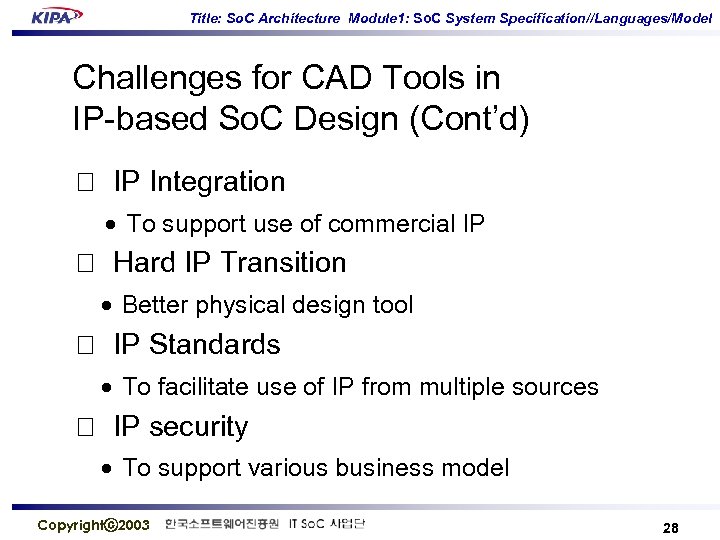

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Challenges for CAD Tools in IP-based So. C Design (Cont’d) IP Integration To support use of commercial IP Hard IP Transition Better physical design tool IP Standards To facilitate use of IP from multiple sources IP security To support various business model Copyrightⓒ 2003 28

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Challenges for CAD Tools in IP-based So. C Design (Cont’d) IP Integration To support use of commercial IP Hard IP Transition Better physical design tool IP Standards To facilitate use of IP from multiple sources IP security To support various business model Copyrightⓒ 2003 28

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Platform A fully defined bus structure and a collection of IP blocks A design methodology to support the feature of “Plugging and Playing” The definition of a platform is the result of a trade-off process involving reusability (programmability and configurability), cost and performance optimization. Enhance the differentiation Copyrightⓒ 2003 29

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Platform A fully defined bus structure and a collection of IP blocks A design methodology to support the feature of “Plugging and Playing” The definition of a platform is the result of a trade-off process involving reusability (programmability and configurability), cost and performance optimization. Enhance the differentiation Copyrightⓒ 2003 29

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model SOC Specification Document-based specification Executable specification Precise behavior description No communication overhead No standard yet Stable methodology CAD tool support required Copyrightⓒ 2003 30

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model SOC Specification Document-based specification Executable specification Precise behavior description No communication overhead No standard yet Stable methodology CAD tool support required Copyrightⓒ 2003 30

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Specification Languages HDL-based specification language VHDL, Verilog Benefit from existing design flow Good for hardware description HLL-based specification language System. C, Spec. C Typically based on C/C++ Good for software/system description Mixed form Superlog, Co. Ware. C Copyrightⓒ 2003 31

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Specification Languages HDL-based specification language VHDL, Verilog Benefit from existing design flow Good for hardware description HLL-based specification language System. C, Spec. C Typically based on C/C++ Good for software/system description Mixed form Superlog, Co. Ware. C Copyrightⓒ 2003 31

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Core Technologies IP Development System Architecture So. C Verification Embedded Software High Speed/Low Power Design Copyrightⓒ 2003 32

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Core Technologies IP Development System Architecture So. C Verification Embedded Software High Speed/Low Power Design Copyrightⓒ 2003 32

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model System Architecture Design Specification, Requirement, Functionalities Architecture C-level design, System. C description and simulation Advantages Broader design space performance, power, cost tradeoff scalability, good for time-in-market Early verification module well-defined, partition, refinement necessary for time-to-market Copyrightⓒ 2003 33

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model System Architecture Design Specification, Requirement, Functionalities Architecture C-level design, System. C description and simulation Advantages Broader design space performance, power, cost tradeoff scalability, good for time-in-market Early verification module well-defined, partition, refinement necessary for time-to-market Copyrightⓒ 2003 33

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Interfacing IPs PCB (=Processor + Peripheral) shrinks to SOC Interface between HW and HW FIFO-based interface: I/O On-chip bus is required On-chip bus: System Bus & Peripheral Bus Copyrightⓒ 2003 34

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Interfacing IPs PCB (=Processor + Peripheral) shrinks to SOC Interface between HW and HW FIFO-based interface: I/O On-chip bus is required On-chip bus: System Bus & Peripheral Bus Copyrightⓒ 2003 34

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Candidates for Standard On-Chip Bus ARM (www. arm. com) AMBA (Advanced Microcontroller Bus Architecture) IBM (www. chips. ibm. com) Core. Connect (PLB/OPB/DCR) PALM Chip (www. palmchip. com) M Bus/Palm Bus Mentor Graphics (www. inventra. com) FISP Bus OMI (www. omimo. be) PI (peripheral Interconnect) Bus Fujitsu (www. fujitsu. com) Spcl Bus Copyrightⓒ 2003 35

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Candidates for Standard On-Chip Bus ARM (www. arm. com) AMBA (Advanced Microcontroller Bus Architecture) IBM (www. chips. ibm. com) Core. Connect (PLB/OPB/DCR) PALM Chip (www. palmchip. com) M Bus/Palm Bus Mentor Graphics (www. inventra. com) FISP Bus OMI (www. omimo. be) PI (peripheral Interconnect) Bus Fujitsu (www. fujitsu. com) Spcl Bus Copyrightⓒ 2003 35

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model So. C Verification System-level verification concurrent, early software hardware co-simulation testbench setup behavior modeling: instruction set simulator, bus functional model, memory behavior model, Verilog or System. C hardware model A dedicated testbench for every IP Register access test to verify bus Test for checking of blocks interconnected functionality and block external interfaces Emulation Copyrightⓒ 2003 36

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model So. C Verification System-level verification concurrent, early software hardware co-simulation testbench setup behavior modeling: instruction set simulator, bus functional model, memory behavior model, Verilog or System. C hardware model A dedicated testbench for every IP Register access test to verify bus Test for checking of blocks interconnected functionality and block external interfaces Emulation Copyrightⓒ 2003 36

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model What is ISV? ISV = In-System Verification When is ISV required? Design refinement down along the hierarchy - Comparison between design levels In-system operation: confirm correct behavior in system environment - Simulation (Chip, I/F) - All-software (Software, Software) - Emulation (HW[FPGA], HW) - Virtual chip (Software, Hardware) Copyrightⓒ 2003 37

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model What is ISV? ISV = In-System Verification When is ISV required? Design refinement down along the hierarchy - Comparison between design levels In-system operation: confirm correct behavior in system environment - Simulation (Chip, I/F) - All-software (Software, Software) - Emulation (HW[FPGA], HW) - Virtual chip (Software, Hardware) Copyrightⓒ 2003 37

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model High Speed / Low Power Design Deep submicron effect High speed circuit design Low power / low voltage design Tradeoffs: Cost vs. Functionality Cost vs. Speed Power vs. Speed Copyrightⓒ 2003 38

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model High Speed / Low Power Design Deep submicron effect High speed circuit design Low power / low voltage design Tradeoffs: Cost vs. Functionality Cost vs. Speed Power vs. Speed Copyrightⓒ 2003 38

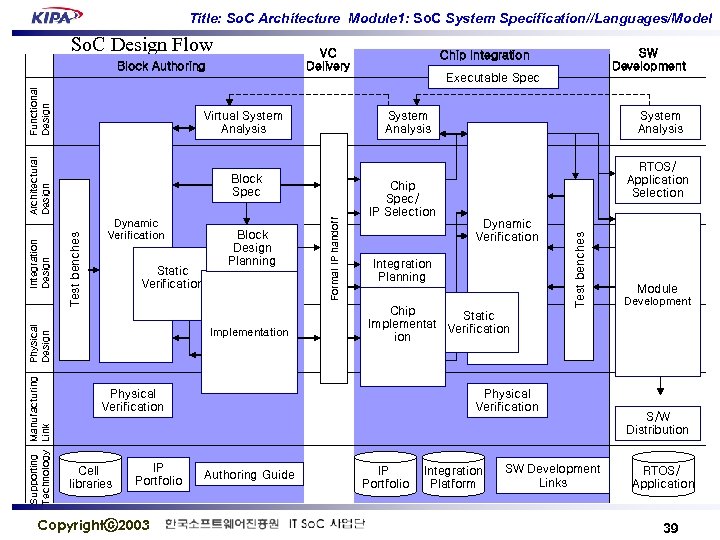

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model VC Delivery Functional Design Block Authoring Static Verification Supporting Manufacturing Technology Link Block Design Planning Implementation Formal IP handoff Test benches Dynamic Verification Executable Spec System Analysis Block Spec Physical Design Integration Design Architectural Design Virtual System Analysis IP Portfolio Copyrightⓒ 2003 System Analysis RTOS/ Application Selection Chip Spec/ IP Selection Dynamic Verification Integration Planning Chip Static Implementat Verification Physical Verification Cell libraries SW Development Chip Integration Test benches So. C Design Flow Physical Verification Authoring Guide IP Portfolio Integration Platform SW Development Links Module Development S/W Distribution RTOS/ Application 39

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model VC Delivery Functional Design Block Authoring Static Verification Supporting Manufacturing Technology Link Block Design Planning Implementation Formal IP handoff Test benches Dynamic Verification Executable Spec System Analysis Block Spec Physical Design Integration Design Architectural Design Virtual System Analysis IP Portfolio Copyrightⓒ 2003 System Analysis RTOS/ Application Selection Chip Spec/ IP Selection Dynamic Verification Integration Planning Chip Static Implementat Verification Physical Verification Cell libraries SW Development Chip Integration Test benches So. C Design Flow Physical Verification Authoring Guide IP Portfolio Integration Platform SW Development Links Module Development S/W Distribution RTOS/ Application 39

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Why do we need models? To perform various design tasks! n n n n n Performance modeling Functional modeling and specification Design and synthesis Validation and verification Test vector generation Test coverage analysis Architecture evaluation and mapping Technology mapping Placement and routing Copyrightⓒ 2003 40

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Why do we need models? To perform various design tasks! n n n n n Performance modeling Functional modeling and specification Design and synthesis Validation and verification Test vector generation Test coverage analysis Architecture evaluation and mapping Technology mapping Placement and routing Copyrightⓒ 2003 40

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model What is a Model? Model: A model is a simplification of another entity, which can be a physical thing or another model. The model contains exactly those characteristics and properties of the modeled entity which are relevant for a given task. A model is minimal with respect to a task, if it does not contain any other characteristics than those relevant for the task. n n A model relates to an entity A model is a simplification of that entity A model is related to a task and an objective A model may relate to a not yet existing entity Copyrightⓒ 2003 41

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model What is a Model? Model: A model is a simplification of another entity, which can be a physical thing or another model. The model contains exactly those characteristics and properties of the modeled entity which are relevant for a given task. A model is minimal with respect to a task, if it does not contain any other characteristics than those relevant for the task. n n A model relates to an entity A model is a simplification of that entity A model is related to a task and an objective A model may relate to a not yet existing entity Copyrightⓒ 2003 41

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Properties of Models n Inherent property: The property is inherent in every model. E. g. the finite state space of a finite state machine model. n Static property: The property can be statically evaluated. E. g. the required memory of a finite state machine model. n Dynamic property: The property can only be dynamically evaluated. E. g. the required memory of a C program. In design we often deal with models of not-yet-existing entities. Thus, the model properties constrain the future entities. Copyrightⓒ 2003 42

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Properties of Models n Inherent property: The property is inherent in every model. E. g. the finite state space of a finite state machine model. n Static property: The property can be statically evaluated. E. g. the required memory of a finite state machine model. n Dynamic property: The property can only be dynamically evaluated. E. g. the required memory of a C program. In design we often deal with models of not-yet-existing entities. Thus, the model properties constrain the future entities. Copyrightⓒ 2003 42

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Heterogeneous Models are Necessary n A system consists of different parts. E. g. data flow and control flow dominated parts. n Different objectives apply for different parts. E. g. the system and its environment. n Different parts are developed by different people and tools. E. g. HW and SW. Copyrightⓒ 2003 43

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model Heterogeneous Models are Necessary n A system consists of different parts. E. g. data flow and control flow dominated parts. n Different objectives apply for different parts. E. g. the system and its environment. n Different parts are developed by different people and tools. E. g. HW and SW. Copyrightⓒ 2003 43

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model (모듈1) 참고문헌 n n n “System Modeling – Model of Computation and their Applications, ” Axel Jantsch LECS, Royal Institute of Technology, Stockholm, Sweden Jan, 2004. “Winning the So. C Revolution-Experiences in Real Design, ” Grant Martin & Henry Chang, Cadence Labs, KAP, Jun, 2003. “Reuse Methodology Manual, ” Michael Keating & Pierre Bricaud, KAP, 2003. “System Design and Methodology: Modeling and Design of Embedded Systems, ” Petru Eles, Linkopings Univ. , Sweden “Embedded Systems Design, ” Frank Vahid, Tony Givargis, John Wiley & Sons, Inc. , 2002. “Memory Issues in Embedded Systems-on-Chip, ” Preeti Ranjan Panda, (Synopsys, Inc. ) Nikil Dutt, (Univ. of Cal/Irvine), Alexandru Nicolau(Univ. of Cal/Irvine), KAP 1999. Copyrightⓒ 2003 44

Title: So. C Architecture Module 1: So. C System Specification//Languages/Model (모듈1) 참고문헌 n n n “System Modeling – Model of Computation and their Applications, ” Axel Jantsch LECS, Royal Institute of Technology, Stockholm, Sweden Jan, 2004. “Winning the So. C Revolution-Experiences in Real Design, ” Grant Martin & Henry Chang, Cadence Labs, KAP, Jun, 2003. “Reuse Methodology Manual, ” Michael Keating & Pierre Bricaud, KAP, 2003. “System Design and Methodology: Modeling and Design of Embedded Systems, ” Petru Eles, Linkopings Univ. , Sweden “Embedded Systems Design, ” Frank Vahid, Tony Givargis, John Wiley & Sons, Inc. , 2002. “Memory Issues in Embedded Systems-on-Chip, ” Preeti Ranjan Panda, (Synopsys, Inc. ) Nikil Dutt, (Univ. of Cal/Irvine), Alexandru Nicolau(Univ. of Cal/Irvine), KAP 1999. Copyrightⓒ 2003 44