Module_1_TMS320F2812.ppt

- Количество слайдов: 15

Модуль 1: Архитектура Цифровой сигнальный контроллер TMS 320 F 2812 Texas Instruments Incorporated 1 -1

Модуль 1: Архитектура Цифровой сигнальный контроллер TMS 320 F 2812 Texas Instruments Incorporated 1 -1

C 281 x Блок схема Шина программ Загр. Секторная D(15 -0) ПЗУ ОЗУ Flash 22 A(18 -0) Менеджер Событий А 12 битный АЦП Сторожевой таймер 32 32 32 R-M-W 32 -бит. 32 x 32 бит АЛУ Регистры Умножитель атомар. PIE прерыв. 3 32 битных ЦП Шина регистров Mc. BSP менеджер функций JTAG реального времени Менеджер Событий B Таймера CAN 2. 0 B SCI-A SCI-B SPI Шина данных GPIO 1 -2

C 281 x Блок схема Шина программ Загр. Секторная D(15 -0) ПЗУ ОЗУ Flash 22 A(18 -0) Менеджер Событий А 12 битный АЦП Сторожевой таймер 32 32 32 R-M-W 32 -бит. 32 x 32 бит АЛУ Регистры Умножитель атомар. PIE прерыв. 3 32 битных ЦП Шина регистров Mc. BSP менеджер функций JTAG реального времени Менеджер Событий B Таймера CAN 2. 0 B SCI-A SCI-B SPI Шина данных GPIO 1 -2

C 28 x ЦП u MCU/DSP - баланс плотности кода & временем его исполнения. u Поддержка 32 -битных инструкций для сокращения времени исполнения u Поддержка 16 -битных инструкций для улучшения эффективности кода Шина программ 32 -бит. 32 x 32 бит АЛУ Регистры Умножитель атомар. u Два 16 x 16 MAC за один цикл с фиксированной точкой (DMAC) u менеджер 32 -/64 -битное ограничение u Модуль деления 64/32 и 32/32 u Быстрое время реакции на прерывания u Инструкции чтения-модификации -записи за один цикл u Уникальная возможность отладки в реальном времени u Совместимость с ранними семействами прерыв. 3 32 битных Шина регистров 32 x 32 битный MAC с фиксированной точкой PIE функций JTAG реального времени 32 -битный DSP процессор с фиксированной запятой u R-M-W u Таймера ЦП Шина данных 1 -3

C 28 x ЦП u MCU/DSP - баланс плотности кода & временем его исполнения. u Поддержка 32 -битных инструкций для сокращения времени исполнения u Поддержка 16 -битных инструкций для улучшения эффективности кода Шина программ 32 -бит. 32 x 32 бит АЛУ Регистры Умножитель атомар. u Два 16 x 16 MAC за один цикл с фиксированной точкой (DMAC) u менеджер 32 -/64 -битное ограничение u Модуль деления 64/32 и 32/32 u Быстрое время реакции на прерывания u Инструкции чтения-модификации -записи за один цикл u Уникальная возможность отладки в реальном времени u Совместимость с ранними семействами прерыв. 3 32 битных Шина регистров 32 x 32 битный MAC с фиксированной точкой PIE функций JTAG реального времени 32 -битный DSP процессор с фиксированной запятой u R-M-W u Таймера ЦП Шина данных 1 -3

Умножитель, АЛУ, Сдвигатели С 28 х Шина программ 32 Шина данных 16 Сдвиг R/L (0 -16) XT (32) or T/TL 32 Умножитель 32 x 32 или два 16 x 16 P (32) or PH/PL 32 32 Сдвиг R/L (0 -16) 32 16/32 8/16 32 32 АЛУ (32) 32 АКК (32) AH (16) AL (16) AH. MSB AH. LSB AL. MSB AL. LSB 32 Сдвиг R/L (0 -16) Шина данных 32 1 -4

Умножитель, АЛУ, Сдвигатели С 28 х Шина программ 32 Шина данных 16 Сдвиг R/L (0 -16) XT (32) or T/TL 32 Умножитель 32 x 32 или два 16 x 16 P (32) or PH/PL 32 32 Сдвиг R/L (0 -16) 32 16/32 8/16 32 32 АЛУ (32) 32 АКК (32) AH (16) AL (16) AH. MSB AH. LSB AL. MSB AL. LSB 32 Сдвиг R/L (0 -16) Шина данных 32 1 -4

Указатели, DP и Память C 28 x Шина данных Шина программ XAR 0 XAR 1 XAR 2 XAR 3 XAR 4 XAR 5 XAR 6 XAR 7 DP (16) 32 6 LSB из IR 22 MUX ARAU Память данных XARn 32 -бита ARn 16 -бит 1 -5

Указатели, DP и Память C 28 x Шина данных Шина программ XAR 0 XAR 1 XAR 2 XAR 3 XAR 4 XAR 5 XAR 6 XAR 7 DP (16) 32 6 LSB из IR 22 MUX ARAU Память данных XARn 32 -бита ARn 16 -бит 1 -5

C 28 x Структура внутренних шин Модуль программ PC Декодер Шина адреса программ (22) Шина данных чтения программ (32) Шина адреса чтения данных (32) Шина данных чтения данных (32) Регистры ARAU SP DP XAR 0 to XAR 7 Память Программ (4 М* 16) @X Модуль исполнения Умнож. 32 x 32 АЛУ XT P ACC R-M-W АЛУ атомар. функций Модуль отладки Эмуляция в реальном времени Память данных (4 Г * 16) JTAG Периферия Шина регистров / Шина результата Шина данных чтения данных/программ (32) Шина адреса записи данных (32) Внешние интерфейсы 1 -6

C 28 x Структура внутренних шин Модуль программ PC Декодер Шина адреса программ (22) Шина данных чтения программ (32) Шина адреса чтения данных (32) Шина данных чтения данных (32) Регистры ARAU SP DP XAR 0 to XAR 7 Память Программ (4 М* 16) @X Модуль исполнения Умнож. 32 x 32 АЛУ XT P ACC R-M-W АЛУ атомар. функций Модуль отладки Эмуляция в реальном времени Память данных (4 Г * 16) JTAG Периферия Шина регистров / Шина результата Шина данных чтения данных/программ (32) Шина адреса записи данных (32) Внешние интерфейсы 1 -6

C 28 x атомарные функции чтения/модификации/записи Преимущество атомарных команд: Загрузка Чтение ЦП АЛУ / Умнож запись Сохранение Стандартное Загрузка/Сохранение DINT MOV AL, *XAR 2 AND AL, #1234 h MOV *XAR 2, AL EINT 6 слов / 6 циклов Память Регистры Легкость программирования Ø Ø Меньше и быстрее код Ø Неразделимы (атомарны) Более эффективны для компилятора Ø Атомарная функция чтения/модификации/записи AND *XAR 2, #1234 h 2 слова / 1 цикл 1 -7

C 28 x атомарные функции чтения/модификации/записи Преимущество атомарных команд: Загрузка Чтение ЦП АЛУ / Умнож запись Сохранение Стандартное Загрузка/Сохранение DINT MOV AL, *XAR 2 AND AL, #1234 h MOV *XAR 2, AL EINT 6 слов / 6 циклов Память Регистры Легкость программирования Ø Ø Меньше и быстрее код Ø Неразделимы (атомарны) Более эффективны для компилятора Ø Атомарная функция чтения/модификации/записи AND *XAR 2, #1234 h 2 слова / 1 цикл 1 -7

C 28 x Конвейер A B C D E F G F 1 F 2 D 1 D 2 R 1 F 1 8 -уровневый конвейер R 2 X W F 2 D 1 D 2 R 1 R 2 X W F 1 F 2 D 1 D 2 R 1 R 2 X F 1 F 2 D 1 D 2 R 1 R 2 X W F 1 F 2 R 1 R 2 X H F 1: Адрес инструкции F 2: Чтение инструкции D 1: Декодирование инструкции D 2: Вычисление адресов операндов R 1: Адрес операнда R 2: Получение операнда X: Вычисление в ЦП W: Сохранение содержимого памяти D 1 D 2 E & G доступ к тому же адресу W W Защита конвейера Ø Ø Порядок результатов такой же как это записано в программе Программисту не нужно заботиться о конвейере 1 -8

C 28 x Конвейер A B C D E F G F 1 F 2 D 1 D 2 R 1 F 1 8 -уровневый конвейер R 2 X W F 2 D 1 D 2 R 1 R 2 X W F 1 F 2 D 1 D 2 R 1 R 2 X F 1 F 2 D 1 D 2 R 1 R 2 X W F 1 F 2 R 1 R 2 X H F 1: Адрес инструкции F 2: Чтение инструкции D 1: Декодирование инструкции D 2: Вычисление адресов операндов R 1: Адрес операнда R 2: Получение операнда X: Вычисление в ЦП W: Сохранение содержимого памяти D 1 D 2 E & G доступ к тому же адресу W W Защита конвейера Ø Ø Порядок результатов такой же как это записано в программе Программисту не нужно заботиться о конвейере 1 -8

TMS 320 F 2812 Карта памяти 0 x 00 0000 Данных | Программ MO SARAM (1 K) Данных | Программ 0 x 00 0400 M 1 SARAM (1 K) PF 0 (2 K) зарезерв. 0 x 00 0800 0 x 00 0 D 00 PIE вектор зарезерв. (256) ENPIE=1 зарезервировано 0 x 00 1000 зарезерв. 0 x 00 6000 PF 2 (4 K) зарезерв. 0 x 00 7000 PF 1 (4 K) 0 x 00 8000 LO SARAM (4 K) 0 x 00 9000 L 1 SARAM (4 K) зарезервировано 0 x 00 A 000 0 x 3 D 7800 OTP (1 K) зарезервировано 0 x 3 D 7 C 00 0 x 3 D 8000 FLASH (128 K) 128 -битный пароль 0 x 3 F 8000 HO SARAM (8 K) зарезервировано 0 x 3 F A 000 0 x 3 F F 000 Загруз. ПЗУ(4 K) MP/MC=0 0 x 3 F FFC 0 BROM vector (32) MP/MC=0 ENPIE=0 зарезервировано XINT Zone 0 (8 K) 0 x 00 2000 XINT Zone 1 (8 K) 0 x 00 4000 зарезервировано XINT Zone 2 (0. 5 M) 0 x 08 0000 XINT Zone 6 (0. 5 M) 0 x 10 0000 0 x 18 0000 зарезервировано 0 x 3 F C 000 XINT Zone 7 (16 K) MP/MC=1 CSM: LO, L 1 XINT Vector-RAM (32) OTP, FLASH MP/MC=1 ENPIE=0 1 -9

TMS 320 F 2812 Карта памяти 0 x 00 0000 Данных | Программ MO SARAM (1 K) Данных | Программ 0 x 00 0400 M 1 SARAM (1 K) PF 0 (2 K) зарезерв. 0 x 00 0800 0 x 00 0 D 00 PIE вектор зарезерв. (256) ENPIE=1 зарезервировано 0 x 00 1000 зарезерв. 0 x 00 6000 PF 2 (4 K) зарезерв. 0 x 00 7000 PF 1 (4 K) 0 x 00 8000 LO SARAM (4 K) 0 x 00 9000 L 1 SARAM (4 K) зарезервировано 0 x 00 A 000 0 x 3 D 7800 OTP (1 K) зарезервировано 0 x 3 D 7 C 00 0 x 3 D 8000 FLASH (128 K) 128 -битный пароль 0 x 3 F 8000 HO SARAM (8 K) зарезервировано 0 x 3 F A 000 0 x 3 F F 000 Загруз. ПЗУ(4 K) MP/MC=0 0 x 3 F FFC 0 BROM vector (32) MP/MC=0 ENPIE=0 зарезервировано XINT Zone 0 (8 K) 0 x 00 2000 XINT Zone 1 (8 K) 0 x 00 4000 зарезервировано XINT Zone 2 (0. 5 M) 0 x 08 0000 XINT Zone 6 (0. 5 M) 0 x 10 0000 0 x 18 0000 зарезервировано 0 x 3 F C 000 XINT Zone 7 (16 K) MP/MC=1 CSM: LO, L 1 XINT Vector-RAM (32) OTP, FLASH MP/MC=1 ENPIE=0 1 -9

Модуль защиты кода u Предотвращает и защищает интеллектуальную собственность 0 x 00 8000 LO SARAM (4 K) 0 x 00 9000 L 1 SARAM (4 K) зарезервировано OTP (1 K) зарезервировано FLASH (128 K) 128 -битный пароль 0 x 00 A 000 0 x 3 D 7800 0 x 3 D 7 C 00 0 x 3 D 8000 u u u 128 -битный пароль пользователя сохраняется во Flash 128 -бит = 2128 = 3. 4 x 1038 возможных паролей Ввод 1 пароля каждые 2 цикла при 150 МГц, потребует затратить как минимум 1. 4 x 1023 лет для нахождения правильной комбинации! 1 - 10

Модуль защиты кода u Предотвращает и защищает интеллектуальную собственность 0 x 00 8000 LO SARAM (4 K) 0 x 00 9000 L 1 SARAM (4 K) зарезервировано OTP (1 K) зарезервировано FLASH (128 K) 128 -битный пароль 0 x 00 A 000 0 x 3 D 7800 0 x 3 D 7 C 00 0 x 3 D 8000 u u u 128 -битный пароль пользователя сохраняется во Flash 128 -бит = 2128 = 3. 4 x 1038 возможных паролей Ввод 1 пароля каждые 2 цикла при 150 МГц, потребует затратить как минимум 1. 4 x 1023 лет для нахождения правильной комбинации! 1 - 10

Управление прерываниями в C 28 x Ø Ø Ø Не требуется программного принятия решения Прямой доступ к векторам в ОЗУ Автоматическое обновление флагов Параллельное сохранение контекста Автоматическое сохранение контекста Умножитель (T, PH, PL) Аккумулятор (AH, AL) Регистр статуса (ST 0, ST 1) Программный счетчик Регистры 0 & 1 Регистр разрешения прерываний Указатель страницы памяти данных 12 x 8 = 96 Ø 96 выделенных PIE векторов Периферийные прерывания Ø PIE - Модуль расширения периферийных прерываний PIE модуль для 96 прерываний INT 1 28 x Логика прерываний ЦП до INT 12 96 12 прерываний IFR IER INTM 28 x ЦП Peripheral Interrupt Expansion Минимальная латентность прерываний 14 – 16 циклов (приблизительно 150 ns при 100 MHz) 1 - 11

Управление прерываниями в C 28 x Ø Ø Ø Не требуется программного принятия решения Прямой доступ к векторам в ОЗУ Автоматическое обновление флагов Параллельное сохранение контекста Автоматическое сохранение контекста Умножитель (T, PH, PL) Аккумулятор (AH, AL) Регистр статуса (ST 0, ST 1) Программный счетчик Регистры 0 & 1 Регистр разрешения прерываний Указатель страницы памяти данных 12 x 8 = 96 Ø 96 выделенных PIE векторов Периферийные прерывания Ø PIE - Модуль расширения периферийных прерываний PIE модуль для 96 прерываний INT 1 28 x Логика прерываний ЦП до INT 12 96 12 прерываний IFR IER INTM 28 x ЦП Peripheral Interrupt Expansion Минимальная латентность прерываний 14 – 16 циклов (приблизительно 150 ns при 100 MHz) 1 - 11

Режимы C 28 x / C 24 x Тип режима Биты режима Опции компилятора OBJMODE AMODE Режим C 24 x 1 1 -v 28 –m 20 Режим C 28 x 1 0 -v 28 Тестовый режим (по умолчанию) 0 0 -v 27 Зарезервировано 0 1 Ø Ø Режим совместимости по коду с C 24 x: Ø Позволяет запускать программы для C 24 x, который был собран средством генерации кода для C 28 x (требуется новая таблица векторов) Режим C 28 x: Ø Обладает достоинствами присущими изначально ядру C 28 x 1 - 12

Режимы C 28 x / C 24 x Тип режима Биты режима Опции компилятора OBJMODE AMODE Режим C 24 x 1 1 -v 28 –m 20 Режим C 28 x 1 0 -v 28 Тестовый режим (по умолчанию) 0 0 -v 27 Зарезервировано 0 1 Ø Ø Режим совместимости по коду с C 24 x: Ø Позволяет запускать программы для C 24 x, который был собран средством генерации кода для C 28 x (требуется новая таблица векторов) Режим C 28 x: Ø Обладает достоинствами присущими изначально ядру C 28 x 1 - 12

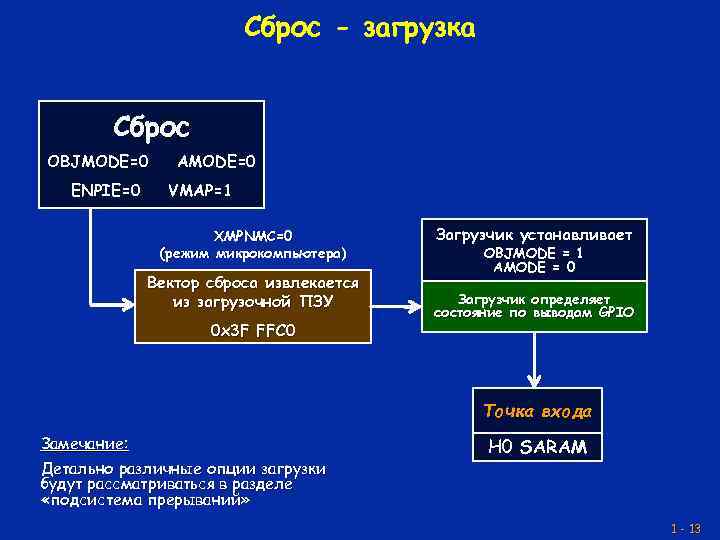

Сброс - загрузка Сброс OBJMODE=0 ENPIE=0 AMODE=0 VMAP=1 XMPNMC=0 (режим микрокомпьютера) Вектор сброса извлекается из загрузочной ПЗУ 0 x 3 F FFC 0 Загрузчик устанавливает OBJMODE = 1 AMODE = 0 Загрузчик определяет состояние по выводам GPIO Точка входа Замечание: Детально различные опции загрузки будут рассматриваться в разделе «подсистема прерываний» H 0 SARAM 1 - 13

Сброс - загрузка Сброс OBJMODE=0 ENPIE=0 AMODE=0 VMAP=1 XMPNMC=0 (режим микрокомпьютера) Вектор сброса извлекается из загрузочной ПЗУ 0 x 3 F FFC 0 Загрузчик устанавливает OBJMODE = 1 AMODE = 0 Загрузчик определяет состояние по выводам GPIO Точка входа Замечание: Детально различные опции загрузки будут рассматриваться в разделе «подсистема прерываний» H 0 SARAM 1 - 13

Заключение u Высокопроизводительный 32 битный DSP u 32 x 32 бита или два 16 x 16 бита MAC u Атомарные инструкции чтения-модификации-записи u 8 -уровневый полностью защищенный конвейер u Менеджер прерываний u 128 K слов Flash памяти на кристалле u Модуль защиты кода (CSM) u Два менеджера событий u 12 -битный модуль АЦП u 56 общих GPIO выводов u Сторожевой таймер u Коммуникационные устройства 1 - 14

Заключение u Высокопроизводительный 32 битный DSP u 32 x 32 бита или два 16 x 16 бита MAC u Атомарные инструкции чтения-модификации-записи u 8 -уровневый полностью защищенный конвейер u Менеджер прерываний u 128 K слов Flash памяти на кристалле u Модуль защиты кода (CSM) u Два менеджера событий u 12 -битный модуль АЦП u 56 общих GPIO выводов u Сторожевой таймер u Коммуникационные устройства 1 - 14